Documente Academic

Documente Profesional

Documente Cultură

Tutorial 1 Answer

Încărcat de

mohandass selvakumarDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Tutorial 1 Answer

Încărcat de

mohandass selvakumarDrepturi de autor:

Formate disponibile

IAS2123-Tutorial 1-MCQ

Multiple-Choice

(Some of the following questions have more than one correct answer. Circle all correct answers.)

1. A program that combines object files into an executable program is called a

_________.

a. compiler

b. loader

c. linker

d. assembler

2. A computer directly executes programs written in its _______ language.

a. system

b. native

c. interpreted

d. machine

3. Is the expression X (Y Z) equivalent to (X Y) (X Z) for all possible inputs

of X, Y, and Z?

a. yes

b. no

4. The following C++ expression can be written using only two lines of assembly

language code:

X = (Y + 4) * 3;

a. true

b. false

5. A single hexadecimal digit can be used to represent 5 binary bits.

a. true

b. false

6. The most significant bit in a binary byte is numbered bit 7.

a. true

b. false

7. A quadword is 8 bytes.

a. true

b. false

COMPUTER ORGANIZATIONS/1

IAS2123-Tutorial 1-MCQ

8. A word (on Intel systems) is 16 bits.

a. true

b. false

9. A doubleword is 64 bits.

a. true

b. false

10. A signed integer stores the sign in the least significant bit (LSB).

a. true

b. false

11. If an integer's sign bit is 1, the integer is negative.

a. true

b. false

12. A signed byte can be equal to +128.

a. true

b. false

13. The expression X Y is only true when X and Y are both true.

a. true

b. false

14. The expression (X Y) is true when X and Y are both false.

a. true

b. false

15. The three most basic operators in Boolean algebra are AND, OR, and NOT.

a. true

b. false

16. The integer range of standard ASCII codes is:

a. 128 to +127

b. 0 to 127

c. 0 to 270

d. 0 to 65,535

COMPUTER ORGANIZATIONS/2

IAS2123-Tutorial 1-MCQ

17. How many bits are used by Unicode characters?

a. 7

b. 8

c. 16

d. 24

18. Which type of program must usually run on multiple platforms?

a. device driver

b. business application

c. embedded system

d. assembler

19. Which of the following best describes the relationship between assembly language

and machine language?

a. one to many

b. one to one

c. many to one

d. many to many

COMPUTER ORGANIZATIONS/3

IAS2123-Tutorial 1-MCQ

20. A program is considered portable if it . . .

a. can be rewritten in a different programming language without losing its meaning.

b. can be quickly copied from conventional RAM into high-speed RAM.

c. can be executed on multiple platforms.

d. none of the above

21. A device driver would ordinarily be written in . . .

a. machine language

b. assembly language

c. a platform-independent language, such as Java

d. an application-oriented language

22. Which of the following are embedded systems applications?

a. an accounting program

b. a javascript program running on a Web page

c. a Nintendo video game

d. a phone book searching program in a cellular phone

23. Suppose a program written in language L1 must be executed on a machine running a

program running in language L0. What important operation must take place?

a. translation of the entire L1 program into L0 code

b. translation of the L0 program into L1 code

c. creation of a language L3 that interprets L0 instructions

d. interpretation of each L1 statement using L0 code as the L1 program is running

24. Conventional machine language instructions are executed by which virtual machine

level?

a. microarchitecture level

b. ISA level

c. assembly language level

d. operating system level

COMPUTER ORGANIZATIONS/4

IAS2123-Tutorial 1-MCQ

25. Which language (or virtual machine) uses short mnemonics such as ADD and SUB

to identify instructions?

a. conventional machine language

b. ISA-level language

c. assembly language

d. microcode interpreter

26. What is the largest unsigned integer that may be stored in 16 bits?

a. 32767

b. 65536

c. 65535

d. 32768

27. What is the largest signed integer that may be stored in 32 bits?

a. 232 1

b. 232

c. 231 1

d. 231

c

28. The two's complement of an integer is formed by doing which of the following?

a. reversing (inverting) the bits and adding 1

b. adding 1 and reversing the bits

c. calculating the integer's additive inverse

d. changing the highest bit to a 1

COMPUTER ORGANIZATIONS/5

IAS2123-Tutorial 1-MCQ

Fill in the Blanks and Short Answer

1

The technique of executing instructions in parallel is called ___pipelining_____.

29. Which unit in the IA-32 instruction cycle performs page protection checks? paging

30. Which component of an operating system is responsible for switching control

between tasks?scheduler

31. Identify three types of segments that would be referenced by segment registers.

Data,code.stack

32. Name two RISC-like features incorporated by Intel into the IA-32 family. Pipelining

superscalar

33. List at least five types of ports found on a typical PC motherboard.

serial,USB,video,keyboard,joystick,mouse

34. Why are serial ports typically slower than parallel ports? Serial transfers 1 bit at a

time but parallel transfers multiple bits simultaneously

Multiple-Choice

35. What is the name of the lowest 8 bits of the EDX register?

a. DL

b. DH

c. DX

d. none of the above

36. How much memory can be addressed in Real-address mode?

a. 640 K

b. 1 MB

c. 16 MB

d. 4 GB

37. How much memory can be addressed in Protected mode?

a. 640 K

b. 1 MB

c. 16 MB

d. 4 GB

COMPUTER ORGANIZATIONS/6

IAS2123-Tutorial 1-MCQ

38. Which of the following linear addresses matches the segment-offset address

08F0:0200?

a. 09100h

b. 09200h

c. 0AF0h

d. 08F2h

39. If you wanted to turn a device on and off using computer software, which type of

port interface would be best?

a. USB

b. keyboard

c. serial

d. parallel

40. What is the name of the bus architecture commonly used with Pentium processors?

a. ISA

b. PCI

c. EISA

d. RAM-BUS

41. Segment-offset addressing is used in which processor mode(s)?

a. Protected

b. Virtual-8086

c. Real-address

d. System management

42. How is Virtual-8086 mode similar to Real-address mode?

a. permits the use of virtual memory (paging)

b. uses a segment descriptor table to track memory usage

c. uses only 16-bit registers for input-output

d. simulates 8086-based computer running in Real-address mode

43. High-speed memory that reduces the frequency of access by the CPU to

conventional memory is called

a. local memory

b. cache memory

c. system memory

COMPUTER ORGANIZATIONS/7

IAS2123-Tutorial 1-MCQ

d. virtual memory

COMPUTER ORGANIZATIONS/8

IAS2123-Tutorial 1-MCQ

44. Why are device drivers needed, given that BIOS programs can do the same task?

a. device drivers allow for the introduction of new devices

b. device drivers have faster performance than BIOS programs

c. BIOS programs are only used by the operating system in Real-address mode

d. device drivers have more direct access to hardware than BIOS programs

45. An interpreter program inside the CPU is written in a language called a(n) _______.

a. machine language interpreter

b. digital driver program

c. microprogram

d. system decoder

46. In regard to multitasking, a task's state consists of which three elements?

a. status flags, program counter, register contents

b. register contents, task variables, program counter

c. task variables, segment descriptor, register contents

d. segment descriptor, status flags, task variables

47. Within the CPU, all calculations and logic operations take place inside the

___________ .

a. registers

b. ALU

c. CU

d. MBU

48. The three types of buses connected to the CPU are:

a. data, address, control

b. data, system, address

c. address, control, memory

d. fetch-decode, control, execution

49. During which phase of the instruction execution cycle is the program counter

incremented?

a. decode

b. execute

c. operand fetch

COMPUTER ORGANIZATIONS/9

IAS2123-Tutorial 1-MCQ

d. fetch

COMPUTER ORGANIZATIONS/10

IAS2123-Tutorial 1-MCQ

50. The four parts of a CPU are:

a. data bus, memory unit, control unit, arithmetic logic unit

b. address bus, registers, control unit, arithmetic logic unit

c. clock, memory unit, control unit, instruction fetch unit

d. clock, registers, control unit, arithmetic logic unit

51. What is the name of the time delay in a CPU caused by differences between the

speed of the CPU, the system bus, and memory circuits?

a. wait cycle

b. wait state

c. dead cycle

d. memory write cycle

52. List the three primary steps of the instruction execution cycle, in sequential order:

a. fetch, decode, memory write

b. fetch, memory read, execute

c. decode, fetch, execute

d. fetch, decode, execute

53. Which stage in the IA-32 instruction cycle is responsible for translating logical

addresses to linear addresses and performing protection checks?

a segment unit

b. code prefetch unit

c. execution unit

d. paging unit

COMPUTER ORGANIZATIONS/11

IAS2123-Tutorial 1-MCQ

54. What are the six stages, or units involved in executing a single IA-32 instruction?

a. code prefetch, instruction decode, execution, segment, paging, memory store

b. bus interface, instruction decode, parallel analysis, execution, segment, paging

c. bus interface, code prefetch, instruction decode, execution, segment, paging

d. bus interface, code prefetch, instruction decode, execution, address translation, paging

55. Which flag is set when an unsigned value is too large to fit into a destination

operand?

a. Sign

b. Carry

c. Overflow

d. Auxiliary Carry

56. In a 4-stage non-pipelined processor, how many clock cycles are required to execute

3 instructions? (Assume that each stage executes in a single clock cycle.)

a. 12

b. 8

c. 6

d. cannot be determined

57. In a 4-stage single-pipelined processor, how many clock cycles are required to

execute 3 instructions? (Assume that each stage executes in a single clock cycle.)

a. 12

b. 8

c. 6

d. cannot be determined

58. In a 6-stage dual-pipelined processor, how many clock cycles are required to execute

5 instructions? (Assume that stage 4 requires two clock cycles, and that stage 4 has

two pipelines.)

a. 10

b. 11

c. 12

d. 15

COMPUTER ORGANIZATIONS/12

IAS2123-Tutorial 1-MCQ

59. Which of the following correctly describes the sequence of reading from memory

during a single clock cycle?

a.

Read line set low; Address placed on bus; Operand placed on data bus by memory

controller; Read line set high, indicating that data bus contains the requested data.

b.

Address placed on bus; Operand placed on data bus by memory controller; Read

line set low; Read line set high, indicating that data bus contains the requested

data.

c.

Address placed on bus; Read line set low; Read line set high, indicating that data

bus contains the requested data; Operand placed on data bus by memory

controller.

d.

Address placed on bus; Read line set low; Operand placed on data bus by

memory controller; Read line set high, indicating that data bus contains the

requested data.

60. Which register is known as a loop counter?

a. EAX

b. EBX

c. ECX

d. EDX

61. Which mode is the native state of the Intel processor?

a. Protected mode

b. Virtual-8086 mode

c. Real-address mode

d. System management mode

62. Real-address mode combines which two values to form addresses?

a. page, segment

b. segment, offset

c. descriptor, segment

d. offset, descriptor

63. When the CPU tries to execute part of a program that has been swapped out to disk,

it executes a

a. descriptor table load

b. general protection fault

c. page fault

d. page translation

COMPUTER ORGANIZATIONS/13

IAS2123-Tutorial 1-MCQ

64. Which type of RAM is typically used for cache memory?

a. static RAM

b. dynamic RAM

c. CMOS RAM

d. Video RAM

(Some of the following questions have more than one correct answer. Circle all correct answers.)

65. Which of the following describe(s) RISC processors?

a. short, simple instructions, executed quickly

b. complex high-level instructions

c. requires microcode interpreter

d. instructions are executed directly by hardware

66. Which of the following is(are) advantages of USB ports over parallel ports?

a. bidirectional data transfer

b. query devices to get name and type of device

c. permits a hub to be connected

d. can suspend power to devices

67. Which type of output is the most general and portable to different computer systems?

a. writing directly to video memory

b. using C++ stream output statements

c. calling operating system functions

d. calling BIOS functions

68. Which type of output will execute the most quickly?

a. writing directly to video memory

b. using C++ stream output statements

c. calling operating system functions

d. calling BIOS functions

Multiple-Choice

1

Which directive identifies the part of a program containing instructions?

a. .DATA

b. .CODE

COMPUTER ORGANIZATIONS/14

IAS2123-Tutorial 1-MCQ

c. .STACK

d. .PROG

69. Which directive(s) are used when defining both signed and unsigned 64-bit integers?

a. QWORD and SQWORD

b. DWORD

c. QWORD

d. DWORD and SDWORD

70. Which of the following are valid data definition statements that create an array of

unsigned bytes containing decimal 10, 20, and 30, named myArray.

a. myArray BYTE 10, 20, 30

b. BYTE myArray 10, 20, 30

c. BYTE myArray[3]: 10, 20,30

d. myArray BYTE DUP (3) 10,20,30

71. In the following data definition, assume that List2 begins at offset 2000h. What is

the offset of the third value (5)?

List2 WORD 3,4,5,6,7

a. 20008h

b. 2002h

c. 2000h

d. 2004h

72. Which letter choice shows the memory byte order, from low to high address, of the

following data definition?

BigVal DWORD 12345678h

a. 56h, 78h,12h,34h

b. 12h,34h,56h,78h

c. 78h,56h,34h,12h

d. 34h,12h,78h,56h

73. The following is a valid identifier: AB62$

a. True

b. False

74. The following is a valid data definition statement:

str1 \

BYTE "This string is quite long!",0

COMPUTER ORGANIZATIONS/15

IAS2123-Tutorial 1-MCQ

a. True

b. False

75. The following are both valid data definition statements:

List1 BYTE 10,20

BYTE 30,40

a. True

b. False

(Some of the following questions have more than one correct answer. Circle all correct

answers.)

76. Which of the following are true about assembly language instructions and directives?

a. a directive is executed at runtime

b. an instruction is executed at runtime

c. a directive is executed at assembly time

d. an instruction is executed at assembly time

77. The basic parts of an instruction, in order from left to right, are:

a. label, mnemonic, operand(s), comment

b. comment, label, mnemonic, operand(s)

c. label, mnemonic, comment

d. mnemonic, operand(s), comment

78. Operands may be any of the following:

a. constant or constant expression

b. reserved word

c. register name

d. variable name (memory)

79. Which of the following will generate assembly errors?

a. var1 BYTE 1101b, 22, 35

b. var2 BYTE "ABCDE",18

c. var3 BYTE '$','98778',

d. var4 BYTE 256,19,40

COMPUTER ORGANIZATIONS/16

IAS2123-Tutorial 1-MCQ

COMPUTER ORGANIZATIONS/17

IAS2123-Tutorial 1-MCQ

Fill in the Blanks and Short Answer

Use the following data definitions until notified otherwise:

byte1 BYTE 0FFh,1,2

byte2 BYTE 14h

word1 WORD 0FFFFh,1,2

word2 WORD 3

word3 SWORD 7FFFh,8000h

word4 SWORD 9000h

dword1 DWORD 10h,20h,30h,40h

dArray DWORD 10 DUP(?)

80. Write one or more statements that move the contents of word1 to word2.

mov ax,word1 ; any general-purpose 16-bits register may be used)

mov word2,ax

81. For each of the following instructions, indicate whether it is legal (L) or illegal (I):

a. mov byte2,0FFh

b. mov word1,byte2

c. mov word2,10000h

d. mov si,word1

L

I

I

L

82. Indicate the hexadecimal value of the destination operand next to each instruction.

Use the letter I to indicate that a particular instruction is illegal:

a. mov dx,word3

b. movsx eax,byte1

c. movdh,al

d. movbx,dx

83. Write an instruction that moves the 32-bit address of word1 into the ESI register

(assume 32-bit Protected mode).

mov esi,OFFSET word1

84. Write an instruction that moves the lower 16 bits of dword1 into the BX register

(hint: use PTR).

mov bx,WORD PTR dword1

85. Write an instruction that moves the lower 8 bits of word2 into the AL register.

mov al, BYTE PTR word2

86. Write an instruction that moves EBX to location word1:

mov DWORD PTR word1,abx

87. What is the value of the expression (TYPE word1)?

COMPUTER ORGANIZATIONS/18

IAS2123-Tutorial 1-MCQ

88. What is the value of the expression (TYPE dword1)? 4

89. What is the value of the expression (LENGTHOF word1)?

90. What is the value of the expression (SIZEOF word1)? 6

Short Programming Problems

Use the following data definitions until notified otherwise:

byte1 BYTE 0FFh,1,2

byte2 BYTE 14h

word1 WORD 0FFFFh,1,2

word2 WORD 3

word3 SWORD 7FFFh,8000h

word4 SWORD 9000h

dword1 DWORD 10h,20h,30h,40h

dArray DWORD 10 DUP(?)

91. Implement the following expression in assembly language, using 32-bit integers

(you may modify any registers you wish):

eax = dword1 + ebx ecx

mov eax,dword1

add eax,ebx

sub eax,ecx

92. Implement the following expression in assembly language, using 32-bit integers

(you may modify any registers you wish):

eax = -dword1 + (edx - ecx) + 1

sub edx,ecx

mov eax,dword1

neg eax

add eax,edx

inc eax

; eax = -dword1

Multiple-Choice

93. The MOV instruction does not permit an immediate value to be moved to a segment

register.

a. true

b. false

94. The MOVSX instruction sign-extends an integer into a larger operand.

a. true

COMPUTER ORGANIZATIONS/19

IAS2123-Tutorial 1-MCQ

b. false

95. Select the answer choice that best implements the following expression. Do not

permit dword1, ECX, or EDX to be modified:

eax = -dword1 + (edx - ecx) + 1

a.

mov eax,dword1

negeax

subedx,ecx

addeax,edx

inceax

b.

mov eax,dword1

negeax

movebx,edx

subebx,ecx

addeax,ebx

inceax

c.

neg dword1

movebx,edx

subebx,ecx

addeax,ebx

inceax

d.

mov eax,dword1

movedx,ebx

subebx,ecx

addeax,ebx

inceax

Some of the following questions have more than one correct answer. Circle all correct

answers:

Use the following data definitions until notified otherwise:

byte1 BYTE 0FFh,1,2

byte2 BYTE 14h

word1 WORD 0FFFFh,1,2

word2 WORD 3

word3 SWORD 7FFFh,8000h

word4 SWORD 9000h

dword1 DWORD 10h,20h,30h,40h

dArray DWORD 10 DUP(?)

96. What is the hexadecimal value of AX when this code executes?

COMPUTER ORGANIZATIONS/20

IAS2123-Tutorial 1-MCQ

movesi,OFFSET word1

add esi,4

mov ax,[esi]

a. 1

b. 2

c. FFFFh

d. 3

97. What is the final hexadecimal value of AX when this code executes?

movebx,OFFSET dword1

sub ebx,2

mov ax,[ebx]

a. 0000h

b. 0010h

c. 9000h

d. 0020h

98. What is the final hexadecimal value of AL when this code executes?

movebx,OFFSET byte1

mov al,[ebx+3]

a. 1

b. 2

c. 14h

d. 3

99. What is the final hexadecimal value of EAX when this code executes?

mov edx,8

mov eax,dword1[edx]

a. 00000010h

b. 20000000h

c. 00300000h

d. 00000030h

100. In Protected mode, which of the following define(s) a pointer variable containing

the offset of word1?

a. ptr1 DWORD word1

b. word1 DWORD ptr1

c. ptr2 DWORD PTR word1

d. ptr2 DWORD OFFSET word1

COMPUTER ORGANIZATIONS/21

IAS2123-Tutorial 1-MCQ

Use the following data for the remaining questions in this section:

word1 WORD 1000h,2000h,3000h,4000h,5000h

dword1 DWORD 10000h,20000h,30000h,40000h

101. What is the final value of AX after this code has executed?

movesi,OFFSET word1

mov ecx,5

mov eax,100h

L1: add ax,[esi]

add ax,16

addesi,TYPE word1

Loop L1

a. F150h

b. 0150h

c. F016h

d. 0016h

102. What is the final value of AX after this code has executed?

movedx,OFFSET word1+8

mov ecx,2

mov ax,0

L1: mov ax,[edx]

add ax,20h

sub edx,4

Loop L1

a. 8040h

b. 9040h

c. 4020h

d. 3020h

COMPUTER ORGANIZATIONS/22

S-ar putea să vă placă și

- C Programming for the Pc the Mac and the Arduino Microcontroller SystemDe la EverandC Programming for the Pc the Mac and the Arduino Microcontroller SystemÎncă nu există evaluări

- IES Objective Question BankDocument10 paginiIES Objective Question BankNischal ParsiÎncă nu există evaluări

- Computer Knowledge Bit Bank for All Competitive ExamsDe la EverandComputer Knowledge Bit Bank for All Competitive ExamsEvaluare: 4 din 5 stele4/5 (4)

- Department of Computer Engineering.: Subject: System Programming and Operating System Class: TEDocument11 paginiDepartment of Computer Engineering.: Subject: System Programming and Operating System Class: TEsurendrarakshitÎncă nu există evaluări

- Intermediate C Programming for the PIC Microcontroller: Simplifying Embedded ProgrammingDe la EverandIntermediate C Programming for the PIC Microcontroller: Simplifying Embedded ProgrammingÎncă nu există evaluări

- BT0036 OPERATING SYSTEM PAPER 1 (BSciIT SEM 2)Document16 paginiBT0036 OPERATING SYSTEM PAPER 1 (BSciIT SEM 2)SeekEducationÎncă nu există evaluări

- All AnswersDocument63 paginiAll AnswersSyed Safian67% (3)

- MCQS in ComputerDocument100 paginiMCQS in ComputerJayve BasconÎncă nu există evaluări

- BC0051-System Software Model Question PaperDocument24 paginiBC0051-System Software Model Question PaperDivyaksh VashishthÎncă nu există evaluări

- BC0042 Operating Systems Paper 1Document16 paginiBC0042 Operating Systems Paper 1SeekEducationÎncă nu există evaluări

- QPDEC2010 Sem 1Document16 paginiQPDEC2010 Sem 1Vishal KanojiyaÎncă nu există evaluări

- Computer Organization Questions and Answers - Basic OrganizationDocument27 paginiComputer Organization Questions and Answers - Basic Organizationmeenakshi singhÎncă nu există evaluări

- Ecen 324 Practice Exam: Midterm #2: Int Unknown (A B && B C: B B A && A C: A 1: C )Document5 paginiEcen 324 Practice Exam: Midterm #2: Int Unknown (A B && B C: B B A && A C: A 1: C )ThatOnePerson123Încă nu există evaluări

- EP TestDocument5 paginiEP Testlc2023asnÎncă nu există evaluări

- Exit Exam Sample QuestionDocument12 paginiExit Exam Sample QuestionHanan ShayiboÎncă nu există evaluări

- Bca CF&PST PutDocument11 paginiBca CF&PST PutPriyanshu SrivastavaÎncă nu există evaluări

- Programming Language ExamsDocument9 paginiProgramming Language ExamsLucien YemahÎncă nu există evaluări

- Computer Basic QuestionsDocument13 paginiComputer Basic QuestionsAnup RawatÎncă nu există evaluări

- CA&ODocument12 paginiCA&OMohammad AhmedÎncă nu există evaluări

- Computer ArchitecureDocument150 paginiComputer ArchitecurediÎncă nu există evaluări

- UNIT 4 MCQDocument3 paginiUNIT 4 MCQomprakash202067% (6)

- SP MCQDocument15 paginiSP MCQVishal KesharwaniÎncă nu există evaluări

- EsasDocument47 paginiEsasLovelle Belaca-olÎncă nu există evaluări

- Comprehensive 1 PDFDocument154 paginiComprehensive 1 PDFSrinithy SaravananÎncă nu există evaluări

- IT Class 9Document20 paginiIT Class 9Sde BdrÎncă nu există evaluări

- Computer MCQDocument31 paginiComputer MCQTECH DIARYÎncă nu există evaluări

- Computer Architecture and OrganizationDocument5 paginiComputer Architecture and OrganizationPriyanka PardeshiÎncă nu există evaluări

- Sample PaperDocument9 paginiSample Papersrdfm gntÎncă nu există evaluări

- Esas ReviewDocument48 paginiEsas ReviewSPARK TVÎncă nu există evaluări

- Multiple Choice QuestionsDocument6 paginiMultiple Choice QuestionsSravanthi Gelley0% (1)

- MC0073 System ProgrammingDocument35 paginiMC0073 System ProgrammingSwati NandiÎncă nu există evaluări

- Computer FundamentalsDocument29 paginiComputer FundamentalsJimmy OrajayÎncă nu există evaluări

- Pps - Question BankDocument65 paginiPps - Question BankS.SRI KRISHNA (RA2111026020166)Încă nu există evaluări

- ZOS MasteryDocument16 paginiZOS MasteryVishal FundingÎncă nu există evaluări

- Ec8552 - Cao MCQDocument27 paginiEc8552 - Cao MCQformyphdÎncă nu există evaluări

- Multiple Choice Questions-CcpDocument8 paginiMultiple Choice Questions-CcpSunitha PÎncă nu există evaluări

- Computer Science Past Papers MCQS SolvedDocument24 paginiComputer Science Past Papers MCQS SolvedLEGAL AFFAIRS DIVISION100% (1)

- Examinations For 2005 - 2006 / Semester 1: Module: Computer Fundamentals Module Code: Duration: 2 HoursDocument8 paginiExaminations For 2005 - 2006 / Semester 1: Module: Computer Fundamentals Module Code: Duration: 2 HoursAmani UrassaÎncă nu există evaluări

- Computer Objective QuestionsDocument17 paginiComputer Objective QuestionsVijay ShindeÎncă nu există evaluări

- Paper 1Document10 paginiPaper 1jerome_weirÎncă nu există evaluări

- Technical Questions: CalypsoDocument17 paginiTechnical Questions: CalypsoPradeep TiwariÎncă nu există evaluări

- Amazon Online Assessment 2021 QuestionsDocument12 paginiAmazon Online Assessment 2021 QuestionsCoder Coder0% (2)

- Computer MCQDocument8 paginiComputer MCQangelo_lopez1993Încă nu există evaluări

- KRISHNENDU GUIN - Assignment 2Document20 paginiKRISHNENDU GUIN - Assignment 2Krishnendu GuinÎncă nu există evaluări

- 2014S IP QuestionDocument49 pagini2014S IP Questionmhel20010Încă nu există evaluări

- 390 - Computer Programming Concepts (Open) - R - 2020Document10 pagini390 - Computer Programming Concepts (Open) - R - 2020avfg gfavdÎncă nu există evaluări

- 5 Units 1 MarksDocument18 pagini5 Units 1 MarksNAGARAJ GÎncă nu există evaluări

- SYCS Sem III SQ Oct 2021 Physical Computing and IOT ProgrammingDocument13 paginiSYCS Sem III SQ Oct 2021 Physical Computing and IOT Programmingsiddhi khamkarÎncă nu există evaluări

- Distributed System - Mcqs A. 16-BitDocument8 paginiDistributed System - Mcqs A. 16-BitAmit PatilÎncă nu există evaluări

- Cse11 MCQ QuestonDocument16 paginiCse11 MCQ Questonmyaswanthkrishna9706Încă nu există evaluări

- Electronics Sample Problems 05Document6 paginiElectronics Sample Problems 05Genesis PinedaÎncă nu există evaluări

- OS Practice Test QuesDocument15 paginiOS Practice Test QuesSwaraj Rawte vines JEÎncă nu există evaluări

- Embedded System QuizDocument19 paginiEmbedded System Quizjaya shreeÎncă nu există evaluări

- 1478175959468-CSE&IT StreamDocument55 pagini1478175959468-CSE&IT StreamsaiprashantÎncă nu există evaluări

- Assignment 2 (Stik)Document12 paginiAssignment 2 (Stik)Jackson YehÎncă nu există evaluări

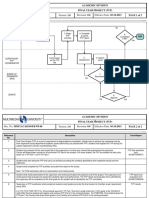

- SOP06 ACAD Final Year ProjectDocument2 paginiSOP06 ACAD Final Year Projectmohandass selvakumarÎncă nu există evaluări

- System DesignDocument2 paginiSystem Designmohandass selvakumarÎncă nu există evaluări

- List of Panel - IAD3162Document2 paginiList of Panel - IAD3162mohandass selvakumarÎncă nu există evaluări

- Disc Brake ProjectDocument3 paginiDisc Brake ProjectPathan ShamsheerkhanÎncă nu există evaluări

- Gantt ChartDocument1 paginăGantt Chartmohandass selvakumarÎncă nu există evaluări

- Solar Thermal Ordinances in EuropeDocument27 paginiSolar Thermal Ordinances in Europemohandass selvakumarÎncă nu există evaluări

- Form of E-Commerce: JN Musical (Jayasuthan A/l Jayabalan & Navakumar A/l Mohan)Document2 paginiForm of E-Commerce: JN Musical (Jayasuthan A/l Jayabalan & Navakumar A/l Mohan)mohandass selvakumarÎncă nu există evaluări

- Industrial Training Programme: Student Personal DetailsDocument1 paginăIndustrial Training Programme: Student Personal Detailsmohandass selvakumarÎncă nu există evaluări

- No4 PDFDocument6 paginiNo4 PDFmohandass selvakumarÎncă nu există evaluări

- Turorial 2Document1 paginăTurorial 2mohandass selvakumarÎncă nu există evaluări

- Department of Statistics Malaysia: Labour Market in Malaysia, June 2015Document4 paginiDepartment of Statistics Malaysia: Labour Market in Malaysia, June 2015mohandass selvakumarÎncă nu există evaluări

- Yes - The Fastest 4G Mobile Internet With VoiceDocument2 paginiYes - The Fastest 4G Mobile Internet With Voicemohandass selvakumarÎncă nu există evaluări

- ViewDocument8 paginiViewmohandass selvakumarÎncă nu există evaluări

- ViewDocument5 paginiViewmohandass selvakumarÎncă nu există evaluări

- Case Study-Software RequirementDocument69 paginiCase Study-Software RequirementNiyaishZahraÎncă nu există evaluări

- Section A - Company/Organization BackgroundDocument3 paginiSection A - Company/Organization Backgroundmohandass selvakumarÎncă nu există evaluări

- In Out: Import Public Class Public Static Void Int NewDocument3 paginiIn Out: Import Public Class Public Static Void Int Newmohandass selvakumarÎncă nu există evaluări

- Faculty of Computer Science and Information Technology: Prepared ForDocument3 paginiFaculty of Computer Science and Information Technology: Prepared Formohandass selvakumarÎncă nu există evaluări

- Analysis of Online Shopping Cart SolutionsDocument23 paginiAnalysis of Online Shopping Cart SolutionsmounicasrungaÎncă nu există evaluări

- Design StrategiesDocument15 paginiDesign Strategiesmohandass selvakumarÎncă nu există evaluări

- Cse-IV-computer Organization (10cs46) - Question PaperDocument9 paginiCse-IV-computer Organization (10cs46) - Question PapernbprÎncă nu există evaluări

- MELG642hout 2 Sem 2012Document2 paginiMELG642hout 2 Sem 2012Neha PachauriÎncă nu există evaluări

- Computer Architecture: Ali Saeed Khan March, 2015Document36 paginiComputer Architecture: Ali Saeed Khan March, 2015Umar TahirÎncă nu există evaluări

- CH01 IntroductionDocument17 paginiCH01 IntroductionLim Soong XIanÎncă nu există evaluări

- Intel Centrino Mobile Technology LearnDocument5 paginiIntel Centrino Mobile Technology LearnSimmi JoshiÎncă nu există evaluări

- Closing The Gap Between Asic Custom Tools and TechniquesDocument431 paginiClosing The Gap Between Asic Custom Tools and TechniquesAnonymous ZaO7fL4t100% (3)

- CBCS ComputerDocument82 paginiCBCS ComputerDeep Narayan PaulÎncă nu există evaluări

- Digital Design and Computer Architecture: ARM® Edition: Sarah L. Harris and David Money HarrisDocument28 paginiDigital Design and Computer Architecture: ARM® Edition: Sarah L. Harris and David Money HarrisSimon ll4Încă nu există evaluări

- ECE 1749H: Interconnection Networks For Parallel Computer Architectures: Router MicroarchitectureDocument58 paginiECE 1749H: Interconnection Networks For Parallel Computer Architectures: Router MicroarchitectureSreekanth PagadapalliÎncă nu există evaluări

- Teaching Computer Architecture Organisation Using SimulatorsDocument6 paginiTeaching Computer Architecture Organisation Using SimulatorsTenma InazumaÎncă nu există evaluări

- MCA Syllabus - 1st Sem PDFDocument32 paginiMCA Syllabus - 1st Sem PDFshatabdi mukherjeeÎncă nu există evaluări

- Assignment 1 - CSE211 RGDocument4 paginiAssignment 1 - CSE211 RGSurya TyagiÎncă nu există evaluări

- Co - SvewDocument82 paginiCo - SvewnbprÎncă nu există evaluări

- Processor AMD Vs Intel 2020Document13 paginiProcessor AMD Vs Intel 2020MD Showeb Arif SiddiquieÎncă nu există evaluări

- Intel Sandy Ntel Sandy Bridge ArchitectureDocument54 paginiIntel Sandy Ntel Sandy Bridge ArchitectureJaisson K SimonÎncă nu există evaluări

- Formative Assessment BN103Document4 paginiFormative Assessment BN103Luchheng GurungÎncă nu există evaluări

- Ecommended Eading: William StallingsDocument23 paginiEcommended Eading: William StallingsNoobies triapthiÎncă nu există evaluări

- Core I5 ReportDocument13 paginiCore I5 ReportAmelia AndreaÎncă nu există evaluări

- Hardware MaintenanceDocument87 paginiHardware MaintenanceMnjira AbdallahÎncă nu există evaluări

- Ok6410 Board Hardware ManualDocument23 paginiOk6410 Board Hardware ManualcharaswatÎncă nu există evaluări

- MP Vs MCDocument6 paginiMP Vs MCAyushi SavaniÎncă nu există evaluări

- Data SheetDocument332 paginiData SheetRuxandra TrandafirÎncă nu există evaluări

- Solution Manual For Modern Processor Design by John Paul Shen and Mikko H. Lipasti PDFDocument2 paginiSolution Manual For Modern Processor Design by John Paul Shen and Mikko H. Lipasti PDFtargetiesÎncă nu există evaluări

- Arm TutorialDocument50 paginiArm Tutorialhub23Încă nu există evaluări

- High Performance ComputingDocument6 paginiHigh Performance ComputingMohammad Bilal MirzaÎncă nu există evaluări

- Instructor: Nima Honarmand: Spring 2015:: CSE 502 - Computer ArchitectureDocument16 paginiInstructor: Nima Honarmand: Spring 2015:: CSE 502 - Computer ArchitectureEv EnidÎncă nu există evaluări

- II I SyllabusDocument24 paginiII I SyllabusDR MAITHILIÎncă nu există evaluări

- Meltdown AttackDocument15 paginiMeltdown AttackNhan Nguyen HienÎncă nu există evaluări

- Syllabus Cbcs III IV 27.09.19Document51 paginiSyllabus Cbcs III IV 27.09.19हर्ष सौदर्शनÎncă nu există evaluări

- New OutlineDocument15 paginiNew OutlineShaista SaeedÎncă nu există evaluări

- iPhone 15 Pro User Guide for Beginners and SeniorsDe la EverandiPhone 15 Pro User Guide for Beginners and SeniorsÎncă nu există evaluări

- iPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsDe la EverandiPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsEvaluare: 5 din 5 stele5/5 (2)

- CompTIA Security+ All-in-One Exam Guide, Sixth Edition (Exam SY0-601)De la EverandCompTIA Security+ All-in-One Exam Guide, Sixth Edition (Exam SY0-601)Evaluare: 5 din 5 stele5/5 (1)

- iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]De la EverandiPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]Evaluare: 5 din 5 stele5/5 (2)

- Chip War: The Fight for the World's Most Critical TechnologyDe la EverandChip War: The Fight for the World's Most Critical TechnologyEvaluare: 4.5 din 5 stele4.5/5 (82)

- Chip War: The Quest to Dominate the World's Most Critical TechnologyDe la EverandChip War: The Quest to Dominate the World's Most Critical TechnologyEvaluare: 4.5 din 5 stele4.5/5 (227)

- CompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102De la EverandCompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Evaluare: 5 din 5 stele5/5 (2)

- iPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XDe la EverandiPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XEvaluare: 3 din 5 stele3/5 (2)

- Computer Science: A Concise IntroductionDe la EverandComputer Science: A Concise IntroductionEvaluare: 4.5 din 5 stele4.5/5 (14)

- Mastering IoT For Industrial Environments: Unlock the IoT Landscape for Industrial Environments with Industry 4.0, Covering Architecture, Protocols like MQTT, and Advancements with ESP-IDFDe la EverandMastering IoT For Industrial Environments: Unlock the IoT Landscape for Industrial Environments with Industry 4.0, Covering Architecture, Protocols like MQTT, and Advancements with ESP-IDFÎncă nu există evaluări

- Unlock Any Roku Device: Watch Shows, TV, & Download AppsDe la EverandUnlock Any Roku Device: Watch Shows, TV, & Download AppsÎncă nu există evaluări

- Hacking With Linux 2020:A Complete Beginners Guide to the World of Hacking Using Linux - Explore the Methods and Tools of Ethical Hacking with LinuxDe la EverandHacking With Linux 2020:A Complete Beginners Guide to the World of Hacking Using Linux - Explore the Methods and Tools of Ethical Hacking with LinuxÎncă nu există evaluări

- Windows 10 Mastery: The Complete User Guide to Learn Windows 10 from Beginner to ExpertDe la EverandWindows 10 Mastery: The Complete User Guide to Learn Windows 10 from Beginner to ExpertEvaluare: 3.5 din 5 stele3.5/5 (6)

- Amazon Web Services (AWS) Interview Questions and AnswersDe la EverandAmazon Web Services (AWS) Interview Questions and AnswersEvaluare: 4.5 din 5 stele4.5/5 (3)

- iWoz: How I Invented the Personal Computer and Had Fun Along the WayDe la EverandiWoz: How I Invented the Personal Computer and Had Fun Along the WayEvaluare: 3.5 din 5 stele3.5/5 (317)

- CompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002De la EverandCompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002Evaluare: 5 din 5 stele5/5 (1)

- How to Jailbreak Roku: Unlock Roku, Roku Stick, Roku Ultra, Roku Express, Roku TV with Kodi Step by Step GuideDe la EverandHow to Jailbreak Roku: Unlock Roku, Roku Stick, Roku Ultra, Roku Express, Roku TV with Kodi Step by Step GuideEvaluare: 1 din 5 stele1/5 (1)

- Essential iPhone X iOS 12 Edition: The Illustrated Guide to Using iPhone XDe la EverandEssential iPhone X iOS 12 Edition: The Illustrated Guide to Using iPhone XEvaluare: 5 din 5 stele5/5 (1)

- Programming with STM32: Getting Started with the Nucleo Board and C/C++De la EverandProgramming with STM32: Getting Started with the Nucleo Board and C/C++Evaluare: 3.5 din 5 stele3.5/5 (3)

- Amazon Echo Manual Guide : Top 30 Hacks And Secrets To Master Amazon Echo & Alexa For Beginners: The Blokehead Success SeriesDe la EverandAmazon Echo Manual Guide : Top 30 Hacks And Secrets To Master Amazon Echo & Alexa For Beginners: The Blokehead Success SeriesÎncă nu există evaluări

![iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]](https://imgv2-1-f.scribdassets.com/img/audiobook_square_badge/728318688/198x198/f3385cbfef/1714829744?v=1)