Documente Academic

Documente Profesional

Documente Cultură

Square Waves To Sine Waves

Încărcat de

Electrical-EngineerTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Square Waves To Sine Waves

Încărcat de

Electrical-EngineerDrepturi de autor:

Formate disponibile

Standalone Circuit Converts Square Waves To Sine Waves

Many microcontrollers or PICs will have uncommitted digital-to-analog converter (DAC) outputs that can be used to generate

sine waves. But these are generally low resolution (8 to 10 bits), yielding a total harmonic distortion (THD) in the 1% range.

Or, using a fifth- or seventh-order switched-capacitor filter with a square-wave output ties up two I/O pins on the MCU. One

output is used for the filter input and one for the filter clock. Also, the two outputs must be square waves and track at a 100:1

ratio.

Because the MCU will have more processes to handle than just generating a sine wave, tying up two timers or one timer

and firmware usually requires too much system overhead. Therefore, the system designer is forced to use a faster or more

expensive MCU.

Here's a better approach: Use an RDD104 selectable four-decade CMOS divider and an MSFS5 switched-capacitor filter to

create a two-chip, 0.2%-distortion sine-wave source. The RDD104 has two pins that select one of four dividers: divide-by-10,

divide-by-100, divide-by-1000, and divide-by-10k. The device can be used either with an external clock on pin 5 or with a

crystal. The maximum frequency range is 1.5 MHz at 5 V dc.

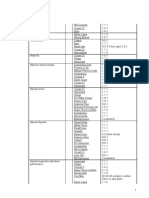

The figure shows the schematic for the square-wave-to-sine-wave converter. A crystal and a 10-MO resistor are connected

across pins 5 and 6 of the RDD104. A 100-pF capacitor (C5) is tied to pin 5. The input capacitance of the MSFS5 and the

connection between pin 6 of the RDD104 and pin 4 of the MSFS5 provides equal capacitance on pin 2 of the crystal. With

DIV_SEL_1 tied low and DIV_SEL_2 tied high, the 100:1 divider is selected.

The MSFS5 is a pin-selectable, seventh-order, low-pass/six-pole bandpass switched-capacitor filter. The eight-pin IC can

set for Butterworth, Bessel, or elliptic low-pass filters; or for full, 1/3- and 1/6-octave bandpass filters. Clock_Out of the

RDD104 is ac-coupled to the Clock input of the MSFS5. The MSFS5 is set for 1/6-octave bandpass operation for maximum

attenuation of square-wave harmonics without attenuating the fundamental. Bandpass and 1/6-octave configuration is

obtained by tying FSEL and TYPE to VDD. The filter is configured for single-supply operation, with VDD at 5 V, VSS at 0 V, and

GND tied to mid-supply with two resistors (R4 and R5). A 0.1-µF capacitor decouples the input. The output of the RDD104 is

attenuated with two 10-kO resistors and ac coupled to the filter input of the MSFS5.

With this configuration, a 10-kHz, 1-V rms sine-wave output is achieved. Total current consumption is less than 2 mA at 5 V

dc, making this solution ideal for portable applications. THD is at 0.2% for a bandwidth from 400 Hz to 300 kHz (measured

with an AP Portable One Plus Access).

S-ar putea să vă placă și

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- CompAI - Learning Algorithms For A Neural Network With Laterally Inhibited Receptive Fields - 1998 - Neural Networks Proceedings, IEEEDocument6 paginiCompAI - Learning Algorithms For A Neural Network With Laterally Inhibited Receptive Fields - 1998 - Neural Networks Proceedings, IEEECristian LiviuÎncă nu există evaluări

- IEEEwaveletDocument18 paginiIEEEwaveletAlbertasDDDÎncă nu există evaluări

- Mousavinezhad, Abdel-Qader. IEEE - Digital Signal Processing in Theory & PracticeDocument4 paginiMousavinezhad, Abdel-Qader. IEEE - Digital Signal Processing in Theory & PracticeAirÎncă nu există evaluări

- IEEE Adaptive Filters in MATLAB - From Novice To Expert - 2002Document6 paginiIEEE Adaptive Filters in MATLAB - From Novice To Expert - 2002cristian1961Încă nu există evaluări

- IEEE - Concept Design For A Web-Based SCADA SystemDocument5 paginiIEEE - Concept Design For A Web-Based SCADA Systemcristian1961Încă nu există evaluări

- IEEE Adaptive Filters in MATLAB - From Novice To Expert - 2002Document6 paginiIEEE Adaptive Filters in MATLAB - From Novice To Expert - 2002cristian1961Încă nu există evaluări

- Watss and VADocument2 paginiWatss and VAArul RamÎncă nu există evaluări

- A Computer Simulation of An Induction HeatingDocument12 paginiA Computer Simulation of An Induction Heatingdumitrescu viorelÎncă nu există evaluări

- IEEE - A Novel Low Power Low Phase-Noise PLL Architecture For Wireless (%1.2)Document4 paginiIEEE - A Novel Low Power Low Phase-Noise PLL Architecture For Wireless (%1.2)Cristian LiviuÎncă nu există evaluări

- Build A Smart Battery Charger Using A Single Transistor CircuitDocument2 paginiBuild A Smart Battery Charger Using A Single Transistor CircuitCristian Liviu100% (1)

- Wavelet Theory DemystifiedDocument14 paginiWavelet Theory DemystifiedAndy2102Încă nu există evaluări

- Spice Simulator Tunes RC ActiveDocument2 paginiSpice Simulator Tunes RC ActiveCristian LiviuÎncă nu există evaluări

- A. J. Viterbi. A Personal History of The Viterbi Algorithm IEEE Signal Processing Magazine PP 120-122 142 July 2006. IEEEDocument4 paginiA. J. Viterbi. A Personal History of The Viterbi Algorithm IEEE Signal Processing Magazine PP 120-122 142 July 2006. IEEECristian LiviuÎncă nu există evaluări

- Use Analog Techniques To Measure Capacitance in Capacitive SensorsDocument9 paginiUse Analog Techniques To Measure Capacitance in Capacitive SensorsCristian LiviuÎncă nu există evaluări

- Use Hybrid PMOS-NMOS Active Loads To Cut Substrate Noise in Differential AmplifiersDocument3 paginiUse Hybrid PMOS-NMOS Active Loads To Cut Substrate Noise in Differential AmplifiersCristian LiviuÎncă nu există evaluări

- VariableGain Active Band Pass Filter Uses Only One Op-AmpDocument1 paginăVariableGain Active Band Pass Filter Uses Only One Op-AmpCristian LiviuÎncă nu există evaluări

- Zero-Cross Detectors Deliver Positivee and Negative TriggeringDocument2 paginiZero-Cross Detectors Deliver Positivee and Negative TriggeringCristian Liviu100% (1)

- Use The PC's Parallel Port For Fast Data Acquisition and ControlDocument3 paginiUse The PC's Parallel Port For Fast Data Acquisition and ControlCristian Liviu100% (1)

- VariableGain Active Band Pass Filter Uses Only One Op-AmpDocument1 paginăVariableGain Active Band Pass Filter Uses Only One Op-AmpCristian LiviuÎncă nu există evaluări

- Use The PC's Parallel Port For Fast Data Acquisition and ControlDocument3 paginiUse The PC's Parallel Port For Fast Data Acquisition and ControlCristian Liviu100% (1)

- Switching Circuit Increases Number of USARTs Available From MCUDocument2 paginiSwitching Circuit Increases Number of USARTs Available From MCUCristian Liviu100% (1)

- Spice Simulator Tunes RC ActiveDocument2 paginiSpice Simulator Tunes RC ActiveCristian LiviuÎncă nu există evaluări

- Use Hybrid PMOS-NMOS Active Loads To Cut Substrate Noise in Differential AmplifiersDocument3 paginiUse Hybrid PMOS-NMOS Active Loads To Cut Substrate Noise in Differential AmplifiersCristian LiviuÎncă nu există evaluări

- Use Your Serial Port For Isolated Data AcquisitionDocument2 paginiUse Your Serial Port For Isolated Data AcquisitionCristian Liviu100% (1)

- Spice Model For An Ideal Transformer Allows Bidirectional OperationDocument3 paginiSpice Model For An Ideal Transformer Allows Bidirectional OperationCristian LiviuÎncă nu există evaluări

- Special Low-Pass Filter Limits SlopeDocument3 paginiSpecial Low-Pass Filter Limits SlopeCristian Liviu100% (1)

- Single Transiator Constant Current GeneratorDocument2 paginiSingle Transiator Constant Current GeneratorCristian LiviuÎncă nu există evaluări

- SerieConected Transistor Use Differential Heating To Sense AirflowDocument3 paginiSerieConected Transistor Use Differential Heating To Sense AirflowCristian LiviuÎncă nu există evaluări

- Single Transiator Constant Current GeneratorDocument2 paginiSingle Transiator Constant Current GeneratorCristian LiviuÎncă nu există evaluări

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (344)

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (399)

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (588)

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (266)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (73)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2259)

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (120)

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)

- IFIS - Intraoperative Floppy Iris Syndrome Wa Wa 27-09-2008Document18 paginiIFIS - Intraoperative Floppy Iris Syndrome Wa Wa 27-09-2008JanuszÎncă nu există evaluări

- 9446 - Data Sheets Final PDFDocument17 pagini9446 - Data Sheets Final PDFmarounÎncă nu există evaluări

- Ansible Automation SA Technical Deck Q2FY19Document43 paginiAnsible Automation SA Technical Deck Q2FY19daniel_vp21Încă nu există evaluări

- HardikDocument21 paginiHardikGohil HardikÎncă nu există evaluări

- Business Model Navigator Whitepaper - 2019Document9 paginiBusiness Model Navigator Whitepaper - 2019Zaw Ye HtikeÎncă nu există evaluări

- Taper Lock BushesDocument4 paginiTaper Lock BushesGopi NathÎncă nu există evaluări

- Lcnews227 - Nexera SeriesDocument47 paginiLcnews227 - Nexera SeriesMuhammad RohmanÎncă nu există evaluări

- Vintage Tavern - PrintInspectionDocument4 paginiVintage Tavern - PrintInspectionBryce AirgoodÎncă nu există evaluări

- An Appraisal of The Literature On Centric Relation. Part II: ReviewDocument11 paginiAn Appraisal of The Literature On Centric Relation. Part II: ReviewManjulika TysgiÎncă nu există evaluări

- 2UEB000487 v1 Drive On GeneratorDocument19 pagini2UEB000487 v1 Drive On GeneratorSherifÎncă nu există evaluări

- Annual Report 2022-23 (Eng.)Document326 paginiAnnual Report 2022-23 (Eng.)Gaurav DurejaÎncă nu există evaluări

- Varactor AssignmentDocument9 paginiVaractor Assignmentjawad_h89Încă nu există evaluări

- Asyb 2020 2Document295 paginiAsyb 2020 2KhangÎncă nu există evaluări

- Timer Relay ERV-09Document1 paginăTimer Relay ERV-09wal idÎncă nu există evaluări

- Coca ColaDocument50 paginiCoca Colamariyha PalangganaÎncă nu există evaluări

- Orifice Assembly With D-D2 Taps PDFDocument1 paginăOrifice Assembly With D-D2 Taps PDFArup MondalÎncă nu există evaluări

- Afectiuni Si SimptomeDocument22 paginiAfectiuni Si SimptomeIOANA_ROX_DRÎncă nu există evaluări

- General Anaesthesia MCQsDocument5 paginiGeneral Anaesthesia MCQsWasi Khan100% (3)

- 5 Years High and Low PointsDocument7 pagini5 Years High and Low PointsNaresh Kumar VishwakarmaÎncă nu există evaluări

- Class 28: Outline: Hour 1: Displacement Current Maxwell's Equations Hour 2: Electromagnetic WavesDocument33 paginiClass 28: Outline: Hour 1: Displacement Current Maxwell's Equations Hour 2: Electromagnetic Wavesakirank1Încă nu există evaluări

- Present Arlypon VPCDocument1 paginăPresent Arlypon VPCErcan Ateş100% (1)

- Estimation of Fire Loads For An Educational Building - A Case StudyDocument4 paginiEstimation of Fire Loads For An Educational Building - A Case StudyEditor IJSETÎncă nu există evaluări

- KZPOWER Perkins Stamford Genset Range CatalogueDocument2 paginiKZPOWER Perkins Stamford Genset Range CatalogueWiratama TambunanÎncă nu există evaluări

- Civil Engineering Topics V4Document409 paginiCivil Engineering Topics V4Ioannis MitsisÎncă nu există evaluări

- Tim Ingold - From The Transmission of Representations To The Education of Attention PDFDocument26 paginiTim Ingold - From The Transmission of Representations To The Education of Attention PDFtomasfeza5210100% (1)

- Disa Match: A Match You Can Count OnDocument8 paginiDisa Match: A Match You Can Count OngÎncă nu există evaluări

- Dinacharya HandbookDocument5 paginiDinacharya Handbookvera sirakovaÎncă nu există evaluări

- Technical Methods and Requirements For Gas Meter CalibrationDocument8 paginiTechnical Methods and Requirements For Gas Meter CalibrationIrfan RazaÎncă nu există evaluări

- Magneto-Convective Non-Newtonian Nanofluid With Momentum and Temperature Dependent Slip Flow From A Permeable Stretching Sheet With Porous Medium and Chemical ReactionDocument18 paginiMagneto-Convective Non-Newtonian Nanofluid With Momentum and Temperature Dependent Slip Flow From A Permeable Stretching Sheet With Porous Medium and Chemical ReactionIOSRjournalÎncă nu există evaluări

- TOP233YDocument24 paginiTOP233YJose BenavidesÎncă nu există evaluări