Documente Academic

Documente Profesional

Documente Cultură

hw6 Circuits

Încărcat de

ayylmao kekTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

hw6 Circuits

Încărcat de

ayylmao kekDrepturi de autor:

Formate disponibile

Brock Wilcox

CS470

Homework 6

2012.04.12

1.Exercises 5.2.1 through 5.2.4, parts a and b

"In this exercise we look at memory locality properties of matrix computation. The following code is written in C,

where elements within the same row are stored contiguously."

Assume that the elements of both the arrays A and B contain single-precision floating-point values, declared with

the codes below:

a.

float A[4000][4000], B[8][8];

for (int I=0; I<4000; I++)

for (int J=0; J<8; J++)

A[I][J] = B[J][0] + A[I][J];

b.

float A[4000][4000], B[8][8];

for (int J=0; J<8; J++)

for (int I=0; I<4000; I++)

A[I][J] = B[J][0] + A[I][J];

Hint: Note that these codes differ slightly from those provided in the textbook exercise.

5.2.1 How many single-precision floating-point values can be stored in a 16-byte cache line? Show your work!

Single floats are 32-bits each, which is 4 bytes (8 bits each). So each float takes 4 bytes,

meaning we can fit 4 floats into the cacheline (4 * 4).

5.2.1.EXTRA.A How many cachelines total would the array A need, if it could be stored completely in cache? Show

your work!

A is 4000 * 4000 = 16,000,000 floats. We divide by 4 floats per cacheline, 16,000,000/4 =

4,000,000 cachelines.

5.2.1.EXTRA.B Since not all of the elements of A are used in the codes above, how many cachelines would the

required elements of the array A actually need, if they could be stored completely in cache? Show your work!

For (a) and (b) we use up to A[4000][8] (well, 1 less counting from zero). So that is 4000 * 8

= 32000 floats, which is 32000 / 4 = 8000 cachelines.

5.2.1.EXTRA.C How many cachelines would the array B require, if it could be stored completely in cache? Show

your work!

B is 8 * 8 = 64 floats. Since we have 4 floats per cacheline, that is 64 / 4 = 16 cachelines.

5.2.1.EXTRA.D Since not all of the elements of B are used in the codes above, how many cachelines would the

required elements of the array B actually need, if they could be stored completely in cache? Show your work!

In both (a) and (b) we use J[0..7][0], which means we are using 8 * 1 = 8 floats. 8 floats / 4

per cacheline = 2 cachelines needed.

5.2.2 References to which variables exhibit temporal locality? Why?

In (a) and (b) the indexes i and j use temporal locality, since they are accessed over and

over again. (these would most likely be stored in a register).

In (b), B[J][0] has temporal locality, since it is accessed over and over (4000 times in a row)

5.2.3 References to which variables exhibit spatial locality? Why?

In (a), A[I][J] has spacial locality. As J is incremented, nearby values of the array are

accessed.

5.2.4 (Using the code provided for exercises 5.2.1 through 5.2.3 above)

How many 16-byte cachelines are needed to store all 32-bit matrix elements being referenced -- as the code

executes? Show your work!

For this question only, assume that only one cacheline from the array A and only one cacheline from the

array B can be in the cache at the same time.

Hint: There will be a difference between the two sets of codes, as one of the codes will use all four floats in a

cacheline from one of the two arrays consecutively and the other code will not.

Note that only the first 8 elements of each row in A are used and only the first element of each of the eight

rows of B is used.

For (a), we need 2 cachelines to hold a whole row of A, which is 4 floats per cacheline.

For (b) we need a cacheline for each separate row of B, so 8 cachelines.

5.2.4.EXTRA.E

Since fetching values from memory (to put into the cache) is far more expensive than fetching values directly from

the cache, which of the two codes above is more efficient? Why?

The first is significantly better. It is able to fetch consecutive locations, whereas (b), as an

even multiple of 2, will keep having cache misses.

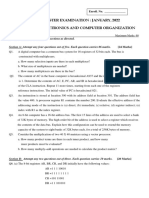

2.Exercise 5.3.1, using the list of references printed in red below:

"Caches are important to providing a high performance memory hierarchy to processors. Below is a list of 32-bit

memory address references, given as word addresses.

5, 215, 174, 7, 82, 215, 66, 175, 65, 104, 87, 214, 5

5.3.1 "For each of these references,

a) identify the binary address,

b) identify the tag, and

c) identify the index given a direct-mapped cache with 16 one-word blocks.

d) Also list if each reference is a hit or a miss, assuming the cache is initially empty."

Word addresses mean a block size of 4-bytes to hold the word. Since we have 16 one-word

blocks, we need 4 bits for the index (though since we are word-aligned we could in theory

ignore the 2 low bits). So the tag needs to be 32 4 = 28 bits, from the high end of the

address.

Reference

Address

Tag

Index

hit/miss

101

101 miss

215

11000000

1101

111 miss

174

10000000

1010

1110 miss

111

111 miss

82

1010010

101

10 miss

215

11000000

1101

66

1000010

100

10 miss

175

10000000

1010

1111 miss

65

1000001

100

1 miss

104

1101000

110

1000 miss

87

1010111

101

111 miss

214

11000000

1101

110 miss

101

101 miss

111 hit

3.Exercise 5.3.4

"There are many different design parameters that are important to a cache's overall performance. The table below

lists parameters for different ONE direct-mapped cache designs."

Cache data size Cache block size Cache access time

64 KB

2 words

2 cycle

5.3.4 "Calculate the total number of bits required for the cache listed in the table, assuming a 32-bit address. Given

that total size, find the total size of the closest direct-mapped cache with 16-word blocks of equal size or greater.

Explain why the second cache, despite its larger data size, might provide slower performance than the first cache."

Hint: Compute n and m first. See Section 5.2.

2^6 = 64, so n = 6. 2 words = 2^m = 2^1, so m=1.

So we get 2^n*(2^m*32+(32-n-m-2)+1)=5632 bits.

4.Exercises 5.4.1 and 5.4.2, parts a and b

"For a direct-mapped cache design with 32-bit address, the following bits of the address are used to access the

cache."

Tag Index Offset

a. 31-10 9-4

3-0

b. 31-12 11-5

4-0

5.4.1 "What is the cache line size (in words)?"

(a) Tag is 22 bits, index is 6 bits (n), offset is 4 bits. So we have 22 = 32 (n + m + 2) = 32

(8 +m), and so m = 32 22 8 = 2. So the cache line size is 2^2 = 4 words.

(b) Tag is 20 bits, index is 7 bits (n), offset is 5 bits. So we have 20 = 32 (n + m + 2) = 32

(7 + m + 2), so 32 20 9 = m = 3. So the cache line size is 2^3 = 8 words.

5.4.2 "How many entries does the cache have?"

This can be determined from the index. In (a) the index is 6 bits, so the cache is 2^6 = 64

blocks. In (b) the index is 7 bits, so the cache is 2^7 = 128 blocks.

5.Exercises 5.4.4 and 5.4.5

"Starting from power on, the following byte-addressed cache references are recorded." (12 references)

Address 0 4 16 132 232 160 1024 30 140 3100 180 2180

Hint: You may assume that m=2 and n = 6.

5.4.4 "How many blocks are replaced?"

Hint: First fill out the table below:

tag is 24 bits (bits 31-8), index is 6 bits (bits 7-2).

Address

Line ID

Hit/Miss

Replace?

1024

16

132 232 160

30

4

10000

1000 1000 1110 1010

1111

100

00000

0

0100 1000 0000

0

0

0

0 2

16

29 20

0 3

M M

M

M

M

M

M

M

N N

N

N

N

N

Y

N

0

3100

140

180

2180

11000

1000

10110 100010

00111

1100

100

000100

00

17

3

22

16

M

M

M

M

N

Y

N

Y

5.4.5 "What is the hit ratio?"

The hit ratio is 0/12 = 0

6.Exercise 5.5.2, using values from table below:

"Recall that we have two write policies and write allocation policies, their combinations can be implemented at either

in L1 or L2 cache.

L1

L2

Write-back, write allocate Write-through, non-write allocate

5.5.2 "Describe the procedure of handling an L1 write miss, considering the component involved and the possibility

of replacing a dirty block."

First we'd check to see if the block is dirty. If it is, then we write the dirty block to memory. Next

we retrieve the target block from memory (overwriting the block that is in our way). Finally we

write to our L1 block. Later, when something else must read in a different memory location

overwriting our block, the block is written.

S-ar putea să vă placă și

- Evolutionary Algorithms for Mobile Ad Hoc NetworksDe la EverandEvolutionary Algorithms for Mobile Ad Hoc NetworksÎncă nu există evaluări

- Co QSTN BankDocument4 paginiCo QSTN Bankjoydeep12Încă nu există evaluări

- CRC of BCA (2) Assignment (Revised Syllabus)Document17 paginiCRC of BCA (2) Assignment (Revised Syllabus)BshrinivasÎncă nu există evaluări

- r05321405 Computer OrganizationDocument6 paginir05321405 Computer OrganizationSRINIVASA RAO GANTAÎncă nu există evaluări

- UWA Department of Electrical and Electronic Engineering Computer Architecture 219 (Tutorial 8Document8 paginiUWA Department of Electrical and Electronic Engineering Computer Architecture 219 (Tutorial 8Kai Ming ChowÎncă nu există evaluări

- IT209 - Computer Organisation - PART 1Document8 paginiIT209 - Computer Organisation - PART 1Jill chaudharyÎncă nu există evaluări

- R07 Set No. 2Document7 paginiR07 Set No. 2Mothilal KaramtothuÎncă nu există evaluări

- Model Answers HW3Document5 paginiModel Answers HW3John100% (1)

- Ec2203 Digital Electronics r8Document3 paginiEc2203 Digital Electronics r8jenifar777Încă nu există evaluări

- GATE QnADocument5 paginiGATE QnAGaurav MoreÎncă nu există evaluări

- Assignment 3Document9 paginiAssignment 3Muhammad UmairÎncă nu există evaluări

- Problem Set 2Document4 paginiProblem Set 2bijan shresthaÎncă nu există evaluări

- Cs 60Document80 paginiCs 60Sirsendu RoyÎncă nu există evaluări

- 07a80305 ComputerorganizationandarchitectureDocument8 pagini07a80305 ComputerorganizationandarchitectureSharanya ThirichinapalliÎncă nu există evaluări

- CS152 Quiz #2: Name: - This Is A Closed Book, Closed Notes Exam. 80 Minutes 9 PagesDocument13 paginiCS152 Quiz #2: Name: - This Is A Closed Book, Closed Notes Exam. 80 Minutes 9 Pagesshri3415Încă nu există evaluări

- Computer Organisation PYQ 2010 TO 2022 3RD SEM CSE ITDocument52 paginiComputer Organisation PYQ 2010 TO 2022 3RD SEM CSE ITKAJI AZAD ALIÎncă nu există evaluări

- Princes Nourah University Cs323-Computer Architecture 1 Semester/ 1435Document6 paginiPrinces Nourah University Cs323-Computer Architecture 1 Semester/ 1435Urwa NaveedÎncă nu există evaluări

- Solutions To Set 8Document18 paginiSolutions To Set 8kitana_sectÎncă nu există evaluări

- Exam1 f12Document15 paginiExam1 f12Ryan DavisÎncă nu există evaluări

- HW5TCMTDocument4 paginiHW5TCMTThanh TrúcÎncă nu există evaluări

- MidtermsolutionsDocument3 paginiMidtermsolutionsRajini GuttiÎncă nu există evaluări

- Digital Electronics & Fundamentals of Microprocessor: B.E. (Information Technology) Third Semester (C.B.S.)Document2 paginiDigital Electronics & Fundamentals of Microprocessor: B.E. (Information Technology) Third Semester (C.B.S.)Hamit BisaneÎncă nu există evaluări

- MCS 012Document5 paginiMCS 012S.M. FarhanÎncă nu există evaluări

- 07A5EC07 COMPUTERORGANIZATIONfrDocument4 pagini07A5EC07 COMPUTERORGANIZATIONfrAnvesh KurapatiÎncă nu există evaluări

- DDCO UPDATED QUESTION BANKttttDocument4 paginiDDCO UPDATED QUESTION BANKttttbrahmareddy.22iseÎncă nu există evaluări

- Previous PapersDocument7 paginiPrevious Paperssureshkumar_kotipalliÎncă nu există evaluări

- COA LAB Assignment CombinedDocument57 paginiCOA LAB Assignment Combinedvarun sahaniÎncă nu există evaluări

- rr320504 Language ProcessorsDocument8 paginirr320504 Language ProcessorsSRINIVASA RAO GANTAÎncă nu există evaluări

- End Semester Examination: January, 2022 Digital Electronics and Computer OrganizationDocument3 paginiEnd Semester Examination: January, 2022 Digital Electronics and Computer OrganizationFFFÎncă nu există evaluări

- 3330 MergedDocument8 pagini3330 MergedHamit BisaneÎncă nu există evaluări

- 2ec601-Ca-See May 2021Document2 pagini2ec601-Ca-See May 2021Ritik GargÎncă nu există evaluări

- CT 801 / CSE802 - Compiler ConstructionDocument12 paginiCT 801 / CSE802 - Compiler ConstructionSumit PaulÎncă nu există evaluări

- Computer Organization and Design (CSE-201) (Makeup)Document2 paginiComputer Organization and Design (CSE-201) (Makeup)damoy28211Încă nu există evaluări

- Computer Architecture Final Exam ReviewDocument10 paginiComputer Architecture Final Exam Reviewkhayat_samirÎncă nu există evaluări

- CS 2006 (Coa) - CS - End - May - 2023Document14 paginiCS 2006 (Coa) - CS - End - May - 2023223UTKARSH TRIVEDIÎncă nu există evaluări

- CS 433 Homework 4: Problem 1 (7 Points)Document14 paginiCS 433 Homework 4: Problem 1 (7 Points)FgfughuÎncă nu există evaluări

- bt31R07 P1 10 11 2009rahulDocument31 paginibt31R07 P1 10 11 2009rahulashok1261Încă nu există evaluări

- Department of EceDocument8 paginiDepartment of Ecerajendr_46Încă nu există evaluări

- Cache Memory ProblemsDocument3 paginiCache Memory Problemsa100% (1)

- Gtu Computer 3130704 Summer 2023Document2 paginiGtu Computer 3130704 Summer 2023madhavjani06Încă nu există evaluări

- Pdfjoiner PDFDocument26 paginiPdfjoiner PDFbakosey323Încă nu există evaluări

- FALLSEM2019-20 CSE2001 TH VL2019201007433 Reference Material I 18-Sep-2019 DA-2Document2 paginiFALLSEM2019-20 CSE2001 TH VL2019201007433 Reference Material I 18-Sep-2019 DA-2Sachin KharelÎncă nu există evaluări

- FALLSEM2019-20 CSE2001 TH VL2019201007433 Reference Material I 18-Sep-2019 DA-2 PDFDocument2 paginiFALLSEM2019-20 CSE2001 TH VL2019201007433 Reference Material I 18-Sep-2019 DA-2 PDFSubarna Lamsal0% (1)

- Practice Questions To Set 8Document8 paginiPractice Questions To Set 8NiravÎncă nu există evaluări

- Analyzing memory cache performance and design parametersDocument2 paginiAnalyzing memory cache performance and design parametersĐức TàiÎncă nu există evaluări

- NR Code No: NR-12/MCA MCA-I Semester Supplementary Examinations, July/Aug 2008. Computer Organization Time: 3hours Max. Marks: 60 Answer Any FIVE Questions All Questions Carry Equal MarksDocument3 paginiNR Code No: NR-12/MCA MCA-I Semester Supplementary Examinations, July/Aug 2008. Computer Organization Time: 3hours Max. Marks: 60 Answer Any FIVE Questions All Questions Carry Equal MarksvirusyadavÎncă nu există evaluări

- Not An Exam PaperDocument5 paginiNot An Exam PaperJill chaudharyÎncă nu există evaluări

- HMK 4 ARCDocument3 paginiHMK 4 ARCskeletorfearsmeÎncă nu există evaluări

- ADS (CSS) Final Question Bank Format For (III-I)Document3 paginiADS (CSS) Final Question Bank Format For (III-I)sravaniÎncă nu există evaluări

- Log Log 64 6: ThelineDocument5 paginiLog Log 64 6: ThelineBantos BenÎncă nu există evaluări

- 9A05406 Computer OrganizationDocument4 pagini9A05406 Computer OrganizationsivabharathamurthyÎncă nu există evaluări

- 2019-20 Supple CoaDocument2 pagini2019-20 Supple Coanaveenk1999nk99Încă nu există evaluări

- CDA 3103 HomeworkDocument7 paginiCDA 3103 HomeworkAdam DementovÎncă nu există evaluări

- GTU Data Structures Exam QuestionsDocument2 paginiGTU Data Structures Exam Questionsnikita gohelÎncă nu există evaluări

- r05221901 Computer IonDocument6 paginir05221901 Computer IonSRINIVASA RAO GANTAÎncă nu există evaluări

- Computer Architecture & Organization: B.E. (Computer Science & Engineering) (New) Third Semester (C.B.S.)Document2 paginiComputer Architecture & Organization: B.E. (Computer Science & Engineering) (New) Third Semester (C.B.S.)Chinmay MokhareÎncă nu există evaluări

- TE 2003&2008 PatternDocument623 paginiTE 2003&2008 PatternAshashwatmeÎncă nu există evaluări

- Exam 1 Review: Cache Performance Calculations and Address MappingDocument6 paginiExam 1 Review: Cache Performance Calculations and Address MappingErz SeÎncă nu există evaluări

- Chapter 4 - Tutorial3Document6 paginiChapter 4 - Tutorial3Erwan Christo Shui 廖Încă nu există evaluări

- Understanding the MIPS Processor PipelineDocument149 paginiUnderstanding the MIPS Processor Pipelineayylmao kekÎncă nu există evaluări

- Summary Exam 2015Document30 paginiSummary Exam 2015ayylmao kekÎncă nu există evaluări

- UFID Exam 2 STA 4321Document5 paginiUFID Exam 2 STA 4321ayylmao kekÎncă nu există evaluări

- UFID Exam 2 STA 4321Document5 paginiUFID Exam 2 STA 4321ayylmao kekÎncă nu există evaluări

- SPRING 2015 CDA 3101 Homework 3: Date-Assigned: Mar 27th, 2015 Due Dates: 11:55pm, April 7th, 2015Document5 paginiSPRING 2015 CDA 3101 Homework 3: Date-Assigned: Mar 27th, 2015 Due Dates: 11:55pm, April 7th, 2015ayylmao kekÎncă nu există evaluări

- CAQA5e ch4Document57 paginiCAQA5e ch4xxxxxxÎncă nu există evaluări

- Copyofdnd5enBT Exam PracticeDocument257 paginiCopyofdnd5enBT Exam Practiceayylmao kekÎncă nu există evaluări

- hw1 ComputerDocument1 paginăhw1 Computerayylmao kekÎncă nu există evaluări

- Credit Card Fraud Detection Using Hidden Markov Model: AbstractDocument53 paginiCredit Card Fraud Detection Using Hidden Markov Model: AbstractNyaga Wa MaragwaÎncă nu există evaluări

- Online Examination Hall Seating ArrangementDocument5 paginiOnline Examination Hall Seating ArrangementIJRASETPublicationsÎncă nu există evaluări

- Tatarchuk GDC 2015 Destiny Renderer WebDocument232 paginiTatarchuk GDC 2015 Destiny Renderer WebRuben Dario Cabrera GarciaÎncă nu există evaluări

- CA Solution 2068 PDFDocument13 paginiCA Solution 2068 PDFBishal ShahiÎncă nu există evaluări

- FrenchDocument9 paginiFrenchYouness El FaquirÎncă nu există evaluări

- SAP ASE System Administration Guide Volume 2 en PDFDocument480 paginiSAP ASE System Administration Guide Volume 2 en PDFSANTOSH TRIPATHIÎncă nu există evaluări

- 1649 GCS200888 Vo Nguyen Duy Nam Assignment1 PDFDocument22 pagini1649 GCS200888 Vo Nguyen Duy Nam Assignment1 PDFDuy Nam Võ NguyễnÎncă nu există evaluări

- The Definitive Guide To Jprofiler: All You Need To Know As A Performance ProfessionalDocument219 paginiThe Definitive Guide To Jprofiler: All You Need To Know As A Performance ProfessionalnandakarsanÎncă nu există evaluări

- 300 Embedded Programming Problems by Yashwanth Naidu TDocument85 pagini300 Embedded Programming Problems by Yashwanth Naidu TSai Krishna K VÎncă nu există evaluări

- Memory Allocation in C: Segments SegmentsDocument24 paginiMemory Allocation in C: Segments SegmentsSharaf AroniÎncă nu există evaluări

- ORA-04031 in Shared Pool Due To Workload or SGA Configuration and Tuning Issue (Doc ID 2647234.1)Document2 paginiORA-04031 in Shared Pool Due To Workload or SGA Configuration and Tuning Issue (Doc ID 2647234.1)Nawab ShariefÎncă nu există evaluări

- Problems On Multilevel Paging PDFDocument6 paginiProblems On Multilevel Paging PDFYash Saitwal100% (1)

- Memory Management With BitmapsDocument37 paginiMemory Management With Bitmapssuneerav17Încă nu există evaluări

- CODch 7 SlidesDocument49 paginiCODch 7 SlidesMohamed SherifÎncă nu există evaluări

- Techno-Commercial IOT Lab Setup Version 3 3 SEPTEMBER - 25-2019Document31 paginiTechno-Commercial IOT Lab Setup Version 3 3 SEPTEMBER - 25-2019Rajesh LalwaniÎncă nu există evaluări

- Tech Note 732 - Wonderware Memory Manager Configuration Best PracticesDocument8 paginiTech Note 732 - Wonderware Memory Manager Configuration Best Practices계수나무Încă nu există evaluări

- 10.question Bank With AnswersDocument156 pagini10.question Bank With Answersnirav_modhÎncă nu există evaluări

- Wipro Placement Paper PatterDocument37 paginiWipro Placement Paper PatterGokul SridharÎncă nu există evaluări

- OopsDocument82 paginiOopsAdarsh SmgÎncă nu există evaluări

- MXFTK enDocument298 paginiMXFTK enaacidskÎncă nu există evaluări

- Ôn tập hệ điều hành - câu hỏi trắc nghiệm và bài tậpDocument7 paginiÔn tập hệ điều hành - câu hỏi trắc nghiệm và bài tậpJohn DangÎncă nu există evaluări

- OS OutlineDocument4 paginiOS OutlineBelmarkÎncă nu există evaluări

- Fundamentals of Operating Systems Memory ManagementDocument25 paginiFundamentals of Operating Systems Memory ManagementpathakpranavÎncă nu există evaluări

- Lecture 3 - DMADocument25 paginiLecture 3 - DMASaim Janjua0% (1)

- T24 Oracle Operations and File MaintenanceDocument10 paginiT24 Oracle Operations and File MaintenancetiemnvÎncă nu există evaluări

- How YAFFS Works: Understanding the Core Mechanisms of the YAFFS Flash File SystemDocument25 paginiHow YAFFS Works: Understanding the Core Mechanisms of the YAFFS Flash File SystemeemkutayÎncă nu există evaluări

- Oracle® E-Business Suite: Mobile Apps Administrator's Guide Release 12.1 and 12.2Document230 paginiOracle® E-Business Suite: Mobile Apps Administrator's Guide Release 12.1 and 12.2Utsav ThakkarÎncă nu există evaluări

- Memory Hierarchy Technology: I I I IDocument22 paginiMemory Hierarchy Technology: I I I Imanu12041990Încă nu există evaluări

- Operating System and ConceptsDocument109 paginiOperating System and ConceptsNipunÎncă nu există evaluări

- SP Merged SlidesDocument242 paginiSP Merged SlidesBentojaÎncă nu există evaluări