Documente Academic

Documente Profesional

Documente Cultură

Design of RISC-Based Processor On FPGA: CENG450: C S A - P

Încărcat de

Ibrahim HejabTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Design of RISC-Based Processor On FPGA: CENG450: C S A - P

Încărcat de

Ibrahim HejabDrepturi de autor:

Formate disponibile

CENG450: COMPUTER SYSTEMS AND ARCHITECTURE - PROJECT REPORT

Design of RISC-Based Processor on FPGA

Prepared For :

CENG450 Lab, April, 2015

Prepared By:

Ibrahim Hazmi (V00835716,

ihaz@uvic.ca

) and

Nick Houghton (V00151783,

nhoughto@uvic.ca

)

Course Instructor: Dr. Amirali Baniasadi (

amiralib@ece.uvic.ca

)

Lab Instructor:

Babak Keshavarz (

babak@ece.uvic.ca

)

CENG450_Project_Report

RISCBasedProcessoronFPGA

CONTENTS

Contents

List of Figures

List of Tables

Introduction

Objective

Design Requirement

Project Outline

System Design

The DataPath

The Control Unit

Detailed Description of the Design

A-Format

B-Format:

L-Format:

Simulation Results

Test Program 1

Test Program 2

Analysis and Discussion

A-Format

B-Format

L-Format

Processor I/O and Hardware Implementation

Conclusion

Appendix (Tables)

FSM Control States (VHDL)

FSM Control Signals

Instruction Set

Program Test 1

Program Test 2

Reference

iHaz & nHoughton 2015

2 out of 31

CENG450_Project_Report

RISCBasedProcessoronFPGA

LIST OF FIGURES

Fig.1 Block Diagram of the Processor Datapath

Fig.2 Register File Block Diagram

Fig.3 ALU Block Diagram

Fig.4 FSM Control

Fig.5 The Actual Pipeline 5-Stages

Fig.7 A-Format Instructions

Fig.8 A-Format Datapath

Fig.9 B-Format Instructions

Fig.10 B-Format Datapath

Fig.11 L-Format Instructions

Fig.12 L-Format Datapath

Fig.13 Flow-Chart of Test Program1

Fig.14 PC3-10: 30,FF & 34,0C (LOADIMM)

Fig.15 PC15-17: 51 (SUB) & 34,0C (LOADIMM)

Fig.16 PC22-27: D6 (MOV) & B8 (IN)

Fig.17 PC32-34: 28,70 (STORE) & 49 (ADD)

Fig.18 PC39-44: 88 (NAND) & C8 (OUT 3C)

Fig.19 PC45-51: 10,70 (LOAD) & 70 (SHR)

Fig.20 PC56-61: 48 (ADD) & C8 (OUT 9C)

Fig.21 Overall Simulation of Test1

Fig.22 Flow-Chart of Test Program2

Fig.23 1st Loop: 1st ADD

Fig.24 2nd Loop: 2nd ADD

Fig.25 3rd Loop: 3rd ADD

Fig.26 4th Loop: 4th ADD

Fig.27 5th Loop: 1st NAND

Fig.28 6th Loop: 2nd NAND

Fig.29 7th Loop: 3rd NAND

Fig.30 8th Loop: 4th NAND

Fig.31 9th Loop: Start Again

Fig.32 A-Format Simulation Example ( 49: ADD r2, r1)

Fig.32 B-Format Simulation Example ( 96: BR r2)

Fig.33 L-Format Simulation Example ( 34,0C: LOADIMM r1, 0C)

Fig.34 Test Program 2 running on Spartan FPGA

iHaz & nHoughton 2015

3 out of 31

CENG450_Project_Report

RISCBasedProcessoronFPGA

LIST OF TABLES

Table 1: FSM Control States

Table 2: Control FSM Signals

Table 3: Instruction Set

Table 4: Program TEST 1

Table 6: Program TEST 2

iHaz & nHoughton 2015

4 out of 31

CENG450_Project_Report

RISCBasedProcessoronFPGA

INTRODUCTION

OBJECTIVE

To design and implement a pipelined processor on FPGA using Xilinx (Spartan3E). We

have used a RISC-like instruction set in the project. Instructions are 1-byte or 2-bytes

depending on the type of instructions. There are four 1-byte general purpose registers;

R0, R1, R2, and R3. For both RAM and ROM, the memory address space is 256 bytes

and is byte addressable. PC is the program counter that points to the next instruction to

be executed. For call subroutine instruction (BR.SUB) a special register, link register

(LR), holds the address of instruction after BR.SUB.

DESIGN REQUIREMENT

There are 3 different instruction formats:

1) A-Format: Arithmetic instructions, which affect zero flag (Z) and negative flag (N).

2) B-Format: Branch instructions. (op-code, brx -to determines type of branch -, and rb).

3) L-Format: Load/store instructions (Two bytes: op-code and ra, and memory address

or immediate value.

PROJECT OUTLINE

This rest of the report is organized as the following:

System Design, where the overall design is presented showing the block diagram of

the datapath and the finite state machine of the control unit.

Detailed Description of the Design, where every format is discussed in details with

specific illustrations and examples (data flow, state diagrams, and simulation

examples)

Simulation Results of two test programs, where the test code is stored in ROM.

Analysis and Discussion, where the simulation results are discussed and the test

codes are shown to be satisfied in simulation and hardware

Conclusion

iHaz & nHoughton 2015

5 out of 31

CENG450_Project_Report

RISCBasedProcessoronFPGA

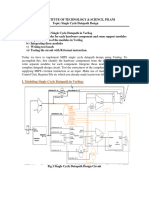

SYSTEM DESIGN

The overall design of the processor is presented in this section showing the block

diagram of the datapath and demonstrating the finite state machine of the control unit.

The instruction set architecture (ISA) of our mini processor is RISC-like and instructions

are 1-byte or 2-bytes depending on the type of instructions. (

Fig.1

) illustrates the actual

datapath of our processor including the control unit and the following subsections will

give more details about these two main components, i.e., the datapath and control units.

THE DATAPATH

Fig.1 Block Diagram of the Processor Datapath

The datapath of our design consists of the following:

iHaz & nHoughton 2015

6 out of 31

CENG450_Project_Report

RISCBasedProcessoronFPGA

REGISTER FILE (RF):

There are four 1-byte general purpose registers; R0, R1, R2, and R3. It is capable of

reading two registers and/or writing one in a single cycle. The target register addresses

are read through lines rd_index1 and rd_index2, the results of the read appear at the

output lines rd_data1 and rd_data2 asynchronously. The data to be written and its

desired location arrive at wr_data and wr_index respectively. The controller activates

wr_en asynchronously however the write will not perform until a positive clock edge is

reached.

Fig.2 Register File Block Diagram

ALU:

The arithmetic logic unit (ALU) performs the basic computation for the system. The unit

receives two byte-length data inputs on input busses in1 and in2. The controller unit

determines the desired operation from the instruction opcode and places a command

code on the alu-mode bus to decree the required operation. The result of the

computations appear on the result bus asynchronously. The z-flag and n-flag signify to

the control unit any instance of a zero or negative result synchronously. Please refer to

table 9 in the appendices for a complete list of instruction description.

Fig.3 ALU Block Diagram

iHaz & nHoughton 2015

7 out of 31

CENG450_Project_Report

RISCBasedProcessoronFPGA

INSTRUCTION MEMORY (ROM):

ROM, the memory address space is 256 bytes and is byte addressable. The ROM is

pre-loaded with the desired test program during FPGA implementation.

DATA MEMORY (RAM):

The RAM is a 256-byte data cache. Input is from either the external input for immediate

store instructions, directly from the register file for load addresses or results from the

ALU. The required datapath is selected by the control unit.

ADDRESS CALCULATION UNIT (ACU):

This unit is responsible for the decision of what the next instruction executed will be. It

includes a program counter register (PC)) which acts as the address input to the

instruction memory (ROM). It also includes the link register (LR) which holds the address

of instruction after BR.SUB. Furthermore, a simple incrementer and two multiplexers are

the complementary components of (ACU) as shown on the left side of (

Fig.1

).

CONTROL BLOCK (CB):

This unit is responsible for the selection and activation of the datapath required for each

instruction. It contains two 8-bit registers, one for instructions called the Instruction

Register (IR) and another for any immediate values contained in instructions (IMR). Every

instruction is placed in the instruction register, the opcode is analyzed and the finite

state machine nature of the component alters the outputs for datapath selection. It is

responsible for branch execution based on analysis from the ALU, deactivation of the

incrementalization of the program counter and the control of system I/O.

THE CONTROL UNIT

In the heart of our control block is the finite state machine (

FSM

), that presents all the

five stages of the processor pipeline and controls all the instructions and data flow in the

system. Most of the instructions, especially arithmetic ones, go through these five

stages in order to be executed, whereas some of them, such as branches do not need

to go through all of the stages. The state diagram in (

Fig.4

) demonstrates the flow of our

(

FSM

). Please refer to table 3 in the appendices for the signal map.

iHaz & nHoughton 2015

8 out of 31

CENG450_Project_Report

RISCBasedProcessoronFPGA

Fig.4 FSM Control

Although the number of states in our (FSM) is more than five, it acts exactly like the

pipeline in (

Fig.5

) which consists of the main five stages: Instruction Fetch (IF), Decode

(ID), Execute (ALU), Memory Access (MEM). The examples in the next section will clarify

this.

Fig.5 The Actual Pipeline 5-Stages

(

Table 1

) in the appendices shows how our FSM look like in VHDL code. Whereas

(

Table 2

) presents the actual flow of the control signals in the FSM controller.

iHaz & nHoughton 2015

9 out of 31

CENG450_Project_Report

RISCBasedProcessoronFPGA

DETAILED DESCRIPTION OF THE DESIGN

After showing the system design with some details about the design of each individual

module in architecture, it is time to see how the system works in each format. in this

section, every format will be discussed in details with specific illustrations and examples.

A-FORMAT

These instructions are 1-byte and considered as the Arithmetic Instructions. Op-code

is the high order nibble and the low order four bits determines the two registers. (

Fig.7

)

represents A-format instructions, while the op-code values for A-format instructions and

the explanation of their functionality are shown in (

Table 3

) in the Appendix.

7

4

Op-Code

Ra

0

Rb

Fig.7 A-Format Instructions

Arithmetic instructions affect zero flag (Z_Flag) and negative flag (N_Flag). Our processor

has 1-byte input port and 1-byte output port. These ports are connected to the external

pins.

IN

and

OUT

instructions transfer values between processor ports and internal

registers.

In this project, the data involved in

IN

or

MOV

instructions go through (ALU) block in the

execution cycle with ALU_Mode equals 000, i.e., doing nothing, whereas the

OUT

Port

is connected directly to (Ra) in case of

OUT

instruction. (

Fig.8

) in the following page

shows the possible data flow when executing an A-format instruction:

iHaz & nHoughton 2015

10 out of 31

CENG450_Project_Report

RISCBasedProcessoronFPGA

Fig.8 A-Format Datapath

B-FORMAT:

B-format instructions are 1-byte and used for branch instructions. As (

Fig.9

) shows,

B-format instructions have op-code, brx, and rb. Brx filed determines type of branch

instruction.

7

4

Op-Code

Ra

0

Rb

Fig.9 B-Format Instructions

(

Table 3

) in the Appendix shows the details of b-format instructions.

iHaz & nHoughton 2015

11 out of 31

CENG450_Project_Report

RISCBasedProcessoronFPGA

The branch instructions contain register labels which points to the target ROM address

for the jump. Upon receipt of a branch the controller enables a read of the addresses

from the register file and enables the br_sel line. The received address is loaded into the

PC. (Fig.10) shows the possible data flow when executing an B-format instruction:

Fig.10 B-Format Datapath

BR instruction jumps into destination address determined by rb fields. BR.Z and BR.N

are conditional branches. If Z/N flag is one, it jumps into destination address determined

by rb. BR.SUB is used for a subroutine call. It saves the address of the next instruction

in the LR and jumps into the address indexed by register file (rb). At the end of the

subroutine, a RETURN instruction writes the value stored in LR into the PC.

iHaz & nHoughton 2015

12 out of 31

CENG450_Project_Report

RISCBasedProcessoronFPGA

L-FORMAT:

L-format instructions are two bytes and are used for load/store instructions. The first

byte holds op-code and ra and the second byte holds address of memory or an

immediate value. (

Fig.11

) shows L-format instructions, while (

Table 3

) in the Appendix

shows details of L-format instructions. M[ea] represents the content of memory with

address ea. Note that in L-format instructions, the least significant two bits of the first

byte are unused.

7

4

Op-Code

Ra

Effective Address / Immediate Value

Fig.11 L-Format Instructions

LOAD instructions reads from address ea and write into register Ra. STORE instruction

reads register ra and writes it into address ea. LOADIMM writes a constant value (imm)

into register ra. (

Fig.12

) shows the possible data flow of L-format instructions:

Fig.12 L-Format Datapath

iHaz & nHoughton 2015

13 out of 31

CENG450_Project_Report

RISCBasedProcessoronFPGA

SIMULATION RESULTS

TEST PROGRAM 1

Two test programs are examined, and the test code is stored in ROM. (

Fig.13

) gives a

clear step by step operation of the intended execution of test program 1.

Fig.13 Flow-Chart of Test Program1

Figures 14-21

show the simulated results of the execution of the program on the

system. The first segment of the program is the execution of two L-format LOADIMM

instructions to load values 0xFF and 0x0C into registers R0 and R1 respectively.

iHaz & nHoughton 2015

14 out of 31

CENG450_Project_Report

RISCBasedProcessoronFPGA

At time 325 ns the second write back state has been completed and it can be seen that

the values have been successfully loaded into the register file (purple).

Fig.14 PC3-10:

30,FF & 34,0C (LOADIMM)

In (

Fig.15

) the shift-left operation has already been completed and the expected value of

0x18 is stored in R1. Instruction #15 in the ROM performs a subtraction of R1 from R0

and the result is stored in R0. At the completion of instruction #15 at time 615ns the

expected result of 0xE7 is stored in the register file at R0. A continued analysis of the

figures 14-21

and comparison to the expected results in (

Fig.13

) demonstrate the

proper execution and desired result of the program providing sufficient evidence of the

proper implementation of the type

A

and

L

instruction

formats

. In addition it is worth

reiterating the correct implementation of 2s complement arithmetic as can be seen by

the receipt of the result 0xE7 in the subtraction operation of (

Fig.15

).

Fig.15 PC15-17:

51 (SUB) & 34,0C (LOADIMM)

iHaz & nHoughton 2015

15 out of 31

CENG450_Project_Report

RISCBasedProcessoronFPGA

Fig.16 PC22-27:

D6 (MOV) & B8 (IN)

Fig.17 PC32-34:

28,70 (STORE) & 49 (ADD)

Fig.18 PC39-44:

88 (NAND) & C8 (

OUT 3C

)

iHaz & nHoughton 2015

16 out of 31

CENG450_Project_Report

RISCBasedProcessoronFPGA

Fig.19 PC45-51:

10,70 (LOAD) & 70 (SHR)

Fig.20 PC56-61:

48 (ADD) & C8 (

OUT 9C

)

Fig.21 Overall Simulation of Test1

iHaz & nHoughton 2015

17 out of 31

CENG450_Project_Report

RISCBasedProcessoronFPGA

TEST PROGRAM 2

Test Program 2 employs the use of all implemented instructions. The proper execution

of the program demonstrates effective design and implementation of the RISC-style

instruction processor. (

Fig.22

) provides a flowchart of the expected execution and

results.

Fig.22 Flow-Chart of Test Program2

iHaz & nHoughton 2015

18 out of 31

CENG450_Project_Report

RISCBasedProcessoronFPGA

Figures 23-31

show the simulated results of the execution of the program on the

system. The program performs four additions and four NAND operations executed by

conditional branches.

Figures 23-26

display the operation of each iteration of the loop

performing addition. In (

Fig.23

) at time 660 ns the value 0xFF has been loaded into both

R0 and R1. By time 900 ns the value in R0 has been shifted right and the value in R1 has

been shifted left resulting in 0x7F and 0xFE in R0 and R1 respectively. This value is then

copied to R3 at time 1,040 ns. The conditional branch is not taken so the addition of R0

and R1 occurs and the result 0x7D can be seen in the register file in R0 by time 1,800

ns. The second branch is taken to the

OUT

state where the value in R0, 0x7D is

displayed on the 7-segment display. This pattern is repeated three additional times, the

summation results 0x3B, 0x17 and 0xFF are displayed.

Fig.23 1st Loop: 1st ADD

Fig.24 2nd Loop: 2nd ADD

iHaz & nHoughton 2015

19 out of 31

CENG450_Project_Report

RISCBasedProcessoronFPGA

Fig.25 3rd Loop: 3rd ADD

Fig.26 4th Loop: 4th ADD

The second portion of the program computes the NAND function. As can be seen in

(

Fig.22

) to execute the NAND the first conditional branch must be taken. In (

Fig.27

) at

time 7,150 ns it can be seen that the branch flag is enabled signifying that the

conditional branch was taken and the NAND operation was executed. For each NAND

the expected result is 0xFF. It can be seen in figure 30 that at time 8,200 ns the value in

the processor_out bus is 0xFF as expected and the done flag is enabled displaying the

result on the 7-segment display. This process is repeated until program execution is

complete and can be viewed in

figures 28-30

.

iHaz & nHoughton 2015

20 out of 31

CENG450_Project_Report

RISCBasedProcessoronFPGA

Fig.27 5th Loop: 1st NAND

Fig.28 6th Loop: 2nd NAND

Fig.29 7th Loop: 3rd NAND

iHaz & nHoughton 2015

21 out of 31

CENG450_Project_Report

RISCBasedProcessoronFPGA

Fig.30 8th Loop: 4th NAND

(

Fig.31

) shows the final stage of the program, the unconditional branch to the start of the

program. At time 16,800 ns the branch flag is enabled and the program counter returns

to instruction 2 as can be seen in the rom_addr_in bus (green).

Fig.31 9th Loop: Start Again

iHaz & nHoughton 2015

22 out of 31

CENG450_Project_Report

RISCBasedProcessoronFPGA

ANALYSIS AND DISCUSSION

The combined functionality of the three instruction formats culminate to an effective

RISC-like processor. The system is able perform computations, basic branching and

memory management.

A-FORMAT

A-format instructions provide the units basic functionality such as addition and

multiplication. (

Fig.32

) provides a visual example of this basic functionality. In the

simulation at time 1,005 ns the inputs to the ALU module are the hexadecimal values

0xC0 and 0x03. The ALU-mode value is 100 which represents the function ADD and

the rf_write_index bus signals 10 which signifies the destination register for the results

is R3. The overall operation implements the summation of the hexadecimal values, the

result of which is stored in the register file in R3. In (

Fig.8

) at the completion of the write

back stage at time 1,025 ns it can be seen in reg_file values (purple) that the expected

result of 0xC3 has been successfully written into the third register file location. This

basic demonstration proves the successful implementation of the A-format instructions.

A provisional feature of the system A-format instructions is the intentional use of 2s

complement negative number computation in the ALU.

Fig.32 A-Format Simulation Example (

49

: ADD r2, r1)

iHaz & nHoughton 2015

23 out of 31

CENG450_Project_Report

RISCBasedProcessoronFPGA

B-FORMAT

B-format instructions execute both conditional and unconditional branch operations in;

figures 11 and 12 demonstrate the action taken. In (

Fig.32

) at time 9,955 ns the system

has received and approved a branch statement and the controller enables the

branch_flag. The rom_addr_in bus increments sequentially until the branch flag is

activated. At the completion of the currently executing instruction the branch target is

loaded into the program counter from the register file enacting the branch mechanism.

As can be seen in (

Fig.11

) the branch function completes successfully.

Fig.32 B-Format Simulation Example (

96

: BR r2)

L-FORMAT

The L-format instructions provide the system the ability to send and retrieve information

between the computational core and the small local RAM. (

Fig.33

) provides an example

of a successful load operation from the RAM. The L-format instruction works in two

stages. At time 275 ns instruction number 4, containing the first portion of the

LOADIMM

command, is loaded into the instruction register. Upon receipt of a

LOADIMM

in the

instruction register the controller knows that the subsequent instruction will be the

immediate value to be loaded or stored. When it arrives it is stored in the IMR register.

At time 295 ns the immediate value is received by the controller which then activates the

imr2_sel line (grey) beginning the load process.

iHaz & nHoughton 2015

24 out of 31

CENG450_Project_Report

RISCBasedProcessoronFPGA

The immediate value in the IMR register is loaded onto the control_out_imm bus (orange)

and the rf_write_index bus (purple) is given the target register value. At time 325 ns it

can be seen that the value 0x0C has been successfully loaded into register R1 in (RF).

Fig.33 L-Format Simulation Example (

34,0C

: LOADIMM r1, 0C)

PROCESSOR I/O AND HARDWARE IMPLEMENTATION

The processor implementation described above was successfully implemented on a

Xilinx Spartan 3E FPGA installed on a Nexys2 circuit board. The Nexys2 board contains

a four-digit common anode seven-segment LED display. To simplify the execution

verification the processor_out bus of the processor was connected to two of the

seven-segment displays. Two active-high push buttons were used for input control, one

as a system reset and one as a program continue. A stop and wait procedure was

implemented in the processor, activated when the controller reaches the out state.

Referring to (

Fig.22

) when test program 2 completes a computation and displays the

result on the 7-segment displays via the controllers out state the controller halts

system execution and waits for activation of the continue push-button; upon the

activation of which the program execution continues normally. This continue feature

allows the clock to be set at any frequency while maintaining the ability to verify program

execution.

iHaz & nHoughton 2015

25 out of 31

CENG450_Project_Report

RISCBasedProcessoronFPGA

For demonstration purposes the external system clock was set to 200 Hz (>150)

allowing rapid program execution and verification, especially for the 7-segment to

display the two digits at the same time. We also added the Display controller VHDL file

to the project in order to display the output on the 7-segments in Digilent Nexys2 Board.

The following settings were used:

clk is external clock FPGA pin U9, reset and start are FPGA pin B18 and pin H13

hex3, hex2,hex1 and hex0 are four bit arrays used to store hex display character.

We used only hex1 and hex0 as we have only two digits

an (an0,an1, an2, an3) four bit array that connect to the display transistors

sseg 7bit array that stores the individual segments of the hex display

Fig.34 Test Program 2 running on Spartan FPGA

iHaz & nHoughton 2015

26 out of 31

CENG450_Project_Report

RISCBasedProcessoronFPGA

CONCLUSION

A pipelined processor employing RISC-like instructions was implemented on a Xilinx

Spartan 3E FPGA installed on a Nexys2 circuit board. The design was verified via the

execution of two test programs designed to use and stress every instruction in the

system. The design includes a 1-byte register file, a 256 byte ROM and 256 byte RAM,

dynamic controller and support modules. The system successfully employs multiple

arithmetic instructions, two conditional and one unconditional branch instruction as well

as memory management instructions. Verification programs were executed on the

Spartan FPGA and verified using two 7-segment displays and two push button inputs

and an system frequency of 150 Hz.

iHaz & nHoughton 2015

27 out of 31

CENG450_Project_Report

RISCBasedProcessoronFPGA

APPENDIX (TABLES)

FSM CONTROL STATES (VHDL)

AlloutputsareInitialized

WHEN

ALU=>

WHEN

S0=>

Flag_Reg<={Z,N}

IF

(

Start='1'

)

THEN

ALUMode<=Inst_reg(64)

PC_en<=1

ExceptforNAND

NextState<=Fetch

IN_Sel<=0

Else

IMR2_Sel<=0

ST:IMR2_Sel,RAM_WR

NextState<=S0

EndIf

LD,LDIm:IMR2_Sel

WHEN

Fetch=>

IN:IN_Sel,IMR2_Sel

Alloutputsare0

NextState<=Write_Back

Inst_reg<=ROM_out

WHEN

Branch=>

NextState<=Decode

ALUMode<=000

WHEN

Decode=>

PC_en<=1

Check(

Inst_reg(74)

)

Check(

Inst_reg(32)

)

AFormat(Arithmetic)

00/11:Br_Sel

IN_Sel<=1

01/10:Br_Sel(Flag)

NextState<=ALU

NextState<=Fetch

BFormat(Branch)

WHEN

Write_Back=>

PC_en<=1

NextState<=Branch

Return:PC_en,Rt_Sel

Check(

Inst_reg(74)

)

0/2/C:RF_en<=0

NextState<=Fetch

AFormat(Arithmetic)

Others:RF_en

PC_en<=1

0001:WB_Sel

NextState<=LD_ST

NextState<=Fetch

Table 1: FSM Control States

iHaz & nHoughton 2015

28 out of 31

CENG450_Project_Report

RISCBasedProcessoronFPGA

FSM CONTROL SIGNALS

State

S0

Fetch

Decode

Op

Code

ALU

Branch

LD/ST

WB

Next

State

Fetch

Decode

ALU

Branch

LD/ST

Fetch

(Return

)

WB

E4

LR_e

n

0

1

0

1

0

Br_Se

l

Fetch

WB

(LD)

Fetch

(ST)

Fetch

S1

Br_Se

l

x

x

S2

Rt_Se

l

x

x

0

0

0

E5

RF_e

n

0

0

Output

S3

S4

IN_Se IMR2_Se

l

l

x

x

x

x

1

0

0

x

E3

PC_e

n

1

0

0

0

0

ALU

ALU_Mod

e

x

x

E6

RAM_WR

S5

0

0

x

x

WB_Sel

NC

NC

Table 2: Control FSM Signals

NC

WB_Sel

INSTRUCTION SET

Format

Mnemonic

NOP

Op-code

0

ADD

SUB

SHL

SHR

6

7

NAND

IN

OUT

MOV

BR

11

12

13

9

BR.Z

BR.N

BR.SUB

RETURN

LOAD

STORE

LOADIMM

9

14

1

2

3

Function

Nothing

R[ra] R[ra] + R[rb]; ((R[ra] + R[rb]) = 0) Z 1; else Z 0;

((R[ra] + R[rb]) < 0) N 1; else N 0;

R[ra] R[ra] R[rb]; ((R[ra] R[rb]) = 0) Z 1; else Z 0;

((R[ra] R[rb]) < 0) N 1; else N 0;

Z R[ra]<7>; R[ra] (R[ra]<6:0>&0);

Z R[ra]<0>; R[ra] (0&R[ra]<7:1>);

R[ra] R[ra] NAND R[rb]; ((R[ra] NAND R[rb]) = 0) Z 1;

else Z 0; ((R[ra] NAND R[rb]) < 0) N 1; else N 0;

R[ra] IN.PORT;

OUT.PORT R[ra];

R[ra] R[rb];

(brx=0) PC R[rb];

(brx=1 Z=1) PC R[rb];

(brx=1 Z=0) PC PC + 1;

(brx=2 N=1) PC R[rb];

(brx=2 N=0) PC PC + 1;

(brx=3) (LR PC + 1; PC R[rb])

(brx=0) PC LR;

R[ra] M[ea];

M[ea] R[ra];

R[ra] imm;

Table 3: Instruction Set

iHaz & nHoughton 2015

29 out of 31

CENG450_Project_Report

RISCBasedProcessoronFPGA

PROGRAM TEST 1

Addr

2

3

4

5

10

15

16

17

22

Inst.

x"30"

x"FF"

x"34"

x"0c"

x"64"

x"51"

x"38"

x"03"

x"D6"

27

x"B8"

32

33

34

39

x"28"

x"70"

x"49"

x"88"

44

x"C8"

45

46

51

56

x"10"

x"70"

x"70"

x"48"

61

x"C8"

MIPSASM

#start#LOADIMMr0,0XFF

0xFF,theimmediatevalue

LOADIMMr1,0X0c

0x0C,theimmediatevalue

SHLr1

SUBr0,r1

r0=r0r1

LOADIMMr2,0x03

0x03,theimmediatevalue

MOVr1,r2

r1=r2

INr2SettheInputto"0xC0"

("11000000")

STOREr2,0x70

EffectiveAddress

ADDr2,r1

r2=r2+r1

NANDr2,r0

r2=r2NANDr0

OUTr2AtthispointR[2]

mustbe"00111100"

LOADr0,0x70

EffectiveAddress

SHRr0

ADDr2,r0(N_Flag)

OUTr2AtthispointR[2]

havetobe"10011100"

r0

FF

E7

r1

0

0C

18

r2 r3 RAM70

0 0

0

3

OUT

C0

C3

3C

C0

60

9C

C0

3C

9C

Table 4: Program TEST 1

PROGRAM TEST 2

Addr Inst.

2 x"30"

3 x"0F"

9 x"20"

10 x"0F"

11 x"30"

12 x"07"

18 x"20"

19 x"0E"

20 x"30"

21 x"FF"

22 x"34"

23 x"FF"

29 x"70"

30 x"64"

35 x"DC"

36 x"10"

37 x"0F"

43 x"70"

49 x"20"

50 x"0F"

MIPSASM

loadimmr0,0F#start#

storer0,add_nand(AN)

loadimmr0,7

storer0,counter(CN)

loadimmr0,FF

loadimmr1,FF

shrr0#loop#

shlr1

movr3,r0

loadr0,add_nand

shrr0

storer0,add_nand

iHaz & nHoughton 2015

r0

0F

FF

ShR

AN

ShR

r1

FF

ShL

r2 r3 RAM714

CN=07

r0

RAM715 OUT

AN=0F

ShRAN

30 out of 31

CENG450_Project_Report

RISCBasedProcessoronFPGA

51 x"D3"

58 x"38"

59 x"4B"

65 x"96"

66 x"41"

67 x"38"

68 x"4C"

74 x"92"

75 x"81"

81 x"C0"

82 x"10"

83 x"0E"

84 x"D9"

85 x"34"

86 x"01"

92 x"51"

98 x"20"

99 x"0E"

100 x"D6"

101 x"38"

102 x"76"

106 x"D3"

109 x"9A"

110 x"38"

111 x"1D"

117 x"92"

118 x"38"

119 x"02"

125 x"92"

movr0,r3

loadimmr2,nand

brznand:

addr0,r1

loadimmr2,out_add_nand

brout_add_nand

nandr0,r1(N)#nand#

outr0

loadr0,counter

movr2,r1

loadimmr1,1

subr0,r1

storer0,counter

movr1,r2

loadimmr2,out:

movr0,r3

brnout

loadimmr2,loop

brloop

loadimmr2,start#out#

brstart

r3

r0+r1

r0Nr1

CN

r0r1

r3

r2

4B

4C

r1

76

1D

2

CN1

r0

Table 6: Program TEST 2

REFERENCE

1. CENG 450 Lab Manual,

University of Victoria, 06/04/2015

2. Digilent Nexys2 Board reference Manual

, (Doc: 502-107) Digilent, Pullman, WA,

2008

iHaz & nHoughton 2015

31 out of 31

S-ar putea să vă placă și

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.De la EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Încă nu există evaluări

- Design and Performance Analysis of 8-Bit RISC Processor Using Xilinx & Microwind ToolDocument10 paginiDesign and Performance Analysis of 8-Bit RISC Processor Using Xilinx & Microwind ToolRakeshconclaveÎncă nu există evaluări

- Vss Paper MicroprocessorDocument4 paginiVss Paper MicroprocessorAnil JhaÎncă nu există evaluări

- WISC-99S Computer Architecture Design ProjectDocument10 paginiWISC-99S Computer Architecture Design ProjectzzzzoobbiiaaÎncă nu există evaluări

- Advanced RISC Machine-ARM Notes BhurchandiDocument8 paginiAdvanced RISC Machine-ARM Notes BhurchandiVipin TiwariÎncă nu există evaluări

- Tkbase + 2148 D-Board: Lpc2148 Training ManualDocument47 paginiTkbase + 2148 D-Board: Lpc2148 Training ManualMahesh BhatkalÎncă nu există evaluări

- Register FileDocument6 paginiRegister FilejayaprasadkalluriÎncă nu există evaluări

- CHAPTER 5, Inside Digital DesignDocument33 paginiCHAPTER 5, Inside Digital DesignSyed Abdullah RizviÎncă nu există evaluări

- An Introduction To ARM Architecture With Each ModuleDocument6 paginiAn Introduction To ARM Architecture With Each ModuleAnusha PadmavathiÎncă nu există evaluări

- Unit - Iv 4.0) Introduction: Digital Logic and Computer OrganizationDocument18 paginiUnit - Iv 4.0) Introduction: Digital Logic and Computer OrganizationJit AggÎncă nu există evaluări

- Fpga Implementation of 16 Bit Risc Cpu and Performance AnalysisDocument4 paginiFpga Implementation of 16 Bit Risc Cpu and Performance AnalysisJournalNX - a Multidisciplinary Peer Reviewed JournalÎncă nu există evaluări

- 19ecs431 - Embedded SystemsDocument18 pagini19ecs431 - Embedded SystemsNaresh KumarÎncă nu există evaluări

- COA Module 2 NotesDocument46 paginiCOA Module 2 NotesAssini HussainÎncă nu există evaluări

- The Design of A RISC Architecture and Its Implementation With An FPGADocument24 paginiThe Design of A RISC Architecture and Its Implementation With An FPGASneha AngreÎncă nu există evaluări

- RISC Instruction Set:: I) Data Manipulation InstructionsDocument8 paginiRISC Instruction Set:: I) Data Manipulation InstructionsSwarup BharÎncă nu există evaluări

- D 32-CPU: Esign of A Bit Single CycleDocument11 paginiD 32-CPU: Esign of A Bit Single CycleAritra GuptaÎncă nu există evaluări

- Hardwired ControlDocument6 paginiHardwired Controlapi-19967001Încă nu există evaluări

- Input Unit: Five Basic Components of Computer SystemDocument9 paginiInput Unit: Five Basic Components of Computer SystemJefin PaulÎncă nu există evaluări

- FPGA Based 32 Bit ALU For Automatic Antenna Control UnitDocument5 paginiFPGA Based 32 Bit ALU For Automatic Antenna Control UnitMinh DucÎncă nu există evaluări

- Micro Instruction ExecutionDocument25 paginiMicro Instruction Executionnikhil_pthkÎncă nu există evaluări

- Spring 2010 ELEC5200/6200 CPU Design Project Assigned Feb 8, 2010Document5 paginiSpring 2010 ELEC5200/6200 CPU Design Project Assigned Feb 8, 2010Qung NguyenÎncă nu există evaluări

- S7-300 PLC in RTGDocument72 paginiS7-300 PLC in RTGmunawar munawarÎncă nu există evaluări

- Simple As Possible ComputerDocument13 paginiSimple As Possible ComputerMd Raton AliÎncă nu există evaluări

- EE6008 Unit 5Document8 paginiEE6008 Unit 5TakeItEasyDude TIEDÎncă nu există evaluări

- FPGA Based 32 Bit ALU For Automatic Antenna Control Unit SM - Adnan21@Document5 paginiFPGA Based 32 Bit ALU For Automatic Antenna Control Unit SM - Adnan21@Edwin GeraldÎncă nu există evaluări

- Unit Iii: Programming OFDocument41 paginiUnit Iii: Programming OFNaga RajanÎncă nu există evaluări

- 2 16 1350130228 7. Flexible Wireless DataDocument6 pagini2 16 1350130228 7. Flexible Wireless DataSumeet SauravÎncă nu există evaluări

- 8-Bit Microcontroller With 2K Bytes of In-System Programmable Flash Attiny22 Attiny22L PreliminaryDocument11 pagini8-Bit Microcontroller With 2K Bytes of In-System Programmable Flash Attiny22 Attiny22L Preliminarymike_helplineÎncă nu există evaluări

- Motorola Program Control Unit 1Document48 paginiMotorola Program Control Unit 1ayush guptaÎncă nu există evaluări

- Tutorial On Simatic s5 Control System :practical Programming and Fault FindingDocument22 paginiTutorial On Simatic s5 Control System :practical Programming and Fault Findingak4dili80% (5)

- SDM Module IDocument28 paginiSDM Module IKiran KrishnanÎncă nu există evaluări

- Cpre 381 Processor Project 1Document20 paginiCpre 381 Processor Project 1api-272773251Încă nu există evaluări

- Arm ArchitectureDocument5 paginiArm ArchitectureYaserÎncă nu există evaluări

- EE6008 Unit 1Document12 paginiEE6008 Unit 1TakeItEasyDude TIEDÎncă nu există evaluări

- Project 2012fallDocument5 paginiProject 2012fallATHIRA V RÎncă nu există evaluări

- Introduction To Processor Based Embedded System DesignDocument8 paginiIntroduction To Processor Based Embedded System DesignSoundarya SvsÎncă nu există evaluări

- Allen Bradley PLC ProgrammingDocument44 paginiAllen Bradley PLC ProgrammingEduardo Luna91% (11)

- Arquitectura de PSoC - EasypsocDocument41 paginiArquitectura de PSoC - EasypsocRednaxela SaenzÎncă nu există evaluări

- Final-Assignment CoverDocument12 paginiFinal-Assignment CoverHứa Đăng KhoaÎncă nu există evaluări

- Reduced Instruction Set Computer (Risc) 32bit Processor On Field Programmable Gate Arrays (Fpgas) ImplementationDocument5 paginiReduced Instruction Set Computer (Risc) 32bit Processor On Field Programmable Gate Arrays (Fpgas) ImplementationDr. Krishna N. SharmaÎncă nu există evaluări

- At Tiny 13Document146 paginiAt Tiny 13Hasri AwalÎncă nu există evaluări

- PLC Overview PID Control and TuningDocument64 paginiPLC Overview PID Control and TuningBalaji KumarÎncă nu există evaluări

- Project 12springDocument5 paginiProject 12springFarzin GhotbiÎncă nu există evaluări

- ARM ArchitectureDocument9 paginiARM Architectureultimatekp144Încă nu există evaluări

- ARM Architecture - L5Document7 paginiARM Architecture - L5Maniswari MothukuruÎncă nu există evaluări

- ARM Architecture - L5Document7 paginiARM Architecture - L5Maniswari MothukuruÎncă nu există evaluări

- Programmable Logic ControllerDocument98 paginiProgrammable Logic Controller126 N.EZHILARASAN EEERÎncă nu există evaluări

- Traffic Light ControlDocument14 paginiTraffic Light ControlsamarthgulatiÎncă nu există evaluări

- Introduction To International Electro Technical Commission (IEC) 61131-3Document38 paginiIntroduction To International Electro Technical Commission (IEC) 61131-3Glan DevadhasÎncă nu există evaluări

- 8 Bit Risc Processor PresentationDocument36 pagini8 Bit Risc Processor PresentationSantanu KumarÎncă nu există evaluări

- QL ServiceManualDocument98 paginiQL ServiceManualOscar Arthur KoepkeÎncă nu există evaluări

- Introduction To MicrocontrollersDocument52 paginiIntroduction To MicrocontrollersSanjayaRangaLSenavirathnaÎncă nu există evaluări

- HW Assignment 5Document3 paginiHW Assignment 5abdul basitÎncă nu există evaluări

- Design of A RISC Microcontroller Core in 48 HoursDocument11 paginiDesign of A RISC Microcontroller Core in 48 HoursPulkit TrivediÎncă nu există evaluări

- Logic Control and PLCsDocument6 paginiLogic Control and PLCsKRISHNA KANT GUPTAÎncă nu există evaluări

- Chapter 1: Introduction To Psoc: From The Free Online Book "Architecture and Programming of Psoc Microcontrollers"Document34 paginiChapter 1: Introduction To Psoc: From The Free Online Book "Architecture and Programming of Psoc Microcontrollers"Joel George MathewÎncă nu există evaluări

- Lab Sheet 6 Single Cycle Datapath FinalDocument3 paginiLab Sheet 6 Single Cycle Datapath FinalSANJEEV MALLICKÎncă nu există evaluări

- Design and Characterization of A CMOS 8-Bit Microprocessor Data PathDocument6 paginiDesign and Characterization of A CMOS 8-Bit Microprocessor Data PathMohamedÎncă nu există evaluări

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960De la EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Încă nu există evaluări

- GCD Fpga Based DesigneDocument30 paginiGCD Fpga Based DesigneIbrahim HejabÎncă nu există evaluări

- C For Engineers HandoutDocument44 paginiC For Engineers HandoutIbrahim HejabÎncă nu există evaluări

- LMC SimulationDocument29 paginiLMC SimulationIbrahim HejabÎncă nu există evaluări

- How Microprocessors WorkDocument15 paginiHow Microprocessors WorkIbrahim HejabÎncă nu există evaluări

- Lab Assignment #2 8255A INTERFACE (LED) : GreenDocument2 paginiLab Assignment #2 8255A INTERFACE (LED) : GreenIbrahim HejabÎncă nu există evaluări

- Micro ExcellentDocument114 paginiMicro ExcellentIbrahim HejabÎncă nu există evaluări

- GatesDocument1 paginăGatesIbrahim HejabÎncă nu există evaluări

- Sage 100 ERP Custom Office SpecDocument2 paginiSage 100 ERP Custom Office SpecBrian RiceÎncă nu există evaluări

- Chateaubriand and RenéDocument4 paginiChateaubriand and RenéMariaÎncă nu există evaluări

- LITERATUREDocument3 paginiLITERATUREKath BocalanÎncă nu există evaluări

- Falcon BMS Keyfile ManualDocument37 paginiFalcon BMS Keyfile ManualhuirttpsÎncă nu există evaluări

- Stig-of-the-Dump More QuestionsDocument5 paginiStig-of-the-Dump More QuestionsSelwenÎncă nu există evaluări

- EncapsulationDocument13 paginiEncapsulationKainat KabeerÎncă nu există evaluări

- Unit Plan Lesson 2 Sunshine and ShadowsDocument2 paginiUnit Plan Lesson 2 Sunshine and Shadowsapi-301741650Încă nu există evaluări

- QRadar SIEM Administration GuideDocument366 paginiQRadar SIEM Administration GuideJoel GuedeÎncă nu există evaluări

- Passive VoiceDocument3 paginiPassive Voiceanon_805613190Încă nu există evaluări

- Manonmaniam Sundaranar University: B.Sc. Mathematics - Iii YearDocument175 paginiManonmaniam Sundaranar University: B.Sc. Mathematics - Iii YearRAKESH KUMARÎncă nu există evaluări

- Levman-Pali The Language The Medium and MessageDocument1 paginăLevman-Pali The Language The Medium and MessageAnandaÎncă nu există evaluări

- CPE Reading Paper Part 1Document8 paginiCPE Reading Paper Part 1Cột100% (1)

- Lec9 Lab CSC371 Database SystemsDocument19 paginiLec9 Lab CSC371 Database SystemsAbdullah ShabbirÎncă nu există evaluări

- Bs 51119009206170Document2 paginiBs 51119009206170LEONA HOSPITALÎncă nu există evaluări

- The Mystic Heart Mystery School Summary Guide OnlineDocument5 paginiThe Mystic Heart Mystery School Summary Guide OnlinePooja SavaliaÎncă nu există evaluări

- Antovic Musicolinguistics PDFDocument15 paginiAntovic Musicolinguistics PDFHucbald100% (1)

- Dock Panel Suite Documentation DetailedDocument47 paginiDock Panel Suite Documentation Detailedgili mudavanhuÎncă nu există evaluări

- E-Learning Excel VBA Programming Lesson 4Document13 paginiE-Learning Excel VBA Programming Lesson 4perepavijayÎncă nu există evaluări

- Oop Lab (Terminal)Document2 paginiOop Lab (Terminal)i am lateÎncă nu există evaluări

- Swift Standars 9 CategoryDocument173 paginiSwift Standars 9 Categoryliittokivi100% (1)

- British and American SpellingDocument12 paginiBritish and American SpellingAileen Cruz SalaysayÎncă nu există evaluări

- Ucm t28234Document495 paginiUcm t28234Marqués Narciso Croto TenebrosoÎncă nu există evaluări

- Iac393 Communicative Chinese 3Document2 paginiIac393 Communicative Chinese 3api-369747076Încă nu există evaluări

- Shakeel Badayuni KalamDocument9 paginiShakeel Badayuni KalamMohammed Hassan Mohiuddin KhanÎncă nu există evaluări

- Xeon Phi Openmp HypackDocument59 paginiXeon Phi Openmp HypackNecmettin yıldızÎncă nu există evaluări

- B1 - 01 Simple Past Tense GrammarDocument3 paginiB1 - 01 Simple Past Tense GrammarnogaraÎncă nu există evaluări

- Unitplan Make A Comic Book PDFDocument9 paginiUnitplan Make A Comic Book PDFapi-584031926Încă nu există evaluări

- On The History of The Aristotelian Writings (Shute Richard) PDFDocument252 paginiOn The History of The Aristotelian Writings (Shute Richard) PDFparasoly100% (1)

- His Appearing-Alyce McPhersonDocument4 paginiHis Appearing-Alyce McPhersontLzmS23Încă nu există evaluări

- Business Writing As A Tool of Management ControlDocument13 paginiBusiness Writing As A Tool of Management Controlkapeel77Încă nu există evaluări