Documente Academic

Documente Profesional

Documente Cultură

Cad Lab Manual

Încărcat de

Sougata GhoshDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Cad Lab Manual

Încărcat de

Sougata GhoshDrepturi de autor:

Formate disponibile

Department of Electronics & Communication Engineering

SET, IFTM University, Moradabad

CAD OF ELECTRONICS LAB (EEC-751)

EEC 751 CAD OF ELECTRONICS LAB

PSPICE Experiments

1. Transient Analysis of BJT inverter using step input.

2. DC Analysis (VTC) of BJT inverter with and without parameters.

3. Transient Analysis of NMOS inverter using step input.

4. Transient Analysis of NMOS inverter using pulse input.

5. DC Analysis (VTC) of NMOS inverter with and without parameters.

6. Analysis of CMOS inverter using step input.

7. Transient Analysis of CMOS inverter using step input with parameters.

8. Transient Analysis of CMOS inverter using pulse input.

9. Transient Analysis of CMOS inverter using pulse input with parameters.

10. DC Analysis (VTC) of CMOS inverter with and without parameters.

11. Transient & DC Analysis of NOR Gate inverter.

12. Transient & DC Analysis of NAND Gate

Department of Electronics & Communication Engineering

SET, IFTM University, Moradabad

CAD OF ELECTRONICS LAB (EEC-751)

Experiment No:1

Aim: Transient analysis of BJT inverter using Step input

Software Used: PSPICE

Theory:

1. Ideal Inverter Digital Gate

The ideal Inverter model is important because it gives a metric by which we can judge the quality of

actual implementation. Its VTC is shown in figure 1.1 and has the following properties:

Infinite gain in the transition region, and gate threshold located in the middle of the logic swing, with

high and low margins equal to the half of the swing. The input and output impedance of the ideal gate

are infinity and zero, respectively.

2. Dynamic Behavior of Inverter Digital Gate

Figure1.2 illustrates the behavior of the inverter digital gate using BJT

There are three regions for the above voltage transfer characteristic

1. Cut-off region.

2. Forward Active region.

3. Saturation region.

BJT Inverter can be best expressed by its voltage transfer characteristic (VTC) or DC transfer

characteristic as shown in figure 1.3. That relates the output voltage to the input one.

If:

Vi = Vol, Vo = Voh = Vcc (VTC) or DC Transfer Characteristic The transistor is OFF.

Department of Electronics & Communication Engineering

SET, IFTM University, Moradabad

CAD OF ELECTRONICS LAB (EEC-751)

Vi = Vil

The transistor Begins to turn on.

Vil < Vi < Vih. The transistor is in forward active region and operates as Amplifier.

Vi = Voh .The transistor will be deep is saturation, Vo = Vce(sat).

A measure of sensitivity to noise is called Noise Margin (NM) which can be expressed by:

Nml = Vil Vol.

Nmh = Voh Vih.

Schematics:

Simulation waveforms:

Result: The transient analysis of BJT inverter using step unit in PSPICE has been successfully done and

the waveforms were plotted successfully. The waveforms tally with the expected behavior of the BJT

inverter.

Department of Electronics & Communication Engineering

SET, IFTM University, Moradabad

CAD OF ELECTRONICS LAB (EEC-751)

Experiment No:8

Aim: Transient analysis of CMOS inverter using pulse input

Software Used: PSPICE

Theory:

Figure below shows the circuit diagram of a static CMOS inverter. Its operation is readily understood

with the aid of the simple switch model of the MOS transistor, the transistor is nothing more than a switch

with an infinite off resistance (for |VGS| < |VT|), and a finite on-resistance (for |VGS| > |VT|).

Fig 3.1: Static CMOS inverter. VDD stands for the supply voltage.

This leads to the following interpretation of the inverter. When Vin is high and equal to VDD, the NMOS

transistor is on, while the PMOS is off. This yields the equivalent circuit of Figure 3.2. A direct path

exists between Vout and the ground node, resulting in a steady-state value of 0V. On the other hand, when

the input voltage is low (0 V), NMOS and PMOS transistors are off and on, respectively. The equivalent

circuit of Figure 5.2b shows that a path exists between VDD and Vout, yielding a high output voltage. The

gate clearly functions as an inverter.

Fig 3.2 Switch models of CMOS inverter.

The nature and the form of the voltage-transfer characteristic (VTC) can be graphically deduced by

superimposing the current characteristics of the NMOS and the PMOS devices. Such a graphical

construction is traditionally called a load-line plot. It requires that the I-V curves of the NMOS and

PMOS devices are transformed onto a common coordinate set. We have selected the input voltage Vin, the

output voltage Vout and the NMOS drain current IDN as the variables of choice. The PMOS I-V relations

can be translated into this variable space by the following relations (the subscripts n and p denote the

NMOS and PMOS devices, respectively):

Department of Electronics & Communication Engineering

SET, IFTM University, Moradabad

CAD OF ELECTRONICS LAB (EEC-751)

IDSp = IDSn

VGSn = Vin ; VGSp = Vin VDD

VDSn = Vout ; VDSp = Vout VDD

The load-line curves of the PMOS device are obtained by a mirroring around the xaxis and a horizontal

shift over VDD. This procedure is outlined in Figure 5.3, where the subsequent steps to adjust the original

PMOS I-V curves to the common coordinate set Vin,Vout and IDn are illustrated.

Figure 3.3 Transforming PMOS I-V characteristic to a common coordinate set (assuming VDD = 2.5 V).

Figure 3.4 Load curves for NMOS and PMOS transistors of the static CMOS inverter (VDD =

2.5 V). The dots represent the dc operation points for various input voltages.

The resulting load lines are plotted in Figure 3.4. For a dc operating points to be valid, the currents

through the NMOS and PMOS devices must be equal. Graphically, this means that the dc points must be

located at the intersection of corresponding load lines. A number of those points (for Vin = 0, 0.5, 1, 1.5,

2, and 2.5 V) are marked on the graph. As can be observed, all operating points are located either at the

high or low output levels. The VTC of the inverter hence exhibits a very narrow transition zone. This

results from the high gain during the switching transient, when both NMOS and PMOS are

simultaneously on, and in saturation. In that operation region, a small change in the input voltage results

in a large output variation. All these observations translate into the VTC of Figure 3.5.

Department of Electronics & Communication Engineering

SET, IFTM University, Moradabad

CAD OF ELECTRONICS LAB (EEC-751)

Figure 3.5 VTC of static CMOS inverter, derived from Figure 5.4 (VDD = 2.5 V). For each operation

region, the modes of the transistors are annotated off, res(istive), or sat(urated).

Schematics:

VCC

XSC1

3.3V

Q3

Ext Trig

+

_

B

V1

0 V 3.3 V

6usec 12usec

Vi

0.5u

1.25u

Q1

Vo

C1

500fF

0.5u

1.25u

Fig 3.6: CMOS inverter with pulse input schematic circuit

Simulation waveforms:

Department of Electronics & Communication Engineering

SET, IFTM University, Moradabad

CAD OF ELECTRONICS LAB (EEC-751)

Result: The transient analysis of CMOS inverter using pulse input in PSPICE has been successfully done

and the waveforms were plotted successfully. The waveforms tally with the expected behavior of the

CMOS inverter.

Experiment No:6

Department of Electronics & Communication Engineering

SET, IFTM University, Moradabad

CAD OF ELECTRONICS LAB (EEC-751)

Aim: Transient analysis of CMOS inverter using step input

Software Used: PSPICE

Theory:

Figure below shows the circuit diagram of a static CMOS inverter. Its operation is readily understood

with the aid of the simple switch model of the MOS transistor, the transistor is nothing more than a switch

with an infinite off resistance (for |VGS| < |VT|), and a finite on-resistance (for |VGS| > |VT|).

Fig 3.1: Static CMOS inverter. VDD stands for the supply voltage.

This leads to the following interpretation of the inverter. When Vin is high and equal to VDD, the NMOS

transistor is on, while the PMOS is off. This yields the equivalent circuit of Figure 3.2. A direct path

exists between Vout and the ground node, resulting in a steady-state value of 0V. On the other hand, when

the input voltage is low (0 V), NMOS and PMOS transistors are off and on, respectively. The equivalent

circuit of Figure 5.2b shows that a path exists between VDD and Vout, yielding a high output voltage. The

gate clearly functions as an inverter.

Fig 3.2 Switch models of CMOS inverter.

The nature and the form of the voltage-transfer characteristic (VTC) can be graphically deduced by

superimposing the current characteristics of the NMOS and the PMOS devices. Such a graphical

construction is traditionally called a load-line plot. It requires that the I-V curves of the NMOS and

PMOS devices are transformed onto a common coordinate set. We have selected the input voltage Vin, the

output voltage Vout and the NMOS drain current IDN as the variables of choice. The PMOS I-V relations

can be translated into this variable space by the following relations (the subscripts n and p denote the

NMOS and PMOS devices, respectively):

Department of Electronics & Communication Engineering

SET, IFTM University, Moradabad

CAD OF ELECTRONICS LAB (EEC-751)

IDS p = IDS n

VGS n = Vin ; VGS p = Vin VDD

VDS n = Vout ; VDS p = Vout VDD

The load-line curves of the PMOS device are obtained by a mirroring around the xaxis and a horizontal

shift over VDD. This procedure is outlined in Figure 5.3, where the subsequent steps to adjust the original

PMOS I-V curves to the common coordinate set Vin,Vout and IDn are illustrated.

Figure 3.3 Transforming PMOS I-V characteristic to a common coordinate set (assuming VDD = 2.5 V).

Figure 3.4 Load curves for NMOS and PMOS transistors of the static CMOS inverter (VDD =

2.5 V). The dots represent the dc operation points for various input voltages.

The resulting load lines are plotted in Figure 3.4. For a dc operating points to be valid, the currents

through the NMOS and PMOS devices must be equal. Graphically, this means that the dc points must be

located at the intersection of corresponding load lines. A number of those points (for Vin = 0, 0.5, 1, 1.5,

2, and 2.5 V) are marked on the graph. As can be observed, all operating points are located either at the

high or low output levels. The VTC of the inverter hence exhibits a very narrow transition zone. This

results from the high gain during the switching transient, when both NMOS and PMOS are

simultaneously on, and in saturation. In that operation region, a small change in the input voltage results

in a large output variation. All these observations translate into the VTC of Figure 3.5.

Department of Electronics & Communication Engineering

SET, IFTM University, Moradabad

CAD OF ELECTRONICS LAB (EEC-751)

Figure 3.5 VTC of static CMOS inverter, derived from Figure 5.4 (VDD = 2.5 V). For each operation

region, the modes of the transistors are annotated off, res(istive), or sat(urated).

Schematics:

VCC

XSC1

3.3V

Q3

Ext Trig

+

_

B

V2

0.5u

1.25u

5nsec

Q1

Vo

C1

500fF

0.5u

1.25u

Fig 3.7: CMOS inverter with step input schematic circuit

Department of Electronics & Communication Engineering

SET, IFTM University, Moradabad

CAD OF ELECTRONICS LAB (EEC-751)

Simulation waveforms:

Result: The transient analysis of CMOS inverter using step input in PSPICE has been successfully done

and the waveforms were plotted successfully. The waveforms tally with the expected behavior of the

CMOS inverter.

Department of Electronics & Communication Engineering

SET, IFTM University, Moradabad

CAD OF ELECTRONICS LAB (EEC-751)

CMOS NAND Gate:

Figure 10.2 shows a two input CMOS NAND gate, output pull-up is provided by

two PMOS in parallel connections, while two NMOS with series connection

provide an output pull-down to ground.

Output High State:

This state is obtained by two cases:

If both inputs are low, the two PMOS are in active operation providing an output pull-up to

VDD, while the two NMOS are off, so ID,PA = ID,PB = 0, and VDS,PA = VDS,PB = 0.

With a single input low, an output pull up path to VDD is exist through the corresponding

PMOS, with the corresponding NMOS is off and no current is pass through NMOS .

In each case: VOH = VDD.

Output Low State:

This state is obtained only if the two inputs are high as follow, if A and B inputs are high, NA and NB

are in active operation , while PA and PB are off, so no output pull up path to VDD is available and

the currents ID,NA = ID,NB = 0, and VOL = 0.

Department of Electronics & Communication Engineering

SET, IFTM University, Moradabad

CAD OF ELECTRONICS LAB (EEC-751)

CMOS NOR Gate:

Figure 10.3 shows a two input CMOS NOR Gate, the NOR function can be

obtained with CMOS pairs; PMOS devices in series to provide pull-up

configuration and NMOS devices in parallel to provide pull-down configuration.

Output Low State:

The output low can be obtained by two cases:

If bothe input are high, the gate to source voltage for both NMOS brings them into active

operation providing an active pull-down to ground, while PMOS's are off.

If any input in high the corresponding NMOS is in active operation to provide an output pulldown to ground.

In each cases:

VOL = 0.

Output High State:

This state can be occurred only if the two inputs are low, where both NA and NB are off, while the

PMOS devices are in active operation to provide an output pull-up to VDD.

VOH = VDD.

Procedure:

Part 1:

1. Construct the circuit shown in Figure 10.1, VDD = 5V

2. Find the truth table filling the following

Department of Electronics & Communication Engineering

SET, IFTM University, Moradabad

CAD OF ELECTRONICS LAB (EEC-751)

3. Filling the following table and Draw the VTC of this gate :

4. Determine VOH,VOL,VIH,VIL

5. Draw the VTC of this gate by using the Orcad .

Department of Electronics & Communication Engineering

SET, IFTM University, Moradabad

CAD OF ELECTRONICS LAB (EEC-751)

S-ar putea să vă placă și

- CMOS Inverter Modelling On CADENCEDocument5 paginiCMOS Inverter Modelling On CADENCESanket KoleyÎncă nu există evaluări

- Unit 1.2 VLSI NotesDocument16 paginiUnit 1.2 VLSI NotesElston RyanÎncă nu există evaluări

- DCID Experiment MergedDocument94 paginiDCID Experiment MergedSumer SainiÎncă nu există evaluări

- Assignment 1Document9 paginiAssignment 1Taslima Rahman MiliÎncă nu există evaluări

- AnExperiment On CmosDocument10 paginiAnExperiment On CmosVinny VenizÎncă nu există evaluări

- Mos Transistor Theory: Figure 1: Symbols of Various Types of TransistorsDocument16 paginiMos Transistor Theory: Figure 1: Symbols of Various Types of TransistorsKirthi RkÎncă nu există evaluări

- Model 1Document22 paginiModel 1Vinay MLÎncă nu există evaluări

- Q02201300137Document8 paginiQ02201300137Vikas PatelÎncă nu există evaluări

- Osciladores Ingles 1Document6 paginiOsciladores Ingles 1Edwin Mauricio ArizaÎncă nu există evaluări

- Unit 5Document6 paginiUnit 5Tarun SinghalÎncă nu există evaluări

- Cmos Inverter CharacteristicsDocument8 paginiCmos Inverter CharacteristicsShambhavi SonuÎncă nu există evaluări

- Cmos InvDocument25 paginiCmos InvkumarbsnspÎncă nu există evaluări

- I. Instructional Objectives: D S G D GDocument4 paginiI. Instructional Objectives: D S G D Gcokelat_kÎncă nu există evaluări

- ElectronicsDocument22 paginiElectronicsVARSHITH REDDY JÎncă nu există evaluări

- Cmos Inverter CharacteristicsDocument5 paginiCmos Inverter CharacteristicsRichu Jose CyriacÎncă nu există evaluări

- A New Approach Ultra Low Voltage CMOS Logic Circuits AnalysisDocument5 paginiA New Approach Ultra Low Voltage CMOS Logic Circuits AnalysisijsretÎncă nu există evaluări

- Nmos and Pmos Plot Using VlsiDocument13 paginiNmos and Pmos Plot Using VlsiSaathvik R KhatavkarÎncă nu există evaluări

- Modified Z-Source Single-Phase Inverter For Single-Phase PM Synchronous Motor DrivesDocument6 paginiModified Z-Source Single-Phase Inverter For Single-Phase PM Synchronous Motor DrivesPRACHI KATAREÎncă nu există evaluări

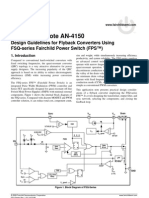

- Application Note AN-4150: Design Guidelines For Flyback Converters Using FSQ-series Fairchild Power Switch (FPS™)Document16 paginiApplication Note AN-4150: Design Guidelines For Flyback Converters Using FSQ-series Fairchild Power Switch (FPS™)Nagendra ChaitanyaÎncă nu există evaluări

- IV. Field Effect Transistor CompleteDocument42 paginiIV. Field Effect Transistor Completegarlic breadÎncă nu există evaluări

- Novel, Switch, Z-Source Three-Phase InverterDocument6 paginiNovel, Switch, Z-Source Three-Phase InverterJanjanam PraveenÎncă nu există evaluări

- Simulation of A Buck Converter Controller Based On A Hardware and Software PSM Mode ControlDocument8 paginiSimulation of A Buck Converter Controller Based On A Hardware and Software PSM Mode ControlIJIRAE- International Journal of Innovative Research in Advanced EngineeringÎncă nu există evaluări

- Group4 EECS511 Huang&SuDocument5 paginiGroup4 EECS511 Huang&SuDivya ReddyÎncă nu există evaluări

- A Novel Space Vector Modulation (SVM) Controlled Inverter For Adjustable Speed Drive ApplicationsDocument9 paginiA Novel Space Vector Modulation (SVM) Controlled Inverter For Adjustable Speed Drive ApplicationsInternational Journal of Engineering Inventions (IJEI)Încă nu există evaluări

- Permanent Magnet Synchronous Motor Drive Based On Maximum Boost Control Z-Source SVPWMDocument8 paginiPermanent Magnet Synchronous Motor Drive Based On Maximum Boost Control Z-Source SVPWMQamilÎncă nu există evaluări

- Vlsi Lab Report FinalDocument5 paginiVlsi Lab Report FinalvenkiÎncă nu există evaluări

- High Speed, Low Power Current Comparators With Hysteresis: Neeraj K. ChastaDocument12 paginiHigh Speed, Low Power Current Comparators With Hysteresis: Neeraj K. ChastanengsintanovitaÎncă nu există evaluări

- Cmos Comparator: Term Paper Eem-511: Analog Electronics DesignDocument11 paginiCmos Comparator: Term Paper Eem-511: Analog Electronics Designvipul4792Încă nu există evaluări

- Assignment 1 Digital IC DesignDocument2 paginiAssignment 1 Digital IC DesignsidhjajÎncă nu există evaluări

- 11 Chapter03 PDFDocument13 pagini11 Chapter03 PDFAtulÎncă nu există evaluări

- Lpvlsi Ii UnitDocument16 paginiLpvlsi Ii UnitrakeshÎncă nu există evaluări

- Voltage-To-Frequency Converter With High Sensitivity Using all-MOS Voltage Window ComparatorDocument6 paginiVoltage-To-Frequency Converter With High Sensitivity Using all-MOS Voltage Window ComparatorThony Tho'il PrasetyoÎncă nu există evaluări

- Low Power MuxDocument4 paginiLow Power MuxPromit MandalÎncă nu există evaluări

- Current Controlled OscillatorDocument4 paginiCurrent Controlled OscillatorajaynkotiÎncă nu există evaluări

- Fikri Pratama - TRE Malam B Laporan DayaDocument7 paginiFikri Pratama - TRE Malam B Laporan Dayafikri pratamaÎncă nu există evaluări

- Low Cost Digital Signal Generation For Driving Space Vector PWM InverterDocument12 paginiLow Cost Digital Signal Generation For Driving Space Vector PWM InverterJunaid AhmadÎncă nu există evaluări

- Simulation and Analysis of Bulk Driven Circuits For Low Power ApplicationsDocument4 paginiSimulation and Analysis of Bulk Driven Circuits For Low Power ApplicationsAbhishek MatÎncă nu există evaluări

- DC BiasingDocument9 paginiDC BiasingnagarajÎncă nu există evaluări

- Iscas06 Curr RefDocument4 paginiIscas06 Curr Refkareka_ccÎncă nu există evaluări

- Cmos Vlsi Vtu NotesDocument51 paginiCmos Vlsi Vtu NotesDwaraka Oruganti100% (2)

- 1.a.characteristics of MOSFETDocument8 pagini1.a.characteristics of MOSFETSamudrala SrikarÎncă nu există evaluări

- Lab 9 XDocument11 paginiLab 9 XNandita GuptaÎncă nu există evaluări

- Analog Integrated Circuits & Technology (EC 305) : Differential Amplifier With Passive Load and Its Detail AnalysisDocument13 paginiAnalog Integrated Circuits & Technology (EC 305) : Differential Amplifier With Passive Load and Its Detail AnalysisAbir HoqueÎncă nu există evaluări

- Linear: CMOS Voltage-to-Current ConverterDocument4 paginiLinear: CMOS Voltage-to-Current ConverterdycsteiznÎncă nu există evaluări

- Low Noise GaAs FET/BJT VCODocument8 paginiLow Noise GaAs FET/BJT VCOsanjeevsoni64Încă nu există evaluări

- All MOS - Voltage To Current - ConverterDocument5 paginiAll MOS - Voltage To Current - ConverterAram ShishmanyanÎncă nu există evaluări

- Paper 2 - PEL20120014 - 2ndDocument5 paginiPaper 2 - PEL20120014 - 2ndSherif M. DabourÎncă nu există evaluări

- Lecture - MOS & MOSFET-1Document21 paginiLecture - MOS & MOSFET-1Kartika MunirÎncă nu există evaluări

- An-978 HV Floating MOS Gate DriversDocument21 paginiAn-978 HV Floating MOS Gate DriversPeter RueÎncă nu există evaluări

- CMOS InverterDocument15 paginiCMOS Inverterمصطفى عادل أصغر حسن العبيديÎncă nu există evaluări

- SLIIT 3rd YearDocument8 paginiSLIIT 3rd YearchamilÎncă nu există evaluări

- Absolute-Value Circuit Using JunctionDocument4 paginiAbsolute-Value Circuit Using JunctionxongassilvaÎncă nu există evaluări

- 1 To 5 ManualDocument30 pagini1 To 5 ManualRoshan DodiyaÎncă nu există evaluări

- Implementation of SVPWM Control On FPGA For Three Phase MATRIX CONVERTERDocument6 paginiImplementation of SVPWM Control On FPGA For Three Phase MATRIX CONVERTERIDESÎncă nu există evaluări

- A Novel Scheme To Eliminate Common Mode Voltage in Multilevel InvertersDocument4 paginiA Novel Scheme To Eliminate Common Mode Voltage in Multilevel InvertersJavier MaldonadoÎncă nu există evaluări

- Design and Implementation of Space Vector PWM Inverter Based On A Low Cost MicrocontrollerDocument12 paginiDesign and Implementation of Space Vector PWM Inverter Based On A Low Cost MicrocontrollerHaider NeamaÎncă nu există evaluări

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1De la EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Evaluare: 2.5 din 5 stele2.5/5 (3)

- VSC-FACTS-HVDC: Analysis, Modelling and Simulation in Power GridsDe la EverandVSC-FACTS-HVDC: Analysis, Modelling and Simulation in Power GridsÎncă nu există evaluări

- Modern Control of DC-Based Power Systems: A Problem-Based ApproachDe la EverandModern Control of DC-Based Power Systems: A Problem-Based ApproachÎncă nu există evaluări

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2De la EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Încă nu există evaluări

- Lamda Rules Layout TutorialDocument15 paginiLamda Rules Layout TutorialSougata GhoshÎncă nu există evaluări

- Montecarlo PDFDocument7 paginiMontecarlo PDFSougata GhoshÎncă nu există evaluări

- Quick Start PDFDocument1 paginăQuick Start PDFSougata GhoshÎncă nu există evaluări

- Abstract-The Enhancement of Recycling Folded Cascode (RFC)Document2 paginiAbstract-The Enhancement of Recycling Folded Cascode (RFC)Sougata GhoshÎncă nu există evaluări

- IIT Kanpur L20 - Class - AB PDFDocument33 paginiIIT Kanpur L20 - Class - AB PDFSougata GhoshÎncă nu există evaluări

- CCPastStatement03 12 2018 PDFDocument1 paginăCCPastStatement03 12 2018 PDFSougata GhoshÎncă nu există evaluări

- JFET Characteristics PDFDocument9 paginiJFET Characteristics PDFSougata GhoshÎncă nu există evaluări

- How To Have A Healthy BabyDocument5 paginiHow To Have A Healthy BabySougata GhoshÎncă nu există evaluări

- 7th LessonDocument54 pagini7th LessonSougata GhoshÎncă nu există evaluări

- Simulation Lab FileDocument42 paginiSimulation Lab FileSougata GhoshÎncă nu există evaluări

- Chapter - 3Document40 paginiChapter - 3Sougata Ghosh100% (1)

- 1501137243609Document2 pagini1501137243609Sougata Ghosh0% (1)

- 03amplitude ModulationDocument50 pagini03amplitude ModulationSougata GhoshÎncă nu există evaluări

- Chapter - 2Document14 paginiChapter - 2Sougata GhoshÎncă nu există evaluări

- Question Bank DSP EEC-602Document3 paginiQuestion Bank DSP EEC-602Sougata GhoshÎncă nu există evaluări

- Question Bank Vlsi Design MEC-020Document2 paginiQuestion Bank Vlsi Design MEC-020Sougata GhoshÎncă nu există evaluări

- Question Bank Vlsi Technology Eec-604Document2 paginiQuestion Bank Vlsi Technology Eec-604Sougata Ghosh100% (1)

- Chapter - 4Document58 paginiChapter - 4Sougata GhoshÎncă nu există evaluări

- DSP Classtest AnswerDocument5 paginiDSP Classtest AnswerSougata GhoshÎncă nu există evaluări

- DSP 20 QuestionsDocument2 paginiDSP 20 QuestionsSougata GhoshÎncă nu există evaluări

- Lic Eec-501 Notes Unit5 Iftm UniversityDocument14 paginiLic Eec-501 Notes Unit5 Iftm UniversitySougata GhoshÎncă nu există evaluări

- DSP 10 QuestionsDocument1 paginăDSP 10 QuestionsSougata GhoshÎncă nu există evaluări

- Pulse & Digital Circuits by K.Venkata Rao, K Rama Sudha & G Manmadha Rao, Pearson Education, 2010. (Selected Portions)Document1 paginăPulse & Digital Circuits by K.Venkata Rao, K Rama Sudha & G Manmadha Rao, Pearson Education, 2010. (Selected Portions)Sougata GhoshÎncă nu există evaluări

- 8.ZXSDR B8200 (L200) Principle and Hardware Structure Training Manual-45Document45 pagini8.ZXSDR B8200 (L200) Principle and Hardware Structure Training Manual-45mehdi_mehdiÎncă nu există evaluări

- User S Manual AURORA 1.2K - 2.2KDocument288 paginiUser S Manual AURORA 1.2K - 2.2KEprom ServisÎncă nu există evaluări

- OZO Player SDK User Guide 1.2.1Document16 paginiOZO Player SDK User Guide 1.2.1aryan9411Încă nu există evaluări

- Deal Report Feb 14 - Apr 14Document26 paginiDeal Report Feb 14 - Apr 14BonviÎncă nu există evaluări

- Working Capital in YamahaDocument64 paginiWorking Capital in YamahaRenu Jindal50% (2)

- LM74680 Fasson® Fastrans NG Synthetic PE (ST) / S-2050/ CK40Document2 paginiLM74680 Fasson® Fastrans NG Synthetic PE (ST) / S-2050/ CK40Nishant JhaÎncă nu există evaluări

- BNF Pos - StockmockDocument14 paginiBNF Pos - StockmockSatish KumarÎncă nu există evaluări

- Rockaway Times 11818Document40 paginiRockaway Times 11818Peter J. MahonÎncă nu există evaluări

- The JHipster Mini Book 2Document129 paginiThe JHipster Mini Book 2tyulist100% (1)

- DQ Vibro SifterDocument13 paginiDQ Vibro SifterDhaval Chapla67% (3)

- PyhookDocument23 paginiPyhooktuan tuanÎncă nu există evaluări

- Stearns 87700 Series Parts ListDocument4 paginiStearns 87700 Series Parts ListYorkistÎncă nu există evaluări

- Recommendations For Students With High Functioning AutismDocument7 paginiRecommendations For Students With High Functioning AutismLucia SaizÎncă nu există evaluări

- Presentation 11Document14 paginiPresentation 11stellabrown535Încă nu există evaluări

- Stress-Strain Modelfor Grade275 Reinforcingsteel With Cyclic LoadingDocument9 paginiStress-Strain Modelfor Grade275 Reinforcingsteel With Cyclic LoadingRory Cristian Cordero RojoÎncă nu există evaluări

- QP December 2006Document10 paginiQP December 2006Simon ChawingaÎncă nu există evaluări

- PMP Question BankDocument3 paginiPMP Question BankOmerZiaÎncă nu există evaluări

- Linguistics Is Descriptive, Not Prescriptive.: Prescriptive Grammar. Prescriptive Rules Tell You HowDocument2 paginiLinguistics Is Descriptive, Not Prescriptive.: Prescriptive Grammar. Prescriptive Rules Tell You HowMonette Rivera Villanueva100% (1)

- Activity # 1 (DRRR)Document2 paginiActivity # 1 (DRRR)Juliana Xyrelle FutalanÎncă nu există evaluări

- Mcdonald 2016Document10 paginiMcdonald 2016Andrika SaputraÎncă nu există evaluări

- Salads: 300 Salad Recipes For Rapid Weight Loss & Clean Eating (PDFDrive) PDFDocument1.092 paginiSalads: 300 Salad Recipes For Rapid Weight Loss & Clean Eating (PDFDrive) PDFDebora PanzarellaÎncă nu există evaluări

- Agco Serie 800 PDFDocument24 paginiAgco Serie 800 PDFJohnny VargasÎncă nu există evaluări

- Article An Incident and Injury Free Culture Changing The Face of Project Operations Terra117 2Document6 paginiArticle An Incident and Injury Free Culture Changing The Face of Project Operations Terra117 2nguyenthanhtuan_ecoÎncă nu există evaluări

- Jesus Prayer-JoinerDocument13 paginiJesus Prayer-Joinersleepknot_maggotÎncă nu există evaluări

- Grade 7 ExamDocument3 paginiGrade 7 ExamMikko GomezÎncă nu există evaluări

- Manual s10 PDFDocument402 paginiManual s10 PDFLibros18Încă nu există evaluări

- Elements of ArtDocument1 paginăElements of Artsamson8cindy8louÎncă nu există evaluări

- Chapter13 PDFDocument34 paginiChapter13 PDFAnastasia BulavinovÎncă nu există evaluări

- Rule 113 114Document7 paginiRule 113 114Shaila GonzalesÎncă nu există evaluări

- Mcom Sem 4 Project FinalDocument70 paginiMcom Sem 4 Project Finallaxmi iyer75% (4)