Documente Academic

Documente Profesional

Documente Cultură

74HC564 PDF

Încărcat de

ZoneM3Descriere originală:

Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

74HC564 PDF

Încărcat de

ZoneM3Drepturi de autor:

Formate disponibile

74HC564

Octal D-type flip-flop; positive-edge trigger; 3-state; inverting

Rev. 03 11 November 2004

Product data sheet

1. General description

The 74HC564 is a high-speed Si-gate CMOS device and is pin compatible with low-power

Schottky TTL (LSTTL). The 74HC564 is specified in compliance with JEDEC

standard no. 7A.

The 74HC564 is a octal D-type flip-flop featuring separate D-type inputs for each flip-flop

and inverting 3-state outputs for bus oriented applications. A clock (CP) and an output

enable (OE) input are common to all flip-flops.

The 8 flip-flops will store the state of their individual D-inputs that meet the set-up and hold

times requirements on the LOW-to-HIGH CP transition. When OE is LOW, the contents of

the 8 flip-flops are available at the outputs. When OE is HIGH, the outputs go to the

high-impedance OFF-state. Operation of the OE input does not affect the state of the

flip-flops.

The 74HC564 is functionally identical to the 74HC574 but has inverting outputs. The

74HC564 is functionally identical to the 74HC534, but has a different pinning.

2. Features

3-state inverting outputs for bus oriented applications

8-bit positive-edge triggered register

Common 3-state output enable input

Independent register and 3-state buffer operation

Low-power dissipation

Complies with JEDEC standard no. 7A

ESD protection:

HBM EIA/JESD22-A114-B exceeds 2000 V

MM EIA/JESD22-A115-A exceeds 200 V.

Multiple package options

Specified from 40 C to +80 C and from 40 C to +125 C.

74HC564

Philips Semiconductors

Octal D-type flip-flop; positive-edge trigger; 3-state; inverting

3. Quick reference data

Table 1:

Quick reference data

GND = 0 V; Tamb = 25 C; tr = tf = 6 ns.

Symbol

Parameter

tPHL, tPLH

Min

Typ

Max

Unit

propagation delay CP CL = 15 pF;

to Qn

VCC = 5 V

15

ns

fmax

maximum clock

frequency

127

MHz

CI

input capacitance

3.5

pF

27

pF

power dissipation

capacitance per

flip-flop

CPD

[1]

Conditions

CL = 15 pF;

VCC = 5 V

VI = GND to VCC

[1]

CPD is used to determine the dynamic power dissipation (PD in W).

PD = CPD VCC2 fi N + (CL VCC2 fo) where:

fi = input frequency in MHz;

fo = output frequency in MHz;

CL = output load capacitance in pF;

VCC = supply voltage in V;

N = number of inputs switching;

(CL VCC2 fo) = sum of outputs.

4. Ordering information

Table 2:

Ordering information

Type number

Package

Temperature range

Name

Description

Version

74HC564N

40 C to +125 C

DIP20

plastic dual in-line package; 20 leads (300 mil)

SOT146-1

74HC564D

40 C to +125 C

SO20

plastic small outline package; 20 leads;

body width 7.5 mm

SOT163-1

9397 750 13814

Product data sheet

Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Rev. 03 11 November 2004

2 of 18

74HC564

Philips Semiconductors

Octal D-type flip-flop; positive-edge trigger; 3-state; inverting

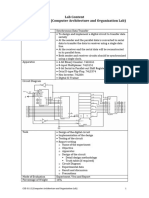

5. Functional diagram

2 D0

Q0 19

3 D1

Q1 18

4 D2

Q2 17

Q3 16

5 D3

FF1 TO

FF8

6 D4

3 STATE

OUTPUTS

Q4 15

7 D5

Q5 14

8 D6

Q6 13

9 D7

Q7 12

11 CP

1 OE

001aab936

Fig 1. Functional diagram

1

11

2

3

4

5

6

7

8

9

11

CP

D0

Q0

D1

Q1

D2

Q2

D3

Q3

D4

Q4

D5

Q5

D6

Q6

D7

Q7

EN

C1

19

18

17

18

16

17

16

15

14

13

12

15

19

1D

14

13

12

OE

1

001aab934

001aab935

Fig 2. Logic symbol

9397 750 13814

Product data sheet

Fig 3. IEC logic symbol

Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Rev. 03 11 November 2004

3 of 18

74HC564

Philips Semiconductors

Octal D-type flip-flop; positive-edge trigger; 3-state; inverting

D0

D1

D2

CP

CP

FF

1

CP

FF

2

D4

D3

CP

FF

3

D5

CP

FF

4

CP

FF

5

D7

D6

CP

FF

6

CP

FF

7

FF

8

CP

OE

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

001aab937

Fig 4. Logic diagram

6. Pinning information

6.1 Pinning

OE

20 VCC

D0

19 Q0

D1

18 Q1

D2

17 Q2

D3

16 Q3

564

D4

15 Q4

D5

14 Q5

D6

13 Q6

D7

12 Q7

GND 10

11 CP

001aab844

Fig 5. Pin configuration

9397 750 13814

Product data sheet

Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Rev. 03 11 November 2004

4 of 18

74HC564

Philips Semiconductors

Octal D-type flip-flop; positive-edge trigger; 3-state; inverting

6.2 Pin description

Table 3:

Pin description

Symbol

Pin

Description

OE

3-state output enable input (active LOW)

D0

data input 0

D1

data input 1

D2

data input 2

D3

data input 3

D4

data input 4

D5

data input 5

D6

data input 6

D7

data input 7

GND

10

ground (0 V)

CP

11

clock input (LOW-to-HIGH, edge-triggered)

Q7

12

3-state flip-flop output 7

Q6

13

3-state flip-flop output 6

Q5

14

3-state flip-flop output 5

Q4

15

3-state flip-flop output 4

Q3

16

3-state flip-flop output 3

Q2

17

3-state flip-flop output 2

Q1

18

3-state flip-flop output 1

Q0

19

3-state flip-flop output 0

VCC

20

positive supply voltage

7. Functional description

7.1 Function table

Table 4:

Function table [1]

Operating mode

Input

OE

CP

Load and read

register

Load register and

disable output

[1]

Qn

H = HIGH voltage level;

h = HIGH voltage level one set-up time prior to the LOW-to-HIGH CP transition;

L = LOW voltage level;

l = LOW voltage level one set-up time prior to the LOW-to-HIGH CP transition;

Z = high-impedance OFF-state;

= LOW-to-HIGH clock transition.

9397 750 13814

Product data sheet

Output

Dn

Internal

flip-flop

Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Rev. 03 11 November 2004

5 of 18

74HC564

Philips Semiconductors

Octal D-type flip-flop; positive-edge trigger; 3-state; inverting

8. Limiting values

Table 5:

Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to

GND (ground = 0 V).

Symbol

Parameter

Conditions

Min

Max

Unit

VCC

supply voltage

IIK

input diode current

VI < 0.5 V or VI > VCC + 0.5 V

0.5

+7

20

mA

IOK

output diode current

VO < 0.5 V or

VO > VCC + 0.5 V

20

mA

IO

output source or sink

current

VO = 0.5 V to VCC + 0.5 V

35

mA

ICC, IGND

VCC or GND current

70

mA

Tstg

storage temperature

65

+150

Ptot

power dissipation

DIP20 package

[1]

750

mW

SO20 package

[2]

500

mW

[1]

Above 70 C: Ptot derates linearly with 12 mW/K.

[2]

Above 70 C: Ptot derates linearly with 8 mW/K.

9. Recommended operating conditions

Table 6:

Recommended operating conditions

Symbol

Parameter

VCC

supply voltage

VI

input voltage

VO

output voltage

tr, tf

input rise and fall times

VCC = 2.0 V

VCC = 4.5 V

VCC = 6.0 V

Tamb

Conditions

ambient temperature

9397 750 13814

Product data sheet

Min

Typ

Max

Unit

2.0

5.0

6.0

VCC

VCC

1000

ns

6.0

500

ns

400

ns

40

+125

Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Rev. 03 11 November 2004

6 of 18

74HC564

Philips Semiconductors

Octal D-type flip-flop; positive-edge trigger; 3-state; inverting

10. Static characteristics

Table 7:

Static characteristics

At recommended operating conditions; voltages are referenced to GND (ground = 0 V).

Symbol

Parameter

Conditions

Min

Typ

Max

Unit

Tamb = 25 C

VIH

VIL

VOH

VOL

HIGH-level input voltage

LOW-level input voltage

HIGH-level output voltage

LOW-level output voltage

VCC = 2.0 V

1.5

1.2

VCC = 4.5 V

3.15 2.4

VCC = 6.0 V

4.2

3.2

VCC = 2.0 V

0.8

0.5

VCC = 4.5 V

2.1

1.35

VCC = 6.0 V

2.8

1.8

IO = 20 A; VCC = 2.0 V

1.9

2.0

IO = 20 A; VCC = 4.5 V

4.4

4.5

IO = 20 A; VCC = 6.0 V

5.9

6.0

IO = 6.0 mA; VCC = 4.5 V

3.98 4.32 -

IO = 7.8 mA; VCC = 6.0 V

5.48 5.81 -

IO = 20 A; VCC = 2.0 V

0.1

IO = 20 A; VCC = 4.5 V

0.1

IO = 20 A; VCC = 6.0 V

0.1

IO = 6.0 mA; VCC = 4.5 V

0.15 0.26

IO = 7.8 mA; VCC = 6.0 V

0.16 0.26

VI = VIH or VIL

VI = VIH or VIL

ILI

input leakage current

VI = VCC or GND; VCC = 6.0 V

0.1

IOZ

3-state OFF-state current

VI = VIH or VIL; VCC = 6.0 V; VO = VCC or GND

0.5

ICC

quiescent supply current

VI = VCC or GND; IO = 0 A; VCC = 6.0 V

CI

input capacitance

8.0

3.5

pF

VCC = 2.0 V

1.5

VCC = 4.5 V

3.15 -

VCC = 6.0 V

4.2

VCC = 2.0 V

0.5

VCC = 4.5 V

1.35

VCC = 6.0 V

1.8

IO = 20 A; VCC = 2.0 V

1.9

IO = 20 A; VCC = 4.5 V

4.4

IO = 20 A; VCC = 6.0 V

5.9

IO = 6.0 mA; VCC = 4.5 V

3.84 -

IO = 7.8 mA; VCC = 6.0 V

5.34 -

Tamb = 40 C to +85 C

VIH

VIL

VOH

HIGH-level input voltage

LOW-level input voltage

HIGH-level output voltage

VI = VIH or VIL

9397 750 13814

Product data sheet

Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Rev. 03 11 November 2004

7 of 18

74HC564

Philips Semiconductors

Octal D-type flip-flop; positive-edge trigger; 3-state; inverting

Table 7:

Static characteristics continued

At recommended operating conditions; voltages are referenced to GND (ground = 0 V).

Symbol

Parameter

Conditions

Min

Typ

Max

Unit

VOL

LOW-level output voltage

VI = VIH or VIL

IO = 20 A; VCC = 2.0 V

0.1

IO = 20 A; VCC = 4.5 V

0.1

IO = 20 A; VCC = 6.0 V

0.1

IO = 6.0 mA; VCC = 4.5 V

0.33

IO = 7.8 mA; VCC = 6.0 V

0.33

ILI

input leakage current

VI = VCC or GND; VCC = 6.0 V

1.0

IOZ

3-state OFF-state current

VI = VIH or VIL; VCC = 6.0 V; VO = VCC or GND

5.0

ICC

quiescent supply current

VI = VCC or GND; IO = 0 A; VCC = 6.0 V

80

Tamb = 40 C to +125 C

VIH

VIL

VOH

VOL

HIGH-level input voltage

LOW-level input voltage

HIGH-level output voltage

LOW-level output voltage

VCC = 2.0 V

1.5

VCC = 4.5 V

3.15 -

VCC = 6.0 V

4.2

VCC = 2.0 V

0.5

VCC = 4.5 V

1.35

VCC = 6.0 V

1.8

VI = VIH or VIL

IO = 20 A; VCC = 2.0 V

1.9

IO = 20 A; VCC = 4.5 V

4.4

IO = 20 A; VCC = 6.0 V

5.9

IO = 6.0 mA; VCC = 4.5 V

3.7

IO = 7.8 mA; VCC = 6.0 V

5.2

IO = 20 A; VCC = 2.0 V

0.1

IO = 20 A; VCC = 4.5 V

0.1

IO = 20 A; VCC = 6.0 V

0.1

IO = 6.0 mA; VCC = 4.5 V

0.4

IO = 7.8 mA; VCC = 6.0 V

0.4

V

A

VI = VIH or VIL

ILI

input leakage current

VI = VCC or GND; VCC = 6.0 V

1.0

IOZ

3-state OFF-state current

VI = VIH or VIL; VCC = 6.0 V; VO = VCC or GND

10.0 A

ICC

quiescent supply current

VI = VCC or GND; IO = 0 A; VCC = 6.0 V

160

9397 750 13814

Product data sheet

Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Rev. 03 11 November 2004

8 of 18

74HC564

Philips Semiconductors

Octal D-type flip-flop; positive-edge trigger; 3-state; inverting

11. Dynamic characteristics

Table 8:

Dynamic characteristics

GND = 0 V; tr = tf = 6 ns; CL = 50 pF; see Figure 9.

Symbol

Parameter

Conditions

Min

Typ

Max

Unit

VCC = 2.0 V

50

165

ns

VCC = 4.5 V

18

33

ns

VCC = 6.0 V

14

28

ns

VCC = 5.0 V; CL = 15 pF

15

ns

VCC = 2.0 V

44

140

ns

VCC = 4.5 V

16

28

ns

VCC = 6.0 V

13

24

ns

VCC = 2.0 V

50

135

ns

VCC = 4.5 V

18

27

ns

VCC = 6.0 V

14

23

ns

VCC = 2.0 V

14

60

ns

VCC = 4.5 V

12

ns

VCC = 6.0 V

10

ns

VCC = 2.0 V

80

14

ns

VCC = 4.5 V

16

ns

VCC = 6.0 V

14

ns

VCC = 2.0 V

60

ns

VCC = 4.5 V

12

ns

VCC = 6.0 V

10

ns

VCC = 2.0 V

ns

VCC = 4.5 V

ns

VCC = 6.0 V

ns

VCC = 2.0 V

6.0

38

MHz

VCC = 4.5 V

30

115

MHz

Tamb = 25 C

tPHL, tPLH propagation delay CP to Qn

tPZH, tPZL

tPHZ, tPLZ

tTHL, tTLH

tW

tsu

th

fmax

CPD

3-state output enable time OE to Qn

3-state output disable time OE to Qn

output transition time

CP clock pulse width HIGH or LOW

set-up time Dn to CP

hold time Dn to CP

maximum clock frequency

see Figure 6

see Figure 7

see Figure 7

see Figure 6

see Figure 6

see Figure 8

see Figure 8

see Figure 6

VCC = 6.0 V

35

137

MHz

VCC = 5.0 V; CL = 15 pF

127

MHz

27

pF

power dissipation capacitance per flip-flop VI = GND to VCC

9397 750 13814

Product data sheet

[1]

Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Rev. 03 11 November 2004

9 of 18

74HC564

Philips Semiconductors

Octal D-type flip-flop; positive-edge trigger; 3-state; inverting

Table 8:

Dynamic characteristics continued

GND = 0 V; tr = tf = 6 ns; CL = 50 pF; see Figure 9.

Symbol

Parameter

Conditions

Min

Typ

Max

Unit

Tamb = 40 C to +85 C

tPHL, tPLH propagation delay CP to Qn

tPZH, tPZL

tPHZ, tPLZ

tTHL, tTLH

tW

tsu

th

fmax

3-state output enable time OE to Qn

3-state output disable time OE to Qn

output transition time

CP clock pulse width HIGH or LOW

set-up time Dn to CP

hold time Dn to CP

maximum clock frequency

see Figure 6

VCC = 2.0 V

205

ns

VCC = 4.5 V

41

ns

VCC = 6.0 V

35

ns

see Figure 7

VCC = 2.0 V

175

ns

VCC = 4.5 V

35

ns

VCC = 6.0 V

30

ns

see Figure 7

VCC = 2.0 V

170

ns

VCC = 4.5 V

34

ns

VCC = 6.0 V

29

ns

see Figure 6

VCC = 2.0 V

75

ns

VCC = 4.5 V

15

ns

VCC = 6.0 V

13

ns

see Figure 6

VCC = 2.0 V

100

ns

VCC = 4.5 V

20

ns

VCC = 6.0 V

17

ns

see Figure 8

VCC = 2.0 V

75

ns

VCC = 4.5 V

15

ns

VCC = 6.0 V

13

ns

see Figure 8

VCC = 2.0 V

ns

VCC = 4.5 V

ns

VCC = 6.0 V

ns

see Figure 6

VCC = 2.0 V

4.8

MHz

VCC = 4.5 V

24

MHz

VCC = 6.0 V

28

MHz

9397 750 13814

Product data sheet

Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Rev. 03 11 November 2004

10 of 18

74HC564

Philips Semiconductors

Octal D-type flip-flop; positive-edge trigger; 3-state; inverting

Table 8:

Dynamic characteristics continued

GND = 0 V; tr = tf = 6 ns; CL = 50 pF; see Figure 9.

Symbol

Parameter

Conditions

Min

Typ

Max

Unit

Tamb = 40 C to +125 C

tPHL, tPLH propagation delay CP to Qn

tPZH, tPZL

tPHZ, tPLZ

tTHL, tTLH

3-state output disable time OE to Qn

output transition time

CP clock pulse width HIGH or LOW

tW

set-up time Dn to CP

tsu

hold time Dn to CP

th

maximum clock frequency

fmax

[1]

3-state output enable time OE to Qn

see Figure 6

VCC = 2.0 V

250

ns

VCC = 4.5 V

50

ns

VCC = 6.0 V

43

ns

see Figure 7

VCC = 2.0 V

210

ns

VCC = 4.5 V

42

ns

VCC = 6.0 V

36

ns

see Figure 7

VCC = 2.0 V

205

ns

VCC = 4.5 V

41

ns

VCC = 6.0 V

35

ns

see Figure 6

VCC = 2.0 V

90

ns

VCC = 4.5 V

18

ns

VCC = 6.0 V

15

ns

see Figure 6

VCC = 2.0 V

120

ns

VCC = 4.5 V

24

ns

VCC = 6.0 V

20

ns

see Figure 8

VCC = 2.0 V

90

ns

VCC = 4.5 V

18

ns

VCC = 6.0 V

15

ns

see Figure 8

VCC = 2.0 V

ns

VCC = 4.5 V

ns

VCC = 6.0 V

ns

see Figure 6

VCC = 2.0 V

4.0

MHz

VCC = 4.5 V

20

MHz

VCC = 6.0 V

24

MHz

CPD is used to determine the dynamic power dissipation (PD in W).

PD = CPD VCC2 fi N + (CL VCC2 fo) where:

fi = input frequency in MHz;

fo = output frequency in MHz;

CL = output load capacitance in pF;

VCC = supply voltage in V;

N = number of inputs switching;

(CL VCC2 fo) = sum of outputs.

9397 750 13814

Product data sheet

Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Rev. 03 11 November 2004

11 of 18

74HC564

Philips Semiconductors

Octal D-type flip-flop; positive-edge trigger; 3-state; inverting

12. Waveforms

1/fmax

CP input

VM

tW

tPHL

Qn output

tPLH

VM

tTHL

tTLH

001aab938

VM = 0.5 VI.

Fig 6. Waveforms showing the clock (CP) to output (Qn) propagation delays, the clock

pulse width, the output transition times and the maximum clock frequency

tr

OE input

10 %

tf

90 %

VM

tPLZ

output

LOW to OFF

OFF to LOW

tPZL

VM

10 %

tPHZ

tPZH

90 %

output

HIGH to OFF

OFF to HIGH

VM

outputs

enabled

outputs

enabled

outputs

disabled

001aab940

VM = 0.5 VI.

Fig 7. Waveforms showing the 3-state enable and disable times

9397 750 13814

Product data sheet

Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Rev. 03 11 November 2004

12 of 18

74HC564

Philips Semiconductors

Octal D-type flip-flop; positive-edge trigger; 3-state; inverting

VM

CP input

tsu

tsu

th

th

VM

Dn input

VM

Qn input

001aab939

The shaded areas indicate when the input is permitted to change for predictable output

performance.

VM = 0.5 VI.

Fig 8. Waveforms showing the data set-up and hold times for the data input (Dn)

S1

VCC

PULSE

GENERATOR

VI

RL =

1000

VO

VCC

open

GND

D.U.T.

CL

RT

mna232

Test data is given in Table 9.

Definitions for test circuit:

RL = Load resistor.

CL = Load capacitance including jig and probe capacitance.

RT = Termination resistance should be equal to the output impedance Zo of the pulse

generator.

Fig 9. Load circuitry for switching times

Table 9:

Test data

Supply

Input

Load

S1

VCC

VI

tr = tf

CL

RL

tPZL, tPLZ

tPZH, tPHZ

tPHL, tPLH

2.0 V

VCC

6 ns

50 pF

1 k

VCC

GND

open

4.5 V

VCC

6 ns

50 pF

1 k

VCC

GND

open

6.0 V

VCC

6 ns

50 pF

1 k

VCC

GND

open

5.0 V

VCC

6 ns

15 pF

1 k

VCC

GND

open

9397 750 13814

Product data sheet

Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Rev. 03 11 November 2004

13 of 18

74HC564

Philips Semiconductors

Octal D-type flip-flop; positive-edge trigger; 3-state; inverting

13. Package outline

DIP20: plastic dual in-line package; 20 leads (300 mil)

SOT146-1

ME

seating plane

A2

A1

c

e

b1

w M

(e 1)

b

MH

11

20

pin 1 index

E

10

10 mm

scale

DIMENSIONS (inch dimensions are derived from the original mm dimensions)

UNIT

A

max.

A1

min.

A2

max.

b1

mm

4.2

0.51

3.2

1.73

1.30

0.53

0.38

0.36

0.23

26.92

26.54

inches

0.17

0.02

0.13

0.068

0.051

0.021

0.015

0.014

0.009

1.060

1.045

e1

ME

MH

Z (1)

max.

6.40

6.22

2.54

7.62

3.60

3.05

8.25

7.80

10.0

8.3

0.254

0.25

0.24

0.1

0.3

0.14

0.12

0.32

0.31

0.39

0.33

0.01

0.078

(1)

(1)

Note

1. Plastic or metal protrusions of 0.25 mm (0.01 inch) maximum per side are not included.

OUTLINE

VERSION

SOT146-1

REFERENCES

IEC

JEDEC

JEITA

MS-001

SC-603

EUROPEAN

PROJECTION

ISSUE DATE

99-12-27

03-02-13

Fig 10. Package outline SOT146-1 (DIP20)

9397 750 13814

Product data sheet

Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Rev. 03 11 November 2004

14 of 18

74HC564

Philips Semiconductors

Octal D-type flip-flop; positive-edge trigger; 3-state; inverting

SO20: plastic small outline package; 20 leads; body width 7.5 mm

SOT163-1

A

X

c

HE

v M A

Z

20

11

Q

A2

(A 3)

A1

pin 1 index

Lp

L

10

1

e

bp

detail X

w M

10 mm

scale

DIMENSIONS (inch dimensions are derived from the original mm dimensions)

UNIT

A

max.

A1

A2

A3

bp

D (1)

E (1)

HE

Lp

mm

2.65

0.3

0.1

2.45

2.25

0.25

0.49

0.36

0.32

0.23

13.0

12.6

7.6

7.4

1.27

10.65

10.00

1.4

1.1

0.4

1.1

1.0

0.25

0.25

0.1

0.01

0.019 0.013

0.014 0.009

0.51

0.49

0.30

0.29

0.05

0.419

0.043

0.055

0.394

0.016

inches

0.1

0.012 0.096

0.004 0.089

0.043

0.039

0.01

0.01

(1)

0.9

0.4

0.035

0.004

0.016

8

o

0

Note

1. Plastic or metal protrusions of 0.15 mm (0.006 inch) maximum per side are not included.

REFERENCES

OUTLINE

VERSION

IEC

JEDEC

SOT163-1

075E04

MS-013

JEITA

EUROPEAN

PROJECTION

ISSUE DATE

99-12-27

03-02-19

Fig 11. Package outline SOT163-1 (SO20)

9397 750 13814

Product data sheet

Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Rev. 03 11 November 2004

15 of 18

74HC564

Philips Semiconductors

Octal D-type flip-flop; positive-edge trigger; 3-state; inverting

14. Revision history

Table 10:

Revision history

Document ID

Release

date

74HC564_3

20041111 Product data sheet

Modifications:

Data sheet status

Change notice Doc. number

-

Supersedes

9397 750 13814 74HC_HCT564_CNV_2

The format of this data sheet has been redesigned to comply with the current presentation

and information standard of Philips Semiconductors.

Removed type number 74HCT564.

Inserted family specification.

74HC_HCT564_CNV_2

19970905 Product specification

74HC_HCT564_1

74HC_HCT564_1

19901201 Product specification

9397 750 13814

Product data sheet

Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Rev. 03 11 November 2004

16 of 18

74HC564

Philips Semiconductors

Octal D-type flip-flop; positive-edge trigger; 3-state; inverting

15. Data sheet status

Level

Data sheet status [1]

Product status [2] [3]

Definition

Objective data

Development

This data sheet contains data from the objective specification for product development. Philips

Semiconductors reserves the right to change the specification in any manner without notice.

II

Preliminary data

Qualification

This data sheet contains data from the preliminary specification. Supplementary data will be published

at a later date. Philips Semiconductors reserves the right to change the specification without notice, in

order to improve the design and supply the best possible product.

III

Product data

Production

This data sheet contains data from the product specification. Philips Semiconductors reserves the

right to make changes at any time in order to improve the design, manufacturing and supply. Relevant

changes will be communicated via a Customer Product/Process Change Notification (CPCN).

[1]

Please consult the most recently issued data sheet before initiating or completing a design.

[2]

The product status of the device(s) described in this data sheet may have changed since this data sheet was published. The latest information is available on the Internet at

URL http://www.semiconductors.philips.com.

[3]

For data sheets describing multiple type numbers, the highest-level product status determines the data sheet status.

16. Definitions

17. Disclaimers

Short-form specification The data in a short-form specification is

extracted from a full data sheet with the same type number and title. For

detailed information see the relevant data sheet or data handbook.

Life support These products are not designed for use in life support

appliances, devices, or systems where malfunction of these products can

reasonably be expected to result in personal injury. Philips Semiconductors

customers using or selling these products for use in such applications do so

at their own risk and agree to fully indemnify Philips Semiconductors for any

damages resulting from such application.

Limiting values definition Limiting values given are in accordance with

the Absolute Maximum Rating System (IEC 60134). Stress above one or

more of the limiting values may cause permanent damage to the device.

These are stress ratings only and operation of the device at these or at any

other conditions above those given in the Characteristics sections of the

specification is not implied. Exposure to limiting values for extended periods

may affect device reliability.

Application information Applications that are described herein for any

of these products are for illustrative purposes only. Philips Semiconductors

make no representation or warranty that such applications will be suitable for

the specified use without further testing or modification.

Right to make changes Philips Semiconductors reserves the right to

make changes in the products - including circuits, standard cells, and/or

software - described or contained herein in order to improve design and/or

performance. When the product is in full production (status Production),

relevant changes will be communicated via a Customer Product/Process

Change Notification (CPCN). Philips Semiconductors assumes no

responsibility or liability for the use of any of these products, conveys no

license or title under any patent, copyright, or mask work right to these

products, and makes no representations or warranties that these products are

free from patent, copyright, or mask work right infringement, unless otherwise

specified.

18. Contact information

For additional information, please visit: http://www.semiconductors.philips.com

For sales office addresses, send an email to: sales.addresses@www.semiconductors.philips.com

9397 750 13814

Product data sheet

Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Rev. 03 11 November 2004

17 of 18

74HC564

Philips Semiconductors

Octal D-type flip-flop; positive-edge trigger; 3-state; inverting

19. Contents

1

2

3

4

5

6

6.1

6.2

7

7.1

8

9

10

11

12

13

14

15

16

17

18

General description . . . . . . . . . . . . . . . . . . . . . . 1

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Quick reference data . . . . . . . . . . . . . . . . . . . . . 2

Ordering information . . . . . . . . . . . . . . . . . . . . . 2

Functional diagram . . . . . . . . . . . . . . . . . . . . . . 3

Pinning information . . . . . . . . . . . . . . . . . . . . . . 4

Pinning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Pin description . . . . . . . . . . . . . . . . . . . . . . . . . 5

Functional description . . . . . . . . . . . . . . . . . . . 5

Function table . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Limiting values. . . . . . . . . . . . . . . . . . . . . . . . . . 6

Recommended operating conditions. . . . . . . . 6

Static characteristics. . . . . . . . . . . . . . . . . . . . . 7

Dynamic characteristics . . . . . . . . . . . . . . . . . . 9

Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Package outline . . . . . . . . . . . . . . . . . . . . . . . . 14

Revision history . . . . . . . . . . . . . . . . . . . . . . . . 16

Data sheet status . . . . . . . . . . . . . . . . . . . . . . . 17

Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Disclaimers . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Contact information . . . . . . . . . . . . . . . . . . . . 17

Koninklijke Philips Electronics N.V. 2004

All rights are reserved. Reproduction in whole or in part is prohibited without the prior

written consent of the copyright owner. The information presented in this document does

not form part of any quotation or contract, is believed to be accurate and reliable and may

be changed without notice. No liability will be accepted by the publisher for any

consequence of its use. Publication thereof does not convey nor imply any license under

patent- or other industrial or intellectual property rights.

Date of release: 11 November 2004

Document number: 9397 750 13814

Published in The Netherlands

S-ar putea să vă placă și

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- EEE301 Project Tic Tac Toe ReportDocument7 paginiEEE301 Project Tic Tac Toe ReportKasshaf Ahmad100% (1)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5795)

- Starter - Components - AskElectronicsDocument20 paginiStarter - Components - AskElectronicsVerne ThomysÎncă nu există evaluări

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (895)

- Service Manual: Downloaded From Manuals Search EngineDocument106 paginiService Manual: Downloaded From Manuals Search EngineManuel Gomez MerquezÎncă nu există evaluări

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- Two - Phase Clocking PDFDocument16 paginiTwo - Phase Clocking PDFVishal PhadtareÎncă nu există evaluări

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (588)

- Physics Project FileDocument14 paginiPhysics Project FileSrutanik BhaduriÎncă nu există evaluări

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (400)

- Software User's Manual: SM-8800 Multi-Function Electronic Load (10 in 1)Document57 paginiSoftware User's Manual: SM-8800 Multi-Function Electronic Load (10 in 1)Farbod Jz.Încă nu există evaluări

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- Digital Lab ManualDocument87 paginiDigital Lab ManualKALAIMATHIÎncă nu există evaluări

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- SM-4.2 Desain Rangkaian SekuensialDocument23 paginiSM-4.2 Desain Rangkaian SekuensialIda Bagus Yudistira AnggradanaÎncă nu există evaluări

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2259)

- Digitronik Digital Indicating Controller SDC10 User's ManualDocument38 paginiDigitronik Digital Indicating Controller SDC10 User's Manualntdien923Încă nu există evaluări

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (74)

- Basic Electronics 2014Document2 paginiBasic Electronics 2014Rajeswari PurushothamÎncă nu există evaluări

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- Maharashtra State Board of Technical Education: Teaching Plan (TP)Document46 paginiMaharashtra State Board of Technical Education: Teaching Plan (TP)mdwalunjkar3095100% (1)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- Digital Potentiometer AD8400 8402 8403Document32 paginiDigital Potentiometer AD8400 8402 8403Ozi ---Încă nu există evaluări

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- Coe117 Final Exam q4 2015 2016 Logic Circuits Final Exam q3 2014 2015 Problems and Answer KeyDocument3 paginiCoe117 Final Exam q4 2015 2016 Logic Circuits Final Exam q3 2014 2015 Problems and Answer KeyEugene MartinÎncă nu există evaluări

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (266)

- PLC Training ManualDocument117 paginiPLC Training ManualrmsanchepÎncă nu există evaluări

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (345)

- Low Power DFF Paper ModDocument15 paginiLow Power DFF Paper Modg_31682896Încă nu există evaluări

- EnDat 21 - 22Document7 paginiEnDat 21 - 22Arshiya TabassumÎncă nu există evaluări

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- Ktechlab: George John 11 June, 2007Document39 paginiKtechlab: George John 11 June, 2007Skain RkÎncă nu există evaluări

- AssignmentsDocument5 paginiAssignments20EEE24 Balaji kanna MÎncă nu există evaluări

- Lecture22 23 DLDDocument33 paginiLecture22 23 DLDRushal-Pooja ShahÎncă nu există evaluări

- 2.sequential CircuitsDocument170 pagini2.sequential CircuitsModyKing99Încă nu există evaluări

- EncoderDocument44 paginiEncoderdaiduongxanh14113Încă nu există evaluări

- Sequential Logic CircuitsDocument385 paginiSequential Logic CircuitsKrista JacksonÎncă nu există evaluări

- Lab Manual 3112Document11 paginiLab Manual 3112Tahamid Hasan.Încă nu există evaluări

- 1990ToshibaC2MOSLogic PDFDocument1.174 pagini1990ToshibaC2MOSLogic PDFionixelectronicsÎncă nu există evaluări

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- S3 Ktu 2016 CseDocument31 paginiS3 Ktu 2016 Csereema luizÎncă nu există evaluări

- UNIT-I Digital System DesignDocument28 paginiUNIT-I Digital System DesignNarasimha Murthy YayavaramÎncă nu există evaluări

- LIC Manual 2Document70 paginiLIC Manual 2Mookambiga ParvathyÎncă nu există evaluări

- MDocument16 paginiMHugo LoureiroÎncă nu există evaluări

- 74 HC 93Document7 pagini74 HC 93Brzata PticaÎncă nu există evaluări

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (121)

- Cs6201 Digital Principles and System Design: Unit IDocument19 paginiCs6201 Digital Principles and System Design: Unit IUttam NeelapureddyÎncă nu există evaluări

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)