Documente Academic

Documente Profesional

Documente Cultură

Fpga Basics

Încărcat de

sriluDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Fpga Basics

Încărcat de

sriluDrepturi de autor:

Formate disponibile

FPGA Basics and Architecture

By vedika on May 1, 2012

1 What is FPGA?

Field Programmable Gate Arrays formally known as FPGA.It is an alternative for

implementation of digital logic in systems. They are prefabricated silicon chips that

can be programmed electrically to implement any digital design. The first static

memory-based FPGA (commonly called as SRAM based FPGA) was proposed by

Wahlstrom in 1967. This architecture allowed for both logic and interconnection

configuration using a stream of configuration bits. Later on the first commercial

modern-era FPGA was introduced by Xilinx in 1984. It contained the low classic

array of Configurable Logic Blocks (CLBs) and inputs/outputs. From that of first

FPGA which contain 64 CLBs and 58 inputs and outputs , FPGAs have grown

enormously in complexity. Todays modern FPGA now can contain approximately

330,000 logic blocks and around 1100 inputs and outputs.

2 What are sub-parts/internal blocks of FPGA?

he basic architecture of FPGA consists of three major components: programmable

logic blocks which implements the logic functions, programmable routing

(interconnects) to implement these functions and I/O blocks to make off-chip

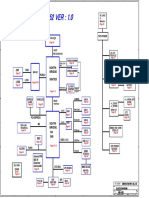

connections. An illustration of typical FPGA architecture is shown in figure

Fig.1 Internal Architecture of FPGA

A.

Programmable Logic blocks-

The purpose of programmable logic block in a FPGA is to provide the basic

computation and storage elements used in digital systems. The basic logic element

contains some form of programmable combinational logic, a flip-flop or latch and

some fast carry logic to reduce area and delay cost to it could be entire processor.

In addition to a basic logic block, many modern FPGAs contains a heterogeneous

mixture of different blocks, some of which can only be used for specific functions,

such as dedicated memory blocks, multipliers or multiplexers; of course,

configuration memory is used throughout the logic block to control the specific

function of each element within the block

B. Programmable Interconnect-

The programmable routing in an FPGA provides connections among logic blocks

and I/O blocks to complete a user defined design. It consists of multiplexers, pass

transistors and tri-state buffers, which forms the desired connection. Generally,

pass transistors and multiplexers are used within a logic cluster to connect the logic

elements together while all three are used for more global routing structures.

Several global routing structures have been used in FPGAs as: island-style,

cellular, bus-based and registered (pipelined) architectures.

C. Programmable I/OThe media or mean required to interface the logic blocks and routing architectures

to the wide range of external components to FPGA called as I/O pads or

programmable I/O. The I/O pad and surrounding supporting logic circuitry forms

as an I/O cells. These cells are important components of an FPGA and consume a

significant portion (approximately 40%) of FPGAs area. The design of I/O

programmable blocks is challenging as there is a great diversity in the supply

voltage and reference voltage standards. One of the most important decisions in

I/O architecture design is the selection of standards that will be supported. This

involves carefully made trade-offs because, unlike LUTs, which can implement

any digital functions, I/O cells can generally implement the voltage standards

selected by designers. Supporting large number of standards can increase the

silicon area required for I/O cells significantly. Additionally to support more

number of standards pin capacitance may increase with more number of pins,

which can limit the performance.

Over the time, the basic FPGA architecture has been further developed through the

addition of more specialised programmable functional blocks. The special function

blocks like- embedded memory (Block RAMs), arithmetic logic (ALUs),

multipliers, DSP-48 and even embedded microprocessors have been added due to a

frequent need of such resources for an application. The result is that many FPGAs

have the heterogeneous mixture of resources than early FPGAs.

As FPGA is Reconfigurable Architecture,while programming FPGA we can have

three type of programming approach depending on the time and resource

requirement of programmer/user.The architectures are discussed as below

A.Serial Approach:

When application demands for minimum resource utilization

but can permit longer execution time then this type of

approach is preferred.This approach is also called as Single

PE approach.

Fig 2:Serial approach

B.Parallel Approach:When

application demands for faster

execuation of code irrespective of hardware resource

utilization, then this type of approach is preferred.This

approach is also called as Systolic approach or nPE

approach.

Fig 3:Parallel Approach

C:Iterative Approach: For

optimization of both resource utilization

and execuation time and to improve area/speed metric this

approach is preferred.

S-ar putea să vă placă și

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5794)

- Power Control in Ac Isolated Microgrids With Renewable Energy Sources and Energy Storage SystemsDocument1 paginăPower Control in Ac Isolated Microgrids With Renewable Energy Sources and Energy Storage SystemssriluÎncă nu există evaluări

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (400)

- Project On Micro FinanceDocument44 paginiProject On Micro Financeredrose_luv23o.in@yahoo.co.in88% (8)

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- Budget Operating 2015Document25 paginiBudget Operating 2015sriluÎncă nu există evaluări

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (895)

- A Project Report On Microfinance in IndiaDocument63 paginiA Project Report On Microfinance in IndiaSABUJ GHOSH86% (81)

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- Behavior FinanceDocument41 paginiBehavior FinancesriluÎncă nu există evaluări

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- Unit II SAPM 17-9-14Document79 paginiUnit II SAPM 17-9-14sriluÎncă nu există evaluări

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- DCS DCE Lect 1Document11 paginiDCS DCE Lect 1Rizwan MukatiÎncă nu există evaluări

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- Ijrcm 4 IJRCM 4 Vol 3 2013 Issue 6 June Art 17Document13 paginiIjrcm 4 IJRCM 4 Vol 3 2013 Issue 6 June Art 17Kuthubudeen T MÎncă nu există evaluări

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (588)

- Financial Foresights)Document84 paginiFinancial Foresights)PriyeshRathodÎncă nu există evaluări

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (74)

- Improving Bandwidth Rectangular Patch Antenna Using Different Thickness of Dielectric SubstrateDocument6 paginiImproving Bandwidth Rectangular Patch Antenna Using Different Thickness of Dielectric SubstrateMohd Zubair KhanÎncă nu există evaluări

- FIBER OPTIC COMMUNICATION SYSTEM TOPIC 2-EditDocument48 paginiFIBER OPTIC COMMUNICATION SYSTEM TOPIC 2-EditFatin SallehÎncă nu există evaluări

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- CDLISTDocument93 paginiCDLISTRavi DharawadkarÎncă nu există evaluări

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (266)

- Economics - Project Digital IndiaDocument3 paginiEconomics - Project Digital IndiaAshutosh SharmaÎncă nu există evaluări

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- HW 4 ADocument8 paginiHW 4 ABelayneh Tadesse100% (1)

- DatasheetDocument61 paginiDatasheetalv.Încă nu există evaluări

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- Operating Instruction ZETADYN 3BFDocument194 paginiOperating Instruction ZETADYN 3BFReaper68Încă nu există evaluări

- Vox Tone Garage DesignDocument7 paginiVox Tone Garage DesignoskashredÎncă nu există evaluări

- Manual Parani Esdv2-V2.0.4Document62 paginiManual Parani Esdv2-V2.0.4Angel JuanÎncă nu există evaluări

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2259)

- KiwiSDR Design ReviewDocument65 paginiKiwiSDR Design ReviewA Daniel LazarescuÎncă nu există evaluări

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- Avionics Questions AnswersDocument26 paginiAvionics Questions AnswersSudhakar Seeman100% (2)

- LS 820Document2 paginiLS 8208819133Încă nu există evaluări

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (344)

- Andrewa Cellmax-O-25 SpecificationsDocument2 paginiAndrewa Cellmax-O-25 SpecificationsRF Coordinator TN CircleÎncă nu există evaluări

- Analysis of PQ Problems in Solar Power Distribution System PDFDocument7 paginiAnalysis of PQ Problems in Solar Power Distribution System PDFEmmanuel Esteban SebanstianÎncă nu există evaluări

- Sw11 PDFDocument12 paginiSw11 PDFscribdsuper21Încă nu există evaluări

- 2.a What Is A Digital System? Why Are Digital Systems So Pervasive? AnswerDocument23 pagini2.a What Is A Digital System? Why Are Digital Systems So Pervasive? AnswerSpiritual developmentÎncă nu există evaluări

- 1421.1 VCB Control Board Manual V1.1Document10 pagini1421.1 VCB Control Board Manual V1.1Ibrahim Shaaban AliÎncă nu există evaluări

- 64 Bit ComputingDocument15 pagini64 Bit ComputingDawod Shaaban Al-SulifanieÎncă nu există evaluări

- LG cf-20d30x Chassis mc64b SM PDFDocument35 paginiLG cf-20d30x Chassis mc64b SM PDFNelu CostinÎncă nu există evaluări

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (121)

- DFT DRC - PPT 0Document3 paginiDFT DRC - PPT 0Mohan RajÎncă nu există evaluări

- Modify Cell Channel Power ConfigurationDocument15 paginiModify Cell Channel Power ConfigurationRaul Rambo100% (1)

- Fabrication Mod 2Document16 paginiFabrication Mod 2albin shajanÎncă nu există evaluări

- C VIEWDocument1 paginăC VIEWarcheranmÎncă nu există evaluări

- FPGA Implementation of Adaptive LMS FilterDocument12 paginiFPGA Implementation of Adaptive LMS FilterembeddedguyÎncă nu există evaluări

- Training LCD Sony AZ3FK PDFDocument39 paginiTraining LCD Sony AZ3FK PDFVictor Avendaño Grillo100% (1)

- DSD SyllabusDocument2 paginiDSD SyllabusprasathvlsiÎncă nu există evaluări

- Class 2Document21 paginiClass 2md sakhwat hossainÎncă nu există evaluări

- AVerMEdia 1304net ManualDocument73 paginiAVerMEdia 1304net ManualaristotelvasileÎncă nu există evaluări

- Ex460 Ms14521 Laptop SchematicDocument49 paginiEx460 Ms14521 Laptop SchematicAndré HipnotistaÎncă nu există evaluări

- Pidnn Arduino2Document2 paginiPidnn Arduino2Byron Xavier Lima CedilloÎncă nu există evaluări

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)