Documente Academic

Documente Profesional

Documente Cultură

Tema1 PDF

Încărcat de

AureabeTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Tema1 PDF

Încărcat de

AureabeDrepturi de autor:

Formate disponibile

Tema 1.

Sistemas combinacionales bsicos

1.1.

1.2.

1.3.

1.4.

Introduccin . . . . . . . . . . . . . . . . . . . .

lgebra de Boole . . . . . . . . . . . . . . . . .

Puertas Lgicas ideales . . . . . . . . . . . . . .

Biestables . . . . . . . . . . . . . . . . . . . . .

1.4.1. Biestable RS: . . . . . . . . . . . . . . .

1.4.2. Biestable J-K: . . . . . . . . . . . . . .

1.4.3. Biestable D: . . . . . . . . . . . . . . . .

1.4.4. Biestable T: . . . . . . . . . . . . . . . .

1.5. Simplificacin de expresiones lgicas . . . . . .

1.5.1. Tablas de Karnaugh de 3 variables . . .

1.5.2. Tablas de Karnaugh de 4 variables . . .

1.5.3. Tablas de Karnaugh de 5 variables . . .

1.6. Circuitos aritmticos y combinacionales bsicos

1.1.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

1

2

3

3

3

5

5

6

6

7

9

9

10

Introduccin

En este primer tema se realizar un rpido repaso por aquellos conceptos

bsicos relativos a la electrnica digital que se explicaron en cursos anteriores,

con idea de sentar las bases que permitan posteriormente desarrollar sistemas

electrnicos digitales.

Se comenzar por enunciar el lgebra de Boole, bsica para las operaciones

lgicas implicadas en la electrnica digital, para posteriormente presentar los

diversos tipos ms comunes de puertas lgicas y biestables que se pueden emplear

en el diseo de sistemas.

Se presentarn a continuacin los mtodos clsicos de sntesis de circuitos

digitales, como son las tablas de Karnaugh, para terminar recordando algunos de

los circuitos combinacionales bsicos como bloques constructivos para circuitos

ms complejos.

Tema 1. Sistemas combinacionales bsicos

1.2.

lgebra de Boole

La electrnica digital trabaja, como es sabido, con valores binarios (1 0),

por lo que toda la aritmtica que se vaya a realizar tendr que estar expresada

en esta base binaria. El lgebra de Boole, desarrollada por George Boole en

1854, establece las leyes fundamentales para trabajar con expresiones lgicas

binarias.

Siendo x e y dos numeros binarios (2{0,1}), se definen dos operaciones bsicas, suma (+) y producto (), as como la negacin (), y se demuestran las

siguientes propiedades:

1. Conmutativa respecto a la primera funcin: x + y = y + x

2. Conmutativa respecto a la segunda funcin: xy = yx

3. Asociativa respecto a la primera funcin: (x + y) + z = x + (y + z)

4. Asociativa respecto a la segunda funcin: (xy)z = x(yz)

5. Distributiva respecto a la primera funcin: (x + y)z = xz + yz

6. Distributiva respecto a la segunda funcin: (xy) + z = (x + z)(y + z)

7. Identidad respecto a la primera funcin: x + 0 = x

8. Identidad respecto a la segunda funcin: x1 = x

9. Complemento respecto a la primera funcin: x + x = 1

10. Complemento respecto a la segunda funcin: xx = 0

Estas funciones tienen, adems las siguientes propiedades, de gran utilidad a la

hora de simplificar expresiones lgicas:

1. Idempotente respecto a la primera funcin: x + x = x

2. Idempotente respecto a la segunda funcin: xx = x

3. Maximalidad del 1: x + 1 = 1

4. Minimalidad del 0: x0 = 0

5. Involucin: (x) = x

6. Inmersin respecto a la primera funcin: x + (xy) = x

7. Inmersin respecto a la segunda funcin: x(x + y) = x

8. Ley de Morgan respecto a la primera funcin: (x + y) = xy

9. Ley de Morgan respecto a la segunda funcin: (xy) = x + y

El lgebra de Boole est detrs de la gran mayora de los mtodos de simplificacin de ecuaciones lgicas, ya sean aplicadas a la electrnica digital o al

pensamiento lgico abstracto. De hecho, a partir del lgebra de Boole se podran

deducir, por ejemplo, los diferentes tipos de silogismos existentes (recurdese si

es posible la Filosofa estudiada en Bachillerato).

La aplicacin del lgebra de Boole a la electrnica se basa en la implementacin de las funciones booleanas (producto, suma y negacin) con puertas

lgicas. Estos dispositivos electrnicos producirn una salida binaria (digital)

que responder a la funcin booleana correspondiente.

2

Tema 1. Sistemas combinacionales bsicos

1.3.

Puertas Lgicas ideales

Las puertas lgicas son, como se ha comentado, dispositivos electrnicos que

imple- mentan, idealmente, la funcin booleana correspondiente. Es conveniente recalcar que dicho comportamiento ideal no es ms que una aproximacin al

funcionamiento real de los dispositivos. En realidad, cualquier dispositivo electrnico producir una tensin continua, cuyo valor depender no slo de las

entradas del dispositivo sino tambin de lo que tenga conectado el mismo a la

salida.

Por lo tanto, al hablar de puertas lgicas ideales estamos definiendo el comportamiento esperado de las puertas lgicas, en situacin ideal, y discretizando

los valores de tensin, tanto a la entrada como a la salida, de manera que consideraremos que a partir de un cierto nivel la tensin representa un 1 lgico, y

por debajo de determinado nivel representar un 0 lgico.

Con estas premisas, se definen las puertas lgicas bsicas AND, OR, NAND,

NOR, XOR y XNOR como:

Entradas

X

Y

0

0

0

1

1

0

1

1

AND

X Y

0

0

0

1

OR

X +Y

0

1

1

1

NAND

(X Y )

1

1

1

0

NOR

(X + Y )

1

0

0

0

XOR

X Y

0

1

1

0

XNOR

(X Y )

1

0

0

1

Smbolo

Adems de las puertas lgicas bsicas antes descritas, tambin dispondremos

de inver- sores, con una nica entrada y una salida igual al negado de la entrada.

Su smbolo es:

Utilizando las propiedades del lgebra de Boole, fundamentalmente las leyes

de De Morgan, es fcil demostrar que TODAS las puertas lgicas bsicas se

pueden construir a base de puertas NAND o puertas NOR nicamente.

1.4.

Biestables

Para la realizacin de circuitos combinacionales, en los que las salidas dependen del valor que tengan las entradas en ese mismo instante, slo necesitar

usar puertas lgicas. Sin embargo, para realizar circuitos secuenciales, en los que

la salida depender tambin de la historia o la secuencia de entradas que se

hayan producido anteriormente, ser obligatorio disponer de algunos elementos

que permitan almacenar valores lgicos. Los biestables (bi-estable: dos estados

estables) cumplen esta funcin.

1.4.1.

Biestable RS:

El biestable ms simple es el formado con slo dos puertas NAND en una

estructura realimentada, que genera el conocido biestable RS:

3

Tema 1. Sistemas combinacionales bsicos

Para comprobar el funcionamiento, supondremos que partimos de la situacin Q=0, y ambas entradas desactivadas (a 1 en este caso). Entonces, si se

activa S, ponindose a 0, la salida de U1 pasar a ser 1, por lo que la salida

de U2 pasar a 0, lo que asegurar que Q siga valiendo 1 aunque S se desactive.

De la misma manera, mientras Q valga 0 la salida de U2 ser siempre 1. El

caso contrario se dar cuando Q valga 1, en cuyo caso al recibir un 0 en R

pasar a valer 0. De ah el nombre de los pines: S, de Set (encender); R, de

Reset (apagar).

Por tanto, la tabla de verdad para el biestable RS dibujado ser:

R

0

0

1

1

S

0

1

0

1

Qt+4t

1

0

1

Qt

Qt+4t

1

1

0

Qt

Donde Qt+4t representa el valor de la salida Q un cierto tiempo de retraso

tras la activacin de las entradas correspondientes.

El valor de la salida en caso de que ambas entradas fuesen 0 no es coherente

con la definicin que se ha hecho de los pines de salida, por lo que deber ser

evitado.

Es importante hacer notar que las entradas son activas a nivel bajo, esto

es actan cuando valen 0. Por ello, se denotan con el smbolo negado

encima del nombre. Usando la misma estructura pero con puertas NOR en vez

de NAND, se realiza un biestable RS activo a nivel alto (comprubese).

Este biestable, as definido, es asncrono dado que las salidas del mismo,

y propiamente el estado, cambian instantneamente, en cuanto se produce un

cambio en las entradas. Es conveniente, a la hora de disear sistemas secuenciales, dotar a stos de una seal de sincronismo, un reloj, que haga que los

sistemas digitales se comporten como sistemas discretos, como ya se comentar

ms adelante. Para ese fin, se disean dispositivos secuenciales sncronos, como

son los biestables sncronos, o activos por flanco.

Los biestables sncronos slo actualizan su valor (su estado) cuando determinada seal denominada reloj sufre un pulso, bien sea de subida o de bajada.

Hay varios tipos de biestables sncronos de gran uso en la prctica, como son

los biestables J-K, D y T.

Tema 1. Sistemas combinacionales bsicos

1.4.2.

Biestable J-K:

Es una evolucin lgica del biestable R-S, en el que se resuelve el problema de

la indeterminacin en caso de que las dos seales estn activas simultneamente.

La tabla de verdad y el smbolo del mismo se muestran a continuacin:

J

0

0

1

1

K

0

1

0

1

Qt+T

Qt

0

1

Qt

Las entradas J y K son sncronas, por lo que slo tendrn efecto en los

flancos (en este caso de bajada) de la seal de reloj. Por eso, el valor de Q

cambiar slo a cada periodo de la seal de reloj, T.

Las entradas adicionales P RE y CLR sern entradas asncronas (no afectadas por la seal de reloj) que servirn para dar valores iniciales al biestable,

antes incluso del primer flanco de reloj. Es importante remarcar el carcter

asncrono de estas dos seales, dado que su uso en un diseo lo convertir inmediatamente en un circuito asncrono, segn las definiciones que se vern al final

de este tema.

1.4.3.

Biestable D:

El biestable D es muy utilizado, dado que constituye la celda bsica para la

creacin de registros o memorias. El nombre (D) viene del ings, Delay, ya que

en modo continuo lo que har ser introducir un retraso de 1 ciclo de reloj a

las seales. En efecto, la tabla de verdad del mismo indica que, a la salida del

biestable tendr siempre lo que tena a la entrada en el periodo anterior:

D

0

1

Qt+T

0

1

Tambin en este caso el biestable est dotado de otras dos entradas, activas

a nivel bajo, asncronas, que sirven para poner a 0 a 1 el biestable independientemente de la entrada D y del reloj.

Un tipo especial de biestable D es el activo por nivel, que captura la entrada

siempre que determinada seal valga 1 ( 0, segn el tipo). A este tipo de

biestables se les denomina comnmente con el trmino ingls Latch. En este

caso, la salida ser siempre igual a la entrada, mientras la seal G est activa,

conservando el ltimo valor cuando la seal G se desactiva:

Tema 1. Sistemas combinacionales bsicos

G

0

1

1.4.4.

Qt

Qt 4t

Dt

Biestable T:

Recibe el nombre del trmino ingls toggle (conmutacin), y su funcionamiento ser tal que cuando la entrada T vale 1, el biestable cambia de estado

cada ciclo de reloj. La tabla de verdad es, por lo tanto, como se observa a

continuacin.

T

0

1

1.5.

Qt

Qt 4t

Qt 4t

Simplificacin de expresiones lgicas

Para implementar un circuito combinacional bsico con componentes de media o baja escala de integracin (puertas lgicas discretas), es necesario reducir

al mximo posible los circuitos a utilizar.

Para simplificar expresiones lgicas se pueden utilizar las propiedades del

lgebra de Boole enunciadas anteriormente. As, por ejemplo para simplificar la

expresin:

f (A, B, C) = B(A

C) + ABC

haramos:

f (A, B, C) = B(A C) + ABC = B(AC + AC) + ABC =

= BAC + BAC + ABC = BAC + BAC + ABC + ABC =

= AB(C + C) + BC(A + A) = AB + BC = B(A + C)

En esta simplificacin hemos aplicado algunas de las propiedades enunciadas,

como la distributiva, asociativa, o idempotente, as como la definicin de puerta

lgica XOR.

6

Tema 1. Sistemas combinacionales bsicos

En cualquier caso, para buscar soluciones simples en caso de que las expresiones sean complejas, resulta conveniente el uso de las conocidas como Tablas

de Karnaugh. Estas tablas son una manera ptima de representar una tabla de

verdad para ms de dos entradas, que permite una cmoda simplificacin.

En esta simplificacin hemos aplicado algunas de las propiedades enunciadas,

como la distributiva, asociativa, o idempotente, as como la definicin de puerta

lgica XOR.

Para ello, se utiliza el concepto de adyacencia, que se puede definir como:

Dos estados o dos combinaciones de entradas son adyacentes cuando, entre

ellas, slo cambia una de las variables que intervienen en la expresin lgica.

Por ejemplo, si tenemos cuatro entradas, las combinaciones ABCD y

ABCD son adyacentes, pero las combinaciones ABCD y ABCD no lo

son, dado que cambian dos valores. Veamos ahora cmo se aplican las tablas de

Karnaugh para la simplificacin de problemas de 3, 4 y 5 variables. La utilidad

de este concepto es que, si dos sumandos de una expresin lgica son adyacentes,

entonces se puede simplificar la expresin eliminando de la misma la entrada

que cambia:

ABCD + ABCD = (ACD)(B + B) = (ACD)1 = ACD

1.5.1.

Tablas de Karnaugh de 3 variables

En este caso, teniendo 3 entradas (A, B, C) en mi circuito combinacional

tendr 8 posibles combinaciones (23 = 8). Para representar todos estos valores,

puedo usar una matriz de 42 elementos. Cada fila representar las 4 posibles

combinaciones de las entradas A y B, y en cada columna desarrollo las dos

posibilidades de la variable C. Si ahora hago corresponder el elemento (i,j) de

esa matriz con el valor de salida de la funcin cuando las entradas A, B, C

toman los valores indicados en la fila i y columna j, tendr una tabla de verdad

expresada de forma compacta.

Si adems obligo ahora a que, al cambiar de una fila a otra o al cambiar de

una columna a otra slo cambie un bit, entonces tengo una Tabla de Karnaugh.

Esto se conseguir desarrollando los posibles valores en binario reflejado (00, 01,

11, 10).

As, usando el mismo ejemplo de antes, la funcin f (A, B, C) = B(A C) +

ABC tendr como tabla de Karnaugh:

Tema 1. Sistemas combinacionales bsicos

La ventaja de usar este tipo de tablas es que, como es fcil notar, las celdas

que representan combinaciones adyacentes (segn la definicin dada anteriormente) se encuentran fsicamente contiguas. Esto es evidente para todos los

casos, excepto para la adyacencia que ocurre entre la primera y la ltima fila,

entre las que tambin cambia un nico bit.

Por lo tanto, dichas celdas representan trminos que pueden ser simplificables. Se observa en el ejemplo que la funcin f (A, B, C) slo vale 1 en tres casos

concretos, que corresponden a las combinaciones 110, 111 y 011. Por tanto, la

funcin f (A, B, C) la podemos expresar como:

f (A, B, C) = ABC + ABC + ABC

pero de la observacin de las adyacencias que se deducen de la tabla de

Karnaugh, vemos que se podr simplificar bastante esta expresin. La tcnica

para simplificar la funcin lgica consiste en agrupar todos los 1 adyacentes que

aparezcan en la tabla, utilizando para ello el mnimo nmero de subconjuntos

que agrupen a todos los 1 del circuito, pudiendo tomar un 1 varias veces,

si ello simplifica el resultado. En la siguiente tabla, se han sombreado los dos

subconjuntos que se pueden extraer:

Por ltimo, observamos que el subconjunto horizontal, que incorpora las

combinaciones 110 y 111, corresponde con los trminos A B C + A B C, por

lo que simplificando obtendra A B. De igual manera, el subconjunto vertical

de este ejemplo engloba el 011 y el 111, o lo que es lo mismo los trminos

A B C + A B C, que pueden ser simplificados como B C.

De esta manera, se obtiene la misma simplificacin que anteriormente, como

no poda ser de otra manera.

Por lo tanto, la tcnica de simplificacin de Karnaugh se puede esquematizar

de la siguiente forma:

1. Generar una tabla de verdad bidimensional, distribuyendo las entradas en

binario reflejado (cdigo Gray).

2. Encontrar el mnimo conjunto de grupos mximos que engloben 1 adyacentes.

3. Deducir el trmino que corresponde a cada grupo, observando qu entradas

permanecen fijas para todas las combinaciones del mismo grupo.

4. Escribir la frmula simplificada resultante como suma de estos trminos.

De manera similar se proceder con las tablas de Karnaugh para 4 y 5 variables.

8

Tema 1. Sistemas combinacionales bsicos

1.5.2.

Tablas de Karnaugh de 4 variables

La nica diferencia real, en este caso, es que la tabla resultar de 22.

El procedimiento ser exactamente el mismo que el descrito para 3 variables.

Veamos un ejemplo:

f (A, B, C, D) = ABD + CA + ACD + ABCD + ABCD

El primer paso sera escribir la tabla de verdad de esta funcin, con sus

16 combinaciones posibles. A continuacin, generamos la tabla de Karnaugh,

poniendo en las filas las combinaciones de A y B, por ejemplo, y en las columnas

las de C y D, teniendo cuidado en ordenarlas en binario reflejado:

ABCD

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

f

0

0

0

1

0

0

0

1

1

1

0

0

1

1

1

1

Observando los grupos de 1 que se encuentran adyacentes, podemos comprobar que la funcin se puede simplificar como:

f (A, B, C, D) = AC + AB + ACD

1.5.3.

Tablas de Karnaugh de 5 variables

Si nuestra funcin depende de 5 variables, tambin puede resolverse por

Karnaugh. En este caso, la quinta variable estar distribuida segn un eje perpendicular al plano del papel; es como si tuvisemos superpuestas dos tablas

de 44, una de ellas representando los casos en que la 5a variable vale 0, y

la otra representando los casos en los que vale 1. En este caso, hay que tener

en cuenta, adems de las adyacencias horizontales o verticales, aquellas que se

producen entre ambos semiplanos. Vemoslo con un ejemplo:

f (A, B, C, D, E) = ABCE + ABCDE + BCDE + ACD+

+ABCD + (A

B)CDE + BCDE

Tema 1. Sistemas combinacionales bsicos

Para simplificar esta funcin, separaremos la tabla de verdad de Karnaugh

en dos mitades, segn que E valga 0 1:

Ahora, los grupos se hacen teniendo en cuenta la adyacencia existente tambin entre las dos mitades de la tabla, como expresan los trazos curvos que unen

los diferentes grupos encontrados.

Por tanto, la expresin queda simplificada como:

f (A, B, C, D, E) = BCE + ABD + ACD + ABCE

En principio, se podra plantear la resolucin usando tablas de Karnaugh

de funciones de 6 entradas, utilizando 2 variables para separar en 4 tablas de

44, de manera que se formara una tabla de 444, pero en la prctica no se

utiliza.

1.6.

Circuitos aritmticos y combinacionales bsicos

Existen en el mercado una serie de circuitos MSI que resuelven algunas de

las funciones lgicas ms frecuentes, evitando tener que realizarlas con puertas

lgicas. Tambin para el diseo de circuitos integrados existen libreras de celdas

prediseadas que realizan dichas funciones lgicas, liberando al diseador de la

necesidad de implementarlas puerta a puerta o incluso transistor a transistor.

Algunos de los ms tiles son:

Multiplexor de 2N a 1: se selecciona una de las 2N entradas, segn el valor

de las N entradas adicionales de control.

10

Tema 1. Sistemas combinacionales bsicos

Decodificador de N a 2N : se activar nicamente la salida que corresponda

al cdigo binario que aparece en las N entradas. Tambin se puede usar

para realizar la funcin contraria al multiplexor, usando como entrada la

seal de habilitacin general del mismo y usando las entradas naturales

del decodificador como entradas de control del mismo. Se pueden poner

en cascada, usando las salidas como habilitacin de la siguiente etapa.

Comparador: como su nombre indica, compara dos entradas digitales de N

bits y activa, segn el caso, una salida que indica cul es mayor o si son

iguales. Se pueden poner en cascada para comparar nmeros de ms bits.

Circuitos aritmticos: Se pueden encontrar, como bloques constructivos y

como circuitos MSI una gran cantidad de circuitos aritmticos, como son

sumadores, restadores, ALUs (unidades aritmtico lgicas, que implementan varias funciones) etc. Dada la gran variedad de los mismos, no resulta

til citar un ejemplo concreto. Se pueden obtener los manuales de los

diferentes productos existentes en el mercado en las pginas web de los

fabricantes, como puede ser:

http://focus.ti.com/docs/logic/logichomepage.jhtml

http://www.st.com

http://www.onsemi.com/site/products/taxonomy

11

Tema 1. Sistemas combinacionales bsicos

Buer triestado: El concepto de triestado es fundamental para el desarrollo de sistemas digitales complejos, ya que sobre l descansa a su vez el

concepto de BUS. Un buer triestado es una puerta lgica que permite

desconectar virtualmente una lnea de un nodo elctrico. De esta manera,

se pueden tener conectadas muchas seales a un mismo punto, siempre y

cuando slo uno de los buer triestado est activo. Este es, en el fondo,

el concepto de BUS: muchos dispositivos podrn leer y escribir una misma seal (por ejemplo, el dato 3o de un bus de datos), pero tendrn que

hacerlo ordenadamente.

12

S-ar putea să vă placă și

- Envenenamiento de La Humanidad y de La Tierra Por AluminioDocument5 paginiEnvenenamiento de La Humanidad y de La Tierra Por Aluminiosoy ese ke viveÎncă nu există evaluări

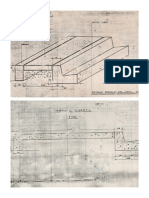

- TIPOSDECUNETASDocument1 paginăTIPOSDECUNETASAureabeÎncă nu există evaluări

- Sportlife7896 PDFDocument130 paginiSportlife7896 PDFAureabeÎncă nu există evaluări

- El Ayuno Como TerapiaDocument27 paginiEl Ayuno Como TerapiaAureabeÎncă nu există evaluări