Documente Academic

Documente Profesional

Documente Cultură

Abstraction Levels in The Digital System Modeling

Încărcat de

Rohit GaganTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Abstraction Levels in The Digital System Modeling

Încărcat de

Rohit GaganDrepturi de autor:

Formate disponibile

Contents

Handling complexity Abstraction levels

Design flow of digital systems

Additional readings

Budapest University of Technology and Economics

Abstraction Levels in the Digital System Modeling

Pter Horvth

Department of Electron Devices

September 25, 2014

Pter Horvth

Abstraction Levels in the Digital System Modeling

1 / 24

Contents

Handling complexity Abstraction levels

Design flow of digital systems

Additional readings

Contents

Contents

handling complexity abstraction levels in digital system modeling

the Gajski-Kuhn Y-diagram function representations, modeling

means, structural elements

a detailed discussion of the different abstraction levels and their

optimization goals

design flow of digital systems

top-down and bottom-up design approaches

top-down and bottom-up methods in digital design

a detailed discussion of the digital system design flow from the

viewpoint of the system designer

additional readings

Pter Horvth

Abstraction Levels in the Digital System Modeling

2 / 24

Contents

Handling complexity Abstraction levels

Design flow of digital systems

Additional readings

Handling complexity

Abstraction levels

Pter Horvth

Abstraction Levels in the Digital System Modeling

3 / 24

Contents

Handling complexity Abstraction levels

Design flow of digital systems

Additional readings

The Gajski-Kuhn Y-diagram

The Gajski-Kuhn Y-diagram

The GK diagram is an expressive representation of the abstraction

levels.

The circles represent the abstraction levels and the arrows represent

the aspects they are examined from.

register transfers

Pter Horvth

Abstraction Levels in the Digital System Modeling

4 / 24

Contents

Handling complexity Abstraction levels

Design flow of digital systems

Additional readings

Abstraction levels

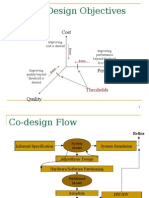

Design objectives on the different abstraction levels

System defining design partitions and their interfaces

Algorithm behavioral modeling with high-level programming

languages

RTL (register-transfer level) defining "microarchitecture",

separating control and datapath

Gate defining the behavior of RTL components with Booleequations

Circuit implementing the behavior of the logic gates with

transistor-based structures

Device constructing small, fast, and low-power transistors

Technology optimizing the technology parameters that influence

the device construction

Pter Horvth

Abstraction Levels in the Digital System Modeling

5 / 24

Contents

Handling complexity Abstraction levels

Design flow of digital systems

Additional readings

Abstraction levels

System-level

The main objective is to define the partitions of the system and the

communication methods and interfaces between the partitions and

the outside world.

The object-oriented paradigm is widely used in system-level design.

design entity examples: GPCPU1 , GPGPU2 , DSP3 , memory (cache,

operative memory, mass storage), I/O subsystem, peripheral

controller

considerations on system-level

number of the microprocessors

topology of the memory subsystem in multiprocessor systems

memory hierarchy (cache levels and sizes)

communication models (hand-shake, mailbox, FIFO etc.)

1 general-purpose

central processing unit

graphics processing unit

3 digital signal processor

2 general-purpose

Pter Horvth

Abstraction Levels in the Digital System Modeling

6 / 24

Contents

Handling complexity Abstraction levels

Design flow of digital systems

Additional readings

Abstraction levels

Algorithm-level

High-level programming language representation of the

subsystems behavior.

Once the algorithm-level implementations of the subsystems are

created, the system can be simulated.

The simulation requires high computation capacity, therefore the

efficiencies of the algorithmic models are critical. The most widely

used tools for algorithmic modeling are native C and C++,

supplemented by a set of hardware-oriented class libraries.

algorithm-level (C++) model of a simple RC filter

Pter Horvth

Abstraction Levels in the Digital System Modeling

7 / 24

Contents

Handling complexity Abstraction levels

Design flow of digital systems

Additional readings

Abstraction levels

RTL register-transfer level

The objective of RTL is to describe the data transfers and their

timing between simple functional units with (registers, register files,

arithmetic-logic units etc.)

Separating datapath and control; the datapath includes the

functional units and their interconnections. The control unit

generates control signals with appropriate timing.

control

unit

considerations on RTL

control: single-cycle, multicycle,

pipeline

internal data-storage structures

(registers, register files)

clocking scheme: frequency, phase

signals

Pter Horvth

control

I/O

data

inputs

control

signals

status

signal

Abstraction Levels in the Digital System Modeling

8 / 24

Contents

Handling complexity Abstraction levels

Design flow of digital systems

Additional readings

Abstraction levels

Gate-level

All digital functions even those containing data storage can be

represented by a set of interconnected logic gates. Although the

elementary data-storage elements (flip-flops) can be described with

gates, they are considered basic building blocks of gate-level models,

because they have a unique physical realization primitive (they are

not implemented as interconnected logic gates).

considerations on gate-level

handling logical hazards

two-level or multilevel logic realization

gate-level architecture optimization of functional units (e.g. adder:

ripple-carry vs. carry lookahead)

Pter Horvth

Abstraction Levels in the Digital System Modeling

9 / 24

Contents

Handling complexity Abstraction levels

Design flow of digital systems

Additional readings

Abstraction levels

Circuit-level

The functionality of a logic gate can be realized by interconnected

transistors. This circuit-level model is a "standard cell".

representations of a standard cell

schematic: a logical network of transistors

layout: a physical realization of the schematic

To simulate a circuit-level

model, the mathematical

models of the transistors (e.g.

Ebers-Moll, Gummel-Poon,

EKV, BSIM3) are required.

considerations on circuit-level

circuit family (ECL, SCL,

static/dynamic CMOS)

topology (e.g. domino

CMOS: alternate/pipeline)

Pter Horvth

Abstraction Levels in the Digital System Modeling

10 / 24

Contents

Handling complexity Abstraction levels

Design flow of digital systems

Additional readings

Abstraction levels

Device-level

To improve the computation capacity, power consumption, and

device density of the digital circuits, we need small, fast, and

efficient transistors. The aim of device-level is to optimize the

transistor parameters.

considerations on device-level

threshold voltage, switching

frequency, power

consumption, size etc.

scaling: short-channel and

strait-channel effects,

hot-electron effect,

gate-depletion, latch-up,

preventing or exploiting

quantum-effects (HKMG,

EEPROM)

Pter Horvth

Abstraction Levels in the Digital System Modeling

11 / 24

Contents

Handling complexity Abstraction levels

Design flow of digital systems

Additional readings

Abstraction levels

Technology-level

The aim of technology-level optimization is to analyze the effect of

technological parameters on the physical indices influencing the

device characteristics.

Technological parameters: temperature and duration of diffusion,

energy of implantation, etc.

Physical indices: oxide thickness, conductivity, carrier lifetime and

mobility, dopant density and distribution, etc.

Pter Horvth

Abstraction Levels in the Digital System Modeling

12 / 24

Contents

Handling complexity Abstraction levels

Design flow of digital systems

Additional readings

Design flow of digital systems

Pter Horvth

Abstraction Levels in the Digital System Modeling

13 / 24

Contents

Handling complexity Abstraction levels

Design flow of digital systems

Additional readings

Top-down and bottom-up design approaches

Top-down design method

In the top-down approach the design process starts with a high-level

representation of the system. The high-level model includes

partitions (subsystems) with a specific task. During the design

process the implementations of the subsystems are elaborated; they

are split into components with more specific sub-tasks and more

detailed implementations. The process stops when the components

of the refined design are simple enough to substitute them with an

existing model (practically with an RTL functional unit).

Pter Horvth

Abstraction Levels in the Digital System Modeling

14 / 24

Contents

Handling complexity Abstraction levels

Design flow of digital systems

Additional readings

Top-down and bottom-up design approaches

Bottom-up design method

In the bottom-up approach the designer creates basic functional

units with very simple tasks. Once a sufficient set of elementary

functionalities is constructed, a more complex model can be

prepared with the combination of the simple ones. The design

process stops when the increasingly complex model is able to

implement the desired functionality defined in the specification.

Pter Horvth

Abstraction Levels in the Digital System Modeling

15 / 24

Contents

Handling complexity Abstraction levels

Design flow of digital systems

Additional readings

Top-down and bottom-up design approaches

Top-down and bottom-up methods in digital design

In the digital design the top-down and the bottom-up methods

are both applied. The system designer creates RTL models from

the high-level specification with top-down method but the standard

cells are constructed from circuit-level by the component library

designer with bottom-up approach.

Pter Horvth

Abstraction Levels in the Digital System Modeling

16 / 24

Contents

Handling complexity Abstraction levels

Design flow of digital systems

Additional readings

Digital system design flow from the viewpoint of the system designer

Step #1. Design partitioning (manual)

concept: The subsystems, their relations and interfaces have to be

outlined. The subsystems are represented as "black boxes".

tools: UML, SystemC TLM4 , MATLAB

specification

4 transaction-level

modeling; a C++ class library for system-level modeling

Pter Horvth

Abstraction Levels in the Digital System Modeling

17 / 24

Contents

Handling complexity Abstraction levels

Design flow of digital systems

Additional readings

Digital system design flow from the viewpoint of the system designer

Step #2. Functional modeling (manual)

concept: The behavior of the subsystems have to be formulated.

tools: high-level programming languages (C, C++, SystemC)

functional model (C++)

Pter Horvth

Abstraction Levels in the Digital System Modeling

18 / 24

Contents

Handling complexity Abstraction levels

Design flow of digital systems

Additional readings

Digital system design flow from the viewpoint of the system designer

Step #3. RTL design (manual/automated)

concept: A microarchitecture consisting of simple functional units

(registers, register files, arithmetic units, etc.) has to be constructed.

tools: hardware description languages (VHDL, Verilog, SystemC)

functional model

Pter Horvth

Abstraction Levels in the Digital System Modeling

19 / 24

Contents

Handling complexity Abstraction levels

Design flow of digital systems

Additional readings

Digital system design flow from the viewpoint of the system designer

Step #4. RTL optimization (manual/automated)

concept: There are many microarchitectures implementing the same

functionality. We have to choose one with parameters optimal for

the application.

tools: hardware description languages (VHDL, Verilog, SystemC)

Pter Horvth

Abstraction Levels in the Digital System Modeling

20 / 24

Contents

Handling complexity Abstraction levels

Design flow of digital systems

Additional readings

Digital system design flow from the viewpoint of the system designer

Step #5. Logic synthesis (automated)

concept: The RTL description is automatically transformed into a

technology and vendor-independent gate-level model.

tools: ISE, Quartus II, LeonardoSpectrum, Precision, Encounter

RTL Compiler

Pter Horvth

Abstraction Levels in the Digital System Modeling

21 / 24

Contents

Handling complexity Abstraction levels

Design flow of digital systems

Additional readings

Digital system design flow from the viewpoint of the system designer

Step #6. Mapping (automated)

concept: The mapping assigns a specific component library

primitive to the generic resources of the gate-level model. These

library primitives are the basic elements of an ASIC technology (e.g.

AMS 0.35) or an FPGA device family (e.g. Xilinx Spartan3E).

tools: ISE, Quartus II, LeonardoSpectrum, Precision, Virtuoso,

Calibre InRoute

Pter Horvth

Abstraction Levels in the Digital System Modeling

22 / 24

Contents

Handling complexity Abstraction levels

Design flow of digital systems

Additional readings

Digital system design flow from the viewpoint of the system designer

Step #7. Place & route (automated)

concept: Place: The mapped primitives are assigned to a specific

resource in a device (FPGA) or they are placed into a specific

position of the chip layout (ASIC). Route: The interconnections of

the placed primitives are constructed. The output of the design flow

is a GDSII file (ASIC) including the information required for

manufacturing or a bitstream file (FPGA) including the

configuration memory content of the FPGA device.

tools: ISE, Quartus II, Virtuoso, Calibre InRoute

Pter Horvth

Abstraction Levels in the Digital System Modeling

23 / 24

Contents

Handling complexity Abstraction levels

Design flow of digital systems

Additional readings

Additional readings

Additional readings

David Money Harris, Sarah L. Harris Digital Design and Computer

Architecture

Peter J. Ashenden Digital Design An Embedded System

Approach Using VHDL

M. Moris Mano, Charles R. Kime Logic and Computer Design

Fundamentals

Pong P. Chu RTL Hardware Design Using VHDL

Thorsten Grtker, Stan Liao, Grant Martin, Stuart Swan System

Design with SystemC

Pter Horvth

Abstraction Levels in the Digital System Modeling

24 / 24

S-ar putea să vă placă și

- Vit Ece 5th Year SyllabusDocument16 paginiVit Ece 5th Year Syllabuspranavateja12399Încă nu există evaluări

- Design Flow OverviewDocument9 paginiDesign Flow OverviewJubin JainÎncă nu există evaluări

- Chapter 1 Introduction To Digital Systems: Design RepresentationsDocument5 paginiChapter 1 Introduction To Digital Systems: Design RepresentationstrungÎncă nu există evaluări

- Digital Design Through Verilog PDFDocument68 paginiDigital Design Through Verilog PDFSammed UpadhyeÎncă nu există evaluări

- SoC Design and Modelling Lecture NotesDocument131 paginiSoC Design and Modelling Lecture NotesSambhav VermanÎncă nu există evaluări

- Simplified FPGA Design Implementation FlowDocument36 paginiSimplified FPGA Design Implementation FlowRajendra PrasadÎncă nu există evaluări

- Fpga Based 32 Bit Risc Processor DesignDocument18 paginiFpga Based 32 Bit Risc Processor DesignAchit YadavÎncă nu există evaluări

- Physical DesignDocument12 paginiPhysical DesignPallavi ChÎncă nu există evaluări

- Synopsis Master of Technology IN Vlsi Design: Ims Engineering College, GhaziabadDocument9 paginiSynopsis Master of Technology IN Vlsi Design: Ims Engineering College, GhaziabadAnubhav SinghalÎncă nu există evaluări

- Digital Design and SynthesisDocument45 paginiDigital Design and Synthesisvirat sharmaÎncă nu există evaluări

- Microcontroller Architecture and Organization: Unit IDocument6 paginiMicrocontroller Architecture and Organization: Unit IhemanthdreamzÎncă nu există evaluări

- Digital System Design GuideDocument5 paginiDigital System Design GuidehkrohillaÎncă nu există evaluări

- Introduction to IC Design and HDL in 40 CharactersDocument38 paginiIntroduction to IC Design and HDL in 40 CharactersSebastian KarlÎncă nu există evaluări

- EEDG/CE 6301 Advanced Digital Logic DesignDocument44 paginiEEDG/CE 6301 Advanced Digital Logic DesignGowtham HariÎncă nu există evaluări

- Digital Design Through Verilog-18 PDFDocument31 paginiDigital Design Through Verilog-18 PDFAnanth G NÎncă nu există evaluări

- System-Level Design Introduction To Digital System Design: Ali Kareem Abdulrazzaq September 6, 2021Document15 paginiSystem-Level Design Introduction To Digital System Design: Ali Kareem Abdulrazzaq September 6, 2021Lưu HảiÎncă nu există evaluări

- Sys Synth - IntroDocument14 paginiSys Synth - IntroRajni YadavÎncă nu există evaluări

- Eee646 Fpga-based-system-Design Ela 2.00 Ac29Document2 paginiEee646 Fpga-based-system-Design Ela 2.00 Ac29Ranjith M KumarÎncă nu există evaluări

- Automated Solution For Data Monitoring (Dashboard) of ASIC Design FlowDocument4 paginiAutomated Solution For Data Monitoring (Dashboard) of ASIC Design FlowseventhsensegroupÎncă nu există evaluări

- System On Chip Design and ModellingDocument131 paginiSystem On Chip Design and ModellingGurram KishoreÎncă nu există evaluări

- CADocument4 paginiCAOneirosVasÎncă nu există evaluări

- Computer Architecture AllClasses-Outline-1-99Document99 paginiComputer Architecture AllClasses-Outline-1-99SrinivasaRaoÎncă nu există evaluări

- Computer Architecture AllClasses-OutlineDocument294 paginiComputer Architecture AllClasses-OutlineSrinivasaRaoÎncă nu există evaluări

- Review: Design Objectives: ThresholdsDocument19 paginiReview: Design Objectives: ThresholdsSahadev RoyÎncă nu există evaluări

- The Guider System For Classical Controller DesignDocument5 paginiThe Guider System For Classical Controller DesignEsmael FloresÎncă nu există evaluări

- Logic Synthesis and Verification: Course InfoDocument7 paginiLogic Synthesis and Verification: Course InfoManisha JadavÎncă nu există evaluări

- CA Classes-1-5Document5 paginiCA Classes-1-5SrinivasaRaoÎncă nu există evaluări

- Co Unit 1Document146 paginiCo Unit 1Adivardhan Akash MaheshwariÎncă nu există evaluări

- Programming of Industrial ComputersDocument11 paginiProgramming of Industrial ComputersshandiezzÎncă nu există evaluări

- Introduction To Hardware Description LanguageDocument5 paginiIntroduction To Hardware Description LanguageMallik KglÎncă nu există evaluări

- Introduction To DDTVDocument62 paginiIntroduction To DDTVWe are youngÎncă nu există evaluări

- Tutorial On High-Level Synthesis: and WeDocument7 paginiTutorial On High-Level Synthesis: and WeislamsamirÎncă nu există evaluări

- Ieee PapersDocument8 paginiIeee PapersAtit PatelÎncă nu există evaluări

- Design Flow OverviewDocument9 paginiDesign Flow OverviewCarlo Jose Bautista ChecaÎncă nu există evaluări

- Vlsi 1Document3 paginiVlsi 1devÎncă nu există evaluări

- Computer Architecture For Digital Signal Processing: Jonathan AllenDocument25 paginiComputer Architecture For Digital Signal Processing: Jonathan AllenDeepthi MvÎncă nu există evaluări

- Bharathidasan University, Tiruchirappalli - 620 024. Master of Computer Application (M.C.A) - Course Structure Under CBCSDocument54 paginiBharathidasan University, Tiruchirappalli - 620 024. Master of Computer Application (M.C.A) - Course Structure Under CBCSB. Srini VasanÎncă nu există evaluări

- SR PSpice SimulationDocument11 paginiSR PSpice SimulationMark Chow Khoon KeatÎncă nu există evaluări

- Hardware-Software Codesign: Jan Beutel & Iuliana Bacivarov Based On Material by Lothar ThieleDocument24 paginiHardware-Software Codesign: Jan Beutel & Iuliana Bacivarov Based On Material by Lothar ThieleEnas DhuhriÎncă nu există evaluări

- VLSI Design FlowDocument10 paginiVLSI Design Flowuday93Încă nu există evaluări

- Introduction To VLSI SystemDocument16 paginiIntroduction To VLSI SystemPrabakaran RajendranÎncă nu există evaluări

- Vlsi System DesignDocument12 paginiVlsi System DesignMahender GoudÎncă nu există evaluări

- Advanced Computer ArchitectureDocument17 paginiAdvanced Computer ArchitectureYoung LiangÎncă nu există evaluări

- CS201Document2 paginiCS201DivyanshuVermaÎncă nu există evaluări

- System-Level Power Optimization: Techniques and ToolsDocument78 paginiSystem-Level Power Optimization: Techniques and ToolsbluesoulÎncă nu există evaluări

- FPGA-BASED SYSTEM DESIGN COURSE OVERVIEWDocument2 paginiFPGA-BASED SYSTEM DESIGN COURSE OVERVIEWNaveen Chaubey100% (1)

- VLSI Design Flow: The 8 Step Process for Creating Integrated CircuitsDocument3 paginiVLSI Design Flow: The 8 Step Process for Creating Integrated CircuitsSaurabh PorwalÎncă nu există evaluări

- Vlsi DesignDocument12 paginiVlsi DesignTanveer AhmedÎncă nu există evaluări

- Implementation and Code Generation of Digital Circuits and System Using MATLAB & SIMULINKDocument16 paginiImplementation and Code Generation of Digital Circuits and System Using MATLAB & SIMULINKVLSISD36 Edwin DominicÎncă nu există evaluări

- Implementation and Code Generation of Digital Circuits and System Using MATLAB & SIMULINKDocument16 paginiImplementation and Code Generation of Digital Circuits and System Using MATLAB & SIMULINKhamim ahmedÎncă nu există evaluări

- Unit 5 - VHDLDocument15 paginiUnit 5 - VHDLMichael FosterÎncă nu există evaluări

- Iscug 2013 Hls TutorialDocument96 paginiIscug 2013 Hls TutorialLiu WenÎncă nu există evaluări

- Presentation With Right FormatDocument14 paginiPresentation With Right FormatAditya KumarÎncă nu există evaluări

- Data Converter BIST Development Tools: Ian Grout, Thomas O'Shea and Jeffrey RyanDocument2 paginiData Converter BIST Development Tools: Ian Grout, Thomas O'Shea and Jeffrey Ryansarin.gaganÎncă nu există evaluări

- Implementation of A Functional Verification System Using SystemcDocument4 paginiImplementation of A Functional Verification System Using Systemcnamhoa02Încă nu există evaluări

- Eee481 - Fa09 - CCSDocument3 paginiEee481 - Fa09 - CCSSai KamalaÎncă nu există evaluări

- Data Driven System Engineering: Automotive ECU DevelopmentDe la EverandData Driven System Engineering: Automotive ECU DevelopmentÎncă nu există evaluări

- Digital Electronics, Computer Architecture and Microprocessor Design PrinciplesDe la EverandDigital Electronics, Computer Architecture and Microprocessor Design PrinciplesÎncă nu există evaluări

- Discrete-Time Control System Implementation Techniques: Advances in Theory and ApplicationsDe la EverandDiscrete-Time Control System Implementation Techniques: Advances in Theory and ApplicationsÎncă nu există evaluări

- GATE 2017 Final Answer Key EC 1Document2 paginiGATE 2017 Final Answer Key EC 1Rohit GaganÎncă nu există evaluări

- Seminar Report On LTE PlanningDocument28 paginiSeminar Report On LTE PlanningRohit GaganÎncă nu există evaluări

- Lecture 1Document22 paginiLecture 1Rohit GaganÎncă nu există evaluări

- Number Systems and Codes ExercisesDocument4 paginiNumber Systems and Codes ExercisesRohit GaganÎncă nu există evaluări

- Lecture 1Document22 paginiLecture 1Rohit GaganÎncă nu există evaluări

- DDPP4 TOCwebDocument8 paginiDDPP4 TOCwebravindarsinghÎncă nu există evaluări

- ABB OVR Recloser and PCD Training - Rev FDocument13 paginiABB OVR Recloser and PCD Training - Rev FChristianM.LeandroYauriÎncă nu există evaluări

- PIR Sensor Based Security System PDFDocument42 paginiPIR Sensor Based Security System PDFzeeshan sikandarÎncă nu există evaluări

- LCFC Confidential NM-B461 Rev0.1 SchematicDocument99 paginiLCFC Confidential NM-B461 Rev0.1 SchematicBoris PeñaÎncă nu există evaluări

- Biochemistry ES 105Document1 paginăBiochemistry ES 105Ko Phyo Wai100% (3)

- 775Twins-HDTV User ManualDocument43 pagini775Twins-HDTV User ManualHerodotoÎncă nu există evaluări

- CA3102Document11 paginiCA3102bonaparteCWBÎncă nu există evaluări

- LC X71 Service Manual FullDocument122 paginiLC X71 Service Manual FullMaurilio CaetanoÎncă nu există evaluări

- LM 309Document8 paginiLM 309Milton AlvesÎncă nu există evaluări

- Registrar: Shri Mata Vaishno Devi UniversityDocument6 paginiRegistrar: Shri Mata Vaishno Devi UniversityIshan KathpalÎncă nu există evaluări

- m500 Brushed DC Servo Motors DatasheetDocument2 paginim500 Brushed DC Servo Motors Datasheethafidzfb100% (1)

- SAUTER System OverviewDocument51 paginiSAUTER System OverviewMetalloy100% (1)

- Sucursal Colón Quito Sucursal Sur Quito Centro de Servicios Técnicos Sucursal Mayor Guayaquil Sucursal Sur Guayaquil Principal QuitoDocument6 paginiSucursal Colón Quito Sucursal Sur Quito Centro de Servicios Técnicos Sucursal Mayor Guayaquil Sucursal Sur Guayaquil Principal QuitoTamara SuconotaÎncă nu există evaluări

- User Manual - BOYALINKDocument20 paginiUser Manual - BOYALINKCATEDRA DEPORTIVA TINGO MARIAÎncă nu există evaluări

- UPS - Netpro Operation Manual 0k6 1k5 VaDocument13 paginiUPS - Netpro Operation Manual 0k6 1k5 VagoroonÎncă nu există evaluări

- ZXSDR BS8900A Quick Installation Guide R2.0 - CH - ENDocument37 paginiZXSDR BS8900A Quick Installation Guide R2.0 - CH - ENMuhammad AliÎncă nu există evaluări

- Everything: You Need To KnowDocument3 paginiEverything: You Need To KnowAndrew RossÎncă nu există evaluări

- GPFM115 Medical: 115 Watt Global Performance SwitchersDocument3 paginiGPFM115 Medical: 115 Watt Global Performance Switchersbruno barbosaÎncă nu există evaluări

- The Miracle Whip: A Multiband QRP Antenna Made From Inexpensive PartsDocument4 paginiThe Miracle Whip: A Multiband QRP Antenna Made From Inexpensive PartsAnonymous vRX0OvwHÎncă nu există evaluări

- TributaryDocument5 paginiTributaryAjay BarwalÎncă nu există evaluări

- Invention of Memory RacetrackDocument6 paginiInvention of Memory Racetrackvishals_31Încă nu există evaluări

- Safety BarreiraDocument32 paginiSafety Barreiratv boxÎncă nu există evaluări

- VSD ComponentsDocument20 paginiVSD ComponentsTanya Singh75% (4)

- Apc Ups Br1200giDocument2 paginiApc Ups Br1200giJorge TorresÎncă nu există evaluări

- Electronics Repair ManualDocument957 paginiElectronics Repair Manuallfloryn96% (27)

- Pruef Messtechnik en PDFDocument40 paginiPruef Messtechnik en PDFFCO ANTONIO CHACONÎncă nu există evaluări

- 3HH-00057-2286-DFZZA-01P01-R4202 CFT Workshop BondingDocument10 pagini3HH-00057-2286-DFZZA-01P01-R4202 CFT Workshop BondingStavros SotiriadisÎncă nu există evaluări

- media-2063038-OM 7.76 Help PDFDocument362 paginimedia-2063038-OM 7.76 Help PDFmicrajacutÎncă nu există evaluări

- AV Receiver: Owner'S Manual Manual de InstruccionesDocument430 paginiAV Receiver: Owner'S Manual Manual de InstruccionesSebas SinÎncă nu există evaluări

- T1004M6R012Document1 paginăT1004M6R012АлександрÎncă nu există evaluări

- LVDSDocument10 paginiLVDSANGEL MAURICIO ALVAREZ CANOÎncă nu există evaluări