Documente Academic

Documente Profesional

Documente Cultură

Data Hazards in ALU Instructions: Consider This Sequence

Încărcat de

sivakumarb92Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Data Hazards in ALU Instructions: Consider This Sequence

Încărcat de

sivakumarb92Drepturi de autor:

Formate disponibile

71

Consider this sequence:

sub $2, $1,$3

and $12,$2,$5

$6 $2

or $13

$13,$6,$2

add $14,$2,$2

sw $15,100($2)

We can resolve hazards with forwarding

How do we detect when to forward?

4.7 Data Hazards: Forwarding vs. Stalling

Data Hazards in ALU Instructions

CS/ECE 3330 Fall 2010

Dependencies & Forwarding

72

CS/ECE 3330 Fall 2010

Detecting the Need to Forward

Pass register numbers along pipeline

e.g., ID/EX.RegisterRs = register number for Rs

sitting in ID/EX pipeline register

ALU operand register numbers in EX stage are

given by

ID/EX.RegisterRs, ID/EX.RegisterRt

Data hazards when

1a. EX/MEM.RegisterRd = ID/EX.RegisterRs

1b.

EX/MEM.RegisterRd

1b EX/MEM

RegisterRd = ID/EX.RegisterRt

ID/EX RegisterRt

2a. MEM/WB.RegisterRd = ID/EX.RegisterRs

2b. MEM/WB.RegisterRd = ID/EX.RegisterRt

Fwd from

EX/MEM

pipeline reg

Fwd from

MEM/WB

pipeline reg

CS/ECE 3330 Fall 2010

73

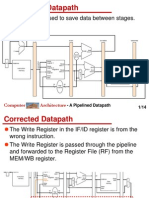

Detecting the Need to Forward

74

But only if forwarding instruction will write to

a register!

EX/MEM.RegWrite, MEM/WB.RegWrite

And only if Rd for that instruction is not $zero

EX/MEM.RegisterRd 0,

MEM/WB.RegisterRd 0

CS/ECE 3330 Fall 2010

Forwarding Paths

75

CS/ECE 3330 Fall 2010

Datapath with Forwarding

79

CS/ECE 3330 Fall 2010

Load-Use Data Hazard

Need to stall

for one cycle

CS/ECE 3330 Fall 2010

80

How to Stall the Pipeline

Force control values in ID/EX register

to 0

EX, MEM and WB do nop (no-operation)

Prevent update of PC and IF/ID register

Using instruction is decoded again

Following instruction is fetched again

1-cycle stall allows MEM to read data for lw

Can subsequently forward to EX stage

82

CS/ECE 3330 Fall 2010

Stall/Bubble in the Pipeline

Stall inserted

here

83

CS/ECE 3330 Fall 2010

Datapath with Hazard Detection

85

CS/ECE 3330 Fall 2010

4.8 Control Hazard

ds

Branch Hazards

If branch outcome determined in MEM

Flush these

instructions

(Set control

values to 0)

PC

CS/ECE 3330 Fall 2010

86

Reducing Branch Delay

87

Move hardware to determine outcome to ID

stage

Target address adder

R i t comparator

t

Register

Example: branch taken

36: sub $10, $4, $8

40: beq $1, $3, 7

44: and $12, $2, $5

48: or

$13, $2, $6

52: add $14, $4, $2

56: slt $15, $6, $7

...

72: lw

$4, 50($7)

CS/ECE 3330 Fall 2010

Data Hazards for Branches

If a comparison register is a destination of 2nd

or 3rd preceding ALU instruction

add $1, $2, $3

IF

add $4, $5, $6

ID

EX

MEM

WB

IF

ID

EX

MEM

WB

IF

ID

EX

MEM

WB

IF

ID

EX

MEM

beq $1, $4, target

WB

Can resolve using forwarding

CS/ECE 3330 Fall 2010

90

Data Hazards for Branches

If a comparison register is a destination of

preceding ALU instruction or 2nd preceding

load instruction

Need 1 stall cycle

lw

$1, addr

IF

, $5,

$ , $6

$

add $

$4,

beq stalled

ID

EX

MEM

WB

IF

ID

EX

MEM

WB

IF

ID

ID

EX

beq $1, $4, target

91

MEM

WB

CS/ECE 3330 Fall 2010

Data Hazards for Branches

If a comparison register is a destination of

immediately preceding load instruction

Need 2 stall cycles

lw

$1, addr

IF

q stalled

beq

ID

EX

IF

ID

MEM

WB

ID

beq stalled

ID

beq $1, $0, target

EX

MEM

WB

CS/ECE 3330 Fall 2010

92

Dynamic Branch Prediction

In deeper and superscalar pipelines, branch

penalty is more significant

Use dynamic prediction

Branch prediction buffer (aka branch history table)

Indexed by recent branch instruction addresses

Stores outcome (taken/not taken)

To execute a branch

Check table, expect the same outcome

Start fetching from fall-through or target

If wrong, flush pipeline and flip prediction

93

CS/ECE 3330 Fall 2010

1-Bit Predictor: Shortcoming

Inner loop branches mispredicted twice!

outer:

inner:

beq , , inner

beq , , outer

Mispredict as taken on last iteration of

inner loop

Then mispredict as not taken on first

iteration of inner loop next time around

CS/ECE 3330 Fall 2010

94

2-Bit Predictor

95

Only change prediction on two successive

mispredictions

CS/ECE 3330 Fall 2010

Calculating the Branch Target

Even with predictor, still need to calculate the

target address

1-cycle penalty for a taken branch

Branch target buffer

Cache of target addresses

Indexed by PC when instruction fetched

If hit and instruction is branch predicted taken, can fetch

target immediately

CS/ECE 3330 Fall 2010

96

Unexpected events requiring change

in flow of control

Different ISAs use the terms differently

4.9 Exceptions

Exceptions and Interrupts

Exception

Arises within the CPU

e.g., undefined opcode, overflow, syscall,

97

Interrupt

From an external I/O controller

Dealing

with

them without

D li

ith th

ith t sacrificing

ifi i

performance is hard

CS/ECE 3330 Fall 2010

10

Sample Exceptions

I/O request

Invoke the operating system from user

program

Arithmetic overflow

Undefined instruction

Hardware malfunction

CS/ECE 3330 Fall 2010

98

Handling Exceptions

99

Save PC of offending (or interrupted)

instruction

In MIPS: Exception Program Counter (EPC)

Save indication of the problem

In MIPS: Cause register

Jump to handler at known address

CS/ECE 3330 Fall 2010

11

Exceptions in a Pipeline

Another form of control hazard

Consider overflow on add in EX stage

add $1, $2, $1

Prevent $1 from being clobbered

Complete previous instructions

Flush add and subsequent instructions

Set Cause and EPC register values

Transfer control to handler

Similar

to

Si il

t mispredicted

i

di t d branch

b

h

Use much of the same hardware

CS/ECE 3330 Fall 2010

102

Exception Example

105

Exception on

40

sub

44

and

48

or

4C

add

50

slt

54

lw

Handler

80000180

80000184

add in

$11, $2, $4

$12, $2, $5

$13 $2,

$2 $6

$13,

$1, $2, $1

$15, $6, $7

$16, 50($7)

sw

sw

$25,

1000($0)

$2

$26, 1004($0)

CS/ECE 3330 Fall 2010

12

Exception Example

106

CS/ECE 3330 Fall 2010

Exception Example

107

CS/ECE 3330 Fall 2010

13

Multiple Exceptions

108

Pipelining overlaps multiple instructions

Could have multiple exceptions at once

Simple approach: deal with exception from

earliest instruction

Flush subsequent instructions

Precise exceptions

In complex pipelines

Multiple instructions issued per cycle

Out-of-order

Out of order completion

Maintaining precise exceptions is difficult!

CS/ECE 3330 Fall 2010

Imprecise Exceptions

Just stop pipeline and save state

Including exception cause(s)

Let the handler work out

Which instruction(s) had exceptions

Which to complete or flush

May require manual completion

109

Simplifies hardware, but more complex

handler software

Not

complex

multiple-issue

N t feasible

f

ibl for

f

l

lti l i

out-of-order pipelines

CS/ECE 3330 Fall 2010

14

S-ar putea să vă placă și

- Computer Organization and Design: The Hardware / Software InterfaceDe la EverandComputer Organization and Design: The Hardware / Software InterfaceEvaluare: 4 din 5 stele4/5 (12)

- Data HazardsDocument15 paginiData HazardsPetreMaziluÎncă nu există evaluări

- 9 MIPS Pipeline HazardsDocument42 pagini9 MIPS Pipeline HazardsNguyễn Trường GiangÎncă nu există evaluări

- Lecture 11 COMP2611 Processor Part3Document41 paginiLecture 11 COMP2611 Processor Part3jnfzÎncă nu există evaluări

- A Pipelined Datapath: Resisters Are Used To Save Data Between StagesDocument14 paginiA Pipelined Datapath: Resisters Are Used To Save Data Between StagesJohnDaGRTÎncă nu există evaluări

- Lecture9 Cda3101Document62 paginiLecture9 Cda3101MD Manan RainÎncă nu există evaluări

- Lecture-16 CH-04 4Document21 paginiLecture-16 CH-04 4Osama RousanÎncă nu există evaluări

- Enhancing Performance With PipeliningDocument71 paginiEnhancing Performance With Pipeliningapi-26072581Încă nu există evaluări

- Lecture # 12Document31 paginiLecture # 12Noman Ajaz KørãíÎncă nu există evaluări

- CS 4200/5200 Computer Architecture I: MIPS Instruction Set ArchitectureDocument12 paginiCS 4200/5200 Computer Architecture I: MIPS Instruction Set ArchitectureIndrit QokuÎncă nu există evaluări

- Mock LectureDocument21 paginiMock LectureAjay SinghÎncă nu există evaluări

- Ca Assignment: Syeda Haima Batool Naqvi CS-18022Document11 paginiCa Assignment: Syeda Haima Batool Naqvi CS-18022Haima NaqviÎncă nu există evaluări

- 33 7 LM V1 S1 Delay ModelingDocument39 pagini33 7 LM V1 S1 Delay ModelingPriyanka AshishÎncă nu există evaluări

- Data HazardDocument8 paginiData HazardJeya Sheeba AÎncă nu există evaluări

- Computer Architecture Test 2Document5 paginiComputer Architecture Test 2gbland100% (1)

- PDF 2Document13 paginiPDF 2Nivedita Acharyya 2035Încă nu există evaluări

- Assembly in One StepDocument15 paginiAssembly in One StepPietro Cristofoli100% (1)

- Computer Programming Laboratory 2018-2019Document37 paginiComputer Programming Laboratory 2018-2019Radhika AjadkaÎncă nu există evaluări

- Pipeline Control HazardsDocument22 paginiPipeline Control HazardsSamin YeaserÎncă nu există evaluări

- CA-Easytrieve Frequently Asked QuestionsDocument12 paginiCA-Easytrieve Frequently Asked Questionsapi-3853979Încă nu există evaluări

- Known Issues On Cisco 7600 Router ESDocument18 paginiKnown Issues On Cisco 7600 Router ESirozaÎncă nu există evaluări

- MIPS Instruction Set Architecture: ECE4680 Computer Organization & ArchitectureDocument4 paginiMIPS Instruction Set Architecture: ECE4680 Computer Organization & ArchitectureNarender KumarÎncă nu există evaluări

- Panel 2Document26 paginiPanel 2tilfaniÎncă nu există evaluări

- Week5 - Instruction Set - Part 3Document26 paginiWeek5 - Instruction Set - Part 3Trung BảoÎncă nu există evaluări

- Just Enough Dump: by Gabe GargiuloDocument18 paginiJust Enough Dump: by Gabe GargiuloLalit KumarÎncă nu există evaluări

- Instructions: Language of The Computer: Dr. Randa MohamedDocument21 paginiInstructions: Language of The Computer: Dr. Randa MohamedBody AbdoÎncă nu există evaluări

- Chapter 4B: The Processor, Part B: Mary Jane IrwinDocument56 paginiChapter 4B: The Processor, Part B: Mary Jane IrwinAdip ChyÎncă nu există evaluări

- 78941cdb0e9833460d05ad79c59f6c0c_ed750806804ba7eb09df7f9f332d16c7Document5 pagini78941cdb0e9833460d05ad79c59f6c0c_ed750806804ba7eb09df7f9f332d16c7Priyank SharmaÎncă nu există evaluări

- PRBs - Short DescriptionDocument47 paginiPRBs - Short Descriptionnithish.singh8946Încă nu există evaluări

- Italian Sprite Multiplexing TutorialDocument56 paginiItalian Sprite Multiplexing Tutorialolivier bernhardÎncă nu există evaluări

- ECE4680 Computer Organization & Architecture: MIPS Instruction Set ArchitectureDocument11 paginiECE4680 Computer Organization & Architecture: MIPS Instruction Set ArchitectureNarender KumarÎncă nu există evaluări

- MULTIcycle OPERATIONSDocument24 paginiMULTIcycle OPERATIONSi_2loveu3235Încă nu există evaluări

- CPS 104 Computer Organization and Programming Lecture-9: The MIPS Instruction Set ArchitectureDocument29 paginiCPS 104 Computer Organization and Programming Lecture-9: The MIPS Instruction Set ArchitectureprachesÎncă nu există evaluări

- Computer Science 37 Lecture 22Document14 paginiComputer Science 37 Lecture 22Alexander TaylorÎncă nu există evaluări

- Seven Segment Display: Lab ExperimentDocument10 paginiSeven Segment Display: Lab ExperimentraÎncă nu există evaluări

- CA Lab Manual 6Document4 paginiCA Lab Manual 6Sourab SomasundarÎncă nu există evaluări

- Insem2 SchemeDocument7 paginiInsem2 SchemeAditya RajÎncă nu există evaluări

- Chapter Six: 2004 Morgan Kaufmann PublishersDocument25 paginiChapter Six: 2004 Morgan Kaufmann PublisherssamquicklyÎncă nu există evaluări

- Troubleshooting Addressing Services: CCNP TSHOOT: Maintaining and Troubleshooting IP NetworksDocument104 paginiTroubleshooting Addressing Services: CCNP TSHOOT: Maintaining and Troubleshooting IP NetworksTomas Saavedra FerreiraÎncă nu există evaluări

- Translating VCD and Ev CD To AteDocument13 paginiTranslating VCD and Ev CD To Atecristian_chitu100% (1)

- Misp Procedure CallsDocument34 paginiMisp Procedure CallsFernando GonzalezÎncă nu există evaluări

- ECAD and VLSI Lab ManualDocument107 paginiECAD and VLSI Lab ManualHarold WilsonÎncă nu există evaluări

- MIPS Instruction ReferenceDocument12 paginiMIPS Instruction Referencedanej8909Încă nu există evaluări

- Easytreve FAQDocument12 paginiEasytreve FAQdhanalekshmirameshÎncă nu există evaluări

- ELEN 468 Advanced Logic Design: MIPS MicroprocessorDocument19 paginiELEN 468 Advanced Logic Design: MIPS MicroprocessorMahendranath CholletiÎncă nu există evaluări

- Compute Assign Increment Decrement Get Display: Count Initialval LastvalDocument3 paginiCompute Assign Increment Decrement Get Display: Count Initialval LastvalNa O LeÎncă nu există evaluări

- COE301 Lab 13 Pipelined CPU Design With Data ForwardingDocument8 paginiCOE301 Lab 13 Pipelined CPU Design With Data ForwardingItz Sami UddinÎncă nu există evaluări

- Assignment 3Document3 paginiAssignment 3bugyourselfÎncă nu există evaluări

- Hassan Ilyas Keyani 253 Fet Bsee f17 BDocument7 paginiHassan Ilyas Keyani 253 Fet Bsee f17 Bshahab ud dinÎncă nu există evaluări

- Coa AppliedDocument13 paginiCoa AppliedIshanÎncă nu există evaluări

- Fault Codes in ACS, CODEDocument17 paginiFault Codes in ACS, CODEeduardo perezÎncă nu există evaluări

- Fault Codes in ACS, CODEDocument17 paginiFault Codes in ACS, CODEeduardo perezÎncă nu există evaluări

- Lab 6 Verilog Data FlowDocument13 paginiLab 6 Verilog Data Flowsafdarmunir070Încă nu există evaluări

- CS104: Computer Organization: 2 April, 2020Document33 paginiCS104: Computer Organization: 2 April, 2020Om PrakashÎncă nu există evaluări

- Mips IsaDocument79 paginiMips Isaphan_vinh_20Încă nu există evaluări

- CS M151B / EE M116C: Computer Systems ArchitectureDocument50 paginiCS M151B / EE M116C: Computer Systems ArchitecturetinhtrilacÎncă nu există evaluări

- ECE232: Hardware Organization and Design: Example: Array AccessDocument13 paginiECE232: Hardware Organization and Design: Example: Array AccessJosé Gabriel Hermes CavalcantiÎncă nu există evaluări

- Integration Data Mapping Template v1Document42 paginiIntegration Data Mapping Template v1Ashish TiwariÎncă nu există evaluări

- Dosen Pengampu: Dr. Ir. Fatchul Arifin, M.TDocument29 paginiDosen Pengampu: Dr. Ir. Fatchul Arifin, M.TYuuta KirigayaÎncă nu există evaluări

- Pipelining and Instruction Level Parallelism: 5 Steps of MIPS DatapathDocument12 paginiPipelining and Instruction Level Parallelism: 5 Steps of MIPS DatapathNgat SkyÎncă nu există evaluări

- List of CPU ArchitecturesDocument3 paginiList of CPU Architecturessivakumarb92Încă nu există evaluări

- 8b/10b Encoder Design: Xu Qiaoyu Liu HuijieDocument3 pagini8b/10b Encoder Design: Xu Qiaoyu Liu Huijiesivakumarb92Încă nu există evaluări

- MIPSDocument6 paginiMIPSsivakumarb92Încă nu există evaluări

- Data HazardsDocument29 paginiData Hazardssivakumarb92Încă nu există evaluări

- Parallel 2Document14 paginiParallel 2sivakumarb92Încă nu există evaluări

- Chapter 12: Multiprocessor Architectures: Cache Coherence Problem and Cache Synchronization Solutions Part 1Document31 paginiChapter 12: Multiprocessor Architectures: Cache Coherence Problem and Cache Synchronization Solutions Part 1sivakumarb92Încă nu există evaluări

- An Implementation of Open Core Protocol For The On-Chip Bus: CH - Suryanarayana, M.Vinodh KumarDocument4 paginiAn Implementation of Open Core Protocol For The On-Chip Bus: CH - Suryanarayana, M.Vinodh Kumarsivakumarb92Încă nu există evaluări

- NVL-07.Thwarting Scan-Based Attacks On Secure-ICsDocument3 paginiNVL-07.Thwarting Scan-Based Attacks On Secure-ICssivakumarb92Încă nu există evaluări

- NVL-14.Minimizing Energy of Integer Unit by Higher VoltageDocument3 paginiNVL-14.Minimizing Energy of Integer Unit by Higher Voltagesivakumarb92Încă nu există evaluări

- NVL 09.low Power Pulse Triggered Flip Flop DesignDocument3 paginiNVL 09.low Power Pulse Triggered Flip Flop Designsivakumarb92Încă nu există evaluări

- NVL-06.Carbon Nanotubes Blowing New Life Into NP DynamicDocument3 paginiNVL-06.Carbon Nanotubes Blowing New Life Into NP Dynamicsivakumarb92Încă nu există evaluări

- NVL-12.Constant Delay Logic StyleDocument3 paginiNVL-12.Constant Delay Logic Stylesivakumarb92Încă nu există evaluări

- NVL-05.Area-Delay-Power Efficient Carry-Select AdderDocument3 paginiNVL-05.Area-Delay-Power Efficient Carry-Select Addersivakumarb92Încă nu există evaluări

- NVL-04.an Optimized Modified Booth Recoder For Efficient Design of The Add-Multiply OperatorDocument4 paginiNVL-04.an Optimized Modified Booth Recoder For Efficient Design of The Add-Multiply Operatorsivakumarb92Încă nu există evaluări

- A High-Speed, Energy-Efficient Two-Cycle Multiply-Accumulate (MAC) Architecture and Its Application To A Double-Throughput MAC UnitDocument9 paginiA High-Speed, Energy-Efficient Two-Cycle Multiply-Accumulate (MAC) Architecture and Its Application To A Double-Throughput MAC Unitsivakumarb92Încă nu există evaluări

- Mips IsaDocument32 paginiMips Isasivakumarb92Încă nu există evaluări

- Fault Tolerant Systems: PrerequisitesDocument14 paginiFault Tolerant Systems: Prerequisitessivakumarb92Încă nu există evaluări

- Srikanth - .Net Developer ResumeDocument2 paginiSrikanth - .Net Developer ResumeRevanth Kumar GÎncă nu există evaluări

- CCNA PresentationDocument127 paginiCCNA PresentationVVNAGESWARÎncă nu există evaluări

- Installation Guide For Nortel Meridian 2Document240 paginiInstallation Guide For Nortel Meridian 2RCraftÎncă nu există evaluări

- Assignment 1 - Technical Description QR CodeDocument7 paginiAssignment 1 - Technical Description QR Codeapi-359176976Încă nu există evaluări

- Drumlin V4 Secure PDF Reader/Publisher Software Please Read And/or PrintDocument21 paginiDrumlin V4 Secure PDF Reader/Publisher Software Please Read And/or PrintJames JohnsonÎncă nu există evaluări

- Pen Drive As An AtmDocument27 paginiPen Drive As An AtmRahul Gupta33% (3)

- Mike Nelson Resume 2008Document2 paginiMike Nelson Resume 2008api-12184182Încă nu există evaluări

- Fiery Training 1Document346 paginiFiery Training 1shamilbasayevÎncă nu există evaluări

- Expression Home XP 445 DatasheetDocument2 paginiExpression Home XP 445 DatasheetkiluvilÎncă nu există evaluări

- OS Assignment#3Document20 paginiOS Assignment#3Fahad SiddiquiÎncă nu există evaluări

- Tcs - Rim Alliance - Tcs BRMS' - FinalDocument34 paginiTcs - Rim Alliance - Tcs BRMS' - Finalsiddhartha_maity_4Încă nu există evaluări

- Siteminder Implementation EnuDocument210 paginiSiteminder Implementation Enupippo5318Încă nu există evaluări

- Ceragon FibeAir - 1500PDocument22 paginiCeragon FibeAir - 1500PRobert LopezÎncă nu există evaluări

- Conceptos Financieros Crown PDFDocument4 paginiConceptos Financieros Crown PDFRodrigo Martinez CordobaÎncă nu există evaluări

- Godaddy Codeigniter IndexphpDocument3 paginiGodaddy Codeigniter IndexphpJenÎncă nu există evaluări

- PDF Aveva Instrumentation Installation User Guide - CompressDocument23 paginiPDF Aveva Instrumentation Installation User Guide - Compressjosejohn1Încă nu există evaluări

- Brochure EleDocument2 paginiBrochure EleVimarsh SrivastavaÎncă nu există evaluări

- Project ProposalDocument10 paginiProject ProposalHarot AsratÎncă nu există evaluări

- HADOOP 1.X Installation Steps On UbuntuDocument3 paginiHADOOP 1.X Installation Steps On UbuntuVisheshUtsavÎncă nu există evaluări

- Se Modifica Ce Este Cu Rosu Dupa Cerinte: #Config DefaultDocument5 paginiSe Modifica Ce Este Cu Rosu Dupa Cerinte: #Config DefaultCristian BujorÎncă nu există evaluări

- MANUAL Tplink TLSF 1016dDocument10 paginiMANUAL Tplink TLSF 1016dTulio Federico PerezÎncă nu există evaluări

- Installation and User's Guide: IBM Tivoli Continuous Data Protection For Files 3.1Document116 paginiInstallation and User's Guide: IBM Tivoli Continuous Data Protection For Files 3.1Anjana DeviÎncă nu există evaluări

- ONAP API Gateway ProposalDocument20 paginiONAP API Gateway ProposalPandji Mulia BudimanÎncă nu există evaluări

- Jeppiaar SRR Engineering College: Title: Smart Wearble Health Monitoring For Patient/Elder PeopleDocument12 paginiJeppiaar SRR Engineering College: Title: Smart Wearble Health Monitoring For Patient/Elder PeopleKurushNishanthÎncă nu există evaluări

- lcd-mst6m48v2.0c 244 PDFDocument12 paginilcd-mst6m48v2.0c 244 PDFzulkarnain apriadiÎncă nu există evaluări

- iVMS-4200 and iVMS-4200Lite ComparisonDocument1 paginăiVMS-4200 and iVMS-4200Lite ComparisonalexÎncă nu există evaluări

- SDLC DetailedDocument26 paginiSDLC DetailedShalesh GabhaneÎncă nu există evaluări

- ERRori JocDocument8 paginiERRori JocAlly ManeaskaÎncă nu există evaluări

- MB Manual Ga-z97x-Gaming3 eDocument116 paginiMB Manual Ga-z97x-Gaming3 eMihai PopaÎncă nu există evaluări

- Projector Manual 5533Document53 paginiProjector Manual 5533Marius DutescuÎncă nu există evaluări