Documente Academic

Documente Profesional

Documente Cultură

6800 Internal Registers

Încărcat de

MANIKANDANTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

6800 Internal Registers

Încărcat de

MANIKANDANDrepturi de autor:

Formate disponibile

7/7/2015

6800InternalRegisters

6800InternalRegisters

CentralProcessingUnit(CPU)REGISTERS

Thereare6registersavailableintheMotorola6800microprocessor:TheCentralProcessing

Unit(CPU)hasthree16bitregistersandthree8bitregistersavailableforusebythe

programmer.

1.Twoaccumulators(ACCAandACCB)

2.Oneindexregister(X)

3.Oneprogramcounterregister(PC)

4.Onestackpointerregister(SP).

5.Oneconditioncoderegister(CC)

Accumulators

TheMPUcontains2accumulatorsdesignatedACCAandACCB.Eachaccumulatoris8bits

(onebyte)longandisusedtoholdoperandsanddatafromthearithmeticlogicunit.

IndexRegister

Theindexregister(X)isa16bit(2byte)registerwhichisprimarilyusedtostoreamemory

addressintheIndexedmodeofmemoryaddressing.Theindexregistermaybedecremented,

incrementedandstored.

ProgramCounter

Theprogramcounter(PC)isa16bitregisterthatcontainstheaddressofthenextbytetobe

fetchedfrommemory.Whenthecurrentvalueoftheprogramcounterisplacedontheaddress

buss,theprogramcounterwillbeincrementedautomatically.

StackPointer

TheStackPointer(SP)isa16bit(2byte)registerthatcontainsabeginningaddress,normallyin

RAM,wherethestatusoftheMPUregistersmaybestoredwhentheMPUhasotherfunctions

toperform,suchasduringaninterruptorduringaBranchtoSubroutine.Theaddressinthe

stackpointeristhestartingaddressofsequentialmemorylocationsinRAMwhereMPUstatus

registerswillbestored.Inthoseapplicationsthatrequirestorageofinformationinthestack

whenpowerislost,thestackmustbenonvolatile.

ConditionCodeRegister(CC)

Theconditioncoderegisterisan8bitregister.Eachindividualbitmaygetsetorgetcleared

fromexecutionofaninstruction.Eachinstructioneffectstheconditioncoderegisterdifferently.

http://www.electronics.dit.ie/staff/tscarff/6800/registers/registers_6800.htm

1/3

7/7/2015

6800InternalRegisters

Theprimaryuseofthisregisterisexecutionoftheconditionalbranchinstruction.Bit6and7are

notusedandremainatlogic1.

BIT(07)NumberFunction:

0C(CarryBorrowTest)

1V(OverflowTest)

2Z(ZeroTest)

3N(NegativeTest)

4I(InterruptMaskTest)

5H(HalfCarryTest).MPU7

CarryBorrow:Foraddition,thecarryborrowconditioncode(C)inthezerobitposition,

representsacarry.Thisbitgetsset(C=1)toindicateacarry,andisreset(C=0)ifthereisno

carry.

Forsubtraction,theCbitisset(C=1)toindicateaborrowandisreset(C=0)toindicatethere

wasnoborrow.

Overflow:TheVbit(bit1)oftheconditioncoderegisterisset(V=1)whentwo'scomplement

overflowresultsfromanarithmeticoperation,andisreset(V=O)iftwo'scomplementoverflow

doesnotoccur.

Zero:TheZbit(bit2)oftheconditioncoderegisterisset(Z=1)iftheresultofanarithmetic

operationiszero,andisreset(Z=0)iftheresultisnotzero.

Negative:TheNbit(bit3)oftheconditioncoderegisterisset(N=1)ifbit7ofanarithmetic

operationisset(equalto1).Thisindicatesthatthetwo'scomplementnumber,representedby

thebitpatternoftheresult,isnegative.TheNbitisreset(N=0)ifbit7ofthearithmeticresultis

equalto0.

InterruptMask:IfthisIbit(bit4)isset(I=1),theMPUcannotrespondtoaninterruptrequest

fromanyperipheraldevice.

HalfCarry:ThehalfcarrybitH(bit5)oftheconditioncoderegisterisset(H=1)during

executionofanyoftheinstructionsABA,ADC,orADD,ifthereisacarryfrombitposition3tobit

position4.Thehalfcarryisreset(H=0)duringtheseoperations,ifthereisnocarryfrombit

position4.

http://www.electronics.dit.ie/staff/tscarff/6800/registers/registers_6800.htm

2/3

7/7/2015

6800InternalRegisters

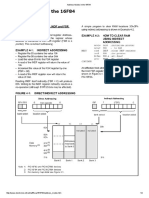

InternalBlockDiagramofthe6800CentralProcessingUnit(CPU)

http://www.electronics.dit.ie/staff/tscarff/6800/registers/registers_6800.htm

3/3

S-ar putea să vă placă și

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960De la EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Încă nu există evaluări

- Counts 16-Bits at A TimeDocument3 paginiCounts 16-Bits at A TimerajeshÎncă nu există evaluări

- Microprocessors and MicrocontrollersDocument22 paginiMicroprocessors and Microcontrollers6012 ANILÎncă nu există evaluări

- ARM Microcontrollers Programming for Embedded SystemsDe la EverandARM Microcontrollers Programming for Embedded SystemsEvaluare: 5 din 5 stele5/5 (1)

- 8051 Microcontroller Part 1Document21 pagini8051 Microcontroller Part 1Sardar IrfanullahÎncă nu există evaluări

- Experiment No: 1: OBJECTIVE: To Study About The Bus Organization and Programmable Model ofDocument5 paginiExperiment No: 1: OBJECTIVE: To Study About The Bus Organization and Programmable Model ofRutul PrajapatiÎncă nu există evaluări

- Course Title: Microcontroller and Interfacing Course Code:4214Document51 paginiCourse Title: Microcontroller and Interfacing Course Code:4214sreejith KBÎncă nu există evaluări

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationDe la EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationÎncă nu există evaluări

- 16 Bit Microprocessor 8086Document11 pagini16 Bit Microprocessor 8086Yogesh KuteÎncă nu există evaluări

- Mega Drive Architecture: Architecture of Consoles: A Practical Analysis, #3De la EverandMega Drive Architecture: Architecture of Consoles: A Practical Analysis, #3Încă nu există evaluări

- Microprocessor: Motorola 6800Document19 paginiMicroprocessor: Motorola 6800Anupam SinghÎncă nu există evaluări

- 8085 Microprocessor ArchitectureDocument3 pagini8085 Microprocessor Architecturetguna21Încă nu există evaluări

- Unit 1 Architecture of Pic 16cXXDocument41 paginiUnit 1 Architecture of Pic 16cXXKapilachander Thangavel100% (1)

- Game Boy Advance Architecture: Architecture of Consoles: A Practical Analysis, #7De la EverandGame Boy Advance Architecture: Architecture of Consoles: A Practical Analysis, #7Încă nu există evaluări

- 8085 Microprocessor June29Document9 pagini8085 Microprocessor June29Mworozi DicksonÎncă nu există evaluări

- 8085 Microprocessor NotesDocument25 pagini8085 Microprocessor NotesAjay Roopesh100% (1)

- PlayStation Architecture: Architecture of Consoles: A Practical Analysis, #6De la EverandPlayStation Architecture: Architecture of Consoles: A Practical Analysis, #6Încă nu există evaluări

- Tutorial On Introduction To 8085 Architecture and ProgrammingDocument23 paginiTutorial On Introduction To 8085 Architecture and ProgrammingdevÎncă nu există evaluări

- PlayStation 2 Architecture: Architecture of Consoles: A Practical Analysis, #12De la EverandPlayStation 2 Architecture: Architecture of Consoles: A Practical Analysis, #12Încă nu există evaluări

- 8085 MicroprocessorDocument23 pagini8085 Microprocessorauromaaroot196% (55)

- 6800Document11 pagini6800Nikola PetrovićÎncă nu există evaluări

- PIC MicrocontrollersDocument35 paginiPIC Microcontrollersanbuelectrical100% (1)

- Basics of Micro ProcessorDocument27 paginiBasics of Micro ProcessorBibin LeeÎncă nu există evaluări

- Master System Architecture: Architecture of Consoles: A Practical Analysis, #15De la EverandMaster System Architecture: Architecture of Consoles: A Practical Analysis, #15Încă nu există evaluări

- Amp Module 1Document14 paginiAmp Module 1fasnamditÎncă nu există evaluări

- C Programming for the Pc the Mac and the Arduino Microcontroller SystemDe la EverandC Programming for the Pc the Mac and the Arduino Microcontroller SystemÎncă nu există evaluări

- Unit Ii: PIC MicrocontrollersDocument59 paginiUnit Ii: PIC MicrocontrollersbalaÎncă nu există evaluări

- Assembly Language:Simple, Short, And Straightforward Way Of Learning Assembly ProgrammingDe la EverandAssembly Language:Simple, Short, And Straightforward Way Of Learning Assembly ProgrammingEvaluare: 2 din 5 stele2/5 (1)

- Intel 8085 Microprocessor ArchitectureDocument2 paginiIntel 8085 Microprocessor ArchitectureipoonamÎncă nu există evaluări

- Nintendo 64 Architecture: Architecture of Consoles: A Practical Analysis, #8De la EverandNintendo 64 Architecture: Architecture of Consoles: A Practical Analysis, #8Încă nu există evaluări

- Microprocessor SlideDocument60 paginiMicroprocessor Slideabm wahiduj jamanÎncă nu există evaluări

- SNES Architecture: Architecture of Consoles: A Practical Analysis, #4De la EverandSNES Architecture: Architecture of Consoles: A Practical Analysis, #4Încă nu există evaluări

- MPMC Unit 2Document31 paginiMPMC Unit 2nikitaÎncă nu există evaluări

- EC 6513 Microprocessor and Microcontroller ManualDocument121 paginiEC 6513 Microprocessor and Microcontroller Manualsaravanantec100% (1)

- PC Engine / TurboGrafx-16 Architecture: Architecture of Consoles: A Practical Analysis, #16De la EverandPC Engine / TurboGrafx-16 Architecture: Architecture of Consoles: A Practical Analysis, #16Încă nu există evaluări

- Case Study - 8085 MicroprocessorDocument14 paginiCase Study - 8085 MicroprocessorChat MateÎncă nu există evaluări

- GameCube Architecture: Architecture of Consoles: A Practical Analysis, #10De la EverandGameCube Architecture: Architecture of Consoles: A Practical Analysis, #10Încă nu există evaluări

- Ebooks For FreeDocument24 paginiEbooks For FreeNihar KhuranaÎncă nu există evaluări

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.De la EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Încă nu există evaluări

- Tutorial On Introduction To 8085 Architecture and ProgrammingDocument23 paginiTutorial On Introduction To 8085 Architecture and ProgrammingDennish KarkiÎncă nu există evaluări

- C Programming for the PIC Microcontroller: Demystify Coding with Embedded ProgrammingDe la EverandC Programming for the PIC Microcontroller: Demystify Coding with Embedded ProgrammingÎncă nu există evaluări

- CS18303 Microprocessor and Microcontroller Lecture NotesDocument160 paginiCS18303 Microprocessor and Microcontroller Lecture NotesDeepak SrinivasÎncă nu există evaluări

- Jump and Branch InstructionsDocument1 paginăJump and Branch InstructionsMANIKANDANÎncă nu există evaluări

- NES Architecture: Architecture of Consoles: A Practical Analysis, #1De la EverandNES Architecture: Architecture of Consoles: A Practical Analysis, #1Evaluare: 5 din 5 stele5/5 (1)

- Std10 Science EM 1Document71 paginiStd10 Science EM 1MANIKANDANÎncă nu există evaluări

- PIC Projects and Applications using C: A Project-based ApproachDe la EverandPIC Projects and Applications using C: A Project-based ApproachEvaluare: 4 din 5 stele4/5 (2)

- MicroC2 eCh15L08ARMDevelopmentToolsDocument39 paginiMicroC2 eCh15L08ARMDevelopmentToolsMANIKANDANÎncă nu există evaluări

- Lpc2148 DatasheetDocument38 paginiLpc2148 DatasheetSandeep ThompsonÎncă nu există evaluări

- SubroutinesDocument1 paginăSubroutinesMANIKANDANÎncă nu există evaluări

- Dreamcast Architecture: Architecture of Consoles: A Practical Analysis, #9De la EverandDreamcast Architecture: Architecture of Consoles: A Practical Analysis, #9Încă nu există evaluări

- Manchester EncodingDocument5 paginiManchester EncodingMANIKANDANÎncă nu există evaluări

- Sega Saturn Architecture: Architecture of Consoles: A Practical Analysis, #5De la EverandSega Saturn Architecture: Architecture of Consoles: A Practical Analysis, #5Încă nu există evaluări

- Electronics GuideDocument22 paginiElectronics GuideFernandes KennethÎncă nu există evaluări

- Intermediate C Programming for the PIC Microcontroller: Simplifying Embedded ProgrammingDe la EverandIntermediate C Programming for the PIC Microcontroller: Simplifying Embedded ProgrammingÎncă nu există evaluări

- Analogue To Digital Converters (ADC)Document3 paginiAnalogue To Digital Converters (ADC)MANIKANDANÎncă nu există evaluări

- Memory Timing AnalysisDocument3 paginiMemory Timing AnalysisMANIKANDANÎncă nu există evaluări

- 6800 Address ModesDocument1 pagină6800 Address ModesMANIKANDANÎncă nu există evaluări

- Formal Report 1: Arrange 10 Numbers in Ascending OrderDocument2 paginiFormal Report 1: Arrange 10 Numbers in Ascending OrderMANIKANDANÎncă nu există evaluări

- Address Modes in The 16F84Document2 paginiAddress Modes in The 16F84MANIKANDANÎncă nu există evaluări

- DramDocument3 paginiDramMANIKANDANÎncă nu există evaluări

- 6800 Internal RegistersDocument3 pagini6800 Internal RegistersMANIKANDANÎncă nu există evaluări

- Formal Report 1: Arrange 10 Numbers in Ascending OrderDocument2 paginiFormal Report 1: Arrange 10 Numbers in Ascending OrderMANIKANDANÎncă nu există evaluări

- VHDL FSM Tutorial MY FIRST FSMDocument29 paginiVHDL FSM Tutorial MY FIRST FSMMANIKANDANÎncă nu există evaluări

- VHDL TutorialDocument68 paginiVHDL TutorialPedro Pablo Parra AlbaÎncă nu există evaluări

- Memory Timing AnalysisDocument3 paginiMemory Timing AnalysisMANIKANDANÎncă nu există evaluări

- Review QuestionsDocument4 paginiReview QuestionsMANIKANDANÎncă nu există evaluări

- Program Control InstructionsDocument3 paginiProgram Control InstructionsMANIKANDANÎncă nu există evaluări

- Numbering Systems TutorialDocument5 paginiNumbering Systems TutorialMANIKANDANÎncă nu există evaluări

- Using EcalDocument4 paginiUsing EcalMANIKANDANÎncă nu există evaluări

- FT021/3 Computer Systems Summer 2004Document2 paginiFT021/3 Computer Systems Summer 2004MANIKANDANÎncă nu există evaluări

- FT021/3 Computer Systems Summer 2004Document2 paginiFT021/3 Computer Systems Summer 2004MANIKANDANÎncă nu există evaluări

- Delay LoopsDocument2 paginiDelay LoopsMANIKANDANÎncă nu există evaluări

- Pic16f8x PDFDocument126 paginiPic16f8x PDFGilberto MataÎncă nu există evaluări

- Introduction To Parallel PortsDocument5 paginiIntroduction To Parallel PortsMANIKANDANÎncă nu există evaluări

- Memory Timing AnalysisDocument3 paginiMemory Timing AnalysisMANIKANDANÎncă nu există evaluări

- Fetch and ExecuteDocument2 paginiFetch and ExecuteMANIKANDANÎncă nu există evaluări

- Troubleshooting: 8.1 Error Code TableDocument70 paginiTroubleshooting: 8.1 Error Code TableNestor GonzálezÎncă nu există evaluări

- Jump, Loop and Call InstructionsDocument25 paginiJump, Loop and Call InstructionsCasper InnocentÎncă nu există evaluări

- BOF enDocument86 paginiBOF enycÎncă nu există evaluări

- Picoblaze ProyectDocument10 paginiPicoblaze ProyectAlex PérezÎncă nu există evaluări

- Inside The 8051Document123 paginiInside The 8051mabat0Încă nu există evaluări

- Java's ArchitectureDocument16 paginiJava's Architectureraghu8215Încă nu există evaluări

- CS602PC - Compiler - Design - Lecture Notes - Unit - 4Document19 paginiCS602PC - Compiler - Design - Lecture Notes - Unit - 4Senthil Kumar SkumarÎncă nu există evaluări

- 8051 InterruptsDocument39 pagini8051 InterruptsShyam kumarÎncă nu există evaluări

- Microcomputer Components: 16-Bit CMOS Single-Chip MicrocontrollerDocument53 paginiMicrocomputer Components: 16-Bit CMOS Single-Chip MicrocontrollerpassnoÎncă nu există evaluări

- Instruction Op-Code Operand Bytes Machine - Cycles T - States DetailDocument3 paginiInstruction Op-Code Operand Bytes Machine - Cycles T - States DetailMonideep BanerjeeÎncă nu există evaluări

- Building and Using DLLsDocument5 paginiBuilding and Using DLLsyoung june kimÎncă nu există evaluări

- Cheat Sheet PDFDocument40 paginiCheat Sheet PDFxoureia laÎncă nu există evaluări

- CS401 Quiz 1Document383 paginiCS401 Quiz 1sapen79344Încă nu există evaluări

- Communication and InvocationDocument14 paginiCommunication and InvocationARVINDÎncă nu există evaluări

- GATE-2015 AnswerKeysDocument16 paginiGATE-2015 AnswerKeysAmit JindalÎncă nu există evaluări

- Chapter 6 Recursion PDFDocument16 paginiChapter 6 Recursion PDFBangtan gurlÎncă nu există evaluări

- Chapter 5 - Strings, Procedures and Macros: From Microprocessors and Interfacing by Douglas HallDocument25 paginiChapter 5 - Strings, Procedures and Macros: From Microprocessors and Interfacing by Douglas HallgokulchandruÎncă nu există evaluări

- Singularity - Rethinking The Software StackDocument13 paginiSingularity - Rethinking The Software StackComputer GuruÎncă nu există evaluări

- 100 C Interview Questions and Answers - C Online TestDocument8 pagini100 C Interview Questions and Answers - C Online TestEr Nayan PithadiyaÎncă nu există evaluări

- 12f508 PDFDocument100 pagini12f508 PDFZdravko RusevÎncă nu există evaluări

- Apple SecureCodingGuideDocument114 paginiApple SecureCodingGuideErnest CunninghamÎncă nu există evaluări

- 8-Bit Microcontroller With 16K Bytes In-System Programmable Flash Atmega16 Atmega16LDocument50 pagini8-Bit Microcontroller With 16K Bytes In-System Programmable Flash Atmega16 Atmega16LKamal Singh RathoreÎncă nu există evaluări

- Vtu 4th Sem Microprocessor and Microcontroller Module - 5Document17 paginiVtu 4th Sem Microprocessor and Microcontroller Module - 5kimbap0% (1)

- Q. 8086 Programmer's Model: Register Organization (IMP)Document6 paginiQ. 8086 Programmer's Model: Register Organization (IMP)Sukanti PalÎncă nu există evaluări

- Deep C ModifiedDocument449 paginiDeep C ModifiedAmit DubeyÎncă nu există evaluări

- Mpi V Sem It Guess Paper SolutionsDocument52 paginiMpi V Sem It Guess Paper Solutionshofehag577Încă nu există evaluări

- COAL Course OutlineDocument2 paginiCOAL Course Outlineroxter_15100% (1)

- Third Homework AssignmentDocument4 paginiThird Homework AssignmentTara Shankar ChakrabortyÎncă nu există evaluări

- Procedure CallsDocument19 paginiProcedure CallsMario Sebastian Rubio ToroÎncă nu există evaluări

- testBankCh05 PDFDocument11 paginitestBankCh05 PDFEnoch0% (1)

- Unlock Any Roku Device: Watch Shows, TV, & Download AppsDe la EverandUnlock Any Roku Device: Watch Shows, TV, & Download AppsÎncă nu există evaluări

- Chip War: The Quest to Dominate the World's Most Critical TechnologyDe la EverandChip War: The Quest to Dominate the World's Most Critical TechnologyEvaluare: 4.5 din 5 stele4.5/5 (227)

- CompTIA Security+ All-in-One Exam Guide, Sixth Edition (Exam SY0-601)De la EverandCompTIA Security+ All-in-One Exam Guide, Sixth Edition (Exam SY0-601)Evaluare: 5 din 5 stele5/5 (1)

- iPhone 15 Pro User Guide for Beginners and SeniorsDe la EverandiPhone 15 Pro User Guide for Beginners and SeniorsÎncă nu există evaluări

- Computer Science: A Concise IntroductionDe la EverandComputer Science: A Concise IntroductionEvaluare: 4.5 din 5 stele4.5/5 (14)

- Chip War: The Fight for the World's Most Critical TechnologyDe la EverandChip War: The Fight for the World's Most Critical TechnologyEvaluare: 4.5 din 5 stele4.5/5 (82)

- iPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XDe la EverandiPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XEvaluare: 3 din 5 stele3/5 (2)

- CompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102De la EverandCompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Evaluare: 5 din 5 stele5/5 (2)

- CompTIA A+ Complete Practice Tests: Core 1 Exam 220-1101 and Core 2 Exam 220-1102De la EverandCompTIA A+ Complete Practice Tests: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Încă nu există evaluări

- Amazon Echo Manual Guide : Top 30 Hacks And Secrets To Master Amazon Echo & Alexa For Beginners: The Blokehead Success SeriesDe la EverandAmazon Echo Manual Guide : Top 30 Hacks And Secrets To Master Amazon Echo & Alexa For Beginners: The Blokehead Success SeriesÎncă nu există evaluări

- Amazon Web Services (AWS) Interview Questions and AnswersDe la EverandAmazon Web Services (AWS) Interview Questions and AnswersEvaluare: 4.5 din 5 stele4.5/5 (3)

- Mastering IoT For Industrial Environments: Unlock the IoT Landscape for Industrial Environments with Industry 4.0, Covering Architecture, Protocols like MQTT, and Advancements with ESP-IDFDe la EverandMastering IoT For Industrial Environments: Unlock the IoT Landscape for Industrial Environments with Industry 4.0, Covering Architecture, Protocols like MQTT, and Advancements with ESP-IDFÎncă nu există evaluări

- Programming with STM32: Getting Started with the Nucleo Board and C/C++De la EverandProgramming with STM32: Getting Started with the Nucleo Board and C/C++Evaluare: 3.5 din 5 stele3.5/5 (3)

- Hacking With Linux 2020:A Complete Beginners Guide to the World of Hacking Using Linux - Explore the Methods and Tools of Ethical Hacking with LinuxDe la EverandHacking With Linux 2020:A Complete Beginners Guide to the World of Hacking Using Linux - Explore the Methods and Tools of Ethical Hacking with LinuxÎncă nu există evaluări

- Windows 10 Mastery: The Complete User Guide to Learn Windows 10 from Beginner to ExpertDe la EverandWindows 10 Mastery: The Complete User Guide to Learn Windows 10 from Beginner to ExpertEvaluare: 3.5 din 5 stele3.5/5 (6)

- iPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsDe la EverandiPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsEvaluare: 5 din 5 stele5/5 (2)

- Raspberry Pi Retro Gaming: Build Consoles and Arcade Cabinets to Play Your Favorite Classic GamesDe la EverandRaspberry Pi Retro Gaming: Build Consoles and Arcade Cabinets to Play Your Favorite Classic GamesÎncă nu există evaluări

- How to Jailbreak Roku: Unlock Roku, Roku Stick, Roku Ultra, Roku Express, Roku TV with Kodi Step by Step GuideDe la EverandHow to Jailbreak Roku: Unlock Roku, Roku Stick, Roku Ultra, Roku Express, Roku TV with Kodi Step by Step GuideEvaluare: 1 din 5 stele1/5 (1)

- CompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002De la EverandCompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002Evaluare: 5 din 5 stele5/5 (1)