Documente Academic

Documente Profesional

Documente Cultură

Tsu and TH - Pdfsdfsdsa

Încărcat de

asfagehejhdhdsgdfsdfgTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Tsu and TH - Pdfsdfsdsa

Încărcat de

asfagehejhdhdsgdfsdfgDrepturi de autor:

Formate disponibile

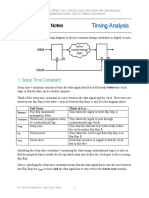

Review of Flip Flop Setup and Hold Time

I Considering D-type

edge-triggered, Flip Flops (FFs)

I Just

before and just after the clock edge, there is a critical time region

where the D input must not change.

I The

region just before the clock edge is called setup time (tsu)

I The

region just after the clock edge is called hold time (th)

FF has minimum required values for tsu and th.

I Every

Review of Flip Flop Setup and Hold Time

I Usually

I From

found in the data sheet or .lib file.

saed90nm typ ht.lib:

cell(AODFFARX2) {

pin(D) {

timing() {

timing_type

: setup_rising; related_pin :

"CLK";

fall_constraint(vio_0_7_7) { values( " 0.129318, 0.130474, 0.134615, 0.143814, 0.164042, 0.205415,

0.275800",\

" 0.126790, 0.128403, 0.132544, 0.141743, 0.161972, 0.203344, 0.273730",\

rise_constraint(vio_0_7_7) { values( " 0.181503, 0.183574, 0.188631, 0.198288, 0.216227, 0.246614,

0.286787",\

" 0.178975, 0.181046, 0.186103, 0.195759, 0.213699, 0.243627, 0.284258",\ .............

timing() {

timing_type

: hold_rising; related_pin

:

"CLK";

fall_constraint(vio_0_7_7) { values( " -0.073929, -0.075542, -0.079683, -0.088882, -0.108653, -0.146363, 0.206220",\

" -0.071858, -0.073471, -0.077155, -0.086354, -0.106582, -0.144293, -0.204150",\ .............

I FFs

in ASIC libraries have tsus about 3-10x the tpd of a 1x inverter.

Review of Flip Flop Setup and Hold Time

I They

have ths ranging from about negative 1 x the tpd of an inverter to

positive 1-2x the tpd of the same inverter.

I tsu and th vary

strongly with temperature, voltage and process.

I tsu and th are

I If

functions of the Gbw of the FF transistors.

the D input changes within the tsu and th window, Q may:

I

I

Follow D correctly I Follow D incorrectly

Assume a metastable state for an indeterminate time followed by a

transition to logic 1 or logic 0.

of:

clock to Q delay of FF0 (tckq) I propagation delay through combo logic (tpd) I

the required setup time (tsu) of FF1

I tckq and tpd are

both delays. tsu is a constraint of FF operation.

Review of Flip Flop Setup and Hold Time

I The

circuit provides setup time as a function of the clock period, tckq and

combo logic delay tpd.

I The

FF requires a specified tsu to operate correctly.

I The difference between the two is called setup time slack.

Review of Flip Flop Setup and Hold Time

setup time slack = (provided setup time) - (required setup time) I We

always want positive slack.

Review of Flip Flop Setup and Hold Time

I An

example: find the setup slack

I What

is the minimum cycle time for the circuit?

Review of Flip Flop Setup and Hold Time

I What

is the minimum cycle time for the circuit?

Review of Flip Flop Setup and Hold Time

I minimum

cycle time

= tckq + tpd + tsu

= 200 + 300 + 100

= 600pS

Review of Flip Flop Setup and Hold Time

I Hold

time is the amount of time that FF0s old data must persist at the

D input of FF1 after the clock edge.

I FFs have a specified minimum hold time.

I The

circuit provides hold time to the FF of (tckq + tpd).

I Hold time slack = (hold time provided - hold time required)

Review of Flip Flop Setup and Hold Time

I Worst

I In

case hold time scenario: FFs directly connected D-to-Q.

this case, the provided hold time is the tckq of the previous FF.

I This

places a restriction on FF timing such that tckq>th

Review of Flip Flop Setup and Hold Time

I So

far, we have looked at FF timing assuming an ideal clock.

I Each

I In

FF saw the clock edge at exactly the same time.

reality, this does not happen.

Interconnect metal length to FF clock pins differs slightly.

I Some FFs have differing capacitance at their clock pins.

I The tpd of the clock tree buffers will be effected by differing temperature

and voltage across the die. These effects are dynamic and cannot be

determined apriori.

I

Review of Flip Flop Setup and Hold Time

I Imperfections

in clock arrival time are called clock skew. I If clock

skew causes clock to arrive later at FF1 than FF0, data leapfrogs

past FF1.

Review of Flip Flop Setup and Hold Time

I If

clock skew casues clock to arrive earlier at FF1 than FF0, data has less

time to reach FF1.

I This requires the clock period must be lengthened over what it could

have been without skew.

Review of Flip Flop Setup and Hold Time

I i.e.,

the system is slower.

Review of Flip Flop Setup and Hold Time

I The

presence of skew simply takes away directly from any slack (setup

or hold) that may exist.

I A more complete picture of setup and hold slack would be:

setup slack = (cycle time - tckq - tpd -tsu) - clock skew I hold slack = (tckq + tpd th) - clock skew

I We

can get more setup slack by slowing down a system.

I There

is nothing you can do to fix hold time slack after fabrication!

S-ar putea să vă placă și

- Set Up DelayDocument15 paginiSet Up DelayNathan BrooksÎncă nu există evaluări

- Timing (3rd Internal)Document13 paginiTiming (3rd Internal)Utsav ParasharÎncă nu există evaluări

- What Is Setup and Hold Time?Document12 paginiWhat Is Setup and Hold Time?Minu MathewÎncă nu există evaluări

- Setup and Hold TimeDocument6 paginiSetup and Hold TimeShobhit GargÎncă nu există evaluări

- Setup and Hold - PDF Version 1Document15 paginiSetup and Hold - PDF Version 1naniÎncă nu există evaluări

- Set Hold BasicsDocument17 paginiSet Hold BasicsMelissa AdamsÎncă nu există evaluări

- Chip Level Timing: ECE124 Digital Circuits and SystemsDocument18 paginiChip Level Timing: ECE124 Digital Circuits and SystemspdnoobÎncă nu există evaluări

- Timing in Digital Circuits - NotesDocument9 paginiTiming in Digital Circuits - NotesKowshick GuruÎncă nu există evaluări

- Equations and Impacts of Setup and Hold TimeDocument5 paginiEquations and Impacts of Setup and Hold TimeShravan Kumar AshannagariÎncă nu există evaluări

- Setup and Hold Time - Semicon ShortsDocument4 paginiSetup and Hold Time - Semicon ShortsSai Uttej MandalaÎncă nu există evaluări

- Equations and Impacts of Setup and Hold Time: SkewDocument5 paginiEquations and Impacts of Setup and Hold Time: SkewVardhan KarnatiÎncă nu există evaluări

- Equations and Impacts of Setup and Hold TimeDocument5 paginiEquations and Impacts of Setup and Hold Timepavithra reddyÎncă nu există evaluări

- Sta Notes 1671631469 PDFDocument47 paginiSta Notes 1671631469 PDFAathith SaiprasadÎncă nu există evaluări

- Setup and Hold Time - Static Timing Analysis (STA) Basic (Part 3a) - VLSI ConceptsDocument3 paginiSetup and Hold Time - Static Timing Analysis (STA) Basic (Part 3a) - VLSI ConceptsRakesh KumarÎncă nu există evaluări

- Timing Paths: ContinuedDocument18 paginiTiming Paths: ContinuedAnusha ChidagniÎncă nu există evaluări

- Vlsi ConceptsDocument168 paginiVlsi ConceptsSGSÎncă nu există evaluări

- What Is STA ?Document13 paginiWhat Is STA ?veeru100% (1)

- STI - FSM - SolutionsDocument6 paginiSTI - FSM - SolutionsAishwarya GajendrulaÎncă nu există evaluări

- Setup and Hold Time Violation Static Timing Analysis (STA) Basic (Part 3b) VLSI ConceptsDocument14 paginiSetup and Hold Time Violation Static Timing Analysis (STA) Basic (Part 3b) VLSI ConceptsĐứcĐỗÎncă nu există evaluări

- Setup and Hold Time - Static Timing Analysis (STA) Basic (Part 3a) - VLSI ConceptsDocument6 paginiSetup and Hold Time - Static Timing Analysis (STA) Basic (Part 3a) - VLSI ConceptsRatnadeep GuptaÎncă nu există evaluări

- DFF Setup Hold ReviewDocument50 paginiDFF Setup Hold ReviewAkanksha221291Încă nu există evaluări

- Static Timing Analysis-1Document58 paginiStatic Timing Analysis-1Pooja selvamÎncă nu există evaluări

- Delay Calculation (IMP)Document28 paginiDelay Calculation (IMP)Amarnath Reddy100% (1)

- Interview QuestionsDocument13 paginiInterview QuestionsVENKATRAMANÎncă nu există evaluări

- Clock Definitions: Rising and Falling Edge of The ClockDocument8 paginiClock Definitions: Rising and Falling Edge of The ClockSrinivas CherukuÎncă nu există evaluări

- What Is MetastabilityDocument5 paginiWhat Is Metastabilityaarthi100Încă nu există evaluări

- Static Timing AnalysisDocument32 paginiStatic Timing AnalysisShantanu Sarkar100% (1)

- Timing Analysis: Supplementary NotesDocument6 paginiTiming Analysis: Supplementary NotesSRINIKHIL GollaÎncă nu există evaluări

- QUALCOMM Interview Questions 1. Basic View of Compression?Document9 paginiQUALCOMM Interview Questions 1. Basic View of Compression?deepa100% (2)

- STA FinalDocument66 paginiSTA FinalgauravkshriÎncă nu există evaluări

- DFTDocument14 paginiDFTRahulÎncă nu există evaluări

- STA Basics by Atun1Document10 paginiSTA Basics by Atun1Nishanth GowdaÎncă nu există evaluări

- TIMINGDocument3 paginiTIMINGRAZÎncă nu există evaluări

- PD FinalDocument25 paginiPD FinalAnusha ChidagniÎncă nu există evaluări

- How A Latch/flip-Flop Goes MetastableDocument3 paginiHow A Latch/flip-Flop Goes MetastableAmena FarhatÎncă nu există evaluări

- Lect17 SeqDocument18 paginiLect17 SeqorengeneralÎncă nu există evaluări

- Clock Tree Synthesis EditedDocument3 paginiClock Tree Synthesis EditedTarikul IslamÎncă nu există evaluări

- Setup & Hold ViolationDocument20 paginiSetup & Hold ViolationdeepaÎncă nu există evaluări

- Timing Issues: by Deepa .BDocument21 paginiTiming Issues: by Deepa .BdeepaÎncă nu există evaluări

- Setup and Hold Time BasicsDocument9 paginiSetup and Hold Time BasicsMahmoud MagdiÎncă nu există evaluări

- Lab Exercise2 - Edge TriggeredDocument4 paginiLab Exercise2 - Edge Triggeredrktiwary256034Încă nu există evaluări

- Sequential Code: ProcessDocument10 paginiSequential Code: ProcessChutiyaÎncă nu există evaluări

- Static Timing Analysis (Sta)Document8 paginiStatic Timing Analysis (Sta)Bck SreedharÎncă nu există evaluări

- New Microsoft PowerPoint PresentationDocument9 paginiNew Microsoft PowerPoint PresentationAnusha SagiÎncă nu există evaluări

- PnR-II-CTS Routing Chip FinishingDocument88 paginiPnR-II-CTS Routing Chip Finishingyhossam95Încă nu există evaluări

- Meta StabilityDocument16 paginiMeta StabilitySahil SharmaÎncă nu există evaluări

- UPLOAD - Simile NavasDocument19 paginiUPLOAD - Simile NavasAnonymous VASS3z0wTHÎncă nu există evaluări

- A Snippet of The STA WorkshopDocument15 paginiA Snippet of The STA WorkshopCyrille MagdiÎncă nu există evaluări

- How Does Clock Reconvergence Pessimism Removal (CRPR) Handle Dynamically Switched Related ClocksDocument4 paginiHow Does Clock Reconvergence Pessimism Removal (CRPR) Handle Dynamically Switched Related ClocksmanojkumarÎncă nu există evaluări

- Embedded Real TimeDocument60 paginiEmbedded Real Timepraveen_kodgirwarÎncă nu există evaluări

- Clock Setup and Hold Slack ExplainedDocument11 paginiClock Setup and Hold Slack Explainedmyforforum0% (1)

- Static Timing Analysis in VLSI CircuitsDocument16 paginiStatic Timing Analysis in VLSI CircuitseeshgargÎncă nu există evaluări

- PLCHAPTER07Document70 paginiPLCHAPTER07Bayu Ardiansyah100% (1)

- VLSI System DesignDocument6 paginiVLSI System DesignbigfatdashÎncă nu există evaluări

- Digital Design Interview QuestionsDocument24 paginiDigital Design Interview QuestionsprabhatÎncă nu există evaluări

- WAN TECHNOLOGY FRAME-RELAY: An Expert's Handbook of Navigating Frame Relay NetworksDe la EverandWAN TECHNOLOGY FRAME-RELAY: An Expert's Handbook of Navigating Frame Relay NetworksÎncă nu există evaluări

- Nonlinear Electronics 2: Flip-Flops, ADC, DAC and PLLDe la EverandNonlinear Electronics 2: Flip-Flops, ADC, DAC and PLLÎncă nu există evaluări

- All-Digital Frequency Synthesizer in Deep-Submicron CMOSDe la EverandAll-Digital Frequency Synthesizer in Deep-Submicron CMOSÎncă nu există evaluări

- RLU Report Layout UtilityDocument8 paginiRLU Report Layout UtilityVISHNU400100% (1)

- Lab1 - Introduction To Digital Control Laboratory - 17-10-2018Document19 paginiLab1 - Introduction To Digital Control Laboratory - 17-10-2018Eng. Ibrahim Abdullah AlruhmiÎncă nu există evaluări

- Small, Low Power, 3-Axis 200 G Accelerometer: ADXL377Document12 paginiSmall, Low Power, 3-Axis 200 G Accelerometer: ADXL377alaa adienÎncă nu există evaluări

- Aspire 5670 (Quanta ZB1) SchematicsDocument50 paginiAspire 5670 (Quanta ZB1) SchematicsjeanpellÎncă nu există evaluări

- Practice 1: Introduction To PL/SQL: Number - of - Days - in - February - This - YearDocument13 paginiPractice 1: Introduction To PL/SQL: Number - of - Days - in - February - This - YearPedro SantosÎncă nu există evaluări

- Adveon Installation Guide V1.3 and V1.5 - Edgecam - BasicDocument46 paginiAdveon Installation Guide V1.3 and V1.5 - Edgecam - BasictibikomaÎncă nu există evaluări

- GSM-R/ETCS Integration ReviewDocument82 paginiGSM-R/ETCS Integration ReviewTiémogo TRAOREÎncă nu există evaluări

- Mock MeetingDocument4 paginiMock MeetinghasbullahputraÎncă nu există evaluări

- Labsheet 1Document4 paginiLabsheet 1KarthikÎncă nu există evaluări

- U (For A User-Defined User Exit) or S (For A Standard User Exit)Document10 paginiU (For A User-Defined User Exit) or S (For A Standard User Exit)biltexÎncă nu există evaluări

- PN-VC841H: Intelligent Touch BoardDocument3 paginiPN-VC841H: Intelligent Touch BoardMohamed ShawkyÎncă nu există evaluări

- Eden Net GSM Anr GuideDocument101 paginiEden Net GSM Anr GuidescarrilcÎncă nu există evaluări

- Evolution-of-wireless-networks-technologies-history-and-emerging-technology-of-5GDocument5 paginiEvolution-of-wireless-networks-technologies-history-and-emerging-technology-of-5GultrahornytgtÎncă nu există evaluări

- Usb Debug Remotely Via AdbDocument11 paginiUsb Debug Remotely Via AdbMarkioni MgayaÎncă nu există evaluări

- Lab 1.2.7 Wireless Component and Media IdentificationDocument13 paginiLab 1.2.7 Wireless Component and Media IdentificationfathiwestÎncă nu există evaluări

- 202MK7 E-Spec OM VBDocument2 pagini202MK7 E-Spec OM VBCsongor BaloghÎncă nu există evaluări

- CCIE EI v1.1 - Deploy Lab 1 - Section 1 - 24-Nov-2023Document57 paginiCCIE EI v1.1 - Deploy Lab 1 - Section 1 - 24-Nov-2023achmmygn9Încă nu există evaluări

- PG DV250Document14 paginiPG DV250admirduÎncă nu există evaluări

- Epo 510 RG Log Files 0-00 En-UsDocument10 paginiEpo 510 RG Log Files 0-00 En-UsabbuasherÎncă nu există evaluări

- Cambridge IGCSE (9-1) : Computer Science 0984/11Document12 paginiCambridge IGCSE (9-1) : Computer Science 0984/11hussain korirÎncă nu există evaluări

- Module-Week 5Document2 paginiModule-Week 5Maria Christina ManzanoÎncă nu există evaluări

- 3ds Emulator With Bios For PC and Mac - Pokemon X and y SuppDocument1 pagină3ds Emulator With Bios For PC and Mac - Pokemon X and y SuppGabriel O'HaraÎncă nu există evaluări

- K2000TC V3.1 Operation 150318Document219 paginiK2000TC V3.1 Operation 150318KV SAI KIRANÎncă nu există evaluări

- Instruction of The Software MPE-822R - 825RDocument2 paginiInstruction of The Software MPE-822R - 825RRoberto TorresÎncă nu există evaluări

- 1) Develop A Java Program To Draw An Applet of Size 300X200 That Prints "Hello World" Text On The Applet Window. Source Code: Helloworldapplet - JavaDocument12 pagini1) Develop A Java Program To Draw An Applet of Size 300X200 That Prints "Hello World" Text On The Applet Window. Source Code: Helloworldapplet - JavaB.J NakumÎncă nu există evaluări

- Router Zte ZXHN H267NDocument13 paginiRouter Zte ZXHN H267NFrancisco GonzalezÎncă nu există evaluări

- Manual SDKDocument59 paginiManual SDKrrarcondoÎncă nu există evaluări

- Motro & Drives - Fall EditionDocument59 paginiMotro & Drives - Fall EditionHavandinhÎncă nu există evaluări

- Mosfets As Current Sources: Analog ElectronicsDocument22 paginiMosfets As Current Sources: Analog ElectronicsPARTH RAMANUJÎncă nu există evaluări