Documente Academic

Documente Profesional

Documente Cultură

Nrr059210505 Computer Organization

Încărcat de

andhracollegesDescriere originală:

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Nrr059210505 Computer Organization

Încărcat de

andhracollegesDrepturi de autor:

Formate disponibile

www.andhracolleges.

com The Complete Information About Colleges in Andhra Pradesh

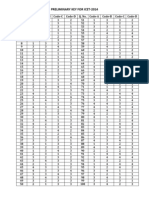

Code No: R059210505 Set No. 1

II B.Tech I Semester Regular Examinations, November 2006

COMPUTER ORGANIZATION

( Common to Computer Science & Engineering, Information Technology

and Computer Science & Systems Engineering)

Time: 3 hours Max Marks: 80

Answer any FIVE Questions

All Questions carry equal marks

www.andhracolleges.com

⋆⋆⋆⋆⋆

1. (a) What are the different interconnection structures used in multiprocessors. Ex-

plain about multistage crossbar switch. [8]

(b) Support or oppose the statement ?Every efficient serial program is efficient

parallel program? [8]

2. Design register selection circuit to select one of the four 4-bit registers content on

to bus. Give fuller explanation. [16]

3. (a) What are the major design considerations in microinstruction sequencing?. [8]

(b) Explain about microinstruction sequencing techniques, specifically variable

format address microinstruction. [8]

4. (a) Explain Booth’s algorithm with its theoretical basis. [8]

(b) Represent two n-bit unsigned numbers multiplications with a series of n/2-bit

multiplications. [8]

5. (a) What is Redundant Array of Inexpensive Discs? What are the advantages of

www.andhracolleges.com

using this kind of systems?

(b) Explain different levels of RAID [8+8]

6. Write short notes on the following:

(a) DMA Controller

(b) I O P

(c) I/O Devices [6+6+4]

7. What is pipelining? Explain pipeline processing with an example. [16]

8. Write short notes on the following

(a) Time-shared common bus organization [6]

(b) Multiport memory organization [5]

(c) System bus structure for multiprocessors [5]

⋆⋆⋆⋆⋆

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

1 ofUSA-UK-Australia-Germany-France-NewZealand

1 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: R059210505 Set No. 2

II B.Tech I Semester Regular Examinations, November 2006

COMPUTER ORGANIZATION

( Common to Computer Science & Engineering, Information Technology

and Computer Science & Systems Engineering)

Time: 3 hours Max Marks: 80

Answer any FIVE Questions

All Questions carry equal marks

www.andhracolleges.com

⋆⋆⋆⋆⋆

1. (a) Explain the terms compiler, linker, assembler, loader and describe how a C

program or any other high level language program is executed in a system.

Indicate entire process with a figure.

(b) Distinguish between high level and low level languages?. What are the re-

quirements for a good programming language? [16]

2. Design a circuit to increment, decrement, complement and clear a 4 bit register

using RS flip-flops. Explain the control logic. [16]

3. (a) Give the typical horizontal and vertical microinstruction formats. [8]

(b) Describe how microinstructions are arranged in control memory and how they

are interpreted. [8]

4. (a) Multiply 10111 with 10011 using, Booths algorithm. [8]

(b) Explain booths algorithm with its theoretical basis. [8]

5. Compare and contrast Asynchronous DRAM and Synchronous DRAM. [16]

www.andhracolleges.com

6. (a) Explain bit oriented and character oriented protocols in serial communication

(b) What are the different issues behind serial communication? Explain. [8+8]

7. (a) What is Flynn’s classification? Categorize [6]

(b) Explain each stream of the Flynn’s classification with an example. [10]

8. (a) Explain the working of 8 x 8 Omega Switching network.

(b) Explain the functioning of Binary Tree network with 2 x 2 Switches. Show a

neat sketch [8+8]

⋆⋆⋆⋆⋆

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

1 ofUSA-UK-Australia-Germany-France-NewZealand

1 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: R059210505 Set No. 3

II B.Tech I Semester Regular Examinations, November 2006

COMPUTER ORGANIZATION

( Common to Computer Science & Engineering, Information Technology

and Computer Science & Systems Engineering)

Time: 3 hours Max Marks: 80

Answer any FIVE Questions

All Questions carry equal marks

www.andhracolleges.com

⋆⋆⋆⋆⋆

1. (a) Explain about sign magnitude and 2’s complement approaches for representing

the fixed point numbers. Why 2’s complement is preferable.

(b) Give means to identify whether or not an overflow has occurred in 2s comple-

ment addition or subtraction operations. Take one example for each possible

situation and explain. Assume 4 bit registers.

(c) Distinguish between tightly coupled microprocessors and tightly coupled Mi-

croprocessors. [16]

2. Mention about full adder circuit functionality with inputs and outputs using a block

diagram. Using FA blocks design combined adder cum subtractor circuit. Assume

two numbers are 4-bit numbers. [16]

3. (a) Why do we need subroutine register in a control unit?. Explain. [8]

(b) Why do we need some bits of current microinstruction to generate address of

the next microinstruction. Support with a live example. [8]

4. (a) Draw a flow chart which explains multiplication of two signed magnitude fixed

www.andhracolleges.com

point numbers. [8]

(b) Multiply 10111 with 10011 with the above procedure given (a). Show all the

registers content for each step. [8]

5. Compare and contrast Asynchronous DRAM and Synchronous DRAM. [16]

6. Explain the following:

(a) Isolated Vs Memory mapped I/O

(b) I/O Bus Vs Memory Bus

(c) I/O Interface

(d) Peripheral Devices [4+4+4+4]

7. Explain the following with related to the Instruction Pipeline

(a) Pipeline conflicts

(b) Data dependency

(c) Hardware interlocks

(d) Operand forwarding

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

1 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: R059210505 Set No. 3

(e) Delayed load

(f) Pre-fetch target instruction

(g) Branch target buffer

(h) Delayed branch [8×2=16]

8. (a) Explain the working of 8 x 8 Omega Switching network.

www.andhracolleges.com

(b) Explain the functioning of Binary Tree network with 2 x 2 Switches. Show a

neat sketch [8+8]

⋆⋆⋆⋆⋆

www.andhracolleges.com

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

2 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: R059210505 Set No. 4

II B.Tech I Semester Regular Examinations, November 2006

COMPUTER ORGANIZATION

( Common to Computer Science & Engineering, Information Technology

and Computer Science & Systems Engineering)

Time: 3 hours Max Marks: 80

Answer any FIVE Questions

All Questions carry equal marks

www.andhracolleges.com

⋆⋆⋆⋆⋆

1. (a) Explain about various buses such as internal, external, backplane, I/O, system,

address, data, synchronous and asynchronous. [10]

(b) Distinguish between high level and low level languages? What are the require-

ments for a good programming language?

(6)

2. (a) Explain about stack organization used in processors. What do you understand

by register stack and memory stack? [10]

(b) Explain how X=(A+B)/(A-B) is evaluated in a stack based computer. [6]

3. Draw the general block diagram of a microsequencer. Explain clearly the inputs

and outputs of the same along with their functioning. [16]

4. Draw a flowchart to explain how two IEEE 754 floating point numbers can be

added, subtracted and multiplied. Assume single precision numbers. Give example

for each [16]

www.andhracolleges.com

5. (a) What is a virtual memory technique? Explain different virtual memory tech-

niques.

[8]

(b) Explain how the technique of paging can be implemented [8]

6. (a) What is Direct Memory Access? Explain the working of DMA.

(b) What are the different kinds of DMA transfers? Explain.

(c) What are the advantages of using DMA transfers? [8+4+4]

7. (a) What is meant by arithmetic pipeline? Explain. [8]

(b) Explain pipeline for floating point addition and subtraction. [8]

8. (a) Explain the working of 8 x 8 Omega Switching network.

(b) Explain the functioning of Binary Tree network with 2 x 2 Switches. Show a

neat sketch [8+8]

⋆⋆⋆⋆⋆

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

1 ofUSA-UK-Australia-Germany-France-NewZealand

1 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

S-ar putea să vă placă și

- Polycet 2014 ST Certificatates Verification DatesDocument1 paginăPolycet 2014 ST Certificatates Verification DatesandhracollegesÎncă nu există evaluări

- Eamcet 2014 Engineering Key SolutionsDocument42 paginiEamcet 2014 Engineering Key Solutionsandhracolleges100% (1)

- Eamcet Agriculture Last Ranks Cutoffs Andhracolleges Eamcet 2013 CutoffsDocument3 paginiEamcet Agriculture Last Ranks Cutoffs Andhracolleges Eamcet 2013 Cutoffsandhracolleges33% (3)

- Polycet2014 Web Counselling NotificationDocument2 paginiPolycet2014 Web Counselling NotificationandhracollegesÎncă nu există evaluări

- Andhracollege Eamcet 2014 Engineering Question Paper With Key SolutionsDocument62 paginiAndhracollege Eamcet 2014 Engineering Question Paper With Key Solutionsandhracolleges50% (4)

- EAMCET 2014 Agriculture & Medical Preliminary Answer KeysDocument1 paginăEAMCET 2014 Agriculture & Medical Preliminary Answer KeysLohith_EnggÎncă nu există evaluări

- JEE Main Advanced 2014 Paper I Maths Paper Answer SolutionsDocument4 paginiJEE Main Advanced 2014 Paper I Maths Paper Answer Solutionsandhracolleges100% (1)

- Polycet 2014 SC BC Oc Certificatates Verification DatesDocument1 paginăPolycet 2014 SC BC Oc Certificatates Verification DatesandhracollegesÎncă nu există evaluări

- ICET 2014 Preliminary Key Primary Key AndhracollegesDocument2 paginiICET 2014 Preliminary Key Primary Key AndhracollegesandhracollegesÎncă nu există evaluări

- Eamcet 2014 Engineering Jntu Preliminary Key AndhracollegesDocument1 paginăEamcet 2014 Engineering Jntu Preliminary Key AndhracollegesandhracollegesÎncă nu există evaluări

- JEE Advanced 2014 Paper I PHYSICS Paper Answer SolutionsDocument6 paginiJEE Advanced 2014 Paper I PHYSICS Paper Answer SolutionsandhracollegesÎncă nu există evaluări

- Polycet 2014 Question PaperDocument24 paginiPolycet 2014 Question PaperandhracollegesÎncă nu există evaluări

- JEE Main Advanced Paper I Answer Key 25 May 2014Document1 paginăJEE Main Advanced Paper I Answer Key 25 May 2014andhracollegesÎncă nu există evaluări

- JEE Advanced 2014 Paper I Chemistry Paper Answer SolutionsDocument4 paginiJEE Advanced 2014 Paper I Chemistry Paper Answer SolutionsandhracollegesÎncă nu există evaluări

- Eamcet 2014 Medical Question Paper With Key Solutions AndhracollegesDocument62 paginiEamcet 2014 Medical Question Paper With Key Solutions Andhracollegesandhracolleges100% (1)

- Eamcet 2014 Engineering Key Solutions AndhracollegesDocument42 paginiEamcet 2014 Engineering Key Solutions Andhracollegesandhracolleges75% (8)

- Eamcet 2012 Medical PaperDocument60 paginiEamcet 2012 Medical Paperandhracolleges100% (1)

- Eamcet 2014 Medical Question Paper AndhracollegesDocument62 paginiEamcet 2014 Medical Question Paper Andhracollegesandhracolleges100% (1)

- Eamcet 2012 Engineering PaperDocument62 paginiEamcet 2012 Engineering Paperandhracolleges100% (1)

- Eamcet 2012 Engineering Paper KeyDocument1 paginăEamcet 2012 Engineering Paper KeyandhracollegesÎncă nu există evaluări

- Eamcet 2013 Engineering PaperDocument62 paginiEamcet 2013 Engineering Paperandhracolleges0% (1)

- Eamcet 2012 Engineering Paper KeyDocument1 paginăEamcet 2012 Engineering Paper KeyandhracollegesÎncă nu există evaluări

- Eamcet 2012 Medical Paper KeyDocument1 paginăEamcet 2012 Medical Paper KeyandhracollegesÎncă nu există evaluări

- Eamcet 2011 Engineering PaperDocument61 paginiEamcet 2011 Engineering PaperandhracollegesÎncă nu există evaluări

- Eamcet 2013 Medical PaperDocument62 paginiEamcet 2013 Medical PaperandhracollegesÎncă nu există evaluări

- Eamcet 2010 Medical PaperDocument63 paginiEamcet 2010 Medical PaperandhracollegesÎncă nu există evaluări

- Eamcet 2009 Engineering Chemistry PaperDocument16 paginiEamcet 2009 Engineering Chemistry PaperandhracollegesÎncă nu există evaluări

- Eamcet 2007 Engineering PaperDocument13 paginiEamcet 2007 Engineering Paperandhracolleges100% (1)

- Eamcet 2008 Engineering PaperDocument62 paginiEamcet 2008 Engineering PaperandhracollegesÎncă nu există evaluări

- Eamcet 2006 Engineering PaperDocument14 paginiEamcet 2006 Engineering PaperandhracollegesÎncă nu există evaluări

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (587)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (399)

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (73)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5794)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2219)

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (344)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (265)

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (119)

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)

- Palm Oil SupplyDocument2 paginiPalm Oil SupplyAftab Hussain ChaudhryÎncă nu există evaluări

- E74h IbmDocument37 paginiE74h IbmJose BerrospiÎncă nu există evaluări

- 1997 Jeep Cherokee Country 4.0Document11 pagini1997 Jeep Cherokee Country 4.0LuissUlsrÎncă nu există evaluări

- VEHICLE MAINTENANCE TIPSDocument89 paginiVEHICLE MAINTENANCE TIPSjalda srikaranÎncă nu există evaluări

- X15 - Humo AzulDocument9 paginiX15 - Humo AzulmttoguboÎncă nu există evaluări

- TCEW: Guide to Electrical Wiring Types and Termination MethodsDocument17 paginiTCEW: Guide to Electrical Wiring Types and Termination MethodsnpfhÎncă nu există evaluări

- Zero Speed Switch Working Principle Instrumentation ToolsDocument3 paginiZero Speed Switch Working Principle Instrumentation Toolsersanjeeb_456100% (1)

- Development of the Lightbulb - How Edison Perfected the InventionDocument2 paginiDevelopment of the Lightbulb - How Edison Perfected the InventionPhượng TạÎncă nu există evaluări

- Suppliers Peugeot 308Document1 paginăSuppliers Peugeot 308Ramsy ArayaÎncă nu există evaluări

- ThermostatsDocument16 paginiThermostatsBritaneyÎncă nu există evaluări

- FXR/VFXR E-Series: 50Hz/230V Inverter/ChargersDocument2 paginiFXR/VFXR E-Series: 50Hz/230V Inverter/Chargersmr. adamÎncă nu există evaluări

- Electrical Input Components: Operación de SistemasDocument5 paginiElectrical Input Components: Operación de Sistemasgalvis1020Încă nu există evaluări

- HP Parts Reference Guide™: Laserjet 1300 Series PrinterDocument18 paginiHP Parts Reference Guide™: Laserjet 1300 Series Printeretc_lctÎncă nu există evaluări

- Connecteur EN3645Document13 paginiConnecteur EN3645FredÎncă nu există evaluări

- 8103-128 - SWE90U (SWE85-90) Parts BookDocument194 pagini8103-128 - SWE90U (SWE85-90) Parts BookatakanÎncă nu există evaluări

- BelimoDocument4 paginiBelimoAnjana2893Încă nu există evaluări

- Experiment #1 – Sparky ElectricianDocument3 paginiExperiment #1 – Sparky ElectricianSteven Ray LabugenÎncă nu există evaluări

- Părțile motorului Jawa 889Document14 paginiPărțile motorului Jawa 889GreereCristianÎncă nu există evaluări

- Belt Scale Installation GuideDocument47 paginiBelt Scale Installation GuideViong Danon100% (1)

- Design and Modelling of An Automatic 3-Point Starter of A Shunt DC MotorDocument5 paginiDesign and Modelling of An Automatic 3-Point Starter of A Shunt DC MotorInternational Journal of Innovative Science and Research TechnologyÎncă nu există evaluări

- 1 Oil ImmersedDocument2 pagini1 Oil ImmersedArif MohiuddinÎncă nu există evaluări

- Low Power Upf NotesDocument5 paginiLow Power Upf Notessaugat guhaÎncă nu există evaluări

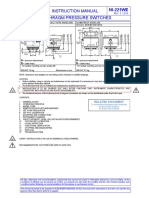

- Instruction Manual Diaphragm Pressure Switches: NI-221WEDocument9 paginiInstruction Manual Diaphragm Pressure Switches: NI-221WEPaul Ramos CarcaustoÎncă nu există evaluări

- FlyBack Transformer CalculationsDocument7 paginiFlyBack Transformer CalculationsdllabarreÎncă nu există evaluări

- Reference2 - Development of An Automated Coconut Scraping MachineDocument14 paginiReference2 - Development of An Automated Coconut Scraping MachineRenz Callejo100% (1)

- LED Solar ProjectDocument102 paginiLED Solar ProjectBrandy RomanÎncă nu există evaluări

- Mccu 216 Manual T04Document18 paginiMccu 216 Manual T04AlberthÎncă nu există evaluări

- DHAF Fan BrochureDocument4 paginiDHAF Fan Brochurepopescu danielaÎncă nu există evaluări

- GA-AX370-Gaming K5 BOM & PCB HISTORYDocument44 paginiGA-AX370-Gaming K5 BOM & PCB HISTORYAndy Díaz MorenoÎncă nu există evaluări