Documente Academic

Documente Profesional

Documente Cultură

Reasearch On Electronic Current Transformer

Încărcat de

raghavendran raghuTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Reasearch On Electronic Current Transformer

Încărcat de

raghavendran raghuDrepturi de autor:

Formate disponibile

Research on the Electronic Transformer Applied in IEC 61850-9-2 Process Bus

LUO Yan, Duan Xiongying, ZHANG Minzhi, DONG Enyuan

Research on the Electronic Transformer Applied in IEC 61850-9-2 Process

Bus

1

LUO Yan, 2Duan Xiongying, 3ZHANG Minzhi, 4DONG Enyuan

School of Electrical Engineering, Dalian University of Technology, Dalian, China,

luoyanl@yeah.net

*2

School of Electrical Engineering, Dalian University of Technology, Dalian, China,

dxy@dlut.edu.cn

3,4

School of Electrical Engineering, Dalian University of Technology, Dalian, China,

eyd@dlut.edu.cn

1

Abstract

Electronic current transformers (ECTs) and electronic voltage transformers (EVTs) play important

roles in Substation Automation Systems (SAS). In this paper, we focus on the digital communication

and the time synchronization relating to the electronic transformer. At the aspect of the digital

communication, according to the limitation on the communication flexibility in the standard IEC

61850-9-2LE, the idea of the distributed sampled value control block (SVCB) is presented, as well as

the communication protocol between the distributed systems is specified. In order to reach the highly

accurate time synchronization, the digital phase-shifter and phase-equalizer are used to compensate

the phase displacement of signal samples and ensure the maximum phase linearity and constant group

delay. The test shows that the method proposed in this paper is feasible.

Keywords: ECTs, EVTs, Substation Automation System (SAS), Communication Flexibility,

1. Introduction

With the development of the smart grid and the digital substation, the position of the electronic

transformer has become more and more prominent. It is usually consisted of three parts structurally: the

conventional primary voltage transformers (VTs) or current transformers (CTs), the signal sampling

system and the merging unit (MU). Merging units are the interface electronic devices, which supply the

secondary equipment with a time-coherent set of current and voltage samples over the communication

network [1].

IEC 61850-9-2 standard deepens the concept of the merging unit (MU), and makes it as a logical

device to be integrated into the entire system of IEC 61850 [2-3]. All primary electrical signals are

sampled and converted to digital in the signal sampling system and packed into the FT3 frame format

to be sent to MU through optical fibers. And then, multi-channel data samples will be combined into a

standard data format, i.e. sampled value (SV) messages in MU and published to corresponding bay

level protection and control (P&C) intelligent electronic devices (IEDs) using the standardized

Ethernet-based communication network.

We can see that the main function of MU is focused on the procession and transmission of timecritical SV messages. Therefore, it has salient features of strong real-time and multitasking-parallel.

However, the interoperability and the flexibility specified in IEC 61850 will result in complex

communication stacks as well as weak real-time properties of MU. In order to resolve the above

contradictions and reduce the implementation difficulties, the IEC 61850-9-2 LE [4] companion

document has been pushed out. It directly maps the abstract communication services onto the Ethernet

link layer and retains only the SendSMVMessage service to facilitate the interoperability on the cost of

limiting the flexibility.

On the other hand, Merging units propagate SVs of currents and voltages acquired from the primary

transducers periodically. These digitalized SVs should be received in synchronism by the bay level

P&C IEDs in order that the protection algorithm will function properly. Consequently, the sample

synchronization technique is becoming one of the key factors to determine the electronic transformers

performance.

Tremendous work is going on with various related issues, such as researching on the primary sensor

performance, deploying Ethernet communication networks for the process bus, evaluating the

International Journal of Advancements in Computing Technology(IJACT)

Volume4, Number13, July2012

doi: 10.4156/ijact.vol4.issue13.25

217

Research on the Electronic Transformer Applied in IEC 61850-9-2 Process Bus

LUO Yan, Duan Xiongying, ZHANG Minzhi, DONG Enyuan

performance of sampled value packet over the IEC 61850-9-2 process bus, etc.[4-10]. Based on these

work, the electronic transformer, which is the key equipment to implement the process levels

communication, should be of considerable concerned. Especially, the sampling synchronization

technique and digital communication are of more important, as the former is one of the key factors to

determine the reliabilities and the availabilities of SV messages, and the latter is related closely to the

interoperability and flexibility of the communication.

2. Digital communication

2.1 Modeling of the merging unit

The server model of MU is constructed in accordance with the concept of layering of the

information model and the idea of the pre-configuration based on IEC 61850-9-2LE, as shown in

Figure 1. E1Q1SB1 is the server representing the external visible behavior of a practical device.

E1Q1SB1Munn is LD containing the information produced and consumed by a group of domainspecific application functions, and each function is defined as a LN. I11ATCTR - I11NTCTR, which

are derived from the LN class TCTR, represent 4-channel protective ECTs. I22ATCTR - I22NTCTR

represent 4-channel metering ECTs. U11ATVTR - U11NTVTR, which are derived from the LN class

TVTR, represent 4-channel EVTs, and each EVT is used to detect the metering phase voltages. Data

attributes Amp and Vol contained in these LNs represent the sampled values of primary phase currents

or voltages respectively.

Figure 1. Server model of the merging unit

A sampled value control Block (SVCB) is used to control the exchange of values of a DATA-SET

based on the publisher/subscriber mechanism. There are different requirements for metering SV

messages and protection SV messages according to IEC 61850-9-2 and IEC 60044. Therefore, two

sampled value control blocks (SVCB) should be designed for controlling the processing and

transmission of SVs. The MSVCB MSVCB01is used to control the transmission of 8-channel metering

voltages and currents, and the MSVCB MSVCB02 is used to control the transmission of 4-channel

protection currents.

Multi-channel sampled analog values (SAV) are integrated into MU and encapsulated into two data

sets: PhsMeas1 and PhsMeas2, and each data set is bonded to the corresponding MSVCB (MSVCB01

or MSVCB02) respectively. Subsequently, the two data sets together with the relevant status

information are wrapped into two standardized data frames in accordance with IEC 61850-9-2LE to be

published to the process bus over Ethernet network.

218

Research on the Electronic Transformer Applied in IEC 61850-9-2 Process Bus

LUO Yan, Duan Xiongying, ZHANG Minzhi, DONG Enyuan

2.2 Distributed sampled values control block

Three abstract services such as SendMSVMessage, GetMSVCBValues and SetMSVCBValues are

defined in MSVCB class to support the method of exchanging time-critical and non-time-critical data.

The transmission of SV packets and the writing & reading data attributes of MSVCB are two

completely different services. The former service (SendMSVMessage) which is the time-critical

service is directly mapped to the Ethernet link layer according to the standard IEC 61850-9-2. The

latter services (GetMSVCBValues & SetMSVCBValues) are mapped to MMS services in accordance

with IEC 61850-8-1, which are very complexity. However, the applications of MMS services are

focused on the remote detection and controlling. Therefore, the real-time requirements for MMS

services are not so much critical.

Based on the analysis above, the distributed SVCB is designed in this paper. FPGA is employed to

implement the time-critical service such as the transmission of SV packets over Ethernet network.

Meanwhile, the embedded system such as ARM/Linux is introduced to implement MMS services that

are conformance to the client/server communication profile based on the OSI Reference model.

Figure 2. Distributed SVCB system

Figure 2 shows that the server model of MU is mapped to the MMS model residing in the embedded

system in accordance with IEC61850 8-1. The abstract services (for example, GetMSVCBValues and

SetMSVCBValues) are mapped to the Read and Write primitives defined in the MMS by using the

specific communication service mapping (SCSM).Through the model mapping and the service

mapping, the MMS model residing in the ARM/Linux system becomes the virtual image of MU. In

logic, MMS objects represent the server model of MU, and in practical communications, MMS objects

become the bridge connecting the MU server and remote clients.

On the other hand, some data objects such as Data, MSVCB and Datset of the server model are

mapped one-to-one to real variables located in FPGA system also. By this data object mapping, the

logical relationships of real variables between the ARM/Linux system and the FPGA system are

constructed, through which the MSVCB residing in FPGA system is able to perceive the dynamic

configuration information sent by the remote client in logical.

219

Research on the Electronic Transformer Applied in IEC 61850-9-2 Process Bus

LUO Yan, Duan Xiongying, ZHANG Minzhi, DONG Enyuan

2.3 Formulate protocols between FPGA and ARM/Linux

In order to control the transmission of SV messages, the remote client should use the MMS Write

service to set data attributes of the MSVCB class. Due to the distributed implementation of MSVCB,

the remote client can only change the data attributes located in the ARM/Linux system. Therefore, it is

necessary to establish a physical communication link between the two distributed systems based on

their logical relationships, in order that the clients settings can have influence on the transmission of

SV messages.

A FIFO channel is created in FPGA in this paper. The remote setting parameters encoded in MMS

service primitives are received and decoded in the ARM/Linux system over MMS stacks and passed to

FPGA through the FIFO channel. Considering of the systems flexibility and extensibility, the Abstract

Syntax Notation (asn.1) is employed to formulate the communication protocol between the two

systems.

Figure 3. Communication protocol defined by asn1

Figure 3 shows the communication protocol formulated by this paper (The figure only shows the

encoding rules of the s_requestes primitive). According to the read & write serices for MSVCB, two

kinds of request / response primitives such as s_requests / s_response and d_requests / d_response are

defined. The ARM/Linux system issues the write request to FPGA to set data attributes of MSVCB

located in FPGA by using the s_requestes primitive. FPGA receives the s_requestes primitive, makes

an appropriate adjustment according to the configuration parameters encoded in the primitive

s_requestes, and then the configuration results will be feedback to ARM/Linux system by using the

primitive s_respones to accomplish the configuration procedure. The process of reading MSVCB is

similar to writing.

As described in Figure 4, ARM/Linux plays a critical role to implement the distributed SVCB. It is

not only the server but also the client. Within MU, it acts as a client requesting to read or write the

MSVCB located in the FPGA. Between the process level and the bay/substation level, it services as a

MMS server to communicate with remote clients. Through ARM/Linux system, a communication

channel is created to achieve the IEC 61850-9-2 standard in a complete sense, by which the remote

clients can control the SV messages transmission at the run-time.

220

Research on the Electronic Transformer Applied in IEC 61850-9-2 Process Bus

LUO Yan, Duan Xiongying, ZHANG Minzhi, DONG Enyuan

Figure. 4 Sequence diagram of service primitives transmission

3. Time synchronization

The processing and transmission of SVs will experience delays, which will result in the phase

displacement of the original signal. The latency between the instant a certain electrical signal is present

at the primary terminals and the instant the electrical information is used at the bay level P&C IEDs

should be compensated in order to maintain the time synchronization.

In this paper the sampled signals are forwarded and maintain approximately linear-phase group

delay with digital phase-shifter and phase equalization technology. The synchronization algorithm is

implemented in FPGA [12-13].

Defining the transfer function of an analogue phase-shifter:

H ( s)

s 1

s 1

(1)

Where >0 is the adjustable parameter of the analogue phase-shifter.

Let s j we get the frequency characteristics of the system:

H ( j)

j 1

j 1

H ( j) 1

() H ( j) arctan 2

2

(2)

(3)

It can be seen from the phase-frequency characteristics that the leading phase angle of this system

varies in the range of 0180 when the value of the parameter is changed. In order to facilitate the

digital phase-shifter in FPGA, it is necessary to convert the transfer function (1) from the S-domain

into the Z-domain by employing the bilinear transformation. Let

2 1 Z 1

T 1 Z 1

(4)

Substitution (4) in (1), the transmission function of the discrete digital phase-shifter can be achieved:

221

Research on the Electronic Transformer Applied in IEC 61850-9-2 Process Bus

LUO Yan, Duan Xiongying, ZHANG Minzhi, DONG Enyuan

H d ( z) k

Where c

1 cz 1

1 dz 1

(5)

2 T

2 T

2 T

, d

, k

, T is the sampling period.

2 T

2 T

2 T

The phase-frequency characteristics of the discrete digital phase-shifter can be derived from (5):

d (w) arctan(sin w /(cos w c)) arctan(sin w /(cos w d ))

(6)

As the group delay ( d (w) (dd (w) / dw) ) is not a constant, the phase-frequency characteristics

of the digital phase-shifter are non-linear. When the signal travels through the digital phase-shifter,

harmonic components with different frequencies contained in the original signal will have variable

delays, which will result in the distortion of the output waveform. The causes accounting for the

nonlinear phase are that the original analog phase-shifter is a nonlinear phase system, as well as the

bilinear transformation is a nonlinear phase algorithm. Here, a second-order all-pass filter is employed

as a phase equalizer to correct the nonlinear phase of the digital phase-shifter, in order to obtain the

linear phase-frequency characteristics without changing the amplitude-frequency characteristics of the

system.

Defining a second-order all-pass filter:

H ap ( z)

z 1 re j z 1 re j

1 re j z 1 1 re j z 1

(7)

The Z-transfer function of the cascaded system would be:

H ( z) H d ( z) H ap ( z)

(8)

Therefore, the frequency characteristics of the cascaded system are:

jw

jw

H (e ) H d (e )

( w) ap ( w) d ( w)

(9)

As we hope that the cascaded system is a linear phase system, the group delay of the system would

be:

(w) ap (w) d (w) 0 ;

(10)

Where 0 = constant.

According to the criterion of the minimum mean square error (MSE), defining a MSE function:

N

E [ ( wi ) 0 ]2

(11)

i 1

All parameters of the second-order all-pass filter (7) can be determined by solving the minimum

value of E at a set of discrete frequency points wi ( i=1, 2,N ). Solving the partial derivative of each

parameter: E / r, E / , and then following the Fletcher-Powell optimization algorithm to be

iterative correct, will be able to obtain the required optimized all-pass filter, whose parameters can

make the value of E to be minimum.

222

Research on the Electronic Transformer Applied in IEC 61850-9-2 Process Bus

LUO Yan, Duan Xiongying, ZHANG Minzhi, DONG Enyuan

4. Test and Conclusion

4.1 Basic accuracy test

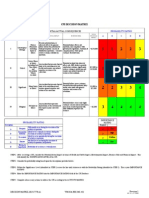

Figure 5 is the distribution maps of ratio errors and phase errors, which are obtained by employing

the XL-807 calibrator. The distribution of ratio errors is even and centralization, which is within the

limits of the 0.2s accuracy class specified in IEC 60044. The phase errors are within the range of -3 to

+3 minutes without a big jump. It reflects the good performance of the time synchronization.

Figure 5. Distribution map of ratio errors and phase errors

4.2 The equal interval dispersion of SV messages

Figure 6. Equal interval dispersion of SV messages

Merging units continuously propagate sampled values of currents and voltages acquired from the

primary sensor. The time interval between two SV messages is required to be as equal as possible in

order that the protection algorithm will function properly. Therefore, the equal interval dispersion is an

important indicator for measuring the performance of SV messages. In figure 6, we can see that the

equal interval dispersion follows a normal distribution approximately. The mean-value and variancevalue of the dispersion is 1.83s and 2.71s respectively. The 95% confidence interval of mean-value

is [1.55s, 2.11s], and the 95% confidence interval of variance-value is [2.53s, 2.93s]. The equal

interval dispersion is within the range of -6 to +8s, which is in accordance with the standard

Q/GDW441-2010.

4.3 Time synchronization performance of multi-channel sampled signals

In order to measure the time synchronization performance of multi-channel signals, we select the

two signals in the same data set and compare their angle phase. The phase errors between two channels

have been showed in Figure7.

When the inputting current is 1%ln (ln =1250A), the phase error between the two channels is 0.55

and the jitter is in the range of 0.18 to 1.02. When the inputting currents is 120%ln, the phase error is 0.01 and the jitter is in the range of -0.1 to 0.08. It reflects a good synchronization performance

between multi-channel signals.

223

Research on the Electronic Transformer Applied in IEC 61850-9-2 Process Bus

LUO Yan, Duan Xiongying, ZHANG Minzhi, DONG Enyuan

Figure 7. Phase errors between two channels

6. References

[1] Instrument Transformers-Part 8: Electrical Current Transducers. IEC 60044-8, Ed. 1, 2002.

[2] IEC Standard for Communication Network and Systems in Substations, IEC Std. 61850, 2003-04,

1st ed.

[3] IEC Standard for Communication Network and Systems in Substations Part-9-2: Specific

Communication Service Mapping (SCSM)-Sampled Values over ISO/IEC 8802-3, IEC 61850-9-2,

2004, 1st ed.

[4] Ibidem, The real-time publisher/subscriber communication model for distributed substations

systems, IEEE Trans. Power Del., vol. 22, no. 3, pp. 14111423, Jul. 2007.[J].

[5] B. Kasztenny; D. McGinn, M. Adamiak, An Optimized Architecture For IEC 61850 Process

Bus, presented at the Power System Conference, 2009.

[6] M. Faifer, R. Ottoboni, An Electronic Current Transformer Based on Rogowski Coil, presented

at the IEEE IMTC 2008 Instrumentation and Measurement Technology Conference, Victoria, BC,

Canada, May. 2008.

[7] B. Kasztenny; D. McGinn,S. Hodder, D. Ma, J. Mazereeuw, and M. Goraj, Practical IEC 618509-2 process bus architecture driven by topology of the primary equipment, Presented at the

CIGRE Session, Paris, France, Aug. 2008, paper B5-105.

[8] M. R. D. Zadeh, T. S. Sidhu, A. Klimek, Implementation and Testing of Directional Comparison

Bus Protection Based on IEC61850 Process Bus, IEEE Trans. Power Del. vol. 26, no. 3, pp.

1530-1537, Jul. 2011.

[9] LIU Chen xu, LIU Yun, ZHANG Zhenjiang, Analytical research on the efficiency of smart grid

with delay performance of wireless sensor network based on queuing theory,, Journal of

convergence information technology, vol. 7, no. 1, pp. 448-456, Jan. 2012.

[10] WEN Junqin, Design of a multi-source information collection and retrieval system, Journal of

convergence information technology, vol. 7, no. 3, pp. 292-298, Feb. 2012.

[11] ZHANG Yanmei, JIANG Shujuan,ZHAO Xuefeng, Analysis of object-oriented programs with

exception-handling constructs, International Journal of Advancements in Computing Technology,

vol. 4, no.1, pp. 504-515, Jan. 2012.

[12] ZHAO Jiecheng, WU Hongwei, GU ShihongDigital filter design for CPT atomic clocks and

FPGA realization, Journal of convergence information technology, vol. 7, no. 4, pp. 97-105, Mar.

2012.

[13] XUE Hua, LI Weibing, Implementation of chaos synchronization on FPGA, Advances in

Information Sciences and Service Sciences, vol. 4, no. 6, pp. 42-51, Apr. 2012.

[14] ZHANG Yikui, Zhu Liwei, Lai Yisheng, Research and application on a wireless GPS data

collection and display system, International Journal of Digital Content Technology and its

Applications, vol. 6, no. 1, pp. 454-461, Jan. 2012.

[15] UCA international users group, Implementation Guidelines for Digital Interface to Instrument

Transformers Using IEC 61850-9-2. Tech. Rep. IEC 61850-9-2LE.

224

S-ar putea să vă placă și

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5794)

- Rudolf Simon CompatibiliteitsmodusDocument16 paginiRudolf Simon Compatibiliteitsmodusthangcbe1818Încă nu există evaluări

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (399)

- NEMA MG Guide For Consultants PDFDocument14 paginiNEMA MG Guide For Consultants PDFraghavendran raghuÎncă nu există evaluări

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- b3 103 2012 PDFDocument10 paginib3 103 2012 PDFraghavendran raghuÎncă nu există evaluări

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (894)

- Final ZLD (Draft) 1Document25 paginiFinal ZLD (Draft) 1raghavendran raghuÎncă nu există evaluări

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- StdsC29-1 - Test Methods For Electrical Power InsulatorsDocument26 paginiStdsC29-1 - Test Methods For Electrical Power Insulatorsraghavendran raghuÎncă nu există evaluări

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- Second International Symposium on Standards for Ultra High Voltage TransmissionDocument13 paginiSecond International Symposium on Standards for Ultra High Voltage Transmissionraghavendran raghuÎncă nu există evaluări

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- ANSI NEMA C29 12-2013 Suspension InsulatorsDocument19 paginiANSI NEMA C29 12-2013 Suspension Insulatorsraghavendran raghu100% (2)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- NEMA VE1 2009 Metal Cable Tray SystemsDocument25 paginiNEMA VE1 2009 Metal Cable Tray Systemsraghavendran raghuÎncă nu există evaluări

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (587)

- RV 2 2011 Nonmetallicsheathed CableDocument28 paginiRV 2 2011 Nonmetallicsheathed Cableraghavendran raghuÎncă nu există evaluări

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (265)

- NEMA TR 1-2013 TransformersDocument21 paginiNEMA TR 1-2013 Transformersraghavendran raghu100% (2)

- DC Load CalculationsDocument20 paginiDC Load Calculationsraghavendran raghuÎncă nu există evaluări

- 115 KV GIS Design Criteria Considering Service ContinuityDocument2 pagini115 KV GIS Design Criteria Considering Service Continuityraghavendran raghuÎncă nu există evaluări

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- ETS-50!06!05-C1 High-Voltage Components - Circuit Breaker 400 KVDocument10 paginiETS-50!06!05-C1 High-Voltage Components - Circuit Breaker 400 KVraghavendran raghuÎncă nu există evaluări

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (73)

- IECEE-CTL EQL 62067 - Ed2 - 201404Document10 paginiIECEE-CTL EQL 62067 - Ed2 - 201404raghavendran raghuÎncă nu există evaluări

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (344)

- ETS-50-00 Outdoor AIS AC Substation Common Conditions and Technical RequirementsDocument8 paginiETS-50-00 Outdoor AIS AC Substation Common Conditions and Technical Requirementsraghavendran raghuÎncă nu există evaluări

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- ETS-50!06!08-C1 High-Voltage Components - Current Transformer 400 KV 2000-1000 ADocument7 paginiETS-50!06!08-C1 High-Voltage Components - Current Transformer 400 KV 2000-1000 Araghavendran raghuÎncă nu există evaluări

- ETS-50-06-12-E1 High-Voltage Components - Surge Arrester, Metal Oxide 170 KV PDFDocument5 paginiETS-50-06-12-E1 High-Voltage Components - Surge Arrester, Metal Oxide 170 KV PDFraghavendran raghuÎncă nu există evaluări

- VCB DatasheetDocument3 paginiVCB Datasheetraghavendran raghuÎncă nu există evaluări

- 13-94559-5 ETS-53!01!04 Standard - Underboringer, RørafslutningDocument18 pagini13-94559-5 ETS-53!01!04 Standard - Underboringer, Rørafslutningraghavendran raghuÎncă nu există evaluări

- 132-400 KV AC Substation: Control Unit Relay Protection Data Exchange With SIMEAS SAFIR ETS-52-01-04 Rev. 0Document11 pagini132-400 KV AC Substation: Control Unit Relay Protection Data Exchange With SIMEAS SAFIR ETS-52-01-04 Rev. 0raghavendran raghuÎncă nu există evaluări

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- ETS-50!06!05-E2 High-Voltage Components - Circuit Breaker 145 KVDocument9 paginiETS-50!06!05-E2 High-Voltage Components - Circuit Breaker 145 KVraghavendran raghuÎncă nu există evaluări

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2219)

- 132-400 KV AC Substation: Control Unit Relay Protection Data Exchange With SIMEAS SAFIR ETS-52-01-04 Rev. 0Document11 pagini132-400 KV AC Substation: Control Unit Relay Protection Data Exchange With SIMEAS SAFIR ETS-52-01-04 Rev. 0raghavendran raghuÎncă nu există evaluări

- ETS-50-06-11-E2 High-Voltage Components - Inductive Voltage Transformer 145 KV PDFDocument9 paginiETS-50-06-11-E2 High-Voltage Components - Inductive Voltage Transformer 145 KV PDFraghavendran raghuÎncă nu există evaluări

- 13-90592-127 ETS-50-08-01 Earthing Systems PDFDocument8 pagini13-90592-127 ETS-50-08-01 Earthing Systems PDFraghavendran raghuÎncă nu există evaluări

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- ETS-50!06!08-E2 High-Voltage Components - Current Transformer 145 KV 1500-750 ADocument9 paginiETS-50!06!08-E2 High-Voltage Components - Current Transformer 145 KV 1500-750 Araghavendran raghuÎncă nu există evaluări

- ETS-50!06!10-E2 High-Voltage Components - Capacitor Voltage Transformer 145 KVDocument8 paginiETS-50!06!10-E2 High-Voltage Components - Capacitor Voltage Transformer 145 KVraghavendran raghuÎncă nu există evaluări

- 13-90242-7 EDS - 50 - 01 Engineering Reports Drawings and Lists - Doc 1752805 - 27 - 2 PDFDocument20 pagini13-90242-7 EDS - 50 - 01 Engineering Reports Drawings and Lists - Doc 1752805 - 27 - 2 PDFraghavendran raghuÎncă nu există evaluări

- ETS-50!06!06-E1 High-Voltage Components - Disconnector-Earthing Switch 170 KVDocument7 paginiETS-50!06!06-E1 High-Voltage Components - Disconnector-Earthing Switch 170 KVraghavendran raghuÎncă nu există evaluări

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (119)

- ETS-50-06-11-E2 High-Voltage Components - Inductive Voltage Transformer 145 KV PDFDocument9 paginiETS-50-06-11-E2 High-Voltage Components - Inductive Voltage Transformer 145 KV PDFraghavendran raghuÎncă nu există evaluări

- ETS-50!06!10-E2 High-Voltage Components - Capacitor Voltage Transformer 145 KVDocument8 paginiETS-50!06!10-E2 High-Voltage Components - Capacitor Voltage Transformer 145 KVraghavendran raghuÎncă nu există evaluări

- Corporate Strategic Planning AssignmentDocument10 paginiCorporate Strategic Planning AssignmentSumit DuttaÎncă nu există evaluări

- Space Gass 12 5 Help Manual PDFDocument841 paginiSpace Gass 12 5 Help Manual PDFNita NabanitaÎncă nu există evaluări

- Getting BetterDocument3 paginiGetting BetterIngrid MedinaÎncă nu există evaluări

- Royal DSMDocument16 paginiRoyal DSMSree100% (2)

- DEMO 2 Critical Reading As ReasoningDocument3 paginiDEMO 2 Critical Reading As ReasoningConnieRoseRamosÎncă nu există evaluări

- ASTM C 136 Sieve Analysis of Fine and Coarse Aggregates (D)Document5 paginiASTM C 136 Sieve Analysis of Fine and Coarse Aggregates (D)Yasir DharejoÎncă nu există evaluări

- DCinv V6 Rev2 CleanDocument38 paginiDCinv V6 Rev2 Cleanyasirarafat91Încă nu există evaluări

- Worksheet 9-2 - Math 7Document2 paginiWorksheet 9-2 - Math 7bfbrfvlfrerÎncă nu există evaluări

- Solar PV Array Modelling PDFDocument13 paginiSolar PV Array Modelling PDFsunilkumarece100% (1)

- Carnot CycleDocument3 paginiCarnot CyclealexontingÎncă nu există evaluări

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)

- Significance of Vaiseshika's PragabhavaDocument5 paginiSignificance of Vaiseshika's Pragabhavavskanchi0% (1)

- HistoryDocument45 paginiHistoryRay Joshua Angcan BalingkitÎncă nu există evaluări

- حقيبة تعليمية لمادة التحليلات الهندسية والعدديةDocument28 paginiحقيبة تعليمية لمادة التحليلات الهندسية والعدديةAnjam RasulÎncă nu există evaluări

- S32 Design Studio 3.1: NXP SemiconductorsDocument9 paginiS32 Design Studio 3.1: NXP SemiconductorsThành Chu BáÎncă nu există evaluări

- New Microsoft Word DocumentDocument5 paginiNew Microsoft Word DocumentxandercageÎncă nu există evaluări

- 2016 John Timm Final Narrative WeeblyDocument8 pagini2016 John Timm Final Narrative Weeblyapi-312582463Încă nu există evaluări

- Perceptron Example (Practice Que)Document26 paginiPerceptron Example (Practice Que)uijnÎncă nu există evaluări

- Circle Midpoint Algorithm - Modified As Cartesian CoordinatesDocument10 paginiCircle Midpoint Algorithm - Modified As Cartesian Coordinateskamar100% (1)

- The God Complex How It Makes The Most Effective LeadersDocument4 paginiThe God Complex How It Makes The Most Effective Leadersapi-409867539Încă nu există evaluări

- McKinsey & Co - Nonprofit Board Self-Assessment Tool Short FormDocument6 paginiMcKinsey & Co - Nonprofit Board Self-Assessment Tool Short Formmoctapka088100% (1)

- Structural Testing Facilities at University of AlbertaDocument10 paginiStructural Testing Facilities at University of AlbertaCarlos AcnÎncă nu există evaluări

- Omega Fluid PDFDocument2 paginiOmega Fluid PDFapatzinfedÎncă nu există evaluări

- Pedestrian Safety in Road TrafficDocument9 paginiPedestrian Safety in Road TrafficMaxamed YusufÎncă nu există evaluări

- Blank Character StatsDocument19 paginiBlank Character Stats0114paolÎncă nu există evaluări

- Decision MatrixDocument12 paginiDecision Matrixrdos14Încă nu există evaluări

- Watershed Management A Case Study of Madgyal Village IJERTV2IS70558Document5 paginiWatershed Management A Case Study of Madgyal Village IJERTV2IS70558SharadÎncă nu există evaluări

- MGMT 410 Book ReportDocument1 paginăMGMT 410 Book ReportLester F BoernerÎncă nu există evaluări

- Balkan TribesDocument3 paginiBalkan TribesCANELO_PIANOÎncă nu există evaluări

- Agricultural Typology Concept and MethodDocument13 paginiAgricultural Typology Concept and MethodAre GalvánÎncă nu există evaluări

- Geo Lab Report Point LoadDocument9 paginiGeo Lab Report Point Loaddrbrainsol50% (2)