Documente Academic

Documente Profesional

Documente Cultură

Digitales Lab 4

Încărcat de

Juan PujaicoDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Digitales Lab 4

Încărcat de

Juan PujaicoDrepturi de autor:

Formate disponibile

Universidad Nacional del Callao

Facultad de Ingeniera Elctrica y Electrnica

Escuela Profesional de Ingeniera Elctrica

LAB. N 4 COMPUERTAS BASICAS, UNIVERSALES Y ESPECIALES DE LA

FAMILIA TTL

Objetivo:

- Verificar experimentalmente la operacin de las compuertas digitales bsicas:

AND, OR y NOT.

- Verificar experimentalmente la operacin de las compuertas digitales

universales: NAND y NOR.

- Verificar experimentalmente la operacin de las compuertas digitales

especiales: EX-OR y EX-NOR

Marco terico:

TTL es la sigla en ingls de transistor-transistor lgica, es decir, "lgica transistor a

transistor, esta fue la primera familia de xito comercial, se utiliz entre 1965 y 1985.

Los circuitos TTL utilizan transistores bipolares y algunas resistencias de polarizacin.

La tensin nominal de alimentacin de los circuitos TTL son 5 V DC. Estn fabricadas

a partir de BJT npn y resistencias, son las ms antiguas en uso y aun a si siguen

siendo populares en sistemas digitales que utilizan circuitos integrados a escala

pequea, media y gran escala de integracin, a pesar de ser sustituidos por las

familias lgicas CMOS y BICMOS en la mayor parte de las aplicaciones, TTL sigue

construyendo un estndar de referencia de la electrnica digital.

Caractersticas. La familia lgica transistor-transistor ha sido una de las familias de CI

ms utilizadas. Los CI de la serie 74 estndar ofrecen una combinacin de velocidad y

disipacin de potencia adecuada a muchas aplicaciones. Los CI de esta serie incluyen

una amplia variedad de compuertas, flip-flops y multivibradores monoestables as

como registros de corrimiento, contadores, decodificadores, memorias y circuitos

aritmticos. La familia 74 cuenta con varias series de dispositivos lgicos TTL (74,

74LS, 74S, etc.). Estas series utilizan una fuente de alimentacin (Vcc) con voltaje

nominal de 5V

Universidad Nacional del Callao

Facultad de Ingeniera Elctrica y Electrnica

Escuela Profesional de Ingeniera Elctrica

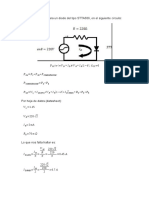

La familia TTL estndar es una familia saturan-te, porque la mayor parte de los

transistores trabajan en corte y saturacin, En la figura 1 se muestra una puerta

inversora TTL estndar a +5V, dividida en tres partes: - Etapa de entrada: El transistor

Q1 tiene por objeto producir la conmutacin rpida de Q2. - Etapa Excitadora: La

etapa extendida asocia al transistor Q2, tiene por objeto generar las dos seales

complementarias necesarias para excitar el circuito de salida. - Etapa de salida TTL:

La etapa de salida contiene los transistores Q3 y Q4 en conexin tipo ttem (ttem

pole). Esta etapa de salida requiere para ser excitada dos corrientes IB3 e IB4

producidas por la etapa excitadora mencionada anteriormente, las cuales tienen las

caractersticas de estar una activa y la otra en inversa. La R4 tiene como funcin

limitar la corriente de salida en caso de cortocircuito en la salida y en las transiciones.

Cuando se aplica una tensin de entrada de nivel bajo Vi=ViL=0 V, Q1 entra en

saturacin (ON), Q2 corta (OFF) porque no recibe corriente de base, y Q3 tambin

corta (OFF) porque tampoco recibe corriente de base. La salida se pone a nivel alto

VOH=3,8V a travs de la conduccin de Q4 (ON) en activa (o en saturacin cuando la

corriente de salida IOH es alta). Ntese que la salida no alcanza Vcc=5V debido a las

cadas en la unin BE de Q4 y en le diodo D. Cuando se aplica una tensin de entrada

de nivel alto Vi=VIH=5V, Q1 entra en activa en inversa (INV), Q2 satura (ON) con la

corriente saliente del colector de Q1, Q3 satura (ON) con la corriente que recibe del

emisor de Q2 y Q4 corta (OFF) cuando Q2 y Q3 estn saturados debido a la cada en

D. La salida se pone a nivel bajo VOL=0,2V.

Materiales

- 01 Protoboard.

- 01 fuente de tensin VDC 5V.

- 05 diodos Leds.

- CI: 7400 74LS00, 7402 74LS02, 7404 74LS04, 7408 74LS08, 7432

74LS32, 7486 74LS86.

- 01 multmetro digital.

- Cables de conexin de telefona.

Procedimiento:

1. COMPUERTA LOGICA AND

Tabla de verdad:

2

Universidad Nacional del Callao

Facultad de Ingeniera Elctrica y Electrnica

Escuela Profesional de Ingeniera Elctrica

A

0v

0v

+5v

+5v

B

0v

+5v

0v

+5v

S=A.B

0v

0v

0v

+5v

B

0v

+5v

0v

+5v

S=A+B

0v

+5v

+5v

+5v

2. COMPUERTA LOGICA OR

Tabla de verdad:

A

0v

0v

+5v

+5v

3. COMPUERTA LOGICA NOT (INVERSOR)

Tabla de verdad:

Universidad Nacional del Callao

Facultad de Ingeniera Elctrica y Electrnica

Escuela Profesional de Ingeniera Elctrica

S=

0v

+5v

+5v

0v

4. COMPUERTA LOGICA NAND

Tabla de verdad:

0v

0v

+5v

+5v

0v

+5v

0v

+5v

S= A . B

+5v

+5v

+5v

0v

5. COMPUERTA LOGICA NOR

Tabla de verdad:

S= A + B

4

Universidad Nacional del Callao

Facultad de Ingeniera Elctrica y Electrnica

Escuela Profesional de Ingeniera Elctrica

0v

0v

+5v

+5v

0v

+5v

0v

+5v

+5v

0v

0v

0v

6. COMPUERTA LOGICA OR-EXCLUSIVA (XOR)

Tabla de verdad:

0v

0v

+5v

+5v

0v

+5v

0v

+5v

S= A B

0v

+5v

+5v

0v

Cuestionario:

1. Dibuje el esquema del C.I. TTL 74LS260, monte el circuito y realice las

combinaciones en las entradas para completar su tabla de verdad o

funcionamiento.

Va a funcionar como una compuerta NOR pero con cinco entradas, solo va

a funcionar cuando todas estn abiertas (0v).

5

Universidad Nacional del Callao

Facultad de Ingeniera Elctrica y Electrnica

Escuela Profesional de Ingeniera Elctrica

2. Obtener e implementar una compuerta lgica NOT usando solo compuertas

lgicas NAND.

3. Obtener e implementar una compuerta lgica OR usando solo compuertas

lgicas NAND.

4. Obtener e implementar una compuerta lgica XOR usando solo compuertas

lgicas NAND

Conclusiones y recomendaciones

Universidad Nacional del Callao

Facultad de Ingeniera Elctrica y Electrnica

Escuela Profesional de Ingeniera Elctrica

Aprendimos el funcionamiento de las compuertas que utilizamos en esta

oportunidad.

Pudimos obtener tablas de verdad de cada compuerta con la ayudad de

la experimentacin realizada.

Tambin llegamos a poder usar distintas compuertas q pueden

reemplazar a otras.

Es recomendable tener en cuenta el tipo de compuerta q se est usando

y su diagrama para no cometer errores.

S-ar putea să vă placă și

- Trabajo1 Pujaico Soto Juan 1223120206Document1 paginăTrabajo1 Pujaico Soto Juan 1223120206Juan PujaicoÎncă nu există evaluări

- Ventiladores, Clasificacion, Aplicacion y Calculo.Document31 paginiVentiladores, Clasificacion, Aplicacion y Calculo.Mane Gonzalez Guzman73% (11)

- NTCSEDocument64 paginiNTCSEJuan PujaicoÎncă nu există evaluări

- Cursos Del Ultimo CicloDocument1 paginăCursos Del Ultimo CicloJuan PujaicoÎncă nu există evaluări

- Calcular La Potencia de Un DiodoDocument4 paginiCalcular La Potencia de Un DiodoJuan PujaicoÎncă nu există evaluări

- Lista de Teoria de Campos ActulizadoDocument6 paginiLista de Teoria de Campos ActulizadoJuan PujaicoÎncă nu există evaluări

- Leyenda de Seguridad FisicaDocument1 paginăLeyenda de Seguridad FisicaJuan PujaicoÎncă nu există evaluări

- Trabajo de Gestion1Document4 paginiTrabajo de Gestion1Juan PujaicoÎncă nu există evaluări

- Libro 1Document3 paginiLibro 1Juan PujaicoÎncă nu există evaluări

- SemaforoDocument17 paginiSemaforoCesar Augusto Tanta HuamanÎncă nu există evaluări

- A La Mierda Papú La Única ManeraDocument1 paginăA La Mierda Papú La Única ManeraJuan PujaicoÎncă nu există evaluări

- Trabajo VentiladoresDocument11 paginiTrabajo VentiladoresJuan PujaicoÎncă nu există evaluări

- Trabajo4 2013BDocument1 paginăTrabajo4 2013BJuan PujaicoÎncă nu există evaluări

- Diagrama en Proteus Si FuncionaDocument1 paginăDiagrama en Proteus Si FuncionaJuan PujaicoÎncă nu există evaluări

- Soluconario para FluiodsDocument5 paginiSoluconario para FluiodsJuan PujaicoÎncă nu există evaluări

- Turbina PeltonDocument21 paginiTurbina PeltonJuan PujaicoÎncă nu există evaluări

- Elminacion Gaussiana Con Pivoteo TotalDocument5 paginiElminacion Gaussiana Con Pivoteo TotalJuan PujaicoÎncă nu există evaluări

- Guia de Laboratorio 2014 - Circuitos DigitalesDocument78 paginiGuia de Laboratorio 2014 - Circuitos DigitalesEdgar Vidal Espinoza OrtegaÎncă nu există evaluări

- Informe 1Document8 paginiInforme 1Juan PujaicoÎncă nu există evaluări

- Evaluación TeóricaDocument5 paginiEvaluación TeóricaJuan PujaicoÎncă nu există evaluări

- Informe Nº6 Turbinas PeltonDocument11 paginiInforme Nº6 Turbinas PeltonRenzo Arone SolarÎncă nu există evaluări

- 99.000 Apu Jul-20 Base de Datos PDFDocument403 pagini99.000 Apu Jul-20 Base de Datos PDFjuanito25politecnicoÎncă nu există evaluări

- Unidad Dental QL2028, Dental Unit, Fengdan, CATALOGO PDFDocument7 paginiUnidad Dental QL2028, Dental Unit, Fengdan, CATALOGO PDFAnibal PeñaÎncă nu există evaluări

- Manejo de MontacargasDocument38 paginiManejo de MontacargasEnrique Rodriguez100% (3)

- Curso Android Grupo de Trabajo CEIP Raimundo de BlasDocument29 paginiCurso Android Grupo de Trabajo CEIP Raimundo de Blasluis aguirreÎncă nu există evaluări

- Inventario 1Document2 paginiInventario 1Alejandro PantojaÎncă nu există evaluări

- Levantamiento topográfico de galería subterránea con brújula y eclímetroDocument15 paginiLevantamiento topográfico de galería subterránea con brújula y eclímetroMartin HerreraÎncă nu există evaluări

- Banco Cond 380VDocument9 paginiBanco Cond 380VJose L.Încă nu există evaluări

- Problemas 2da LeyDocument19 paginiProblemas 2da LeyJuan Carlos Chique Perez0% (1)

- EMBUTIDODocument7 paginiEMBUTIDOManuel Vazquez MÎncă nu există evaluări

- Diseño de fuente regulada variable de 30V según número DNIDocument4 paginiDiseño de fuente regulada variable de 30V según número DNISamuel D Los RiosÎncă nu există evaluări

- Normas de seguridad en el laboratorioDocument4 paginiNormas de seguridad en el laboratorioEilithÎncă nu există evaluări

- Rethane HS 700 Certificado de CalidadDocument1 paginăRethane HS 700 Certificado de CalidadFreddy Taipe CruÎncă nu există evaluări

- Angela Galindo - Taller ReactoresDocument11 paginiAngela Galindo - Taller ReactoresAngela GalindoÎncă nu există evaluări

- Interconexion Guatemala Mexico 400kVDocument34 paginiInterconexion Guatemala Mexico 400kVcastillejosÎncă nu există evaluări

- GUIA 3er Dep - Quimica III 2017Document10 paginiGUIA 3er Dep - Quimica III 2017Emiliano Martin Torres PachecoÎncă nu există evaluări

- Acrylics Wifi AnálisisDocument14 paginiAcrylics Wifi AnálisisVicenteÎncă nu există evaluări

- Presentacion DomoticaDocument38 paginiPresentacion DomoticaCristhian Arnaud100% (1)

- Elasticidad: Conceptos y Leyes FundamentalesDocument26 paginiElasticidad: Conceptos y Leyes FundamentalesBryan JohnsonÎncă nu există evaluări

- Patrimonio Vial de ColombiaDocument27 paginiPatrimonio Vial de Colombiapepe616Încă nu există evaluări

- Generalidades PLCDocument24 paginiGeneralidades PLCRodolfo A SandovalÎncă nu există evaluări

- Triptico 3 Jose TigaciDocument2 paginiTriptico 3 Jose TigaciJose TigaciÎncă nu există evaluări

- Puentes Acueductos - Miguel 011Document11 paginiPuentes Acueductos - Miguel 011Elvis ChávezÎncă nu există evaluări

- Lista de Chequeo para Vehiculos de CargaDocument2 paginiLista de Chequeo para Vehiculos de CargaMaryorieÎncă nu există evaluări

- Fenómenos Eléctricos PDFDocument3 paginiFenómenos Eléctricos PDFjol1386100% (2)

- Guia Tecnica... Metodos Cuantitativos para El Análisis de RiesgosDocument119 paginiGuia Tecnica... Metodos Cuantitativos para El Análisis de RiesgosgustavoÎncă nu există evaluări

- Contaminacion Del SueloDocument20 paginiContaminacion Del SueloAngie MatallanaÎncă nu există evaluări

- Doc. Congreso Geografia PDFDocument173 paginiDoc. Congreso Geografia PDFWilly MerloÎncă nu există evaluări

- Andrea Palladio, arquitecto clave del RenacimientoDocument5 paginiAndrea Palladio, arquitecto clave del RenacimientoDarianna Jimenez100% (1)

- Intercambiador de Calor de Una Caldera AcuotubularDocument17 paginiIntercambiador de Calor de Una Caldera AcuotubularAuvemar RodriguezÎncă nu există evaluări