Documente Academic

Documente Profesional

Documente Cultură

Project 1

Încărcat de

Vignesh PrasadDescriere originală:

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Project 1

Încărcat de

Vignesh PrasadDrepturi de autor:

Formate disponibile

Project 1

CS 2200 - Systems and Networks

Spring 2015

Requirements

Download VirtualBox VM Image on T-Square and follow the instructions to set it up.

Alternatively, use 32-bit Ubuntu or Debian. Click here to download.

Download build essentials for linux as needed. If you are using Mint/Ubuntu/Debian type in sudo

apt-get install build-essential.

Download the proper version of Logisim. Be sure to use the most updated version. DO NOT USE

BRANDONSIM FROM CS 2110! Click here to go to the download page. The VM image we

provide you has Logisim ready to go.

Logisim is not perfect and does have small bugs. In certain scenarios, files have been corrupted and

students have had to re-do the entire project. Please back up your work using some form of version

control, such as a local git repository.

Project Overview and Description

Project 1 is designed to give you a good feel for exactly how a processor works. In Phase I, you will design

a datapath in Logisim to implement a supplied instruction set architecture. You will use the datapath as

a tool to determine the control signals needed to execute each instruction. In Phases II and III you are

required to build a simple finite state machine (AKA control-unit) to control your computer and actually

run programs on it.

Note: You will need to have a working knowledge of Logisim. Make sure that you know how to make basic

circuits as well as subcircuits before proceeding. Always remember to see the TAs if you need help.

Project 1

CS 2200 - Systems and Networks

Spring 2015

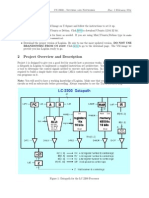

Figure 1: Datapath for the LC 2200 Processor

Phase 1 - Implement the Datapath

In this phase of the project, you must learn the Instruction Set Architecture (ISA) for the processor we will

be implementing. Afterwards, we will implement a complete LC 2200 16 bit datapath in Logisim using what

you have just learned.

You must do the following:

1. Learn and understand the LC 2200 16 ISA. Simply read and understand Appendix B: LC 2200 Instruction Set Architecture. DO NOT MOVE ON UNTIL YOU HAVE FULLY READ AND

UNDERSTOOD THE ISA AS IT WILL BE IMPOSSIBLE TO IMPLEMENT THE DATAPATH IF YOU DO NOT!

2. Using Logisim, implement the LC 2200 datapath. The basic operation of the datapath will be discussed

in the class and is delineated in the book. As you build the datapath, you should consider adding

functionality that will allow you to operate the whole datapath by hand. This will make testing

individual operations quite simple. We suggest your datapath include devices that will allow you to

put arbitrary values on the bus and to view the current value of the bus. Feel free to add any additional

hardware that will help you understand what is going on.

Please use figure 1 while constructing your datapath in Logisim.

Project 1

CS 2200 - Systems and Networks

Spring 2015

Phase 2 - Implement the Microcontrol Unit

In this phase of the project, you will use Logisim to implement the microcontrol unit for the LC 2200 processor. This component is referred to as the Control Logic in the images and schematics. The microcontroller

will contain all of the signal lines to the various parts of the datapath.

You must do the following:

1. Read and understand the microcontroller logic:

Please refer to Appendix A: Microcontrol Unit for details.

Note: You will be required to write the microcode for the microcontrol unit that you implement

in Phase 3 so please read the README file in the microcontrol unit folder for more details.

2. Implement the Microcontrol Unit using Logisim. The above link contains all of the necessary information. Take note that the input and output signals on the schematics directly match the signals marked

in the LC 2200 datapath schematic (see figure 1).

Phase 3 - Microcode and Testing

In this final stage of the project, you will write the microcode control program that will be loaded into the

microcontrol unit you implemented in Phase 2. Then, you will hook up the control unit you built in Phase 2

of the project to the datapath you implemented in Phase 1. Finally, you will test your completed computer

using a simple test program and ensure that it properly executes.

You must do the following:

1. Write the microcode control program for the microcontrol unit from Phase 2. Please see the README

file located in the microcontrol folder for more information and instructions on how to implement the

microcode.

2. After the microcode has been written, use the provided tools to convert it into hex. This should then

be loaded into your microcontrol units ROM. The tools to convert the microcode into hex can be

found in the microcontroller folder.

3. Connect the completed control unit to the datapath you implemented in Phase 1. Using the figure 1

and the microcontrol unit schematic, connect the control signals to their appropriate spots.

4. Finally, it is time to test your completed computer. Use the provided assembler (found in the assembler folder) to convert a test program from assembly to hex (see the README for help). We

recommend using test programs that contain a single instruction since you are bound to have a few

bugs at this stage of the project. Finally, try running your factorial program you wrote for Homework

1 as an ultimate test.

Deliverables

Please submit all of the following files in a .tar archive. You must turn in:

Logisim Datapath File (LC-2200-16.circ)

Microcontrol Unit Logisim File (you can implement this in the same file as the datapath if you wish)

Microcode (<filename>.xml, NOT THE HEX FILES!)

Dont forget to sign up for a demo slot! We will announce when

these are available. Failure to demo results in a 0.

Project 1

CS 2200 - Systems and Networks

Spring 2015

We do not accept late submissions. If your assignment is not submitted on T-Square by the deadline, you will receive a 0.

Precaution: You should always re-download your assignment from

T-Square after submitting to ensure that all necessary files were

properly uploaded. If what we download does not work, you will

get a 0 regardless of what is on your machine.

Project 1

CS 2200 - Systems and Networks

Spring 2015

Appendix A: Microcontrol Unit

You will make a microcontrol unit which will drive all of the control signals to various items on the datapath.

This Finite State Machine (FSM) can be constructed in a variety of ways. You could implement it with

combinational logic and Flip Flops, or you could hardwire signals using a single ROM. The signle ROM

solution will waste a tremendous amount of space since most of the microstates do not depend on the opcode

or the Z register to determine which signals to assert. For example, since Z register is an input for the

address, every microstate would have to have an address for Z = 0 as well as Z = 1, even though this only

matters for one particular microstate.

To solve this problem, we will use a three ROM microcontroller. In this arrangement, we will have three

ROMs:

the main ROM, which outputs the control signals,

the sequencer ROM, which helps to determine which microsotate to go at the end of the FETCH state,

and the OnZ ROM, which helps determine whether or not to branch during the BEQ instruction.

Examine the following:

Figure 2: Three ROM Microcontrol Unit

As you can see, there are three different locations that the next state can come from - part of the output

from the previous state (main ROM), the sequencer ROM, and the OnZ ROM. The mux controls which of

Project 1

Spring 2015

CS 2200 - Systems and Networks

these sources gets through to the state register. If the previous states next state field determines where

to go, neither the OPTest nor chkZ signals will be asserted. If the Op Code from the IR determines the

next state (such as at the end of the Fetch state), the OpTest signal will be asserted. If the zero-detection

circuitry determines the next state (such as in the BEQ instruction), the TestZ signal will be asserted. Note

that these two signals should never be asserted at the same time since nothing is input into the 11 pin on

the MUX.

The OpCheck ROM should have one address per instruction, and the OnZ ROM should have one address

for taking the branch and one for not taking the branch.

Note: Logisim has a minimum of two address bits for a ROM (i.e. four addresses), even though only one

address bit (two addresses) is needed for the OnZ ROM. Just ignore the other two addresses. You should

design it so that the high address bit for this ROM is permanently set to zero.

Before getting down to specifics you need to determine the control scheme for the datapath. To do this

examine each instruction, one by one, and construct a finite state bubble diagram showing exactly what

control signals will be set in each state. Also determine what are the conditions necessary to pass from one

state to the next. You can experiment by manually controlling your control signals on the bus youve created

in part 1 to make sure that your logic is sound.

Once the finite state bubble diagram is produced, the next step is to encode the contents of the Control Unit

ROM with a tool we are providing. Then you must design and build (in Logisim) the Control Unit circuit

which will contain the three ROMs, a MUX, and a state register. Your design will be better if it allows you

to single step and insure that it is working properly. Finally, you will load the Control Units ROMs with

the output of the tool.

Note that the input address to the ROM uses bit 0 for the lowest bit of the current state and 5 for the

highest bit for the current state.

Bit

0

1

2

3

4

Purpose

NextState[0]

NextState[1]

NextState[2]

NextState[3]

NextState[4]

Bit

5

6

7

8

9

Table 1: ROM Output Signals

Purpose

Bit Purpose Bit

NextState[5]

10

DrOFF

15

DrREG

11

LdPC

16

DrMEM

12

LdIR

17

DrALU

13 LdMAR

18

DrPC

14

LdA

19

Table 2: Register Selection Map

RegSelHi RegSelLo Register

0

0

RX

0

1

RY

1

0

RZ

1

1

Unused

Purpose

LdB

LdZ

WrREG

WrMEM

RegSelLo

Bit

20

21

22

23

24

Purpose

RegSelHi

ALULo

ALUHi

OPTest

chkZ

Project 1

CS 2200 - Systems and Networks

Table 3: ALU Function Map

ALUHi ALUlLo Function

0

0

ADD

0

1

NAND

1

0

A-B

1

1

A+1

Spring 2015

Project 1

Spring 2015

CS 2200 - Systems and Networks

Appendix B: LC 2200 Instruction Set Architecture

The LC-2200-16 (Little Computer 2200-16 bits) is very simple, but it is general enough to solve complex

problems. (Note: This is a 16-bit version of the ISA specification you will find in the Ramachandran & Leahy

textbook for CS 2200.) This section describes the instruction set and instruction format of the LC-2200. The

LC-2200-16 is a 16-register, 16-bit computer. All addresses are word-addresses. Although the 16 registers

are for general purpose use, we will assign then special duties for convention (and for all that is good on this

Earth).

Register Number

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Table 4: Registers and their Uses

Name

Use

$zero

Always Zero

$at

Reserved for the Assembler

$v0

Return Value

$a0

Argument 1

$a1

Argument 2

$a2

Argument 3

$t0

Temporary Variable

$t1

Temporary Variable

$t2

Temporary Variable

$s0

Saved Register

$s1

Saved Register

$s2

Saved Register

$k0

Reserved for OS and Traps

$sp

Stack Pointer

$fp

Frame Pointer

$ra

Return Address

Callee Save?

NA

NA

No

No

No

No

No

No

No

Yes

Yes

Yes

NA

No

Yes

No

1. Register 0 is always read as zero. Any values written to it are discarded. Note: for the purposes of

this project, you must implement the zero register. Regardless of what is written to this register, it

should always output zero.

2. Register 1 is a general purpose register. You should not use it because the assembler will use it in

processing pseudo-instructions.

3. Register 2 is where you should store any returned value from a subroutine call.

4. Registers 3 - 5 are used to store temporary values. Note: registers 2 through 8 should be placed

on the stack if the caller wants to retain those values. These registers are fair game for the callee

(subroutine) to trash.

5. Registers 6- 8 are designated for temporary variables. The caller must save these registers if they

want these values to be retained.

6. Registers 9 - 11 are saved registers. The caller may assume that these registers are never tampered

with by the subroutine. if the subroutine needs these registers, then it should place them on the stack

and restore them before they jump back to the caller.

7. Register 12 is used to handle interrupts.

8. Register 13 is your anchor on the stack. It keeps track of the top of the activation record for a

subroutine.

9. Register 14 is used to point to the first address on the activation record for the currently executing

process. Dont worry about using this register.

Project 1

CS 2200 - Systems and Networks

Spring 2015

10. Register 15 is used to store the address a subroutine should return to when it is finsihed executing.

It is only supposed to be used by the JALR (Jump And Link Register) instruction.

There are four types of instructions: R-Type (Register Type), I-Type (Immediate value Type), J-Type

(Jump Type), and S-Type (Stack Type).

Here is the instruction format for R-Type instructions (ADD, NAND):

Bits

Purpose

15 - 13

opcode

12 - 9

RX

8-5

RY

4-1

RZ

0

Unused

Here is the instruction format for I-Type instructions (ADDI, LW, SW, BEQ):

Bits

Purpose

15 - 13

opcode

12 - 9

RX

8-5

RY

4-0

2s Complement Offset

Here is the instruction format for J-Type instructions (JALR):

Bits

Purpose

15 - 13

opcode

12 - 9

RX

8-5

RY

4-0

Unused (all 0s)

Here is the instruction format for S-Type instructions (SPOP):

Bits

Purpose

Name

add

Type

R

nand

addi

lw

sw

beq

jalr

halt

15 - 13

opcode

12 - 2

Unused (all 0s)

1-0

Control Code

Table 5: Assembly Language Instruction Descriptions

Example

Opcode Action

add $v0, $a0, $a2

000

Add contents of RY with the contents

of RZ and store the result in RX.

nand $v0, $a0, $a2

001

NAND contents of RY with the contents of RZ and store the result in RX.

addi $v0, $a0, 7

010

Add contents of RY to the contents of

the offset field and store the result in

RX.

lw $v0, 0x07($sp)

011

Load RX from memory. The memory

address is formed by adding the offset

to the contents of RY.

sw $a0, 0x07($sp)

100

Store RX into memory. The memory

address is formed by adding the offset

to the contents of RY.

beq $a0, $a1, done

101

Compare the contents of RX and RY. If

they are the same, then branch to address PC + 1 + Offset, where PC is the

address of the beq instruction. Memory is word addressed.

jalr $at, $ra

110

First store PC + 1 in RY, where PC

is the address of the jalr instruciton.

Then branch to the address in RX. If

RX = RY, then the processor will store

PC + 1 into RY and end up branching

to PC + 1.

halt

111

Tells the processor to halt. No further

instructions should be executed.

Project 1

CS 2200 - Systems and Networks

Spring 2015

Finally, the assembler supports labels which represent the address of the line it is on. If a label is used in a

BEQ instruction, it will evaluate to some relative offset.

For example:

(address 0):

(address 1):

(address 2):

(address 3):

(address 4):

Becomes:

(address

(address

(address

(address

(address

0):

1):

2):

3):

4):

loop:

end:

000

010

101

101

111

add $s0, $zero, $zero

addi $s0, $s0, -1

beq $s0, $zero, end

beq $zero, $zero, loop

halt

1001

1001

1001

0000

0000

0000

1001

0000

0000

0000

00000

11111

00001

11101

00000

or

or

or

or

or

0x1200

0x533F

0xB201

0xA01D

oxE000

S-ar putea să vă placă și

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.De la EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Încă nu există evaluări

- Project 1Document9 paginiProject 1openid_FpjZWipRÎncă nu există evaluări

- Project 1Document12 paginiProject 1John SmithÎncă nu există evaluări

- WAN TECHNOLOGY FRAME-RELAY: An Expert's Handbook of Navigating Frame Relay NetworksDe la EverandWAN TECHNOLOGY FRAME-RELAY: An Expert's Handbook of Navigating Frame Relay NetworksÎncă nu există evaluări

- AutomationDocument31 paginiAutomationJerry JosephÎncă nu există evaluări

- PLC Programming Using SIMATIC MANAGER for Beginners: With Basic Concepts of Ladder Logic ProgrammingDe la EverandPLC Programming Using SIMATIC MANAGER for Beginners: With Basic Concepts of Ladder Logic ProgrammingEvaluare: 4 din 5 stele4/5 (1)

- Application Note 1Document7 paginiApplication Note 1hossam_fadeel2560Încă nu există evaluări

- PLC Programming from Novice to Professional: Learn PLC Programming with Training VideosDe la EverandPLC Programming from Novice to Professional: Learn PLC Programming with Training VideosEvaluare: 5 din 5 stele5/5 (1)

- Lab - Establishing A Console Session With Tera TermDocument5 paginiLab - Establishing A Console Session With Tera TermKevin KimÎncă nu există evaluări

- 2.1.4.7 Lab - Establishing A Console Session With Tera TermDocument11 pagini2.1.4.7 Lab - Establishing A Console Session With Tera Term12niverÎncă nu există evaluări

- Project 2 Computer ScienceDocument9 paginiProject 2 Computer SciencethedonutpirateÎncă nu există evaluări

- Laboratorio DroneDocument7 paginiLaboratorio DroneFernando MontanhaÎncă nu există evaluări

- Lab 0Document8 paginiLab 0huutan86Încă nu există evaluări

- TSR NotesDocument6 paginiTSR NotesTarun KulchandraÎncă nu există evaluări

- Calc ProjectDocument3 paginiCalc Projectsumitg_27Încă nu există evaluări

- MET 382 Lab 1 Fall 09Document6 paginiMET 382 Lab 1 Fall 09Minn HtutÎncă nu există evaluări

- Lab 01 - Introduction To PLC Hardware and SoftwareDocument18 paginiLab 01 - Introduction To PLC Hardware and SoftwareSyed Abdullah Hasan Chishti100% (1)

- PCB Drilling Machine 2Document7 paginiPCB Drilling Machine 2juliusjgunnÎncă nu există evaluări

- Lab 1 - The Basics: ObjectivesDocument7 paginiLab 1 - The Basics: Objectivesjramisch44Încă nu există evaluări

- Laboratorio de Enseñaza 2: TopologyDocument7 paginiLaboratorio de Enseñaza 2: TopologyVICUÑA HUAYLINOS CESAR AUGUSTOÎncă nu există evaluări

- Volume6 2003 PDFDocument31 paginiVolume6 2003 PDFZeljkoSipcicÎncă nu există evaluări

- Villaseñor - MP2 - 100% - October 28, 2022Document27 paginiVillaseñor - MP2 - 100% - October 28, 2022Villaseñor, Christian Cyrille Y.Încă nu există evaluări

- Lab 1 - Part A (2.3.8) - Navigate The IOS by Using Tera Term For Console Connectivity-UpdatedDocument6 paginiLab 1 - Part A (2.3.8) - Navigate The IOS by Using Tera Term For Console Connectivity-Updatedkhalifaalmuhairi20Încă nu există evaluări

- AS-84.3149 Bionics: Project Work Spring 2008Document12 paginiAS-84.3149 Bionics: Project Work Spring 2008veenadivyakishÎncă nu există evaluări

- Scicos Vs SimulinkDocument65 paginiScicos Vs SimulinkaalbieroÎncă nu există evaluări

- Today We Will Cover The First Three Steps On How To Backup Your Allen-Bradley Logix Controller Program To Your PC. The Detailed Steps IncludeDocument13 paginiToday We Will Cover The First Three Steps On How To Backup Your Allen-Bradley Logix Controller Program To Your PC. The Detailed Steps IncludeKrishna JashaÎncă nu există evaluări

- 2.3.8 Lab - Navigate The IOS by Using Tera Term For Console Connectivity - ILMDocument7 pagini2.3.8 Lab - Navigate The IOS by Using Tera Term For Console Connectivity - ILMMichael Isael Altamirano CuevaÎncă nu există evaluări

- Lab1 SpecDocument6 paginiLab1 Spec星期三的配音是對的Încă nu există evaluări

- Connect Kuka Robots With RoboDKDocument6 paginiConnect Kuka Robots With RoboDKRicardo100% (1)

- Wireless Simulation With QualnetDocument16 paginiWireless Simulation With Qualnetkdilip05Încă nu există evaluări

- Telepo SDK Develop Guide Linux For TPS300 v1 0Document10 paginiTelepo SDK Develop Guide Linux For TPS300 v1 0Petit-Homme Ben-JacquesÎncă nu există evaluări

- LC 3b ProjectDocument11 paginiLC 3b ProjectParmanand KhajuriyaÎncă nu există evaluări

- PLC Software: Hand Held ProgrammerDocument11 paginiPLC Software: Hand Held Programmervamsidar47Încă nu există evaluări

- MCRNC Commissioning Guide Document V1 0Document57 paginiMCRNC Commissioning Guide Document V1 0AbdalalhÎncă nu există evaluări

- ECE 315 Computer Interfacing Lab #3: Interfacing Using The Zynq-7000 SPI InterfaceDocument7 paginiECE 315 Computer Interfacing Lab #3: Interfacing Using The Zynq-7000 SPI InterfaceShawn ShadeÎncă nu există evaluări

- Readme PDFDocument12 paginiReadme PDFXavier FelixÎncă nu există evaluări

- Programming PIC Microcontrollers in CDocument126 paginiProgramming PIC Microcontrollers in CShomeswaran Mugunthan100% (3)

- SLC Examples Application Manual: 3150-MCM Example Ladder LogicDocument24 paginiSLC Examples Application Manual: 3150-MCM Example Ladder LogicVÕ QUỐC HIỆUÎncă nu există evaluări

- Chapter 3Document11 paginiChapter 3nikhilÎncă nu există evaluări

- Lab 2 Networking DevicesDocument13 paginiLab 2 Networking DevicesramanshankarÎncă nu există evaluări

- Idirect User Manual W2ADocument35 paginiIdirect User Manual W2AAlexander LouisÎncă nu există evaluări

- 00 - Final Project - V9-SimonlyDocument8 pagini00 - Final Project - V9-SimonlyAndré SantosÎncă nu există evaluări

- New PLC Lab Manual2 Compressed (1) 1650437778Document66 paginiNew PLC Lab Manual2 Compressed (1) 1650437778sureshgurujiÎncă nu există evaluări

- 2SIT325-21P Network Performance Evaluation-TaskSheetDocument5 pagini2SIT325-21P Network Performance Evaluation-TaskSheetNarendraÎncă nu există evaluări

- MCRNC Commissioning Guide Document-V1.0Document57 paginiMCRNC Commissioning Guide Document-V1.0metootheskull90% (10)

- How To Program The ScopeDocument4 paginiHow To Program The ScopetuxnorÎncă nu există evaluări

- Spectrum Shadow ROMDisassemblyDocument149 paginiSpectrum Shadow ROMDisassemblyMarcos GeorgeÎncă nu există evaluări

- Oaisim WalkthroughDocument7 paginiOaisim Walkthroughselvakumar2k2Încă nu există evaluări

- EasyPLC User Manual PDFDocument100 paginiEasyPLC User Manual PDFJac JacÎncă nu există evaluări

- QL Prog - ManualDocument25 paginiQL Prog - ManualOscar GarnicaÎncă nu există evaluări

- Tutorial On Simatic s5 Control System :practical Programming and Fault FindingDocument22 paginiTutorial On Simatic s5 Control System :practical Programming and Fault Findingak4dili80% (5)

- COGENT Toolbox Manual v125Document51 paginiCOGENT Toolbox Manual v125LlassimoÎncă nu există evaluări

- Using Labview To Design A Payload Control System: Stephen HoranDocument10 paginiUsing Labview To Design A Payload Control System: Stephen HoranPradip GuptaÎncă nu există evaluări

- Ucos + ArmDocument33 paginiUcos + Armசெல்வம் முத்துராமன்Încă nu există evaluări

- PLC-Driver (V5) Schneider Modicon TSX Quantum Momentum Compact - Modbus TCP-IPDocument7 paginiPLC-Driver (V5) Schneider Modicon TSX Quantum Momentum Compact - Modbus TCP-IPAdelmoKarigÎncă nu există evaluări

- Nrf24l01 Tutorial 1 Pic18Document9 paginiNrf24l01 Tutorial 1 Pic18Silvanei Fonseca LeandroÎncă nu există evaluări

- Micro HopeDocument48 paginiMicro Hopeviolator100% (1)

- Lab 3: Basic C Signals and Sockets ICMP/PING, and TracerouteDocument7 paginiLab 3: Basic C Signals and Sockets ICMP/PING, and TracerouteInf EtherealÎncă nu există evaluări

- Software Stage EDocument19 paginiSoftware Stage ETim TaylorÎncă nu există evaluări

- 2200book Full PDFDocument705 pagini2200book Full PDFVignesh Prasad100% (8)

- 2200book Full PDFDocument705 pagini2200book Full PDFVignesh Prasad100% (8)

- Chapter 13Document7 paginiChapter 13Vignesh PrasadÎncă nu există evaluări

- 2200book Full PDFDocument705 pagini2200book Full PDFVignesh Prasad100% (8)

- Answer KeyDocument49 paginiAnswer KeyEnglish Teacher0% (1)

- Active HDL Simulation TutorialDocument6 paginiActive HDL Simulation Tutorialtapas_bayen9388Încă nu există evaluări

- 08 Coombes PostcolonialDocument6 pagini08 Coombes PostcolonialStergios SourlopoulosÎncă nu există evaluări

- Curriculum Approaches in Language Teaching:: Forward, Central, and Backward DesignDocument24 paginiCurriculum Approaches in Language Teaching:: Forward, Central, and Backward DesignJohn Carlo Quiane100% (1)

- Companion To Real Analysis - ErdmanDocument261 paginiCompanion To Real Analysis - ErdmankhoconnoÎncă nu există evaluări

- Lit Analysis 2 - ManilaDocument6 paginiLit Analysis 2 - ManilaPatrick Nuguid100% (1)

- Intro To DBMS Unit 1 AKTUDocument34 paginiIntro To DBMS Unit 1 AKTUSyed Ahmad HusainÎncă nu există evaluări

- A 0214050103Document3 paginiA 0214050103Ximena MorenoÎncă nu există evaluări

- Deductive DatabasesDocument23 paginiDeductive DatabasesMuhammed JishanÎncă nu există evaluări

- Rohit Dvclub 130422125508 Phpapp02Document20 paginiRohit Dvclub 130422125508 Phpapp02Sam HoneyÎncă nu există evaluări

- 6MF28520AA00 Datasheet enDocument3 pagini6MF28520AA00 Datasheet enIvan JeremicÎncă nu există evaluări

- RPM CounterDocument4 paginiRPM CountermailtoakhilsÎncă nu există evaluări

- The Heart of Oracle How The Core Architecture Works Martin Widlake PDFDocument45 paginiThe Heart of Oracle How The Core Architecture Works Martin Widlake PDFronrodriÎncă nu există evaluări

- Critical Thinking and Critical PedagogyDocument28 paginiCritical Thinking and Critical PedagogySohail AkhtarÎncă nu există evaluări

- K80S & K120S Wiring DiagramDocument2 paginiK80S & K120S Wiring DiagramrawsteelÎncă nu există evaluări

- Dewi Noviyanti FitkDocument81 paginiDewi Noviyanti FitkReinaldus Aton 12118023Încă nu există evaluări

- Computer NetworkDocument14 paginiComputer NetworkRoger FreeÎncă nu există evaluări

- Cambridge Vocabulary For IELTS Unit 5Document9 paginiCambridge Vocabulary For IELTS Unit 5Minh Chanh Nguyen100% (2)

- Selection ViewDocument351 paginiSelection ViewjitendrayadavcsÎncă nu există evaluări

- The American Novel in The 21st Century: Changing Contexts, Literary Developments, New Modes of ReadingDocument49 paginiThe American Novel in The 21st Century: Changing Contexts, Literary Developments, New Modes of ReadingАлександра ГеркероваÎncă nu există evaluări

- Assignment Meg 004 (14 15)Document1 paginăAssignment Meg 004 (14 15)bubli234100% (1)

- APJDDVol1No2 ShenDocument36 paginiAPJDDVol1No2 ShenGrace Kong Yun RuiÎncă nu există evaluări

- DLD Lab-11 Sequential Circuit Using SR, D and JK Flip-Flop: Software: Circuit Maker TASK1Document7 paginiDLD Lab-11 Sequential Circuit Using SR, D and JK Flip-Flop: Software: Circuit Maker TASK1Anonymous AnonymousÎncă nu există evaluări

- SF LRN XDom O C S IntegDocument34 paginiSF LRN XDom O C S IntegThuyết Mai VănÎncă nu există evaluări

- IEC 61850 Server Interface: User ManualDocument33 paginiIEC 61850 Server Interface: User ManualThành CôngÎncă nu există evaluări

- Influence of Atmospheric Stability On The Spatial Structure of TurbulenceDocument109 paginiInfluence of Atmospheric Stability On The Spatial Structure of TurbulenceKlaas KronaÎncă nu există evaluări

- Presentation SCADA GroupDocument59 paginiPresentation SCADA GroupUdit Upreti100% (1)

- Body Image and The Media EssaysDocument6 paginiBody Image and The Media EssayskbmbwubafÎncă nu există evaluări

- A Companion To The Study of HistoryDocument369 paginiA Companion To The Study of HistoryNawaz205050% (2)

- "Without Contraries, There Is No Progression": An Analysis On Blake'sDocument6 pagini"Without Contraries, There Is No Progression": An Analysis On Blake'sSara LupónÎncă nu există evaluări

- Computer Science: A Concise IntroductionDe la EverandComputer Science: A Concise IntroductionEvaluare: 4.5 din 5 stele4.5/5 (14)

- CompTIA Security+ All-in-One Exam Guide, Sixth Edition (Exam SY0-601)De la EverandCompTIA Security+ All-in-One Exam Guide, Sixth Edition (Exam SY0-601)Evaluare: 5 din 5 stele5/5 (1)

- iPhone 15 Pro User Guide for Beginners and SeniorsDe la EverandiPhone 15 Pro User Guide for Beginners and SeniorsÎncă nu există evaluări

- Chip War: The Quest to Dominate the World's Most Critical TechnologyDe la EverandChip War: The Quest to Dominate the World's Most Critical TechnologyEvaluare: 4.5 din 5 stele4.5/5 (227)

- Chip War: The Fight for the World's Most Critical TechnologyDe la EverandChip War: The Fight for the World's Most Critical TechnologyEvaluare: 4.5 din 5 stele4.5/5 (82)

- Unlock Any Roku Device: Watch Shows, TV, & Download AppsDe la EverandUnlock Any Roku Device: Watch Shows, TV, & Download AppsÎncă nu există evaluări

- iPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XDe la EverandiPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XEvaluare: 3 din 5 stele3/5 (2)

- Amazon Web Services (AWS) Interview Questions and AnswersDe la EverandAmazon Web Services (AWS) Interview Questions and AnswersEvaluare: 4.5 din 5 stele4.5/5 (3)

- Windows 10 Mastery: The Complete User Guide to Learn Windows 10 from Beginner to ExpertDe la EverandWindows 10 Mastery: The Complete User Guide to Learn Windows 10 from Beginner to ExpertEvaluare: 3.5 din 5 stele3.5/5 (6)

- CompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102De la EverandCompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Evaluare: 5 din 5 stele5/5 (2)

- Hacking With Linux 2020:A Complete Beginners Guide to the World of Hacking Using Linux - Explore the Methods and Tools of Ethical Hacking with LinuxDe la EverandHacking With Linux 2020:A Complete Beginners Guide to the World of Hacking Using Linux - Explore the Methods and Tools of Ethical Hacking with LinuxÎncă nu există evaluări

- Programming with STM32: Getting Started with the Nucleo Board and C/C++De la EverandProgramming with STM32: Getting Started with the Nucleo Board and C/C++Evaluare: 3.5 din 5 stele3.5/5 (3)

- Essential iPhone X iOS 12 Edition: The Illustrated Guide to Using iPhone XDe la EverandEssential iPhone X iOS 12 Edition: The Illustrated Guide to Using iPhone XEvaluare: 5 din 5 stele5/5 (1)

- How to Jailbreak Roku: Unlock Roku, Roku Stick, Roku Ultra, Roku Express, Roku TV with Kodi Step by Step GuideDe la EverandHow to Jailbreak Roku: Unlock Roku, Roku Stick, Roku Ultra, Roku Express, Roku TV with Kodi Step by Step GuideEvaluare: 1 din 5 stele1/5 (1)

- CompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002De la EverandCompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002Evaluare: 5 din 5 stele5/5 (1)

- iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]De la EverandiPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]Evaluare: 5 din 5 stele5/5 (2)

- Mastering IoT For Industrial Environments: Unlock the IoT Landscape for Industrial Environments with Industry 4.0, Covering Architecture, Protocols like MQTT, and Advancements with ESP-IDFDe la EverandMastering IoT For Industrial Environments: Unlock the IoT Landscape for Industrial Environments with Industry 4.0, Covering Architecture, Protocols like MQTT, and Advancements with ESP-IDFÎncă nu există evaluări

- Raspberry Pi for Python Programmers Cookbook - Second EditionDe la EverandRaspberry Pi for Python Programmers Cookbook - Second EditionÎncă nu există evaluări

- Raspberry Pi Retro Gaming: Build Consoles and Arcade Cabinets to Play Your Favorite Classic GamesDe la EverandRaspberry Pi Retro Gaming: Build Consoles and Arcade Cabinets to Play Your Favorite Classic GamesÎncă nu există evaluări

- Amazon Echo Manual Guide : Top 30 Hacks And Secrets To Master Amazon Echo & Alexa For Beginners: The Blokehead Success SeriesDe la EverandAmazon Echo Manual Guide : Top 30 Hacks And Secrets To Master Amazon Echo & Alexa For Beginners: The Blokehead Success SeriesÎncă nu există evaluări

- iPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsDe la EverandiPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsEvaluare: 5 din 5 stele5/5 (2)

- Embedded Systems Design with Platform FPGAs: Principles and PracticesDe la EverandEmbedded Systems Design with Platform FPGAs: Principles and PracticesEvaluare: 5 din 5 stele5/5 (1)

- Real-Time UML Workshop for Embedded SystemsDe la EverandReal-Time UML Workshop for Embedded SystemsEvaluare: 3.5 din 5 stele3.5/5 (2)

![iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]](https://imgv2-1-f.scribdassets.com/img/audiobook_square_badge/728318688/198x198/f3385cbfef/1714829744?v=1)