Documente Academic

Documente Profesional

Documente Cultură

Gate Level Modeling

Încărcat de

Irfan HussainDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Gate Level Modeling

Încărcat de

Irfan HussainDrepturi de autor:

Formate disponibile

UNIVERSITY OF ENGINEERING AND TECHNOLOGY, TAXILA

FACULTY OF TELECOMMUNICATION AND INFORMATION ENGINEERING

COMPUTER ENGINEERING DEPARTMENT

Digital Logic Design

Introduction to Gate Level Modeling in Verilog

Dated:

04th April, 2016 to 08th April, 2016

Semester:

Spring 2016

Digital Logic Design

Session:-2K15 Computer

Lab Instructor:-Engr. Aamir Arsalan

UNIVERSITY OF ENGINEERING AND TECHNOLOGY, TAXILA

FACULTY OF TELECOMMUNICATION AND INFORMATION ENGINEERING

COMPUTER ENGINEERING DEPARTMENT

Objective:At the end of this part of the lab you should be able to:

Write a Verilog code at gate level.

What is Verilog?

Verilog is a programming language that has been developed for describing digital circuits and

systems.

Verilog is case-sensitive.

Verilog is free format |i.e. statements can be written on one line or on multiple lines.

// is used to create a comment line.

Verilog supports two type of operators: Arithmetic operators.

Bit-wise operators

Different Types of Design Models in Verilog:There are four different types of modeling methods in Verilog.

Switch Level Modeling

Gate Level Modeling

Data Flow Modeling

Behavioral Modeling

In Digital Design we mostly use Gate level modeling, Data Flow Modeling, Behavioral Modeling.

It is very rare that we choose switch level modeling using transistors, but Verilog provides us to

model at switch level. Switch level is not mostly used because with the increasing complexity of

circuits it becomes very difficult to manage switches so we switch to higher level of modeling.

Verilog only has well defined states 0, 1, x, z. There is no analog value in Verilog, so the transistors

act as switches here with sates of on or off.

Gate Level Modeling:Verilog has built in primitives like gates, transmission gates, and switches.

Digital Logic Design

Session:-2K15 Computer

Lab Instructor:-Engr. Aamir Arsalan

UNIVERSITY OF ENGINEERING AND TECHNOLOGY, TAXILA

FACULTY OF TELECOMMUNICATION AND INFORMATION ENGINEERING

COMPUTER ENGINEERING DEPARTMENT

The gates have one scalar output and multiple scalar inputs. The 1st terminal in the list of gate

terminals is an output and the other terminals are inputs.

Examples: and U1(out,in);

and U2(out,in1,in2,in3,in4);

xor U3(out,in1,in2,in3);

Digital Logic Design

Session:-2K15 Computer

Lab Instructor:-Engr. Aamir Arsalan

UNIVERSITY OF ENGINEERING AND TECHNOLOGY, TAXILA

FACULTY OF TELECOMMUNICATION AND INFORMATION ENGINEERING

COMPUTER ENGINEERING DEPARTMENT

Transmission Gate Primitives:-

Examples: bufif0 U1(data_bus,data_drive, data_enable_low);

buf U2(out,in);

not U3(out,in);

Designing Using Primitives:NOT gate using NAND Gate:-

Digital Logic Design

Session:-2K15 Computer

Lab Instructor:-Engr. Aamir Arsalan

UNIVERSITY OF ENGINEERING AND TECHNOLOGY, TAXILA

FACULTY OF TELECOMMUNICATION AND INFORMATION ENGINEERING

COMPUTER ENGINEERING DEPARTMENT

AND gate using NAND Gate:-

Implement OR using NAND:-

Implement NOR using NAND:-

Digital Logic Design

Session:-2K15 Computer

Lab Instructor:-Engr. Aamir Arsalan

UNIVERSITY OF ENGINEERING AND TECHNOLOGY, TAXILA

FACULTY OF TELECOMMUNICATION AND INFORMATION ENGINEERING

COMPUTER ENGINEERING DEPARTMENT

Implement XOR using NAND:-

Implement NOT using NOR Gate:-

Implement AND using NOR:-

Digital Logic Design

Session:-2K15 Computer

Lab Instructor:-Engr. Aamir Arsalan

UNIVERSITY OF ENGINEERING AND TECHNOLOGY, TAXILA

FACULTY OF TELECOMMUNICATION AND INFORMATION ENGINEERING

COMPUTER ENGINEERING DEPARTMENT

Implement OR Using NOR:-

Implement NAND using NOR:-

Implement XOR using NOR:-

Digital Logic Design

Session:-2K15 Computer

Lab Instructor:-Engr. Aamir Arsalan

UNIVERSITY OF ENGINEERING AND TECHNOLOGY, TAXILA

FACULTY OF TELECOMMUNICATION AND INFORMATION ENGINEERING

COMPUTER ENGINEERING DEPARTMENT

Verilog code for implementing NOT gate using NAND Gate:-

module nand_and(out,in1);

input in1;

output out;

nand(out,in1,in1);

endmodule

Lab Tasks:Write the Verilog code for all the above circuits and

verify their operation.

Digital Logic Design

Session:-2K15 Computer

Lab Instructor:-Engr. Aamir Arsalan

S-ar putea să vă placă și

- KNN Image Classification Using MS EE AI DatasetDocument4 paginiKNN Image Classification Using MS EE AI DatasetIrfan HussainÎncă nu există evaluări

- ResultsDocument13 paginiResultsIrfan HussainÎncă nu există evaluări

- Electrical Substations: How To Remember Lagging and Leading Phenomenon of Capacitor andDocument2 paginiElectrical Substations: How To Remember Lagging and Leading Phenomenon of Capacitor andIrfan HussainÎncă nu există evaluări

- IDAPS Model for Intelligent Distributed Autonomous Power SystemDocument4 paginiIDAPS Model for Intelligent Distributed Autonomous Power SystemIrfan HussainÎncă nu există evaluări

- Intelligent Distributed Autonomous Power System Model (IDAPSDocument26 paginiIntelligent Distributed Autonomous Power System Model (IDAPSIrfan HussainÎncă nu există evaluări

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5784)

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (890)

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (399)

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (265)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (72)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (344)

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (119)

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)

- Personal Statement SamplesDocument11 paginiPersonal Statement SamplesAshfaque HussainÎncă nu există evaluări

- Lab 2Document3 paginiLab 2ruseÎncă nu există evaluări

- SynopsysDocument20 paginiSynopsysbennettmatthewÎncă nu există evaluări

- Ecen 248 Lab 8 ReportDocument7 paginiEcen 248 Lab 8 Reportapi-241454978Încă nu există evaluări

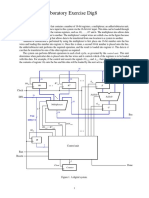

- Laboratory Exercise D: R0, - . - , R7 and A. The Multiplexer Also Allows DataDocument6 paginiLaboratory Exercise D: R0, - . - , R7 and A. The Multiplexer Also Allows DataMunya RushambwaÎncă nu există evaluări

- Linking Novas Files With Simulators and Enabling FSDB DumpingDocument172 paginiLinking Novas Files With Simulators and Enabling FSDB DumpingMarko Nedic100% (2)

- VCS TrainingDocument80 paginiVCS Trainingcaya0401923611Încă nu există evaluări

- Edi11 Ccopt SlidesDocument28 paginiEdi11 Ccopt SlidesBaluvu JagadishÎncă nu există evaluări

- Register Management With Csrcompiler An Introduction: 145 Eldora Drive Mountain View, Ca 94041 (650) 960-0925Document16 paginiRegister Management With Csrcompiler An Introduction: 145 Eldora Drive Mountain View, Ca 94041 (650) 960-0925varunmrÎncă nu există evaluări

- AMD Previous Int QuestionsDocument9 paginiAMD Previous Int QuestionsMahmood VdnÎncă nu există evaluări

- Laboratory No. 9: Simple Calculator (Final LabDocument10 paginiLaboratory No. 9: Simple Calculator (Final Lab2017 01051Încă nu există evaluări

- Dram Sim 2Document4 paginiDram Sim 2pjluluÎncă nu există evaluări

- Qts Qii51007Document76 paginiQts Qii51007Nisreen AlhamriÎncă nu există evaluări

- Synthesis ABCs Part 1: From Files to ConstraintsDocument37 paginiSynthesis ABCs Part 1: From Files to Constraintsmadhu.thomas4541100% (1)

- Making Qsys ComponentsDocument36 paginiMaking Qsys ComponentsJulian Mauricio Ruiz EcheverriÎncă nu există evaluări

- RTL Sandesh P 1.3yearsDocument3 paginiRTL Sandesh P 1.3yearschaitanyhÎncă nu există evaluări

- VLSI Semi Custom Design Methodologies GuideDocument25 paginiVLSI Semi Custom Design Methodologies GuidePraveen KumarÎncă nu există evaluări

- Verilog HDL Lab - ODD - 2019 - 20 LAB MANUALDocument69 paginiVerilog HDL Lab - ODD - 2019 - 20 LAB MANUAL098 Prajwal SÎncă nu există evaluări

- Verilog Bhaskar .JDocument230 paginiVerilog Bhaskar .JSuraj GhaleÎncă nu există evaluări

- Lab 10Document14 paginiLab 10shailly_shahÎncă nu există evaluări

- Asic - QPDocument2 paginiAsic - QPveeramaniks408Încă nu există evaluări

- BugHunter Pro and VeriLogger ProDocument63 paginiBugHunter Pro and VeriLogger ProParan NatarajanÎncă nu există evaluări

- Getting Started Lab With SpyGlass 450Document47 paginiGetting Started Lab With SpyGlass 450Siva Kamuni50% (2)

- Module 1 - Introduction To Hardware Description LanguageDocument32 paginiModule 1 - Introduction To Hardware Description LanguageNanilyn TumlodÎncă nu există evaluări

- Embedded Linux Hands-On Tutorial - Zedboard: Design Is Shown in Figure 1Document46 paginiEmbedded Linux Hands-On Tutorial - Zedboard: Design Is Shown in Figure 1Federico Garcia CÎncă nu există evaluări

- EGCP 446: Advanced Digital Design: Part One - Moore State Machine On FPGADocument16 paginiEGCP 446: Advanced Digital Design: Part One - Moore State Machine On FPGAShashwat PatelÎncă nu există evaluări

- Design of Embedded ProcessorsDocument80 paginiDesign of Embedded ProcessorsSayan Kumar KhanÎncă nu există evaluări

- Signals & Systems (Common To Ec/Tc/It/Bm/Ml)Document5 paginiSignals & Systems (Common To Ec/Tc/It/Bm/Ml)sureshfm1Încă nu există evaluări

- Eg09 AXI4 StreamDocument15 paginiEg09 AXI4 StreamHarrishÎncă nu există evaluări

- 281 Final Project - Eli and BaylorDocument18 pagini281 Final Project - Eli and Baylorapi-696541991Încă nu există evaluări