Documente Academic

Documente Profesional

Documente Cultură

Arquitectura Harvard

Încărcat de

Jose Giovanni Gf0 evaluări0% au considerat acest document util (0 voturi)

67 vizualizări4 paginiEl documento describe y compara las arquitecturas de Von Neumann y Harvard. La arquitectura de Von Neumann tiene una memoria única para instrucciones y datos, mientras que la arquitectura Harvard tiene memorias separadas. La arquitectura de Harvard permite el acceso simultáneo a las memorias de instrucciones y datos, lo que mejora la velocidad en comparación con la arquitectura de Von Neumann que solo permite accesos secuenciales a la memoria única.

Descriere originală:

Programación acerca de la arquitectura harvard

Drepturi de autor

© © All Rights Reserved

Formate disponibile

DOCX, PDF, TXT sau citiți online pe Scribd

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentEl documento describe y compara las arquitecturas de Von Neumann y Harvard. La arquitectura de Von Neumann tiene una memoria única para instrucciones y datos, mientras que la arquitectura Harvard tiene memorias separadas. La arquitectura de Harvard permite el acceso simultáneo a las memorias de instrucciones y datos, lo que mejora la velocidad en comparación con la arquitectura de Von Neumann que solo permite accesos secuenciales a la memoria única.

Drepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca DOCX, PDF, TXT sau citiți online pe Scribd

0 evaluări0% au considerat acest document util (0 voturi)

67 vizualizări4 paginiArquitectura Harvard

Încărcat de

Jose Giovanni GfEl documento describe y compara las arquitecturas de Von Neumann y Harvard. La arquitectura de Von Neumann tiene una memoria única para instrucciones y datos, mientras que la arquitectura Harvard tiene memorias separadas. La arquitectura de Harvard permite el acceso simultáneo a las memorias de instrucciones y datos, lo que mejora la velocidad en comparación con la arquitectura de Von Neumann que solo permite accesos secuenciales a la memoria única.

Drepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca DOCX, PDF, TXT sau citiți online pe Scribd

Sunteți pe pagina 1din 4

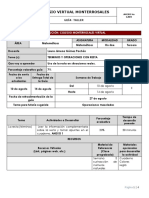

Jos Giovanni Gutirrez Flores

19/feb/2016

Investiga la arquitectura Harvard y de Von Neumann

Arquitectura von Neumann y arquitectura Harvard

Hay dos arquitecturas distintas relacionadas con el uso y distribucin de la

memoria: Arquitectura de von Neumann y Arquitectura Harvard.

Arquitectura de von Neumann: Tradicionalmente los sistemas con

microprocesadores se basan en esta arquitectura, en la cual la unidad central de

proceso (CPU), est conectada a una memoria principal nica (casi siempre slo

RAM) donde se guardan las instrucciones del programa y los datos. A dicha

memoria se accede a travs de un sistema de buses nico (control, direcciones y

datos).

En un sistema con arquitectura Von Neumann el tamao de la unidad de datos o

instrucciones est fijado

por el ancho del bus que comunica la memoria con la CPU. As un

microprocesador de 8 bits con un bus de 8 bits, tendr que manejar datos e

instrucciones de una o ms unidades de 8 bits (bytes) de longitud. Si tiene

que acceder a una instruccin o dato de ms de un byte de longitud, tendr que

realizar ms de un acceso a la memoria.

El tener un nico bus hace que el microprocesador sea ms lento en su

respuesta, ya que no puede buscar

en memoria una nueva instruccin mientras no finalicen las transferencias de

datos de la instruccin anterior.

Las principales limitaciones que nos encontramos con la arquitectura Von

Neumann son:

La limitacin de la longitud de las instrucciones por el bus de datos, que

hace que el microprocesador tenga que realizar varios accesos a memoria

para buscar instrucciones complejas.

Jos Giovanni Gutirrez Flores

19/feb/2016

La limitacin de la velocidad de operacin a causa del bus nico para datos

e instrucciones que no deja acceder simultneamente a unos y otras, lo

cual impide superponer ambos tiempos de acceso

Los ordenadores con arquitectura Von Neumann constan de las siguientes

partes:

La arquitectura Von Neumann realiza o emula los siguientes pasos

secuencialmente:

1) Obtiene la siguiente instruccin desde la memoria en la direccin indicada por

el contador de programa y la guarda en el registro de instruccin.

2) Aumenta el contador de programa en la longitud de la instruccin para apuntar

a la siguiente.

3) Descodifica la instruccin mediante la unidad de control. sta se encarga de

coordinar el resto de componentes del ordenador para realizar una funcin

determinada.

4) Se ejecuta la instruccin. sta puede cambiar el valor del contador del

programa, permitiendo as operaciones repetitivas.

5) Regresa al paso N 1.

Conclusin:

* La mayora de las computadoras todava utilizan la arquitectura Von Neumann,

propuesta a principios de los aos 40 por John Von Neumann.

* La arquitectura Von Neumann describe a la computadora con 4 secciones

Jos Giovanni Gutirrez Flores

19/feb/2016

principales: la unidad lgica y aritmtica (ALU), la unidad de control, la memoria, y

los dispositivos de entrada y salida (E/S).

* En este sistema, la memoria es una secuencia de celdas de almacenamiento

numeradas, donde cada una es un bit, o unidad de informacin.

La instruccin es la informacin necesaria para realizar, lo que se desea, con la

computadora.

Las celdas contienen datos que se necesitan para llevar a cabo las instrucciones,

con la computadora.

* El tamao de cada celda y el nmero de celdas vara mucho de computadora a

computadora, y las tecnologas empleadas para la memoria han cambiado

bastante; van desde los rels electromecnicos, tubos llenos de mercurio en los

que se formaban los pulsos acsticos, matrices de imanes permanentes,

transistores individuales a circuitos integrados con millones de celdas en un solo

chip.

Arquitectura Harvard: Este modelo, que utilizan los Microcontroladores PIC,

tiene la unidad central de

proceso (CPU) conectada a dos memorias (una con las instrucciones y otra con

los datos) por medio de dos buses diferentes.

Una de las memorias contiene solamente las instrucciones del programa

(Memoria de Programa), y la otra slo almacena datos (Memoria de Datos).

Ambos buses son totalmente independientes lo que permite que la CPU pueda

acceder de forma

independiente y simultnea a la memoria de datos y a la de instrucciones. Como

los buses son independientes estos pueden tener distintos contenidos en la

misma direccin y tambin distinta longitud.

Tambien la longitud de los datos y las instrucciones puede ser distinta, lo que

optimiza el uso de la memoria en general.

Para un procesador de Set de Instrucciones Reducido, o RISC (Reduced

Jos Giovanni Gutirrez Flores

19/feb/2016

Instruccin Set Com puter), el set de instrucciones y el bus de memoria de

programa pueden disearse de tal manera que todas las instrucciones tengan una

sola posicin de memoria de programa de longitud.

Adems, al ser los buses independientes, la CPU puede acceder a los datos para

completar la ejecucin de

una instruccin, y al mismo tiempo leer la siguiente instruccin a ejecutar.

Ventajas de esta arquitectura:

* El tamao de las instrucciones no est relacionado con el de los datos, y por lo

tanto puede ser

optimizado para que cualquier instruccin ocupe una sola posicin de memoria de

programa,

logrando as mayor velocidad y menor longitud de programa.

* El tiempo de acceso a las instrucciones puede superponerse con el de los datos,

logrando una

mayor velocidad en cada operacin.

S-ar putea să vă placă și

- Fundamentos de Redes InformáticasDe la EverandFundamentos de Redes InformáticasEvaluare: 4.5 din 5 stele4.5/5 (9)

- Simbologia Del Grado de Aprendiz y Del T PDFDocument146 paginiSimbologia Del Grado de Aprendiz y Del T PDFHunter Samame100% (12)

- Programación de microcontroladores paso a paso: Ejemplos prácticos desarrollados en la nubeDe la EverandProgramación de microcontroladores paso a paso: Ejemplos prácticos desarrollados en la nubeÎncă nu există evaluări

- Computadores para bases de datos. IFCT0310De la EverandComputadores para bases de datos. IFCT0310Încă nu există evaluări

- UF0513 - Gestión auxiliar de archivo en soporte convencional o informáticoDe la EverandUF0513 - Gestión auxiliar de archivo en soporte convencional o informáticoEvaluare: 1 din 5 stele1/5 (1)

- Planificación Cuarto PrimariaDocument26 paginiPlanificación Cuarto PrimariaHenryhg282% (74)

- Compilador C CCS y Simulador Proteus para Microcontroladores PICDe la EverandCompilador C CCS y Simulador Proteus para Microcontroladores PICEvaluare: 2.5 din 5 stele2.5/5 (5)

- UF1271 - Instalación y configuración del software de servidor webDe la EverandUF1271 - Instalación y configuración del software de servidor webÎncă nu există evaluări

- Manejo Técnico de PacoDocument29 paginiManejo Técnico de PacoNelson Roger Saire Choquenaira100% (3)

- 08 - Operación Cargador FrontalDocument5 pagini08 - Operación Cargador Frontalesteban leytonÎncă nu există evaluări

- Arquitectura de Las ComputadorasDocument14 paginiArquitectura de Las ComputadorasOliver Atom0% (1)

- UF0853 - Explotación de las funcionalidades del sistema microinformáticoDe la EverandUF0853 - Explotación de las funcionalidades del sistema microinformáticoÎncă nu există evaluări

- Mapa Conceptual de Arquitectura de Moldelo de Von Neumann.Document1 paginăMapa Conceptual de Arquitectura de Moldelo de Von Neumann.yuridia100% (3)

- AA - Vv. - El Materialismo Histórico Según Los Grandes Marxistas (Ocr) (1973)Document155 paginiAA - Vv. - El Materialismo Histórico Según Los Grandes Marxistas (Ocr) (1973)Enrique Lopez100% (1)

- UF1275 - Selección, instalación, configuración y administración de los servidores de transferencia de archivosDe la EverandUF1275 - Selección, instalación, configuración y administración de los servidores de transferencia de archivosÎncă nu există evaluări

- UF0852 - Instalación y actualización de sistemas operativosDe la EverandUF0852 - Instalación y actualización de sistemas operativosEvaluare: 5 din 5 stele5/5 (1)

- La Arquitectura de Von NeumannDocument19 paginiLa Arquitectura de Von NeumannOmar Saavedra PeaÎncă nu există evaluări

- Criterio de Estabilildad NyquistDocument15 paginiCriterio de Estabilildad NyquistDerlis Romero100% (6)

- Desarrollo de componentes software para el manejo de dispositivos. IFCT0609De la EverandDesarrollo de componentes software para el manejo de dispositivos. IFCT0609Încă nu există evaluări

- Cotizacion ByvDocument6 paginiCotizacion ByvJorge Luis Adrián Estrada0% (1)

- Benitez Rojo La Isla Que Se Repite PDFDocument401 paginiBenitez Rojo La Isla Que Se Repite PDFPaola Lizana Miranda100% (1)

- Arquitectura de Los MicrocontroladoresDocument15 paginiArquitectura de Los MicrocontroladoresJoel RinconÎncă nu există evaluări

- Arquitectura Von Neumann y Arquitectura HarvardDocument3 paginiArquitectura Von Neumann y Arquitectura HarvardJuan RuizÎncă nu există evaluări

- Arquitectura Von Neumann y Arquitectura HarvardDocument3 paginiArquitectura Von Neumann y Arquitectura HarvardCesarBeltran100% (1)

- Arquitectura ComputadoraDocument4 paginiArquitectura ComputadoraEthiel Morales CÎncă nu există evaluări

- Arquitectura de Las ComputadorasDocument5 paginiArquitectura de Las ComputadorasHermes MejíaÎncă nu există evaluări

- Arquitectura de Von NeumannDocument4 paginiArquitectura de Von NeumanncxgarcianÎncă nu există evaluări

- Arquitectura Harvard Ventajas y DesventajasDocument2 paginiArquitectura Harvard Ventajas y DesventajasOsbaldo Taurino GQ100% (1)

- Arquitectura HarvardDocument4 paginiArquitectura HarvardMaria Ruiz LinoÎncă nu există evaluări

- Arquitectura Harvard y Von Neumann PDFDocument2 paginiArquitectura Harvard y Von Neumann PDFLuis AlbertoÎncă nu există evaluări

- Arquitectura Von Neumann y Arquitectura HarvardDocument3 paginiArquitectura Von Neumann y Arquitectura HarvardMerari Davalos PerezÎncă nu există evaluări

- Arquitectura Harvard y Von NeumannDocument2 paginiArquitectura Harvard y Von NeumannEFRAIN SANDOVALÎncă nu există evaluări

- Arquitecturas de MicrocontroladoresDocument19 paginiArquitecturas de MicrocontroladoresStephenakd13Încă nu există evaluări

- Trabajo2 RedesDocument3 paginiTrabajo2 RedesIvan CazorlaÎncă nu există evaluări

- Arquitectura de ComputadorasDocument8 paginiArquitectura de ComputadorasSorel TorresÎncă nu există evaluări

- Evidencia #1Document7 paginiEvidencia #1Berenice KztroÎncă nu există evaluări

- Arquitectura Von Neumann y Arquitectura Harvard UltimaDocument5 paginiArquitectura Von Neumann y Arquitectura Harvard UltimaDuivan Andree Mata JaureguiÎncă nu există evaluări

- Actividad 3.1 Arquitecturas Von Neumman y HarvardDocument4 paginiActividad 3.1 Arquitecturas Von Neumman y HarvarddiegoÎncă nu există evaluări

- Tipos de Memoria y Arquitectura de Von Neuman Vs HarvardDocument10 paginiTipos de Memoria y Arquitectura de Von Neuman Vs Harvardviviam pal,maÎncă nu există evaluări

- Modelo de Arquitectura Von NeumannDocument8 paginiModelo de Arquitectura Von NeumannChristopherTrujilloÎncă nu există evaluări

- Actividad 3.1 Arquitecturas Von Neumman y HarvardDocument5 paginiActividad 3.1 Arquitecturas Von Neumman y HarvarddiegoÎncă nu există evaluări

- Arquitecturas Von Neumann & HarvardDocument1 paginăArquitecturas Von Neumann & HarvardCarlos Alberto HernándezÎncă nu există evaluări

- Taller # 2 Organización de ComputadorasDocument7 paginiTaller # 2 Organización de Computadorascarlos javier alcala orozcoÎncă nu există evaluări

- (Anon-12) Arquitectura Von Neumann y Arquitectura Harvard - Computo IntegradoDocument4 pagini(Anon-12) Arquitectura Von Neumann y Arquitectura Harvard - Computo IntegradoSERGIOÎncă nu există evaluări

- La Arquitectura Von NeumannDocument2 paginiLa Arquitectura Von NeumannRonald DelgadoÎncă nu există evaluări

- Arquitectura Von Neumann Vs Arquitectura HarvardDocument4 paginiArquitectura Von Neumann Vs Arquitectura HarvardImaa DuarteÎncă nu există evaluări

- Comparación Entre Microcontroladores y MicroprocesadoresDocument7 paginiComparación Entre Microcontroladores y MicroprocesadorespabloÎncă nu există evaluări

- Arquitectura Basica de Un Sistema Minimo de ComutadoraDocument23 paginiArquitectura Basica de Un Sistema Minimo de ComutadoralinchmxÎncă nu există evaluări

- La Arquitectura de Von NeumannDocument4 paginiLa Arquitectura de Von NeumannwilkinsÎncă nu există evaluări

- TAREA 4 Microprocesadores EsimezacDocument4 paginiTAREA 4 Microprocesadores EsimezacRelck QuijadaÎncă nu există evaluări

- Arquitectura de HarvardDocument9 paginiArquitectura de HarvardManuel Villarroel100% (1)

- Tabla Comparativa Entre MicrocontroladoresDocument9 paginiTabla Comparativa Entre MicrocontroladoresArcelia Garcia100% (1)

- Arquitectura Harvard y Von NeumannDocument6 paginiArquitectura Harvard y Von NeumannAngel VelayÎncă nu există evaluări

- MicrocontroladoresDocument16 paginiMicrocontroladoresVicktor RedÎncă nu există evaluări

- Arquitectura de Computadoras y Modelos de ArquitecturasDocument15 paginiArquitectura de Computadoras y Modelos de ArquitecturasPabloGomezPerezÎncă nu există evaluări

- Taller Nº2 OrganizacionDocument12 paginiTaller Nº2 OrganizacionMartinezMelloÎncă nu există evaluări

- La Acquitecuta de Los Micro ControladoresDocument7 paginiLa Acquitecuta de Los Micro Controladoresosvaldo De la garzaÎncă nu există evaluări

- Arquitectura Von NeumannDocument5 paginiArquitectura Von NeumannYEIMY MARIBEL CAC OSORIOÎncă nu există evaluări

- Manual de Microcontroladores PICDocument68 paginiManual de Microcontroladores PICabraham-tellez-5555Încă nu există evaluări

- PipelinesDocument8 paginiPipelinesAndre FernándezÎncă nu există evaluări

- Montaje y Mantenimiento 1º EjerciciosDocument3 paginiMontaje y Mantenimiento 1º EjerciciosChristian46RMÎncă nu există evaluări

- Tipos de ArquitecturasDocument5 paginiTipos de ArquitecturasLiz Montes de OcaÎncă nu există evaluări

- MODELO Von NeumannDocument13 paginiMODELO Von Neumannalbertoolivas936100% (1)

- ChippptDocument11 paginiChippptTaniaÎncă nu există evaluări

- Arquitectura HarvardDocument7 paginiArquitectura HarvardLuisÎncă nu există evaluări

- Desarrollo y optimización de componentes software para tareas administrativas de sistemas. IFCT0609De la EverandDesarrollo y optimización de componentes software para tareas administrativas de sistemas. IFCT0609Încă nu există evaluări

- Computación Física: Explorando la visión por computadora en la computación físicaDe la EverandComputación Física: Explorando la visión por computadora en la computación físicaÎncă nu există evaluări

- Valores y AntivaloresDocument2 paginiValores y AntivaloresJunior Javier CastilloÎncă nu există evaluări

- Taller 3-Cálculo de Varias Variables G2 PDFDocument2 paginiTaller 3-Cálculo de Varias Variables G2 PDFYanitza Camila Macias CendalesÎncă nu există evaluări

- Ficha 10 - 3ero - Unid. 3Document2 paginiFicha 10 - 3ero - Unid. 3Danfer Fabian Delgado Herrera100% (1)

- Textos Argumentativos POWERDocument11 paginiTextos Argumentativos POWERShirley EstefaniÎncă nu există evaluări

- Resumen - Norma Iso 14001Document4 paginiResumen - Norma Iso 14001Marcela FragozoÎncă nu există evaluări

- Modelo de Conduccion Estrategica (32 Hojas)Document32 paginiModelo de Conduccion Estrategica (32 Hojas)Marcelo Arenas100% (1)

- Guia Semana 5Document4 paginiGuia Semana 5Marleth Lechuga SierraÎncă nu există evaluări

- Taller - Investigacion Regimen Tributario EspecialDocument11 paginiTaller - Investigacion Regimen Tributario EspecialSebas V. Uribe ツÎncă nu există evaluări

- Frederick William Lanchester ..Document10 paginiFrederick William Lanchester ..Angely GuerraÎncă nu există evaluări

- Taller - Multivariado FinalDocument11 paginiTaller - Multivariado FinalRoberto Sanchez FigueroaÎncă nu există evaluări

- Historia Del Microsoft Power PointDocument9 paginiHistoria Del Microsoft Power PointHector Rolando CastroÎncă nu există evaluări

- Tutorial de Análisis FinancieroDocument72 paginiTutorial de Análisis FinancieroLioVasni VegaÎncă nu există evaluări

- Teorias Democraticas ParticipativasDocument44 paginiTeorias Democraticas ParticipativasUlisses AlvesÎncă nu există evaluări

- Resumen Primer Parcial Neurofisiologia Iorio 2016Document35 paginiResumen Primer Parcial Neurofisiologia Iorio 2016Azul AlbertolliÎncă nu există evaluări

- Tarea 7Document3 paginiTarea 7Osiris Martínez OlmosÎncă nu există evaluări

- Monografia Minaya Montes Perez SandovalDocument37 paginiMonografia Minaya Montes Perez Sandovalkhonny montes quitoÎncă nu există evaluări

- Realismo en ItaliaDocument1 paginăRealismo en ItaliaEsme MayaÎncă nu există evaluări

- Informe de IsomeriaDocument2 paginiInforme de IsomeriaALVARO marcanoÎncă nu există evaluări

- Proyectual CBC UNA 1 ICP2.FEDERICORUIZ.221.OLGA-PABLO.B2L8Document1 paginăProyectual CBC UNA 1 ICP2.FEDERICORUIZ.221.OLGA-PABLO.B2L8Federico RuizÎncă nu există evaluări

- Proyecto de Ley 241 de 2011Document9 paginiProyecto de Ley 241 de 2011yoinerlpÎncă nu există evaluări

- Cii-Pr-Pc1-0007-Procedimiento de Colocación, Vibrado y Curado Del ConcretoDocument17 paginiCii-Pr-Pc1-0007-Procedimiento de Colocación, Vibrado y Curado Del ConcretoNoelia Marian Cruz AlemanÎncă nu există evaluări

- Espinoza Medina PDFDocument3 paginiEspinoza Medina PDFRivaldo EMÎncă nu există evaluări