Documente Academic

Documente Profesional

Documente Cultură

BPSK Supressed Carrier NRZ Data Demodulation Using Costas Loop On Actel Microsemi FPGA

Încărcat de

Prabhpreet Singh DuaDescriere originală:

Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

BPSK Supressed Carrier NRZ Data Demodulation Using Costas Loop On Actel Microsemi FPGA

Încărcat de

Prabhpreet Singh DuaDrepturi de autor:

Formate disponibile

Introduction

Objectives

Implementation of Costas Loop

Summary

BPSK Supressed Carrier NRZ Data Demodulation

using Costas Loop on Actel Microsemi FPGA

IP Seminar

Prabhpreet Singh Dua

June 21, 2016

Introduction

Objectives

Implementation of Costas Loop

Outline

1

Introduction

BPSK and NRZ

BPSK Supressed Carrier

BPSK Demodulator

Symbol Synchronization

FPGAs

Objectives

Implementation of Costas Loop

Clock

Costas Loop Components

Results

Summary

Introduction

Objectives

Implementation of Costas Loop

Outline

1

Introduction

BPSK and NRZ

BPSK Supressed Carrier

BPSK Demodulator

Symbol Synchronization

FPGAs

Objectives

Implementation of Costas Loop

Clock

Costas Loop Components

Results

Summary

Introduction

Objectives

Implementation of Costas Loop

BPSK and NRZ

PSK: Phase Shift Keying

sin(0 t + )

Encode data in

BPSK: Binary phase shift keying

=

= m(t)sin(0 t), m(t) = 1

NRZ: Non Return to Zero

Data encoding technique

0 A, 1 +A

Summary

Introduction

Objectives

Implementation of Costas Loop

Outline

1

Introduction

BPSK and NRZ

BPSK Supressed Carrier

BPSK Demodulator

Symbol Synchronization

FPGAs

Objectives

Implementation of Costas Loop

Clock

Costas Loop Components

Results

Summary

Introduction

Objectives

Implementation of Costas Loop

Summary

BPSK and Coherent Demodulation

Need synchronized carrier for demodulation!

m(t)sin(0 t)

m(t)

LPF

sin(0 t)

Data: m(t) = 1 , Carrier Frequency: 0

Introduction

Objectives

Implementation of Costas Loop

Summary

Residual Carrier

Transmit a residual carrier and use a phase lock loop with narrow

loop bandwidth to obtain reference carrier:

y (t) = 2Psin(0 t + m m(t))

= 2Pcos(m )sin(0 t) + 2Psin(m m(t))cos(0 t)

|

{z

} |

{z

}

ResidualCarrier

Data

Vary power of residual carrier and data through 0 < m < 2 .

Problems:

Data power interferes with residual carrier SNR.

Carrier power could be used towards transmitting data

Introduction

Objectives

Implementation of Costas Loop

Summary

PLL

sin(0 t)

cos(0 t + )

sin(0 t)

cos(0 t + )

1

2 sin()

LPF

Loop Filter

Feedback

z}|{

cos(0 t + )

VCO

Introduction

Objectives

Implementation of Costas Loop

Problems in residual carrier method

Problems:

Data power interferes with residual carrier SNR.

Carrier power could be used towards transmitting data

Summary

Introduction

Objectives

Implementation of Costas Loop

Summary

Supressed Carrier

Use all power for transmitting data.

y (t) = 2Pm(t)sin(0 t)

Problem: PLL needs a carrier reference to track!

Solution: Use Costas Loop which can reconstruct carrier reference

for tracking (a special kind of PLL).

Introduction

Objectives

Implementation of Costas Loop

Summary

Costas Loop

1

m(t) {cos()

2

1

m(t)cos()

2

cos(20 t + )}

LPF

sin(0 t + )

m(t)sin(0 t)

1 2

m (t)sin(2)

8

VCO

Loop Filter

=

cos(0 t + )

1

sin(2)

8

LPF

1

m(t) {sin()

2

+ sin(20 t + )}

1

m(t)sin()

2

Introduction

Objectives

Implementation of Costas Loop

Outline

1

Introduction

BPSK and NRZ

BPSK Supressed Carrier

BPSK Demodulator

Symbol Synchronization

FPGAs

Objectives

Implementation of Costas Loop

Clock

Costas Loop Components

Results

Summary

Introduction

Objectives

Implementation of Costas Loop

Summary

Costas Loop as BPSK Demodulator

In-phase arm of Costas Loop can be used to demodulate BSPK

when loop is locked, i.e. = 0!

1

m(t) {cos(0)

2

1

2 m(t)

cos(20 t)}

LPF

sin(0 t)

m(t)sin(0 t)

VCO

Loop Filter

cos(0 t)

LPF

1

m(t) {sin(0)

2

+ sin(20 t)}

Introduction

Objectives

Implementation of Costas Loop

Outline

1

Introduction

BPSK and NRZ

BPSK Supressed Carrier

BPSK Demodulator

Symbol Synchronization

FPGAs

Objectives

Implementation of Costas Loop

Clock

Costas Loop Components

Results

Summary

Introduction

Objectives

Implementation of Costas Loop

Clock Extraction

Provide a clock reference in sync with data.

Different methods

Open loop synchronizers

Closed loop (feedback) synchronizers

Summary

Introduction

Objectives

Implementation of Costas Loop

Outline

1

Introduction

BPSK and NRZ

BPSK Supressed Carrier

BPSK Demodulator

Symbol Synchronization

FPGAs

Objectives

Implementation of Costas Loop

Clock

Costas Loop Components

Results

Summary

Introduction

Objectives

Implementation of Costas Loop

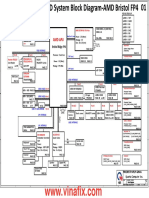

FPGAs

Flexible digital circuits

Comprised of logic blocks and routing channels

Actel FPGAs: Use fuses instead of SRAM to avoid EM

interference

Programmed using VHDL/Verilog and synthesis tools

Figure: Structure of Actel FPGAs

Summary

Introduction

Objectives

Implementation of Costas Loop

Summary

Objectives

Primary Objective

To implement supressed carrier BPSK demodulation using a Type

II Costas Loop on a Microsemi Actel FPGA (Field Programmable

Array) for 8-16KHz carrier signal and data rate of 2-4 kbps.

Introduction

Objectives

Implementation of Costas Loop

Summary

Objectives

Secondary Objectives

The secondary outcomes are the following features in the Costas

Loop:

Subcarrier lock: To indicate subcarrier lock has been achieved

Clock and bit sync lock: A clock in sync with the demod data

of 50 % duty cycle, and a bit sync lock indication to indicate

synchronization between your data and clock outputs (The

clock should be such that after initial sync, even if continuous

0s or 1s are given for 40 bits and then alternate 0 and 1s are

restored, the clock should not loose sync.)

Infinite Impulse Response filter implementation (aside from

use of FIR filters)

Introduction

Objectives

Implementation of Costas Loop

Outline

1

Introduction

BPSK and NRZ

BPSK Supressed Carrier

BPSK Demodulator

Symbol Synchronization

FPGAs

Objectives

Implementation of Costas Loop

Clock

Costas Loop Components

Results

Summary

Introduction

Objectives

Implementation of Costas Loop

Summary

Clock

Clock Speed is variable in the requirements.

Therefore, minimum clock speed depends on the highest frequency

being used in the loop (64KHz) into 2.

Minimum clock speed: 128KHz.

We are using 256KHz.

Introduction

Objectives

Implementation of Costas Loop

Outline

1

Introduction

BPSK and NRZ

BPSK Supressed Carrier

BPSK Demodulator

Symbol Synchronization

FPGAs

Objectives

Implementation of Costas Loop

Clock

Costas Loop Components

Results

Summary

Introduction

Objectives

Implementation of Costas Loop

Costas Loop Components

NCO (Digital equivalent of VCO)

Multiplier

Arm filters (Can be FIR, IIR)

Loop filter design (IIR)

Summary

Introduction

Objectives

Implementation of Costas Loop

NCO

Implementation: N=6, M=8, P=5

Summary

Introduction

Objectives

Implementation of Costas Loop

NCO VHDL Testbench Simulation

Summary

Introduction

Objectives

Implementation of Costas Loop

Summary

Arm Filters

Low pass filters to remove the component of 20 .

Implemented using 10th Order Least Squares Method Optimization

FIR

order = 10;

Fpass = 6000;

Fstop = 8000;

Wpass = 1;

Wstop = 0.05;

arm coeffs = firls(order, [0 Fpass Fstop f sampling/2]/

(f sampling/2), [1 1 0 0], [Wpass Wstop]);

Coefficients are Q1.17 fixed point.

Introduction

Objectives

Implementation of Costas Loop

Summary

Arm Filters

Used MATLABs filter design toolbox to visualize filters and

created a class for simulating FIR filter fixed point implementation.

Introduction

Objectives

Implementation of Costas Loop

Summary

Linearized model of a PLL/Costas Loop

(t)

Loop Filter

VCO

F (s)

1

s

Transfer function

F (s)

s

(s)

F (s)

H(s) =

=

(s)

s + F (s)

G (s) =

(t)

Introduction

Objectives

Implementation of Costas Loop

Summary

Transfer function type

Type of transfer function: Important parameter in describing

PLL

From Control Theory: Number of poles at zero (integrators)

in a unit negative feedbacks transfer function (G (s)).

Type II can acquire (zero steady state error) unit step and

unit ramp response, can track (finite steady state error) unit

acceleration functions.

In terms of phase, it means it can exactly replicate carriers

phase and frequency but can only track steady change in

frequency in the carrier (due to Doppler effects).

Introduction

Objectives

Implementation of Costas Loop

PI Loop Filter

Loop filter: Proportional + Integral Controller

s

s +

= G (s) =

s2

F (s) = +

Two poles at zero = Type 2 system

Converted to z-domain using bilinear transform

s=

where T is sampling time.

2 1 z 1

T 1 + z 1

Summary

Introduction

Objectives

Implementation of Costas Loop

Outline

1

Introduction

BPSK and NRZ

BPSK Supressed Carrier

BPSK Demodulator

Symbol Synchronization

FPGAs

Objectives

Implementation of Costas Loop

Clock

Costas Loop Components

Results

Summary

Introduction

Objectives

MATLAB Simulation

Implementation of Costas Loop

Summary

Introduction

Objectives

Implementation of Costas Loop

Summary

Summary

Accomplished: Costas Loop Pre-Synthesis Simulation finished

Next TODO

Subcarrier Lock Indication

Clock Extraction

S-ar putea să vă placă și

- First Year Syllabus DsceDocument60 paginiFirst Year Syllabus Dscetheju100% (2)

- HP G94aDocument48 paginiHP G94aJhon Kelvin GerónimoÎncă nu există evaluări

- Root Raised Cosine Filter and Pulse ShapingDocument30 paginiRoot Raised Cosine Filter and Pulse ShapingphithucÎncă nu există evaluări

- Communication Lab Manual EL394 PDFDocument26 paginiCommunication Lab Manual EL394 PDFKhan Shahrukh AshrafÎncă nu există evaluări

- MIASOLÉ - MR-107 (108 W) : The Advantages at A GlanceDocument4 paginiMIASOLÉ - MR-107 (108 W) : The Advantages at A GlancePower EngÎncă nu există evaluări

- Automatic Door Opener Using Motion SensorDocument9 paginiAutomatic Door Opener Using Motion SensorHussain Lagua0% (1)

- Silicon - Controlled Rectifiers: Group MembersDocument13 paginiSilicon - Controlled Rectifiers: Group MembersMartin John Ramirez100% (1)

- Design and Implementation of Early-Late Gate Bit Synchronizer For Satellite CommunicationDocument4 paginiDesign and Implementation of Early-Late Gate Bit Synchronizer For Satellite CommunicationMatthew CarterÎncă nu există evaluări

- 802 16d PHY SimuLinkDocument24 pagini802 16d PHY SimuLinkDevilhart KrisÎncă nu există evaluări

- Question Bank: Subject Code: Subject NameDocument5 paginiQuestion Bank: Subject Code: Subject NamemsurendiranÎncă nu există evaluări

- CDMA Baseband Processing On A TMS320C54x DSPDocument11 paginiCDMA Baseband Processing On A TMS320C54x DSPsampath5211Încă nu există evaluări

- Digital Signal Processing For Deep Space TransponderDocument6 paginiDigital Signal Processing For Deep Space TransponderSatish KapalavayiÎncă nu există evaluări

- RAKE Receiver: Wireless Information Transmission System LabDocument62 paginiRAKE Receiver: Wireless Information Transmission System Labmitso123Încă nu există evaluări

- Clock and Data Recovery For Serial Digital CommunicationDocument79 paginiClock and Data Recovery For Serial Digital Communicationquail36Încă nu există evaluări

- Digital Signal Processing Question BankDocument4 paginiDigital Signal Processing Question BanksharlisreeÎncă nu există evaluări

- Chapter 9: Synchronization: Shanghai Jiao Tong University 11.2011Document57 paginiChapter 9: Synchronization: Shanghai Jiao Tong University 11.2011Shi SunÎncă nu există evaluări

- RC LDPC Dec OpexDocument7 paginiRC LDPC Dec OpexAyodele Emmanuel SonugaÎncă nu există evaluări

- QPSKDocument12 paginiQPSKATUL SACHAN100% (1)

- Synchronization in IEEE 802.15.4 Zigbee Transceiver Using Matlab SimulinkDocument5 paginiSynchronization in IEEE 802.15.4 Zigbee Transceiver Using Matlab SimulinktesteÎncă nu există evaluări

- Chapter 3 QuestionsDocument2 paginiChapter 3 Questionssmatuszak97Încă nu există evaluări

- 15EC306J Cycle 2 ExptsDocument28 pagini15EC306J Cycle 2 ExptsSanjeev KumarÎncă nu există evaluări

- Semiconductor Application Note: Prepared By: Garth Nash Applications EngineeringDocument12 paginiSemiconductor Application Note: Prepared By: Garth Nash Applications EngineeringefddfdsdsaÎncă nu există evaluări

- GNSS - SDR Receivers: A-The Signal in Space (SIS)Document50 paginiGNSS - SDR Receivers: A-The Signal in Space (SIS)dangkitaÎncă nu există evaluări

- Chapter 6 Speed Independent Control CircuitsDocument90 paginiChapter 6 Speed Independent Control CircuitsemailparacadastroÎncă nu există evaluări

- Telecom - Exp - 10 - QAM, MSK, & GMSKDocument15 paginiTelecom - Exp - 10 - QAM, MSK, & GMSKrakibÎncă nu există evaluări

- Implementation of Digital QPSK Modulator by Using VHDL / MatlabDocument5 paginiImplementation of Digital QPSK Modulator by Using VHDL / Matlabblesson123Încă nu există evaluări

- DC - Experiment - No. 5Document8 paginiDC - Experiment - No. 5amol maliÎncă nu există evaluări

- SDH OverviewDocument26 paginiSDH OverviewKavish Jaggi100% (1)

- Digital Signal ProcessingDocument7 paginiDigital Signal ProcessingAhsan MalikÎncă nu există evaluări

- Design and Implementation of Early-Late Gate Bit Synchronizer For Satellite CommunicationDocument4 paginiDesign and Implementation of Early-Late Gate Bit Synchronizer For Satellite CommunicationdabajiÎncă nu există evaluări

- 5g Ug PDFDocument26 pagini5g Ug PDFypobuleshÎncă nu există evaluări

- Phase Locked Loop Design FundamentalsDocument22 paginiPhase Locked Loop Design Fundamentalsptt3iÎncă nu există evaluări

- Kiings DSPDocument4 paginiKiings DSPkar07indiaÎncă nu există evaluări

- Performance Evaluation of A 3GPP LTE Terminal Receiver: Konstantinos Manolakis, Andreas Ibing, Volker JungnickelDocument5 paginiPerformance Evaluation of A 3GPP LTE Terminal Receiver: Konstantinos Manolakis, Andreas Ibing, Volker Jungnickelhanochk12Încă nu există evaluări

- Lab 5: Digital Phase Locked Loop (PLL) : Matlab Part: ObjectiveDocument11 paginiLab 5: Digital Phase Locked Loop (PLL) : Matlab Part: ObjectiveThế Anh NguyễnÎncă nu există evaluări

- TCOM513 Lecture5Document100 paginiTCOM513 Lecture5Pranveer Singh PariharÎncă nu există evaluări

- OFDM For Optical CommunicationsDocument41 paginiOFDM For Optical CommunicationsPrasanna Kumar100% (1)

- OFDM & Cyclic PrefixDocument37 paginiOFDM & Cyclic PrefixRani KumariÎncă nu există evaluări

- DSP Manual - 2017 VTU 2015 Cbcs SchemeDocument99 paginiDSP Manual - 2017 VTU 2015 Cbcs SchemeNikhil Miranda100% (1)

- Low-Power, High-Speed FFT Processor For MB-OFDM UWB ApplicationDocument10 paginiLow-Power, High-Speed FFT Processor For MB-OFDM UWB ApplicationPhuc HoangÎncă nu există evaluări

- PSK Demodulation (Part 1)Document10 paginiPSK Demodulation (Part 1)particlereddyÎncă nu există evaluări

- Ofc Lab Manual 2Document21 paginiOfc Lab Manual 2Shobhit JainÎncă nu există evaluări

- Bandpass Modulation Schemes Bandpass Modulation Schemes For Wireless SystemsDocument15 paginiBandpass Modulation Schemes Bandpass Modulation Schemes For Wireless SystemsTina BurgessÎncă nu există evaluări

- Performance of COFDM Using Turbo Codes: Primary Technical Subject Area: Radio CommunicationDocument11 paginiPerformance of COFDM Using Turbo Codes: Primary Technical Subject Area: Radio Communicationmsachemo1Încă nu există evaluări

- Instituto Superior Técnico: 2 Semester 2012/2013Document5 paginiInstituto Superior Técnico: 2 Semester 2012/2013Milupa7Încă nu există evaluări

- Implementation of DSP Algorithms On Fixed Point DSP ProcessorsDocument13 paginiImplementation of DSP Algorithms On Fixed Point DSP ProcessorsNikhil PanikkarÎncă nu există evaluări

- DVD2 JNTU Set1 SolutionsDocument12 paginiDVD2 JNTU Set1 Solutionsకిరణ్ కుమార్ పగడాలÎncă nu există evaluări

- Analog FFT Interface For Ultra-Low Power Analog Receiver ArchitecturesDocument4 paginiAnalog FFT Interface For Ultra-Low Power Analog Receiver ArchitecturesNathan ImigÎncă nu există evaluări

- Kings: Department of Electronics and Communication EngineeringDocument5 paginiKings: Department of Electronics and Communication EngineeringA RahmanÎncă nu există evaluări

- OFDMDocument5 paginiOFDMUsama JavedÎncă nu există evaluări

- VLSI & ASIC Digital Design Interview QuestionsDocument6 paginiVLSI & ASIC Digital Design Interview QuestionsRupesh Kumar DuttaÎncă nu există evaluări

- Anna University Digital Signal Processing Question BankDocument6 paginiAnna University Digital Signal Processing Question Banks.ranjithÎncă nu există evaluări

- EE 230 - Analog Circuits Lab - 2021-22/I (Autumn) Experiment 1: Familiarization With NGSPICE Circuit Simulator and Lab EquipmentDocument7 paginiEE 230 - Analog Circuits Lab - 2021-22/I (Autumn) Experiment 1: Familiarization With NGSPICE Circuit Simulator and Lab EquipmentTanmay JainÎncă nu există evaluări

- Final Exam: ECE 697 Delta-Sigma Data Converter Design (Spring 2010) Due On Thursday, May 15, 2010Document5 paginiFinal Exam: ECE 697 Delta-Sigma Data Converter Design (Spring 2010) Due On Thursday, May 15, 2010anjugaduÎncă nu există evaluări

- Chapter 5 Introduction To Digital Data Transmission PDFDocument66 paginiChapter 5 Introduction To Digital Data Transmission PDFJoel TibebuÎncă nu există evaluări

- OFDMDocument15 paginiOFDMAvinash RaghooÎncă nu există evaluări

- Mapping DSP Algorithms Into FpgasDocument35 paginiMapping DSP Algorithms Into FpgasMayam AyoÎncă nu există evaluări

- Elec9123 DSP DesignDocument7 paginiElec9123 DSP DesignSydney FinestÎncă nu există evaluări

- AN535 Phase Lock Loop Design FundamentalsDocument13 paginiAN535 Phase Lock Loop Design FundamentalsfahkingmoronÎncă nu există evaluări

- Nanomap: An Integrated Design Optimization Flow For A Hybrid Nanotube/Cmos Dynamically Reconfigurable ArchitectureDocument27 paginiNanomap: An Integrated Design Optimization Flow For A Hybrid Nanotube/Cmos Dynamically Reconfigurable Architectureசக்தி இலக்கியா சத்தீஸ்வரன்Încă nu există evaluări

- Wemmu 001Document4 paginiWemmu 001shastryÎncă nu există evaluări

- Digital Signal Processing: Instant AccessDe la EverandDigital Signal Processing: Instant AccessEvaluare: 3.5 din 5 stele3.5/5 (2)

- LTE Signaling: Troubleshooting and Performance MeasurementDe la EverandLTE Signaling: Troubleshooting and Performance MeasurementÎncă nu există evaluări

- ABB TransformersDocument8 paginiABB TransformersElias100% (2)

- Investigation Into IGBT DVDT During Turn-Off and Its Temperature DependenceDocument13 paginiInvestigation Into IGBT DVDT During Turn-Off and Its Temperature DependenceOsman T.Încă nu există evaluări

- Grid Converters: System ArchitectureDocument15 paginiGrid Converters: System Architecturedigital2000Încă nu există evaluări

- 89C51Document15 pagini89C51Bhasker GurramÎncă nu există evaluări

- HC4538ADocument14 paginiHC4538AnatanaelÎncă nu există evaluări

- Transparent ElectronicsDocument14 paginiTransparent ElectronicsgopiraamÎncă nu există evaluări

- Solar CellDocument25 paginiSolar CellfebriÎncă nu există evaluări

- eLMS - Activity - Week - 5 (Gen Phy) - RelevoDocument2 paginieLMS - Activity - Week - 5 (Gen Phy) - Relevocessarine relevoÎncă nu există evaluări

- Comparative Study of Single-Phase Power Factor Correction Topologies For Electric Vehicle Battery Charger Based On Boost ConverterDocument5 paginiComparative Study of Single-Phase Power Factor Correction Topologies For Electric Vehicle Battery Charger Based On Boost ConverterPrasin PradeepÎncă nu există evaluări

- Nokia Smart Radio Concept For EDGEDocument3 paginiNokia Smart Radio Concept For EDGEkrafael2Încă nu există evaluări

- Biasing: Unit - Ii Transistor Biasing Circuits Ans Small Signal Analysis of BJT Amplifiers 9 HrsDocument19 paginiBiasing: Unit - Ii Transistor Biasing Circuits Ans Small Signal Analysis of BJT Amplifiers 9 HrsGoran WnisÎncă nu există evaluări

- Met 2Document225 paginiMet 2Pranav kant100% (1)

- Automotive Digital Clock Ic: DescriptionDocument7 paginiAutomotive Digital Clock Ic: DescriptionppanagosÎncă nu există evaluări

- Modern Physics - Chapter 25Document83 paginiModern Physics - Chapter 25Hamza PagaÎncă nu există evaluări

- Semiconductor 2N3904: Technical DataDocument4 paginiSemiconductor 2N3904: Technical Datanamartinez26Încă nu există evaluări

- ITC - Power Factor CorrectionDocument92 paginiITC - Power Factor Correctiongopir28Încă nu există evaluări

- ME3281 Term PaperDocument11 paginiME3281 Term PaperEdmund ChongÎncă nu există evaluări

- Solutions For Metrology: EV GROUP® - Products MetrologyDocument6 paginiSolutions For Metrology: EV GROUP® - Products MetrologyvinayakpandeyÎncă nu există evaluări

- Module 3Document68 paginiModule 3Royston LimÎncă nu există evaluări

- Blm18ag102sn1 Ferrite Rs485Document3 paginiBlm18ag102sn1 Ferrite Rs485onafetsÎncă nu există evaluări

- Tle 92464 EdDocument117 paginiTle 92464 EdcqlÎncă nu există evaluări

- AVR Session 1 PDFDocument44 paginiAVR Session 1 PDFKirito SoloÎncă nu există evaluări

- M140 DatasheetDocument10 paginiM140 DatasheetBozo ThaClownÎncă nu există evaluări

- Photocatalytic Decolorization of Bismarck Brown RDocument170 paginiPhotocatalytic Decolorization of Bismarck Brown Rgeorge.ejaam8975Încă nu există evaluări