Documente Academic

Documente Profesional

Documente Cultură

Lab VH Dle Strut

Încărcat de

Rodrigo FerronatoTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Lab VH Dle Strut

Încărcat de

Rodrigo FerronatoDrepturi de autor:

Formate disponibile

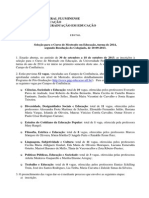

UFPR Bacharelado em Cincia da Computao

26 de agosto de 2016

CI210 Projetos Digitais e Microprocessadores

Laboratrio sobre Modelagem de Circuitos Combinacionais em VHDL 2016-2

1

1.1

Modelagem de Circuitos Combinacionais em VHDL

Objetivos

So dois os objetivos deste laboratrio: (i) efetuar a modelagem estrutural em

VHDL de multiplexadores, demultiplexadores e decodificadores; e (ii) verificar, atravs de simulao, a corretude dos modelos daqueles circuitos.

O trabalho pode ser efetuado em duplas.

1.2

Como definir as ligaes de um circuito?

Examine a Figura 1 e liste, de forma sucinta, as convenes empregadas para que

ele possa ser interpretado por discentes matriculados nesta disciplina. DeMorgan

a

s

r

r

p p p p p pp p p

ppp ppp p

pp .

pp pppp ......... pppp pppppppp

p

p

p

p

ppppppppp

p

p p pp

..

pppp

pp

pp

p

p p p p p pp p p

ppp

p p pp

ppppppp ....... ppppppp pp pppppppp

p ..

p p pp p

p p p p pp p p p q

p p p p p pp p p

ppppppp r.........

..

pppppp p ..

p p p p p pp pp

Figura 1: Circuito combinacional.

espao em branco proposital

UFPR, BCC, CI2102016-2

Sua

(i)

(ii)

(iii)

(iv)

(v)

lista deve conter, pelo menos:

uma representao para as portas lgicas;

uma representao para as ligaes;

uma representao para as entradas;

uma representao para as sadas; e

uma denominao para as variveis lgicas transportadas pelas ligaes.

At agora temos usado vrias convenes:

portas lgicas tem formatos distintos ( );

multiplexadores e decodificadores so trapzios;

somadores so trapzios com um recorte/chanfro;

registradores so retngulos com tringulo do relgio;

circuitos complexos so caixas retangulares;

ligaes (fios, sinais) so linhas;

sinais fluem da esquerda para a direita;

entradas no lado esquerdo (ou acima);

sadas no lado direito (ou abaixo);

se no bvio, setas indicam o fluxo dos dados; e

um trao curto com um nmero indica largura do sinal, se maior do que 1.

O diagrama na Figura 2 ilustra estas convenes: so quatro os registradores, chamados de r1, r2, r3 e STAT, os sinais fluem da esquerda para a direita, o sinal clock

tem um bit de largura, o sinal oper e a entrada do registrador STAT tem 4 bits de largura, e os demais sinais tem largura de 16 bits. O circuito no centro um somador,

ou uma unidade de lgica e aritmtica, que assunto a ser explorado futuramente.

clock

oper=add

4 ........

... ..

......

..

r1

.

...

16

clock

... ..

......

..

r2

.

...

16

pppppppppppppp..........

pppppppppppppp

ppppppp

...........

.....

A

ppppp

ppppp

p

pp p R

pppp pp p

S

...........

.....

B ppp pppppppppp ppppppp

pppppp ppppppp

clock

... ..

......

..

...

..

...........

.....

16

...

...

...

...

...

... .

. ..

.

r3

clock

...........

.....

STAT

... ..

.....

..

Figura 2: Exemplo das convenes usadas em diagramas de circuitos.

1.3

E se a descrio for textual?

A interpretao automtica de desenhos uma arte, mesmo que os desenhos sejam diagramas to simples como nossos circuitos. Para permitir a interpretao

automtica de representaes para circuitos emprega-se texto.

A representao que usaremos nesta disciplina e adiante no curso codificada na

linguagem VHDL V uma sigla, HDL a abreviatura para Hardware Description

Language grave este nome.

Circuitos so representados em VHDL por sinais (fios) e componentes (design units).

Um componente descrito por duas construes da linguagem, uma entidade que

descreve sua interface com o mundo externo e uma arquitetura que descreve seu

modelo com as construes da linguagem.

UFPR, BCC, CI2102016-2

Uma entidade (entity) descreve as ligaes externas do componente:

(i) entradas so in

(ii) sadas so out

(iii) ligaes so representadas por sinais, no nosso caso bits

ou vetores de bits (bit_vectors).

Uma arquitetura (architecture) descreve as ligaes internas do componente. A

arquitetura declara quais componentes so usados na implementao, que sinais

internos so necessrios para interligar os componentes internos, e de que forma os

componentes so interligados entre si e com os sinais da entidade.

Uma certa entidade pode ser modelada em VHDL de mais de uma forma, como

veremos em breve para uma entidade (interface), podem ser projetadas mais de

uma arquitetura (circuito).

Antes de passarmos a um exemplo, vejamos as convenes de tipografia para o

cdigo VHDL: palavras reservadas so grafadas em negrito (entity), nomes de sinais

e componentes so grafados com largura fixa (meuSinal), e comentrios iniciam com

-- e terminam no final da linha e so grafados com -- caracteres inclinados.

1.3.1

MUX2 entidade e arquitetura

O multiplexador mostrado anteriormente descrito em VHDL pelas suas entidade e

arquitetura. A entidade chamada mux2 descreve a interface deste componente, com

trs sinais de entrada e um de sada, todos com a largura de um bit.

entity mux2 is

port (a , b : in bit ;

s

: in bit ;

z

: out bit );

end mux2 ;

z....

.

.......

p

p pp

ppp p p

pp .

....

.

.......

pppp ...

..p....p

pppp ..1.

ppp

.

....

.

.......

A arquitetura, chamada estrutural define a estrutura do circuito modelado ela descreve como os componentes so interligados. Entre as palavras chave architecture

e begin devem ser declarados os componentes usados na implementao do multiplexador neste caso inversor, porta nand e porta nor e os sinais internos necessrios

para ligar os componentes e a interface, que so os sinais r, p e q.

Entre o begin e o end architecture so definidas as ligaes entre os componentes

da implementao. Como mostra o diagrama ao lado do cdigo, h uma correspondncia direta entre o diagrama e o cdigo VHDL que o representa. Uma chateao

com descries textuais que, ao contrrio dos diagramas, todos os sinais devem

ser explicitamente nomeados.

A construo port map faz a ligao entre os sinais internos arquitetura e os sinais declarados para cada componente individual usado na modelagem. O port map

quem liga sinais em componentes ao mapear os sinais internos declarados na arquitetura, aos sinais declarados nas entidades dos componentes. A instanciao dos

componentes com o mapeamento das portas similar a um operador aritmtico prefixado; ao invs da forma usual, que infixada, mostrada esquerda, emprega-se a

forma prefixada direita:

c=a+b

+ (a, b, c) .

UFPR, BCC, CI2102016-2

O trecho de cdigo abaixo parte do material que lhe ser fornecido nesta aula.

O cdigo est incompleto e serve apenas para mostrar como os componentes do

modelo so interligados. As instrues de como compilar e simular este modelo

esto na Seo 1.6.

architecture estrutural of mux2 is

-- declara o

component inv

port ( A : in

end component

de componentes

is

bit ; S : out bit );

inv ;

component nand2 is

port (A , B : in bit ; S : out bit );

end component nand2 ;

-- declara o de sinais internos

signal r , p , q : bit ;

begin

-- instancia o e

-interliga o dos componentes

Ui : inv port map (s , r );

z...

..

.

.......

ppp

p

p

ppp

pp

p p p p p p p p p p p pp p p

ppp

pp p

pp pp Uor ppppp

ppp

pp p

p pp p p p p p p p p p p p p p p p p p pp p

ppp ..... s

pp 1

pp p p pppp pppp p p

p

p

p

p

p

p

p

p

p

p pp p p

q

pp

p pp p ppppp pppp

p

p

pp p ppp p

pp

pp Ua1 pp pppp

p Ua0

ppp

pppp ppp

....

ppppppppp pppppppppppppp

pp p ....

ppp

p

Ui

p

p

p

p

pp

p

pppppp s

ppp

r

p

p

.

.......

.

.......

Ua0 : nand2 port map (a , r , p );

Ua1 : nand2 port map (b , s , q );

Uor : nand2 port map (p , q , z );

end architecture estrutural ;

Entre architecture e begin, os componentes e os sinais so declarados. Entre o

begin e o end architecture, os sinais e componentes so instanciados e conectados

atravs dos sinais internos e do mapeamento dos sinais nas portas dos entidades com

o port map.

1.4

Projeto topdown

Uma forma de descrever o ciclo de vida do desenvolvimento de um sistema com a

chamada espiral de projeto, mostrada na Figura 3. Tipicamente, o processo se inicia

com uma ideia, e a partir dela escreve-se uma especificao (abstrata) para o sistema.

Esta especificao refinada para um projeto, que essencialmente uma verso mais

detalhada e menos abstrata da especificao. A implementao do projeto resulta

numa verso concreta da especificao, e esta pode ento ser verificada quanto a sua

corretude e avaliada quanto ao seu desempenho. Se a implementao no satisfaz

especificao, deve-se efetuar um novo ciclo da espiral, com repeties at que os

requisitos de projeto estejam atendidos.

Da forma como VHDL ser empregada nesta disciplina, (i) a ideia a especificao

em Portugus de um circuito, (ii) o projeto o primeiro refinamento da especificao, que obtido com trabalho intelectual, lpis e papel; (iii) a implementao a

codificao em VHDL, e (iv) a verificao a confirmao de que a implementao

UFPR, BCC, CI2102016-2

refinamento

projeto . .

.

. . . .. . .

. .

. .

especificao

idia

.

.

.....

.

........

........

.

........

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

........

.

.

.....

......

.

........

.......

.

.....

........

.....

.

....

........

....

........

...

...

.

.........

.

.

...

..

.

.

.

.

.

.

... .................

.

...

.

... .. .

.

...

..

..

.

..

..

.

.

..

.

.

............. ...

..

.

.

.

.

.

.

.

.

.

...

. ............

..

...

.

..

.......

.

.

.

.

.

.

.

.

.

.

...

....... .

.

...

...

.........

...

...

.

.........

...

.

...

........

.....

.

.....

....

.

.

.

.

.

.....

.

.....

......

.

.......

.......

.

........

............

.

.

...................................

.

.

.

.

.

.

.

.

.

.

.

.

.

. .

. .

. . .

. . . . . .

.

abstrato

concreto

codificao

implementao

simulao

verificao

Figura 3: Espiral de projeto.

satisfaz ao especificado, atravs de simulao.

Um projeto pode ser refinado de mais de uma forma, na sua fase inicial, e a cada

refinamento, o resultado mais concreto e prximo da implementao. Por exemplo,

partindo-se de uma especificao (abstrata) do comportamento desejado, esta sofre

um refinamento que resulta num diagramas de blocos, que ao ser refinado produz o

projeto dos blocos, o refinamento dos blocos resulta na formalizao da especificao,

que a modelagem concreta dos componentes do projeto em VHDL cdigo VHDL

para os componentes do projeto.

1.5

VHDL

VHDL uma linguagem extremamente verstil e usada para

a modelagem e simulao de circuitos;

especificao, projeto e sntese de circuitos;

descrever lista de componentes e de ligaes; e

verificao de corretude: se especificao implementao.

A linguagem padronizada pelo IEEE, no padro IEEE 1076-1987 V[HSIC] H D

L, ou Very High Speed Integrated Circuit Hardware Description Language, o padro

IEEE Std 1164 define pacote std_logic, e o padro IEEE Std 1076.3 VHDL Numeric

Standard define uma biblioteca de funes numricas. H mais, muito mais nos bons

textos do ramo.

1.5.1

Como se d a compilao de VHDL?

A compilao de cdigo VHDL se d em trs fases: anlise, elaborao e simulao.

No nosso caso, o resultado da compilao um programa em C gerado automaticamente por ghdl que simula o comportamento do modelo escrito em VHDL. Usaremos gtkwave para verificar o comportamento dos modelos dos circuitos. Detalhes

em seguida.

UFPR, BCC, CI2102016-2

Anlise Na fase de anlise, o compilador VHDL verifica a corretude da sintaxe e

a semntica dos comandos. Na anlise sinttica, so sinalizados erros de grafia das

palavras reservadas, sinais que no foram declarados, etc. Na anlise da semntica,

so verificados os tipos dos sinais, e se os operadores so aplicados a operandos com

os tipos apropriados somar dois nmeros faz sentido, somar dois ifs no.

A anlise pode ser efetuada em partes de um modelo. Por exemplo, um par entidadearquitetura (uma design unit) pode ser analisado em separado, e se nenhum erro

encontrado, o resultado da anlise armazenado na biblioteca work-obj93.cf, para

uso futuro. Esta biblioteca mantida no diretrio em que ocorre a compilao.

Elaborao Na fase de elaborao, o compilador constri um modelo completo de

toda a hierarquia do projeto. Reveja o cdigo da arquitetura do mux2 na pgina 4.

A hierarquia consiste da arquitetura do mux2 e mais as declaraes dos componentes

inv e and2.

O compilador examina a arquitetura de mais alto nvel da hierarquia e expande

todas as declaraes dos componentes instanciados naquela arquitetura. Para cada

componente, o compilador examina sua arquitetura e expande todas as declaraes l

instanciadas. A elaborao termina quando todas as declaraes forem substitudas

por atribuies para ser mais preciso, a elaborao termina quando s restam

processos e os sinais que os interligam. De forma muito simplificada, um processo

uma generalizao para uma atribuio. Voltaremos a falar de processos em outro

laboratrio.

Simulao Ao final da elaborao, o ghdl traduz a estrutura de processos e os

sinais que os interligam para um programa em C, que depois de compilado, permite

simular a execuo do modelo completo. Veja, na Seo 1.5.4, como funciona a

simulao.

A sada da simulao pode ser mostrada na tela, pode ser gravada em arquivos, ou

pode gerar um conjunto de dados que representa um diagrama de tempo, que pode

ser exibido com o programa gtkwave.

Neste laboratrio e nos prximos, o processo de compilao est escondido num

script que lhes ser fornecido juntamente com o cdigo VHDL para verificar os

modelos por estudar.

1.5.2

Tipos de dados

Alguns dos tipos bsicos de dados disponveis em VHDL so mostrados na Tabela 1.

O tipo bit tem dois valores, 0 e 1 note as aspas simples. Um vetor de bits, ou

um bit_vector, representado por mais de um bit, enfeitado com aspas duplas:

"1001". As regras para caracteres (aspas simples) e cadeias (aspas duplas) so

similares quelas para bits e vetores de bits. Constantes booleanas, nmeros inteiros,

nmeros reais e constantes de tempo so representadas sem aspas.

A atribuio a um sinal representada pela flecha dupla <= e a concatenao de

vetores de bits, ou de caracteres, representada pelo &, como mostra o exemplo da

concatenao das cadeias de caracteres.

UFPR, BCC, CI2102016-2

Tipo

Bit

Bit_vector

Boolean

Integer

Real

Time

Character

String

valor

1, 0

vetor de bits

True, False

-2,-1,0,1,1

1.0, -1.0E5

1 us, 7 ns

a,2,$

vetor de char

exemplo de uso

Q <= 1;

Dout <= "0011";

EQ <= True;

Cnt <= Cnt + 2;

V1 = V2/5.3;

Q <= 1 after 6 ns;

Char <= p;

Msg <= "error: " & "badAddr";

Tabela 1: Subconjunto pequeno dos tipos de dados em VHDL.

1.5.3

Sinais e Vetores de Sinais

Os sinais em VHDL correspondem aos fios que transportam os bits no circuito e a

linguagem define sinais de um bit, e vetores de sinais com muitos bits.

O cdigo abaixo declara um sinal x com um bit de largura, e este inicializado em

1. O sinal vb um vetor com 4 bits de largura e a posio de cada um dos bits

aquela em que o bit mais significativo est esquerda, e o menos significativo

direita. Esta a declarao adequada para vetores que representam nmeros.

-- declara o de sinais do tipo bit

signal x : bit := 1 ; -- inicializado em 1

signal vb : bit_vector (3 downto 0) := " 1100 " ; -- inicializ em 12

O sinal bv declarado com a direo contrria quela do sinal vb, e o bit mais

significativo deste vetor aquele na direita.

signal bv : bit_vector (0 to 3); -- bit 0 o Mais Significativo

As atribuies abaixo produzem resultados que talvez no sejam intuitivos a uma

primeira vista.

signal bH : bit_vector (7 downto 0); -- bit 7 Mais Sign .

signal bL : bit_vector (0 to 7);

-- bit 0 Mais Sign .

bH <= b " 11000000 " -- bH se torna 0 xc0 = 192

bL <= b " 11000000 " -- bL se torna 0 x03 = 3

possvel selecionar um subconjunto dos bits de um sinal. Os comandos abaixo

declaram 4 sinais: um com 1 bit, um com 8 bits, e dois sinais com 4 bits de largura.

A primeira atribuio seleciona o bit mais significativo do sinal v8 e o atribui x.

As atribuies v4 e t4 selecionam o quarteto central de v8, e armazenam estes

quartetos na ordem numrica em v4, e na ordem invertida em t4.

signal x : bit ; -- um bit

signal v8 : bit_vector (7 downto 0); -- vetor de 8 bits

signal v4 : bit_vector (3 downto 0); -- vetor de 4 bits

signal t4 : bit_vector (3 downto 0); -- vetor de 4 bits

...

x <= v8 (7);

-- atribui o do bit mais significativo

v4 <= v8 (5 downto 2); -- atribui o do quarteto central de v8

t4 <= v8 (2 to 5);

-- mesmo quarteto , na ordem inversa

UFPR, BCC, CI2102016-2

Vetores de bits podem ser representados nas bases hexadecimal (x), octal (o) e

binria (b). A representao binria implcita a normal: se nada for dito em

contrrio, o vetor um vetor de bits.

hexadecimal

octal

binaria_expl

binaria_impl

1.5.4

<=

<=

<=

<=

x " C0 " ;

o " 300 " ;

b " 11000000 " ;

" 11000000 " ;

-----

1100 0000

OITO bits

011 000 000 NOVE bits

11000000 base -2 expl cita

11000000 base -2 impl cita

Mecanismo de simulao

A simulao de modelos escritos em VHDL emprega a Simulao de Eventos Discretos os eventos ocorrem em instantes determinados pela prpria simulao.

Processos so alguns dos comandos da linguagem que estudaremos em breve. No

trecho de cdigo acima, cada uma das atribuies um processo, embora o uso do

nome processo seja reservado para um comando especfico, que veremos em breve.

processo

A simulao consiste de duas fases: uma fase de inicializao e passos de simulao.

Na fase de inicializao (i) todos os sinais so inicializados com os valores declarados, ou com os menores valores possveis para os sinais; (ii) o tempo simulado

inicializado em zero; e (iii) todos os processos so executados exatamente uma vez.

A atribuio a um sinal causa uma transao, e a atribuio ser efetivada no prximo delta (t). Se o sinal muda de estado, ento este sinal sofre um evento. Um

evento no sinal S causa a execuo de processos que dependem de S.

delta

Uma atribuio pode especificar o instante em que transao ocorrer:

A <= B ;

X <= Y after 10 ns ;

-- transa o no pr ximo delta

-- transa o depois de 10 ns

...........

X<=Y after 10 ns;

A<=B; ........... A=B

X=Y

...

0

0 + 10ns

Durante um passo de simulao (i) o tempo simulado avana at o prximo instante

em que uma transao est programada; (ii) todas as transaes programadas para

aquele instante so executadas; (iii) estas transaes podem provocar eventos em

sinais; (iv) processos que dependem destes eventos so ento executados; e (v) depois

que todos os processos executam, a simulao avana at o instante em que a prxima

transao est programada para ocorrer.

O tempo simulado avana em funo de eventos nos sinais; a cada mudana no estado

de um sinal corresponde um evento. Se ocorre um evento num sinal no lado direito

de uma atribuio, a expresso do lado direito reavaliada, e se houver mudana no

estado do sinal representado pela expresso, o novo estado atribudo ao sinal do

lado esquerdo causando um evento neste sinal.

Sinais so avaliados neste delta, mas eventos tm efeito no prximo delta enquanto

houver eventos no delta corrente, estes so avaliados e eventos resultantes so escalonados para o prximo delta. Eventos podem ser escalonados para instantes futuros

com after.

transao

evento

UFPR, BCC, CI2102016-2

Como um exemplo, considere o modelo de um somador completo, com modelagem

da propagao dos sinais atravs do circuito. Um evento em A pode causar um

evento em Cout no prximo delta, e em Sum em delta-atual mais 10ns.

Sum <= A xor B xor Cin after 10 ns ;

Cout <= ( A and B ) or ( A and Cin ) or ( B and Cin );

1.6

Da tarefa

Etapa 1 Copie para sua rea de trabalho o arquivo com o cdigo VHDL, e extraia

seu contedo com os seguinte comandos:

(1) wget http://www.inf.ufpr.br/roberto/ci210/vhdl/l_estrutural.tgz

(2) expanda-o com tar xzf l_estrutural.tgz

(3) o diretrio estrutural ser criado na expanso da tarball;

(4) mude para aquele diretrio com cd estrutural

O arquivo packageWires.vhd contm definies para nomes de sinais, uma vez que

digitar reg8 mais econmico do que bit_vector(7 downto 0).

O arquivo aux.vhd contm os modelos das portas lgicas not, nand, nor, xor, que

so os componentes bsicos para este laboratrio. Este arquivo no deve ser editado.

O arquivo estrut.vhd contm um modelo para um multiplexador de duas entradas,

mux2. Este modelo serve de base para que voc escreva os modelos para os componentes mux4, mux8, demux2, demux4, demux8, decod2, decod4, decod8, que so

definidos na Seo 1.3 de [RH12].

O script run.sh compila o cdigo VHDL e produz um simulador. Se executado sem

nenhum argumento de linha de comando, run.sh somente (re)compila o simulador.

Com qualquer argumento o script dispara a execuo de gtkwave: ./run.sh 1 &

O arquivo v.vcd contm definies para o gtkwave tais como a escala de tempo e

sinais a serem exibidos na tela para a verificao do modelo mux2.

Das mensagens de erro Em caso de erro de compilao detectado pelo

compilador VHDL, o script run. sh aborta a compilao, e exibe as

mensagens de erro emitidas pelo compilador. Estas mensagens so a

melhor indicao que o compilador capaz de emitir para ajud-lo a

encontrar o erro, e portanto as mensagens de erro devem ser lidas.

Os programadores do GHDL dispenderam um esforo considervel para

emitir mensagens (relativamente) teis em caso de erro. No desperdice

a preciosa ajuda que lhe oferecida.

1.6.1

mensagens

de erro

Modelo do multiplexador

A entidade do multiplexador de duas entradas mostrada abaixo. O circuito tem

duas entradas a e b, uma entrada de seleo s e uma sada z, todas de um bit.

entity

UFPR, BCC, CI2102016-2

10

Programa 1: Entidade mux2.

use work . p_wires . all ;

entity mux2 is

port (a , b : in bit ;

s

: in bit ;

z

: out bit );

end mux2 ;

z....

.

.......

p

p pp

ppp p p

pp ...

....

.

.......

pppp ...

..p....p

pppp ..1.

ppp

.

....

.

.......

Um modelo estrutural do mux2 mostrado no Programa 2. Numa implementao

bvia do mux2 so necessrios trs sinais internos, r com o complemento de s, e p,q

para interligar as portas nand e a porta nor. No Programa 2, os componentes e os

sinais internos so declarados entre o architecture e o begin. Os componentes so

instanciados entre o begin e o end architecture.

Programa 2: Arquitetura do mux2.

architecture estrutural of mux2 is

-- declara o dos componentes

component inv is

port ( A : in bit ; S : out bit );

end component inv ;

component nand2 is

port (A , B : in bit ; S : out bit );

end component nand2 ;

-- declara o sinais internos

signal r , p , q : bit ;

begin

-- in cio da rea concorrente

-- instancia o

Ui : inv

port

Ua0 : nand2 port

Ua1 : nand2 port

Uor : nand2 port

dos

map

map

map

map

componentes

(s , r );

(a , r , p );

(b , s , q );

(p , q , z );

z...

..

.

.......

ppp

p

p

ppp

pp

p p p p p p p p p p p pp p p

ppp

pp p

pp pp Uor ppppp

ppp

pp p

p pp p p p p p p p p p p p p p p p p p pp p

ppp ..... s

pp 1

pp p p pppp pppp p p

p

p

p

p

p

p

p

p

p

p pp p p

q

pp

p pp p ppppp pppp

p

p

pp p ppp p

pp

pp Ua1 pp pppp

p Ua0

ppp

pppp ppp

....

ppppppppp pppppppppppppp

pp p ....

ppp

p

Ui

p

p

p

p

pp

p

pppppp s

ppp

r

p

p

.

.......

.

.......

-- fim da rea concorrente

end architecture estrutural ;

Na instanciao, cada componente tem um label (opcional) Uxx: que significa

design Unit xxx e o mapeamento das portas do componente com os sinais da

interface (declarados na entidade) e os sinais internos (declarados na arquitetura).

Por exemplo, na instanciao

port map

Ua0 : nand2 port map (a ,r , p )

as portas A, B e S do componente nand2 so ligados aos sinais a, r, e p, e este

mapeamento chamado de mapeamento posicional porque os sinais da arquitetura

so associados s portas do componente na ordem em que as portas so declaradas.

A regio entre o begin e o end architecture chamada de rea concorrente e os comandos nesta rea so executados concorrentemente. Isso significa que o cdigo dos

componentes instanciados simulado (executado) em paralelo, imitando o comportamento de um circuito real. Os quatro componentes do mux2 reagem a eventos nas

mapeamento

posicional

rea

concorrente

UFPR, BCC, CI2102016-2

11

entradas e possivelmente provocam eventos na sada. Um evento uma mudana

num sinal (1 0 ou 0 1).

1.6.2

evento

O modelo est pronto, e agora?

Posta a pergunta do ttulo de outra forma: como testar um circuito combinacional?

Iniciemos pela tabela verdade do multiplexador de duas

entradas, mostrada ao lado. So trs as entradas e portanto as 23 = 8 combinaes de entradas devem ser verificadas, para garantir que a sada do circuito a esperada.

O projetista de hardware tem duas obrigaes distintas

porm inseparveis: (i) deve projetar um circuito que

atenda ao especificado; e (ii) deve prover a garantia de

que seu circuito atende especificao.

s

0

0

0

0

1

1

1

1

a

0

0

1

1

0

0

1

1

b

0

1

0

1

0

1

0

1

z

0

0

1

1

0

1

0

1

Com base na tabela verdade este no o nico mtodo o projetista gera um

vetor de testes para exercitar o circuito, e confirmar que seu comportamento o

correto, segundo a especificao.

A especificao junto com o vetor de testes so o contrato de venda do circuito, que

garante ao comprador que o circuito cumpre o que foi prometido pelo vendedor.

1.6.3

Testbench

O arquivo tb_estrut.vhd contm o programa de testes (testbench, ou TB) para

verificar a corretude dos seus modelos. Para simplificar a depurao do seu cdigo

VHDL, voc deve verificar cada novo modelo assim que seu cdigo for completado.

A entidade tb_estrut vazia porque o programa de testes autocontido e no

tem interfaces com nenhum outro componente. A arquitetura do TB declara os

componentes que sero testados e um record que ser usado para excitar os modelos.

O registro test_record possui seis campos e os valores destes campos devem ser

atribudos por voc de forma a gerar todas (todas?) as combinaes de entradas

necessrias para garantir a corretude do seu modelo. O vetor de testes test_array

contm onze elementos para ilustrar as possibilidades, e excitar e verificar o mux2.

No test_record, o campo k um bit (0), os campos a e s so vetores de bits

codificados em binrio (b"01001100"). O campo mx o bit com a sada esperada

para um multiplexador quando os valores definidos em s e a so aplicados s entradas.

O campo dm o vetor de bits com a sada esperada para um demultiplexador quando

recebe as entradas definidas pelos valores em k,s. O campo dc o vetor de bits com

a sada esperada para um decodificador cujas entradas so definidas pelos valores

em s.

Note que cada um dos registros usado para testar todos os circuitos simultaneamente e portanto, dependendo do teste, alguns dos campos no so relevantes naquele teste. Por exemplo, para testar o mux2, somente o bit 0 do sinal s (s(0))

relevante; para testar mux4, s(1 downto 0) so relevantes, e para o mux8 todos os

trs bits so relevantes, s(2 downto 0).

Registro

(record)

test_record

Vetor

(array)

test_array

escalar: 0

vetor: b"01"

seleo de

componentes

de um vetor

de bits:

s(0)

s(M downto N)

UFPR, BCC, CI2102016-2

12

Programa 3: Vetor de valores de entrada para testar modelos.

type test_record is record

k : bit ;

-- entrada de bit para d emulti plexad ores

a : reg8 ;

-- entrada para multiplexadores

s : reg3 ;

-- entrada de sele o

mx : bit ;

-- sa da esperada do MUX

dm : reg8 ;

-- sa da esperada do DEMUX

dc : reg8 ;

-- sa da esperada do DECOD

end record ;

type test_array is array ( positive range < >) of test_record ;

constant test_vectors : test_array := (

--k ,

a,

s,

mx ,

dm ,

dc

( 0 , b " 00000011 " ,b " 000 " , 0 , b " 00010000 " ,b " 00000000 " ) ,

( 0 , b " 00000011 " ,b " 001 " , 1 , b " 00010000 " ,b " 00000000 " ) ,

...

( 0 , b " 00000000 " ,b " 000 " , 0 , b " 00000000 " ,b " 00000001 " )

);

Dos vetores de teste genricos Os elementos do vetor de entrada dos

testes so genricos no sentido de que um elemento deve ser usado para

testar os modelos mux2, mux4, e mux8. Para cada um destes testes,

voc deve ligar ou desligar os bits relevantes para a largura do modelo

sob teste: 2, 4 ou 8 bits, na entrada, e 1, 2 ou 3 bits no sinal de controle.

O diagrama na Figura 4 mostra as ligaes entre os componentes que voc deve

modelar e o processo que percorre o vetor de testes e gera as sequncias de entradasde-teste e sadas-de-teste. As entradas-de-teste (a, k, s) excitam seus modelos, que

produzem sadas de acordo com suas especificaes. As sadas-de-teste (mx, dm, dc)

so comparadas com as sadas produzidas pelos modelos. O nmero de bits em a

depende da largura do multiplexador, assim como o nmero de bits (n e m) dos

sinais dm e dc.

pppppppppppppp

pppppppppppppp

ppppp

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ..

.. . . . . . . . . . . ..

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

..... ..... ..

.

.

.

.

.

.

.

.

.

. .....

0..2

.

.

.

.

.

.

.

.

. ..... ..

.

.

.

.

.

.

.

.

.

.. .....

.

.

. ......

.

.

.

. .... .....

.

.

.

..

.

.

......

.

.

.

..... .

..

.

.

.

.

.

.

.

.

. ..

.

..

.

.

.

.

.

.

. .

.

.

.....

. .

.

.

.

.

.

.

.

.

.

.

.

.

. ..

.

.

.

.............

.

. .

. .......

.

.

. .

.

......

.

......

.

. ..

.

.

..

.

.

.

.

.

..

.

.

.

.

...

.

.

.

..

.

.

.

.

....

.

..

.

.

.

.

.

.

.

.

. .......

...

.

.

.

.

.

.

..

.

.

.

0..2

.

.

.

.

.

... ..

.

.

.

.

.

.

.

.

..... ..

.....

.

.

.

.....

.

.

.

.....

.

...

.

.

.

.

.....

.

.

.

....

.

.

.

.

.

.

.

.

.

.

.

..

.

...

.

.

.

.

.

.

.

.

.

...

.

.

.

.

.

.

......

.

.

.

.

.

.

.

.

.

.

.

.

.

.....

. .....

.

.

.

.

0..2

. ......

.

.

.

.

.

.

.

.

.

....

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

...

.

.

.

.

.

.

.

.

.

.

.

.

.

. .......

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

..

.

.

.

.

.

.

.

.

.

.

.

.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ..

q

q

q

pp p p p p p pp

p pppp ppppppp

pppp

p

p p p pp p p p p p p

pp p p p p p p p

mux

pppppppp

pp pppppppppp

ppppp ppppppp

p ppppp

pppp ppppppppp

ppppppp pppppp

s

demux

k

s

qq

q

pppppppppppsppp

pppppppppppppp

pppppp

pppppp

ppppppppp pppp

pp ppppppppspp p

pppppsel

pppppppppppppp

pppppppppppppp

p

q

q

q

pp p p p p p p p pp

pppp p pppppp

pppp

p

p p p pp p p p p p p p

ppp p p ppp

q

q

q

pppp pppp

pppppp pppppppp

pppp

p

p p p pp p p p p p p

ppp p pppp

mx

asserts

dm

sl

gerador de vetores de testes

Figura 4: Ligaes entre o testbench e os modelos.

A sequncia de valores de entrada para os testes dos modelos gerada pelo processo

UFPR, BCC, CI2102016-2

13

U_testValues, com um lao for ... loop. A varivel de iterao itera no espao

definido pelo nmero de elementos do vetor de testes (test_vectorsrange) o

atributo range representa a faixa de valores do ndice do vetor. Se mais elementos

forem acrescentados ao vetor, o lao executar mais iteraes. O elemento do vetor

atribudo varivel v e os todos os campos do vetor so ento atribudos aos sinais

que excitam os modelos. O processo U_testValues executa concorrentemente com o

seu(s) modelo(s) e quando os sinais de teste so atribudos no lao, estes provocam

alteraes nos sinais dos modelos.

O comando assert similar a um printf() em C e pode ser usado para exibir

o valor de sinais ao longo de uma simulao. Este comando tem trs clusulas:

assert condio report string severity nvel. A condio deve ser falsa para que

o simulador imprima a string. A severidade pode ter quatro nveis: note, warning,

error, failure, e a ltima (failure) aborta a simulao.

atributo

range

assert

O assert no Programa 4 verifica se a sada observada no multiplexador igual

sada esperada. Se os valores forem iguais, o comportamento o esperado, e

portanto correto com relao aos vetores de teste que voc escreveu. Note que se

voc escolher valores de teste inadequados, ou errados, pode ser difcil diagnosticar

problemas no seu modelo.

Programa 4: Mensagem de verificao de comportamento.

assert saidaMUX2 = esperadaMUX

report " mux2 : saida errada sel = " & B2STR ( s (0)) &

" saiu = " & B2STR ( saidaMUX2 ) & " esperada = " & B2STR ( esperadaMUX )

severity error ;

Se os valores de saidaMUX2 e esperadaMUX diferem, a mensagem no Programa 4

emitida no terminal, indicando o erro. A funo B2STR converte um bit em uma

string para que o valor do bit seja emitido; a funo BV2STR converte um vetor de

bits para uma string. O operador & concatena duas strings. A seleo de um

subcampo de bits obtida especificando-se quais bits deseja-se selecionar, como

discutido na pgina 7.

Ao final do lao, a simulao termina no comando wait; este faz com que a execuo

do processo U_testValues se encerre.

1.6.4

Teste dos multiplexadores

O Programa 5 uma verso muito alterada do Programa 3, e serve para mostrar

como deve ser vetor de testes para o mux-2, cujo vetor de testes discutido na

Seo 1.6.2.

Os valores que so irrelevantes ao teste do mux-2 esto mostrados no test_vectors

como .. No use o caractere . no vetor de testes porque este valor no pertence

a IB. A menos da ordem das colunas, test_vectors contm todas as linhas da tabela

verdade do mux-2

&

concatenao

seleo de

campo

UFPR, BCC, CI2102016-2

14

Programa 5: Vetor de testes para o mux-2.

constant test_vectors : test_array := (

-ab

s

z

( . , b " ......00 " ,b " ..0 " , 0 , b " ........ " ,b " ........ " ) ,

( . , b " ......01 " ,b " ..0 " , 1 , b " ........ " ,b " ........ " ) ,

( . , b " ......10 " ,b " ..0 " , 0 , b " ........ " ,b " ........ " ) ,

( . , b " ......11 " ,b " ..0 " , 1 , b " ........ " ,b " ........ " ) ,

( . , b " ......00 " ,b " ..1 " , 0 , b " ........ " ,b " ........ " ) ,

( . , b " ......01 " ,b " ..1 " , 1 , b " ........ " ,b " ........ " ) ,

( . , b " ......10 " ,b " ..1 " , 0 , b " ........ " ,b " ........ " ) ,

( . , b " ......11 " ,b " ..1 " , 1 , b " ........ " ,b " ........ " ) ,

...

);

A coluna mx de test_vectors a sada esperada para o mux-2 e o

assert saidaMUX2 = esperadaMUX ...

emitir mensagem de erro somente se o modelo produzir sada diferente de mx. Se

a sada esperada a produzida, ento o assert fica silente porque o circuito est

correto, segundo o vetor de testes.

Uma vez que voc esteja certo de que o mux-2 est correto, teste o mux-4. Este

circuito composto de trs mux-2, e voc acaba de garantir que um circuito que

atende a sua especificao. O mux-4 tem seis entradas e sua tabela verdade tem

26 = 64 linhas, sendo portanto necessrios 64 testes. Certo?

Sim, certo. Podemos usar de inteligncia e descobrir qual o nmero mnimo de

testes para garantir a corretude do mux-4. Este nmero bem menor do que 64.

Gere o vetor de testes (reduzido) para o mux-4 e verifique sua corretude. Isso feito,

comente o assert saidaMUX4 em tb_estrut.vhd.

O mux-8 composto de dois mux-4 que voc garante que correto e de um

mux-2 que voc tambm garante que correto. O mux-8 tem onze entradas e sua

tabela verdade tem 211 = 2048 linhas. So necessrios 2048 testes. Certo?

Gere o vetor de testes (reduzido) para o mux-8 e verifique sua corretude. Isso feito,

comente o assert saidaMUX8.

1.6.5

Teste dos demultiplexadores

Usaremos o mesmo procedimento para testar os demultiplexadores. Em tb_estrut.vhd, descomente a linha com

assert saidaDEMUX2

A tabela verdade das sadas z e w do demux-2, mostrada

ao lado, e com base nela, o vetor de testes mostrado no

Programa 6.

s

0

0

1

1

a

0

1

0

1

z

0

1

0

0

w

0

0

0

1

Os valores que so irrelevantes ao teste do demux-2 esto mostrados no test_vectors

como .. No use o caractere . no vetor de testes porque este valor no pertence

a IB. A menos da ordem das colunas, test_vectors contm todas as linhas da tabela

verdade do demux-2.

UFPR, BCC, CI2102016-2

15

Programa 6: Vetor de testes para o demux-2.

constant test_vectors : test_array := (

--a

s

zw

( 0 , b " ........ " ,b " ..0 " , . , b " ......00 " ,b " ........ " ) ,

( 1 , b " ........ " ,b " ..0 " , . , b " ......10 " ,b " ........ " ) ,

( 0 , b " ........ " ,b " ..1 " , . , b " ......00 " ,b " ........ " ) ,

( 1 , b " ........ " ,b " ..1 " , . , b " ......01 " ,b " ........ " ) ,

...

);

Da mesma forma que com os multiplexadores, os demux-4 e demux-8 so composies de demux-2. Uma vez que o componente pequeno tenha sido verificado, a

verificao do componente grande necessita de um nmero relativamente pequeno

de testes para tambm ser verificada.

A cada tamanho testado, lembre de descomentar a linha com assert saidaDEMUXn

antes do teste, e de coment-la novamente aps o teste.

1.6.6

Teste dos decodificadores

Voc j entendeu o processo...

O Programa 7 mostra os campos relevantes para o teste do decod-2.

Programa 7: Vetor de testes para o decod-2.

constant test_vectors : test_array := (

-s

zw

( . , b " ........ " ,b " ..0 " , . , b " ........ " ,b " ......01 " ) ,

( . , b " ........ " ,b " ..1 " , . , b " ........ " ,b " ......10 " ) ,

...

);

1.7

Modelagem Estrutural de Circuitos Mais Complexos

Etapa 2 Acrescente ao arquivo estrut.vhd o cdigo VHDL para os modelos

dos multiplexadores de 4 e 8 entradas, dos demultiplexadores de 2,4,8 sadas, e dos

decodificadores de 2,4,8 sadas. Acrescente e/ou altere os elementos do vetor de

testes para verificar a corretude dos seus modelos.

H duas entidades distintas para o mux8. A primeira, mux8, emprega oito sinais

de tipo bit nas entradas, e trs bits para seleo. A segunda, mux8vet mostrada

no Programa 8, tem como entradas um vetor de 8 bits entr: reg8 e outro vetor

sel: reg3 para a seleo. As duas arquiteturas so idnticas, exceto que as ligaes

dos sinais da interface aos componentes devem usar seleo de campos de bits.

Programa 8: Entidade do mux8 com vetores de bits.

entity mux8vet is

port ( entr : in reg8 ; -- vetor com 8 bits

sel : in reg3 ; -- vetor com 3 bits

z

: out bit ); -- sa da de 1 bit

end mux8vet ;

UFPR, BCC, CI2102016-2

16

Note que voc quem deve ajustar a sada esperada para cada um dos

circuitos nos vetores de teste. O projetista dos modelos responsvel por

escrever os vetores de teste e portanto sua tarefa ajustar os campos

mx (sada esperada dos muxN), dm (sada esperada dos demuxN), e dc

(sada esperada dos decodN). Se os valores que voc atribuir queles

campos forem incorretos para as entradas, ento os asserts indicaro

falso-positivos para erros.

Os asserts que verificam a corretude dos demultiplexadores e decodificadores esto

comentados para reduzir a poluio na tela. Aps completar a verificao dos trs

multiplexadores, comente seus asserts e descomente aqueles dos demultiplexadores.

Repita para os decodificadores.

Referncias

[RH12]

Sistemas Digitais e Microprocessadores, R.A.Hexsel, 2012, Editora da

UFPR.

[PJA90] The VHDL Cookbook,

http://freecomputerbooks.com/The-VHDL-Cookbook.html

EOF

Histrico das

26ago2016:

25ago2016:

24ago2016:

22ago2016:

23set2015:

12set2015:

29jul2015:

Revises:

exemplos de vetores de testes;

includas sugestes de Zanata, remoo de FPGA;

bv(0 to 3) pg. 8;

compilao VHDL;

portas CMOS;

ajustes cosmticos, diagrama com simulador;

primeira verso.

a responsabilidade

pelos testes

do

projetista!

S-ar putea să vă placă și

- PPC Ec NovoDocument179 paginiPPC Ec NovoRodrigo FerronatoÎncă nu există evaluări

- 2016 2 Ricardo-Artur-Staroski ApresentacaoDocument44 pagini2016 2 Ricardo-Artur-Staroski ApresentacaoRodrigo FerronatoÎncă nu există evaluări

- Ba200 Lista4Document2 paginiBa200 Lista4Rodrigo FerronatoÎncă nu există evaluări

- Pratica2 FTDocument17 paginiPratica2 FTRodrigo FerronatoÎncă nu există evaluări

- Manual Pim IIDocument27 paginiManual Pim IIRodrigo FerronatoÎncă nu există evaluări

- Alfabeto e LinguagemDocument7 paginiAlfabeto e LinguagemRodrigo FerronatoÎncă nu există evaluări

- Apostila de EstudoDocument136 paginiApostila de EstudoRodrigo FerronatoÎncă nu există evaluări

- Edital Mestrado UFFDocument7 paginiEdital Mestrado UFFFelipe LameuÎncă nu există evaluări

- Colheitadeira New HollandDocument56 paginiColheitadeira New HollandALEXANDRE F VOLTAÎncă nu există evaluări

- Af Mapa AlgarveDocument1 paginăAf Mapa AlgarveGustavo MartinsÎncă nu există evaluări

- NR 18 - Manual - EsmerilhadeiraDocument3 paginiNR 18 - Manual - EsmerilhadeiraCPSSTÎncă nu există evaluări

- Como Obter o Índice Radiônico de Uma Pessoa Ou Animal Usando Uma Máquina Radiônica SimplesDocument8 paginiComo Obter o Índice Radiônico de Uma Pessoa Ou Animal Usando Uma Máquina Radiônica Simplescmidsa100% (1)

- Aula - FermentaçãoDocument11 paginiAula - FermentaçãosimaspedroÎncă nu există evaluări

- MANUAL Boulevard M800 2009Document37 paginiMANUAL Boulevard M800 2009Arthur Demah Bardos71% (21)

- I EE Medidas en 2015.1 Resolução POLIDocument11 paginiI EE Medidas en 2015.1 Resolução POLIRafaelcl8Încă nu există evaluări

- Exercicio TGCDocument23 paginiExercicio TGCIlana LopesÎncă nu există evaluări

- Ponte SalinaDocument3 paginiPonte SalinaoliveiraferreiraÎncă nu există evaluări

- Artesanato de Bolsas PDFDocument10 paginiArtesanato de Bolsas PDFHelton Corrêa100% (1)

- Midas Material de Apoio Módulo Extra Carine Aula 1Document4 paginiMidas Material de Apoio Módulo Extra Carine Aula 1Glaucia AndradeÎncă nu există evaluări

- Faculdade Da Aldeia de Carapicuíba - TCC KarlaDocument16 paginiFaculdade Da Aldeia de Carapicuíba - TCC KarlaKarla Cristina AlvesÎncă nu există evaluări

- Procedimento Configuração LTE - Elsys CPE EPRL14Document10 paginiProcedimento Configuração LTE - Elsys CPE EPRL14Rodrigo SilvaÎncă nu există evaluări

- Filo CnidariaDocument3 paginiFilo CnidariaNicollas SouzaÎncă nu există evaluări

- Prova 5S 1ºB 2010Document2 paginiProva 5S 1ºB 2010SandraGehardt100% (8)

- INA Catálogo de Aplicações Acionamento de Válvulas, Rolamentos para Caixas de Câmbio e Variadas Aplicações - Leve PDFDocument142 paginiINA Catálogo de Aplicações Acionamento de Válvulas, Rolamentos para Caixas de Câmbio e Variadas Aplicações - Leve PDFcpdrozimbo0% (1)

- Modbus ManualDocument25 paginiModbus ManualDiego GuimarãesÎncă nu există evaluări

- CoelhosDocument4 paginiCoelhosLuiza MedeirosÎncă nu există evaluări

- Check List Dobra de FerroDocument1 paginăCheck List Dobra de FerroIndiaraÎncă nu există evaluări

- O Hospital e Asilo Da Venerável Ordem Terceira Da Penitência S. Francisco de Coimbra (1851-1926)Document239 paginiO Hospital e Asilo Da Venerável Ordem Terceira Da Penitência S. Francisco de Coimbra (1851-1926)tofcoimbraÎncă nu există evaluări

- Bole Tim 9Document28 paginiBole Tim 9espiritualidadeeufologiaÎncă nu există evaluări

- Per030015 1981 00111Document38 paginiPer030015 1981 00111IzaelSouzaÎncă nu există evaluări

- Ldia10 Ficha Leitura Exposicao SorvetesDocument3 paginiLdia10 Ficha Leitura Exposicao Sorvetessofia_ritoÎncă nu există evaluări

- Paradigma Cine ArteDocument1 paginăParadigma Cine ArteDanielNogueiraÎncă nu există evaluări

- Trombone InscricaoDocument2 paginiTrombone InscricaoAntónio BravoÎncă nu există evaluări

- Raízes Mag N.º 2Document63 paginiRaízes Mag N.º 2Clara GageiroÎncă nu există evaluări

- Progressão Aritimética - Aula MatemáticaDocument5 paginiProgressão Aritimética - Aula MatemáticaLuiza Mirele Alves Oliveira MotaÎncă nu există evaluări

- Artigo - Bibliografia Comentada - Café HistóriaDocument4 paginiArtigo - Bibliografia Comentada - Café HistóriaProf. Marcus OliveiraÎncă nu există evaluări

- 4 - Barema Do Trabalho - DPC - CEFS II - 2023Document3 pagini4 - Barema Do Trabalho - DPC - CEFS II - 2023godinhomgÎncă nu există evaluări