Documente Academic

Documente Profesional

Documente Cultură

Chapter 03

Încărcat de

Talha YasinDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Chapter 03

Încărcat de

Talha YasinDrepturi de autor:

Formate disponibile

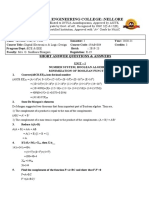

CHAPTER 3

2008 Pearson Education, Inc.

3-1.

Place a 1 in each K-map cell where 2 or more inputs are equal to 1.

Y

1

X

This is the same function as the

carry for the full adder.

F = XZ + XY + YZ

1 1

Z

3-2.*

C

F = AB + AC

3-3.

CD

AB

CD

00 01 11 10

AB

00

00

01

01

11 1

10

CD

00 01 11 10

AB

01

W=A B C D + A B C D

10 1

10

X =A B C D + A B C + A B D

00 01 11 10

01 1

11 1

11

1

AB

00

00

1

11

1

CD

00 01 11 10

Y =A B (C D + C D) + A B(C D + C D)

10 1

Z =A B D + B C D + A B D

3-4. a) For the 3 x 3 pattern, there are exactly three row, three column and two diagonal combinations that

represent a win for the X player: W = X1 X2 X3 + X4 X5 X6 + X7 X8 X9 + X1 X4 X7 + X2 X5 X8 + X3 X6 X9

+ X1 X5 X9 + X3 X5 X7 Gate Input cost = 32

b) W = X5 (X1 X9 + X2 X8 + X3 X7 + X4 X6) + X1 X2 X3 + X1 X4 X7 + X7 X8 X9 + X3 X6 X9 Gate Input Cost = 30

3-5. a) For the 4 x 4 pattern, there are exactly four row, four column and two diagonal combinations that represent a

win for the X player: W = X1 X2 X3 X4 + X5 X6 X7 X8 + X9 X10 X11 X12 + X13 X14 X15 X16 + X1 X5 X9 X13

X2 X6 X10 X14 + X3 X7 X11 X15 + X4 X8 X12 X16 + X1 X6 X11 X16 + X4 X7 X10 X13 Gate Input cost = 50

b) W = X1(X2 X3 X4 + X5 X9 X13 + X6 X11 X15) + X7(X5 X6 X8 + X3 X11 X15 + X4 X10 X13) + X9 X10 X 11 X12

+ X13 X14 X15 X16 + X2 X6 X10 X14 + X4 X8 X12 X16 Gate Input Cost = 48

25

Problem Solutions Chapter 3

3-6.

a) Detecting a change in one-out-ofthree inputs can be done using a

parity function as Z. The truth

table shown is for even parity.

For this case,

Z = X1 X2 X3

If odd parity is chosen, then an

alternative result for Z is:

X1

0

0

0

0

1

1

1

1

X2

0

0

1

1

0

0

1

1

X3

0

1

0

1

0

1

0

1

Z

0

1

1

0

1

0

0

1

Z = X1 X2 X3

3-7.+

B

ABCD GNS YNS RNS GEW YEW REW

0000

1

0

0

0

0

1

0001

1

0

0

0

0

1

0011

1

0

0

0

0

1

0010

1

0

0

0

0

1

0110

1

0

0

0

0

1

0111

1

0

0

0

0

1

0101

0

1

0

0

0

1

0100

0

0

1

0

0

1

1100

0

0

1

1

0

0

1101

0

0

1

1

0

0

1111

0

0

1

1

0

0

1110

0

0

1

1

0

0

1010

0

0

1

1

0

0

1011

0

0

1

1

0

0

1001

0

0

1

0

1

0

1000

0

0

1

0

0

1

B

GNS

A

C

GEW = AB + AC

GNS = AC + AB

A

B

C

D

A

B

C

D

YNS

YNS = ABCD

B

0

0

1

1

0

0

1

1

C S5 S4

0 0 0

1 0 0

0 0 0

1 0 0

0 0 1

1 0 1

0 1 0

1 1 1

S3

0

0

0

1

0

1

0

0

S2

0

0

1

0

0

0

1

0

B

C

D

B

C

D

RNS

RNS = A + BCD

S1 S0

0 0

0 1

0 0

0 1

0 0

0 1

0 0

0 1

26

YEW

YEW = ABCD

3-8.

A

0

0

0

0

1

1

1

1

GEW

S0 = C

S1 = 0

S2 = ABC + ABC

S3 = ABC + ABC

S4 = AB + AC

S5 = AB

REW

REW = A + BCD

Problem Solutions Chapter 3

3-9.+

A

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

B

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

C

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

A

0

0

0

0

0

0

0

0

1

1

B C

0 0

0 0

0 1

0 1

1 0

1 0

1 1

1 1

0 0

0 0

1010 to

1111

D S2 S1 S0

0 0 0 0

1 0 0 1

0 0 0 1

1 0 1 0

0 0 1 0

1 0 1 0

0 0 1 0

1 0 1 1

0 0 1 1

1 0 1 1

0 0 1 1

1 0 1 1

0 0 1 1

1 1 0 0

0 1 0 0

1 1 0 0

S0 = B C D + B C D + AB + AC D + ABCD

S1 = AB + AB + ACD + BC D

S2 = ABC + ABD

3-10.

D W X

0 0 1

1 0 1

0 1 0

1 1 0

0 1 0

1 1 0

0 1 1

1 1 1

0 1 1

1 1 1

Y

1

1

0

0

1

1

0

0

1

1

Z

0

1

0

1

0

1

0

1

0

1

W=A+B+C

X = B C + BC

Y=C

Z=D

XXXX

3-11.

a)

PS LS RS RR PL LL RL

0 0 0 0 0 0 0

0 0 0 1 0 0 0

0 0 1 0 0 0 1

0 0 1 1 0 0 1

0 1 0 0 0 1 0

0 1 0 1 0 1 0

0 1 1 0 0 0 1

0 1 1 1 0 1 0

1 0 0 0 1 0 0

1 0 0 1 1 0 0

1 0 1 0 1 0 0

1 0 1 1 1 0 0

1 1 0 0 1 0 0

1 1 0 1 1 0 0

1 1 1 0 1 0 0

1 1 1 1 1 0 0

PL = PS

LL = PS LS RS + PS LS RR

RL = PS LS RS + PS RS RR

b)

PL

PS

LS

LL

RS

RL

RR

27

Problem Solutions Chapter 3

3-12.

C

a)

1

1

1

1

A

1

C

1

1

1

1

1 1

1 1

C

1

C

1

C

1 1

1

1

A

1

b)

a = AC + A B D + ABD + AB C

b = A B + B C + A C D + ACD

c = AB + B C + AD

d = ABCD + AB C + A B D + A BC + ACD

e = B C D + ACD

f = AB C + ABD + ABC + A C D

g = AB C + ABC + A BC + ACD

c) The following gate input counts include input inverters and share AND gates.

Total gate inputs for this solutions = 74. Total gate inputs for book solution is 70. The book solution is better by 4 gate inputs.

3-13.

X

Hierarchy

X

Y

Z

W=XZ + YZ

Z

Hierarchy

X

Y

Z

F = A(CE + DE) + AD

C

D

E

Hierarchy

X

Y

Z

Hierarchy

X

Y

Z

28

G = B(CE + DE) + BC

Problem Solutions Chapter 3

3-14.

Hierarchy

X

Y

Z

Hierarchy

X

Y

Z

G = A(BC + BD) + A(BC + BD)

= ABC + ABD + ABC + ABD

BC+BD

D

Hierarchy

X

Y

Z

BC+BD

3-15.+

b)

a)

c)

Part b requires 6 fewer gates.

A

B

C

D

E

F

G

H

A

B

C

D

E

F

G

H

3-16.

A

B

C

A

B

C

D

E

F

D

E

F

a) Original circuit

b) Replacement with equivalents

A

B

C

G

D

E

F

c) Cancel inverters

29

Problem Solutions Chapter 3

3-17.

A

A

B

C

D

E

F

B

C

D

a) Original circuit

F

b) Replacement with equivalents

B

C

D

G

B

C

D

c) Manipulate inverters

d) Cancel inverters

3-18.

C

D

C

D

G

E

F

A

a) Original circuit

C

D

b) Replacement with equivalents

C

D

F

A

F

A

c) Manipulate inverters

B

d) Cancel inverters

30

Problem Solutions Chapter 3

3-19.

C

D

G

C

D

E

F

A

G

E

F

A

B

a) Original circuit

H

C

G D

D

E

F

G

E

F

c) Manipulate inverters

d) Cancel and minimize inverters

3-20.

T1 = X Y

T2 = X Y

T3 = X Y

F = XY + X Y

X

T2

T1

F

T3

3-21.

Y 0 = ABCE

Except for G1 = 1 and G2A and G2B = 0,

the outputs Y0 through Y7 are all 1s. Otherwise, one of Y0 through Y7 is equal to 0

with all others equal to 1. The output that is

equal to 0 has index i = decimal value of

the values of (A,B,C) in binary. E.g., if

(A,B,C) = (1,1,0), then Y6 = 0.

Y 1 = ABCE

G1

Y 2 = ABCE

G2A

G2B

= G1 G2A G2B

Y 3 = ABCE

Y 4 = ABCE

Y 5 = ABCE

Y 6 = ABCE

Y 7 = ABCE

31

Problem Solutions Chapter 3

3-22.

A

B

C

G1

G2A_n

G2B_n

Y 11111111

01111111

10111111

11011111

11101111

11110111

11111011

11111101

11111110

11111111

[0]

[1]

[2]

[3]

[4]

[5]

[6]

[7]

100

200

300

400

500

600

3-23.

10

11

13

12

14

15

A

B

C

D

W

X

Y

Z

20

40

60

80

100

120

140

3-24.*

a)

b)

VDD

F7

G7

F6

G6

F5

G5

F4

G4

F3

G3

F2

G2

F1

G1

F0

G0

3-25.

a)

b)

VDD

VDD

F7

G7

3

2

F6

F5

F4

F3

G4

1

0

F2

G6

G5

G3

G2

F1

G1

F0

G0

32

160

Problem Solutions Chapter 3

3-26.

a)

b)

11

9

7

5

3

1

12

5

4

3

2

1

0

G(3:0)

F(3:0)

7:4

3:0

3-27.

V = A = ( S0 S1 S2 S3 S 4 S5 ) + M

S5

S4

S3

S2

S1

S0

C = V

A = (S 0 S1 S2 S3 S4 S5 ) + M

L = A

A

L

V

C

3-28.

A0

A1

A2

DECODER

0

A0

1

A1

2

A2

D0

3

4

5

6

7

D1

D2

D3

D4

D5

D6

D7

A3

DECODER

0

A0

1

A1

2

A2

D8

D9

3

4

5

6

7

D10

D11

D12

D13

D14

D15

33

Problem Solutions Chapter 3

3-29.

DECODER

A0

A1

DECODER

A2

A3

A0

A1

EN

EN

A0

A1

En

0

1

2

3

0

1

2

3

D0

D1

D2

D3

DECODER

A0

A1

A0

A1

En

0

1

2

3

D4

D5

D6

D7

DECODER

A0

A1

A0

A1

En

0

1

2

3

D8

D9

D10

D11

DECODER

A0

A1

A0

A1

En

0

1

2

3

D12

D13

D14

D15

3-30.*

D0

D1

D2

D3

D4

D5

D6

D7

D8

DECODER

A0

A1

A2

A0

A1

A2

0

1

2

3

4

5

6

7

D9

D10

D11

D12

D13

A3

A4

D14

DECODER

0

A0

1

A1

D15

2

3

D16

D17

D18

D19

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

D30

D31

34

Problem Solutions Chapter 3

3-31. (Errata: Replace 4 with 3 in 4-to-6-line decoder)

DECODER

A0

A1

A0

A1

0

1

2

3

D0

D1

D2

DECODER

A0

A2

D3

0

1

D4

D5

3-32.

a) The Truth Table:

X2 X1 X0

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

b) A = {d}

B = {a,g}

C = {c. e}

D = {b, f}

a

d

0

1

1

1

1

1

d

Note: a = g, b = f, and c = e.

b

d

0

0

0

1

1

1

d

A

X2

c

d

0

0

0

0

0

1

d

d

d

1

0

1

0

1

0

d

e

d

0

0

0

0

0

1

d

f

d

0

0

0

1

1

1

d

X0

g

d

0

1

1

1

1

1

d

DECODER

X0

X1

X2

X0

d 1

X1

X2

1

A = X0

A0

A1

A2

0

1

2

3

4

5

6

7

a

g

b

f

c

e

d

X0

C

d

X1

X2 1

B = X1 + X2

d

d

X1

X2 1

1

C = X1X2

3-33.

D0

A1

D1

D2

D3

A2

D4

D5

D6

D7

EN

35

d

1

D = X2

Gate input cost: b = 4 compared to a = 27 + 11 = 38

A0

X0

X1

Problem Solutions Chapter 3

3-34.

K-Map for GE5: BCD = (C3,C2, C1, C0)

B0

B1

B2

B3

C1

C3

C2

C0

GE5 = C3 + C2 (C1 + C0)

C2

C1

C0

D0

D1

1 D2

2 D3

3 D4

4 D5

5 D6

6 D7

7 D8

8 D9

9 D10

10 D11

11 D12

12 D13

13 D14

14 D15

15

DECODER

0

A0

P0

A1

A2

A3

P1

P2

P3

P4

GE5

C3

P5

Equations for output logic:

P0 = D0 + GE5D1

P1 = D2 + GE5D1

P2 = D3 + GE5D4

P3 = D5 + GE5D4

P4 = D6 + GE5D7

P5 = D8 + GE5D7

P6 = D9 + GE5D10

P7 = D11 + GE5D10

P8 = D12+ GE5D13

P9 = D14 + D15 + GE5D13

P6

P0

P0

P0

3-35.*

D3

0

X

X

X

1

D1

A1

D2 D1 D0 A1 A0 V

0 0 0 X X 0

X X 1 0 0 1

X 1 0 0 1 1

1 0 0 1 0 1

0 0 0 1 1 1

X

1

D3

D2

A0 = D 0( D 1 + D 2 )

1

1

1

1

1

D0

8

0

0

0

0

0

0

0

0

0

1

X

7

0

0

0

0

0

0

0

0

1

X

X

6

0

0

0

0

0

0

0

1

X

X

X

Decimal Inputs

5 4 3 2

0 0 0 0

0 0 0 0

0 0 0 0

0 0 0 1

0 0 1 X

0 1 X X

1 X X X

X X X X

X X X X

X X X X

X X X X

1

0

0

1

X

X

X

X

X

X

X

X

A0

Binary Outputs

0 A3 A2 A1 A0

0 X X X X

1 0 0 0 0

X 0 0 0 1

X 0 0 1 0

X 0 0 1 1

X 0 1 0 0

X 0 1 0 1

X 0 1 1 0

X 0 1 1 1

X 1 0 0 0

X 1 0 0 1

36

D3

D1

X

D3

9

0

0

0

0

0

0

0

0

0

0

1

D2

A0

A1 = D 0D 1

3-36.

A1

1

D0

V = D 0 + D 1 + D2 + D3

D0

D1

V

0

1

1

1

1

1

1

1

1

1

1

D2

Problem Solutions Chapter 3

3-37.

a)

b)

DECODER

S0

S1

S2

A0

A1

A2

0

1

2

3

4

5

6

7

I0

4x1 MUX

S0

S1

I0

I1

I2

I3

I1

I2

I3

S0

S1

0

1

2

3

Y

2x1 MUX

S2

S

0

1

4x1 MUX

I4

S0

S1

I4

I5

I6

I7

I5

I6

S0

S1

0

1

2

3

I7

3-38.

DECODER

A0

A1

A2

A3

A0

A1

A2

A3

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

37

Problem Solutions Chapter 3

3-39.

DECODER

S0

S1

S2

0

1

2

3

4

5

6

7

A0

A1

A2

IA0

IA1

IA2

IA3

YA

IA4

IA5

IA6

IA7

IB0

IB1

IB2

IB3

YB

IB4

IB5

IB6

IB7

3-40.

DECODER

S3

A0

0

1

I0

S0

S1

S2

I1

DECODER

A0

A1

A2

0

1

2

3

4

5

6

7

I2

I3

I4

I5

I6

I7

I8

I9

I10

I11

38

Problem Solutions Chapter 3

3-41.

A(2:0)

D0(7:0)

D1(7:0)

D2(7:0)

8x1 MUX

D(7:0) Y

0

S(2:0)

8x1 MUX

D(7:0) Y

0

S(2:0)

A3

8x1 MUX

D(7:0) Y

0

S(2:0)

2x1x4 MUX

D3(7:0)

A0

8x1 MUX

S

D0,0

D0,1

D0,2

D0,3

D1,0

D1,1

D1,2

D1,3

D(7:0) Y

0

S(2:0)

2x1x4 MUX

D0(8)

D1(8)

D2(8)

D3(8)

D0(9)

D1(9)

D2(9)

D3(9)

S

D0,0

D0,1

D0,2

D0,3

D1,0

D1,1

D1,2

D1,3

Y0

Y1

Y2

Y3

O0

O1

O2

O3

Y0

Y1

Y2

Y3

3-42.*

8x1 MUX

D(7:0)

D(7:0) Y

0

A(2:0)

S(2:0)

8x1 MUX

D(14:8)

D(6:0) Y

0

D(7)

S(2:0)

A(3)

3 OR gates

3-43.*

A1

0

0

0

0

1

1

1

1

A0

0

0

1

1

0

0

1

1

E

0

1

0

1

0

1

0

1

D0

0

1

0

0

0

0

0

0

D1

0

0

0

1

0

0

0

0

D2

0

0

0

0

0

1

0

0

D3

0

0

0

0

0

0

0

1

Consider E as the data input and A0, A1 as the

select lines. For a given combination on (A1,

A0), the value of E is distributed to the corresponding D output. For example for (A1, A0) =

(10), the value of E appears on D2, while all other

outputs have value 0.

39

Problem Solutions Chapter 3

3-44.

DECODER

A0

A1

A2

X

Y

Z

0

1

2

3

4

5

6

7

F1

F2

F3

3-45.

a) LR = LTBL + LTBR + EMBL = BL(LT + EM) + LTBR

RR = RTBL + RTBR + EMBL = BR(RT + EM) + RTBR

b) Maximum of four inputs on OR gates assumed.

LT EM BR BL LR

0

0

0

0

0

0

0

0

1

0

0

0

1

0

1

0

0

1

1

1

0

1

0

0

0

0

1

0

1

1

0

1

1

0

1

0

1

1

1

1

1

0

0

0

0

1

0

0

1

1

1

0

1

0

0

1

0

1

1

1

1

1

0

0

0

1

1

0

1

1

1

1

1

0

0

1

1

1

1

1

BL

BR

EM

LT

DECODER

0

A0

1

A1

2

A2

A3

3

4

5

6

7

8

9

10

11

12

13

14

15

LR

For RR, same circuit with LT replace by RT.

3-46.

A

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

B

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

C

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

D

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

F

0

0

1

0

1

0

1

0

0

1

1

1

0

0

0

1

C

B

A

F=0

D

F=D

VDD

F=D

F=D

F=D

F=1

F=0

F=D

40

8 x 1 MUX

S0

S1

S2

D0

D1

D2

D3

D4

D5

D6

D7

Problem Solutions Chapter 3

3-47.*

A

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

B

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

C

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

D

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

C

D

F

0

1

0

1

1

0

0

0

0

0

0

1

1

1

1

1

F=D

B

A

F=C D

D0

D1

D2

D3

VDD

F=C D

F=1

3-48.

DECODER

D

C

B

A0

A1

A2

EN

0

1

2

3

4

5

6

7

DECODER

D

C

B

A0

A1

A2

EN

4 x 1 MUX

S0

S1

0

1

2

3

4

5

6

7

41

S-ar putea să vă placă și

- James Ruse 2008 Year 10 Maths Yearly & SolutionsDocument16 paginiJames Ruse 2008 Year 10 Maths Yearly & SolutionsRicha Ng50% (2)

- ATI TEAS Calculation Workbook: 300 Questions to Prepare for the TEAS (2023 Edition)De la EverandATI TEAS Calculation Workbook: 300 Questions to Prepare for the TEAS (2023 Edition)Încă nu există evaluări

- Instructor's Manual to Accompany CALCULUS WITH ANALYTIC GEOMETRYDe la EverandInstructor's Manual to Accompany CALCULUS WITH ANALYTIC GEOMETRYÎncă nu există evaluări

- Solution Manual of Digital Logic and Computer Design (2nd Edition) Morris Mano PDFDocument40 paginiSolution Manual of Digital Logic and Computer Design (2nd Edition) Morris Mano PDFSadaf Rasheed0% (4)

- Pure Maths Unit 1 Paper 1 2013Document10 paginiPure Maths Unit 1 Paper 1 2013KingBee1123100% (1)

- Form 5 Additional Maths NoteDocument10 paginiForm 5 Additional Maths NoteEric WongÎncă nu există evaluări

- Answers to Selected Problems in Multivariable Calculus with Linear Algebra and SeriesDe la EverandAnswers to Selected Problems in Multivariable Calculus with Linear Algebra and SeriesEvaluare: 1.5 din 5 stele1.5/5 (2)

- RCF Art310a Base Amp Art Series Se515666 2005Document3 paginiRCF Art310a Base Amp Art Series Se515666 2005tlw72100% (1)

- Analytic Geometry: Graphic Solutions Using Matlab LanguageDe la EverandAnalytic Geometry: Graphic Solutions Using Matlab LanguageÎncă nu există evaluări

- NMTC 2013Document11 paginiNMTC 2013lay50% (2)

- KVPY SA SolutionsDocument24 paginiKVPY SA SolutionsawaninderÎncă nu există evaluări

- BMW Motronic Siemens Ms40 Ecu (Data Sheet)Document3 paginiBMW Motronic Siemens Ms40 Ecu (Data Sheet)81968Încă nu există evaluări

- Logic and Computer Design M Mano SolDocument42 paginiLogic and Computer Design M Mano Soltareen372aÎncă nu există evaluări

- Electronic PanelDocument1 paginăElectronic PanelMahmoud ElgabryÎncă nu există evaluări

- Sol 5Document13 paginiSol 5ee206023Încă nu există evaluări

- (CSM51A / EE16 S10) Solutions For Midterm: Problem Points Score 1 15 2 10 3 20 4 20 5 15 6 20 Total 100Document10 pagini(CSM51A / EE16 S10) Solutions For Midterm: Problem Points Score 1 15 2 10 3 20 4 20 5 15 6 20 Total 100krazykrnxboyÎncă nu există evaluări

- DLD Chpater 2Document11 paginiDLD Chpater 2Patrick FeghaliÎncă nu există evaluări

- Math Sample Paper-1 (With Solutions)Document21 paginiMath Sample Paper-1 (With Solutions)Veeresh SavadiÎncă nu există evaluări

- Solutions 2 MatricesDocument10 paginiSolutions 2 MatricesMarlon VellaÎncă nu există evaluări

- KVPY 2011 Stream SB SX Solved PaperDocument40 paginiKVPY 2011 Stream SB SX Solved PaperAnkitKambojÎncă nu există evaluări

- Math Home ExamDocument18 paginiMath Home ExamBikram ShresthaÎncă nu există evaluări

- Higher QA 2008 With SolutionsDocument36 paginiHigher QA 2008 With Solutionsrajdeepghai5607Încă nu există evaluări

- Proctored Mock 1 SolutionDocument10 paginiProctored Mock 1 Solutiontheholyghost5989Încă nu există evaluări

- Class X Maths P1 PDFDocument8 paginiClass X Maths P1 PDFSoniyaKanwalGÎncă nu există evaluări

- Homework 1 Solution: 1 6 11 1 Bits 2 1 2047 25 1 Bits 2 1 33,554,431Document16 paginiHomework 1 Solution: 1 6 11 1 Bits 2 1 2047 25 1 Bits 2 1 33,554,431Rahul GuptaÎncă nu există evaluări

- Chapter 04Document33 paginiChapter 04Iqbal Ashfaq Joiya100% (1)

- NSTSE 2015 Class 11 PCM Answer Key & SolutionDocument9 paginiNSTSE 2015 Class 11 PCM Answer Key & SolutionMota ChashmaÎncă nu există evaluări

- 20 CSEC - Past Year Paper Solution 2019-2020 Sem 1 CE/CZ 1005 Digital LogicDocument7 pagini20 CSEC - Past Year Paper Solution 2019-2020 Sem 1 CE/CZ 1005 Digital Logicmohor.banerjeeÎncă nu există evaluări

- (1031) DPP 11 Matrices Determinant and Trigonometry B.PDF - TMP PDFDocument14 pagini(1031) DPP 11 Matrices Determinant and Trigonometry B.PDF - TMP PDFNikhil MittalÎncă nu există evaluări

- Vls I SolutionDocument60 paginiVls I SolutionOla Gf OlamitÎncă nu există evaluări

- Test Q: Section A: A1) Find The Value of X For The Following EquationDocument13 paginiTest Q: Section A: A1) Find The Value of X For The Following EquationKapeel PokhrelÎncă nu există evaluări

- KmapDocument38 paginiKmapPECMURUGANÎncă nu există evaluări

- DLD 2nd Chapter KeyDocument15 paginiDLD 2nd Chapter KeyAnnas AfzalÎncă nu există evaluări

- S. No Questions Solutions Sol: 1 (B) : Poornima University. For Any Query, Contact Us At: 8875666617,18Document6 paginiS. No Questions Solutions Sol: 1 (B) : Poornima University. For Any Query, Contact Us At: 8875666617,18Vaibhav SinghÎncă nu există evaluări

- IIFT Sample Test SolutionDocument12 paginiIIFT Sample Test SolutionrafaadalviÎncă nu există evaluări

- HKMO1992heatans PDFDocument11 paginiHKMO1992heatans PDFChai Usajai UsajaiÎncă nu există evaluări

- 2011Pro2Serve Tennessee Math ContestDocument7 pagini2011Pro2Serve Tennessee Math ContestBHAAJI0001Încă nu există evaluări

- 7361 June 2009 MSDocument23 pagini7361 June 2009 MSAqibur RahmanÎncă nu există evaluări

- Mat133y Final 2009wDocument8 paginiMat133y Final 2009wexamkillerÎncă nu există evaluări

- DELD - Short Answer Questions and AnswersDocument23 paginiDELD - Short Answer Questions and AnswersPasupuleti Venkata RamanaÎncă nu există evaluări

- 2009 BmathDocument14 pagini2009 BmathAK The Tuber's CafeÎncă nu există evaluări

- Final AMTI NMTC 2014 Junior Level - Bhaskara Contest - IX X STD PDFDocument7 paginiFinal AMTI NMTC 2014 Junior Level - Bhaskara Contest - IX X STD PDFVijay KumarÎncă nu există evaluări

- Business MathematicsDocument14 paginiBusiness MathematicsamityscribdÎncă nu există evaluări

- KVPY 2015 Stream SB SX SolutionsDocument39 paginiKVPY 2015 Stream SB SX SolutionsCompetitive TutorialÎncă nu există evaluări

- IIT JAM 2012 Paper MathematicsDocument41 paginiIIT JAM 2012 Paper MathematicsacÎncă nu există evaluări

- April 2004Document15 paginiApril 2004vikramkolanuÎncă nu există evaluări

- Digital Logic by NODIADocument49 paginiDigital Logic by NODIAJyoti GoswamiÎncă nu există evaluări

- Solution ManualDocument14 paginiSolution ManualdattadhanweÎncă nu există evaluări

- Assignment 1Document8 paginiAssignment 1Mohammad NasserÎncă nu există evaluări

- Arth CirDocument105 paginiArth Cirnoor_dcetÎncă nu există evaluări

- Rajagiri School of Engineering and Technology: Rajagiri Valley, Kakkanad. Third SemesterDocument37 paginiRajagiri School of Engineering and Technology: Rajagiri Valley, Kakkanad. Third SemesterAmrita VenkitaramaniÎncă nu există evaluări

- Answer: X - Y 0010001Document12 paginiAnswer: X - Y 0010001GanesamoorthyÎncă nu există evaluări

- 14 DETEMINANTS & MATRICES PART 3 of 6 PDFDocument10 pagini14 DETEMINANTS & MATRICES PART 3 of 6 PDFsabhari_ramÎncă nu există evaluări

- Answers and Explanations: Proctored Mock CAT-5 2011Document10 paginiAnswers and Explanations: Proctored Mock CAT-5 2011Anshuman SharmaÎncă nu există evaluări

- Ten-Decimal Tables of the Logarithms of Complex Numbers and for the Transformation from Cartesian to Polar Coordinates: Volume 33 in Mathematical Tables SeriesDe la EverandTen-Decimal Tables of the Logarithms of Complex Numbers and for the Transformation from Cartesian to Polar Coordinates: Volume 33 in Mathematical Tables SeriesÎncă nu există evaluări

- Tapes To Complete Your Toolkit: Rubber, Mastic and Specialty Tapes Application GuideDocument17 paginiTapes To Complete Your Toolkit: Rubber, Mastic and Specialty Tapes Application GuideTalha YasinÎncă nu există evaluări

- Computation of K: Design Methods: Dr. Abdul Qayyum KhanDocument22 paginiComputation of K: Design Methods: Dr. Abdul Qayyum KhanTalha YasinÎncă nu există evaluări

- © 2008 Pearson Education, Inc.: Verification of Demorgan'S Theorem + +Document11 pagini© 2008 Pearson Education, Inc.: Verification of Demorgan'S Theorem + +Talha YasinÎncă nu există evaluări

- Control System Design in State-SpaceDocument15 paginiControl System Design in State-SpaceTalha YasinÎncă nu există evaluări

- CDS IiDocument48 paginiCDS IiTalha YasinÎncă nu există evaluări

- Transcript Exponentials enDocument8 paginiTranscript Exponentials enTalha YasinÎncă nu există evaluări

- Physics in Nuclear Medicine: James A. Sorenson, PH.DDocument10 paginiPhysics in Nuclear Medicine: James A. Sorenson, PH.DTalha YasinÎncă nu există evaluări

- Growing Exponentials: A Teacher's Guide: Square NumberDocument2 paginiGrowing Exponentials: A Teacher's Guide: Square NumberTalha YasinÎncă nu există evaluări

- DRG PLC1Document16 paginiDRG PLC1ZubedÎncă nu există evaluări

- Ductos - PDF 2Document1 paginăDuctos - PDF 2KEVIN ESTRADA ECÎncă nu există evaluări

- DM Industrial, C.A.: 28/6/2021 Stock Y PreciosDocument5 paginiDM Industrial, C.A.: 28/6/2021 Stock Y PreciosEukaris PintoÎncă nu există evaluări

- VB-HD EngDocument4 paginiVB-HD EngYudes LiyanageÎncă nu există evaluări

- TH2Document7 paginiTH2api-3820722Încă nu există evaluări

- X5 X6 X7 X8 X9 X10 X11 X12 X13 X14 X15 X16 X17 X18Document1 paginăX5 X6 X7 X8 X9 X10 X11 X12 X13 X14 X15 X16 X17 X18Lê Huy HòaÎncă nu există evaluări

- Concentrado 2022Document658 paginiConcentrado 2022Ramon Perez RivadeneyraÎncă nu există evaluări

- 7th and 13th Floor PlanDocument1 pagină7th and 13th Floor PlanRishiraj MarneÎncă nu există evaluări

- COM128Document1 paginăCOM128ĐỗHoàngTuấnÎncă nu există evaluări

- Drainage PLANDocument1 paginăDrainage PLANSanjula MaheshwariÎncă nu există evaluări

- MRF NBP 25-04-2012Document14 paginiMRF NBP 25-04-2012AanchalMehraÎncă nu există evaluări

- Aman 1Document1 paginăAman 1Aman YadavÎncă nu există evaluări

- Stepenovanje: Aa A ADocument4 paginiStepenovanje: Aa A AMaja SokolovicÎncă nu există evaluări

- Icom Ic-Pw1 Service Manual AddendumDocument201 paginiIcom Ic-Pw1 Service Manual AddendumDaveÎncă nu există evaluări

- Tarifas AlmesaDocument112 paginiTarifas AlmesaMiguel PlazaÎncă nu există evaluări

- Vasavi Sarovar Floor Plans Booklet - 06th SeptDocument11 paginiVasavi Sarovar Floor Plans Booklet - 06th SeptBrajesh Kumar AnupamÎncă nu există evaluări

- Monotron SchematicDocument1 paginăMonotron SchematicmrsemaineÎncă nu există evaluări

- TS100 V2.46 Schematic Diagram V1.0 PDFDocument1 paginăTS100 V2.46 Schematic Diagram V1.0 PDFnitroboozter100% (1)

- Crest Audio P2500 SCH PDFDocument7 paginiCrest Audio P2500 SCH PDFmiltoncgÎncă nu există evaluări

- Crest CA12 PwrampDocument15 paginiCrest CA12 Pwrampcarlos dutraÎncă nu există evaluări

- MW1580 Esquema ElétricoDocument1 paginăMW1580 Esquema Elétricoapi-3711045100% (1)

- TT Exercise 2 27Document54 paginiTT Exercise 2 27pallavi.cseÎncă nu există evaluări

- Power Supply Skyworth 8M51BDocument1 paginăPower Supply Skyworth 8M51BautreraÎncă nu există evaluări

- 210-Vijak M5 8H7 PR 1Document6 pagini210-Vijak M5 8H7 PR 1milanropcevicÎncă nu există evaluări

- Alex Internship ReportDocument77 paginiAlex Internship ReportdamarismagererÎncă nu există evaluări

- Schematic DiagramDocument1 paginăSchematic Diagrambakadesu senpaitachiÎncă nu există evaluări

- Plan2014 Bidart PDFDocument1 paginăPlan2014 Bidart PDFcÎncă nu există evaluări