Documente Academic

Documente Profesional

Documente Cultură

An1958 PDF

Încărcat de

සම්පත් චන්ද්රරත්නTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

An1958 PDF

Încărcat de

සම්පත් චන්ද්රරත්නDrepturi de autor:

Formate disponibile

Freescale Semiconductor

Application Note

3-Phase AC Motor Control

with V/Hz Speed Closed

Loop Using the 56F800/E

Design of a Motor Control Application Based on

Processor Expert

1.

Introduction

This application note describes the design of a 3-phase AC

induction motor drive with Volts per Hertz control in closed-loop

(V/Hz CL). It is based on Freescales 56F800/E microcontrollers,

which are ideal for motor control applications. The system is

designed as a motor control system for driving medium-power,

3-phase AC induction motors. The part is targeted toward

applications in both the industrial and home appliance industries,

such as washing machines, compressors, air conditioning units,

pumps, or simple industrial drives.

The drive introduced here is intended as an example of a 3-phase

AC induction motor drive. The drive serves as an example of AC

V/Hz motor control system design using Freescales controller

with Processor ExpertTM (PE) support.

This document includes the basic motor theory, system design

concept, hardware implementation, and software design,

including the PC master software visualization tool inclusion.

2.

Freescale Controller Advantages

and Features

The Freescale 56F800/E families are ideal for digital motor

control, combining the DSPs calculation capability with the

MCUs controller features on a single chip. These controllers

offer a rich dedicated peripherals set, such as Pulse Width

Modulation (PWM) modules, Analog-to-Digital Converter

(ADC), timers, communication peripherals (SCI, SPI, CAN),

on-board Flash and RAM. Several parts comprise the family:

56F80x with different peripherals and on-board memory

configurations. Generally, all are suited for motor control.

Freescale Semiconductor, Inc., 2004, 2005. All rights reserved.

AN1958

Rev. 0, 07/2005

Contents

1. Introduction ......................................... 1

2. Freescale Controller Advantages and

Features ......................................... 1

3. Target Motor Theory .......................... 3

3.1 3-phase AC Induction Motor Drives3

3.2 Volts per Hertz Control................... 5

3.3 Speed Closed-Loop System ............ 6

4. System Design Concept ...................... 7

5. Hardware ........................................... 10

5.1 System Outline.............................. 10

5.2 High-Voltage Hardware Set.......... 10

6. Software Design ................................ 12

6.1 Data Flow...................................... 12

6.1.1 Acceleration/Deceleration

Ramp......................................... 13

6.1.2 Speed Measurement.................. 13

6.1.3 PI Controller ............................. 13

6.1.4 V/Hz Ramp ............................... 13

6.1.5 DCBus Voltage Ripple

Elimination ............................... 14

6.1.6 PWM Generation...................... 16

6.1.7 Fault Control............................. 18

7. Software implementation .................. 19

7.1 Embedded Beans........................... 19

7.2 Bean Modules ............................... 19

7.2.1 Initialization.............................. 30

7.3 State Diagram................................ 30

7.3.1 Application State Machine ....... 32

7.3.2 Check Run/Stop Switch............ 32

8. PC Master Software .......................... 32

9. References ......................................... 34

Freescale Controller Advantages and Features

A typical member of the 56F800 family, the 56F805, provides the following peripheral blocks:

Two Pulse Width Modulators (PWMA & PWMB), each with six PWM outputs, three current status

inputs, and four fault inputs, fault-tolerant design with dead time insertion; supports both center- and

edge- aligned modes

Two 12-bit, Analog-to-Digital Converters (ADCs), supporting two simultaneous conversions with

dual 4-pin multiplexed inputs; can be synchronized by PWM modules

Two quadrature decoders (Quad Dec0 & Quad Dec1), each with four inputs, or two additional quad

timers (A & B)

Two dedicated general-purpose quad timers totalling six pins: Timer C with two pins and Timer D

with four pins

CAN 2.0 A/B module with 2-pin ports used to transmit and receive

Two Serial Communication Interfaces (SCI0 & SCI1), each with two pins, or four additional MPIO

lines

Serial Peripheral Interface (SPI), with configurable 4-pin port, or four additional MPIO lines

Computer Operating Properly (COP) timer

Two dedicated external interrupt pins

Fourteen dedicated multiple purpose I/O (MPIO) pins and 18 multiplexed MPIO pins

External reset pin for hardware reset

JTAG/on-chip emulation (OnCE)

Software-programmable, phase lock loop-based frequency synthesizer for the controller core clock

The Pulse Width Modulation (PWM) block offers high freedom in its configuration, enabling efficient control

of the AC induction motor.

The PWM block has the following features:

Three complementary PWM signal pairs, or six independent PWM signals

Features of complementary channel operation

Dead time insertion

Separate top and bottom pulse width correction via current status inputs or software

Separate top and bottom polarity control

Edge-aligned or center-aligned PWM reference signals

15 bits of resolution

Half-cycle reload capability

Integral reload rates from one to 16

Individual software-controlled PWM outputs

Programmable fault protection

Polarity control

20-mA current sink capability on PWM pins

Write-protectable registers

The PWM outputs are configured in the complementary mode in this application.

3-Phase AC Motor Control with V/Hz Speed Closed Loop, Rev. 0

2

Freescale Semiconductor

3-phase AC Induction Motor Drives

3.

Target Motor Theory

3.1 3-phase AC Induction Motor Drives

The AC induction motor is a workhorse with adjustable speed drive systems. The most popular type is the

3-phase, squirrel-cage AC induction motor. It is a maintenance-free, less noisy and efficient motor. The stator

is supplied by a balanced 3-phase AC power source.

The synchronous speed ns of the motor is calculated by:

120 f s

n s = ------------------p

[ rpm ]

(EQ 3-1.)

where fs is the synchronous stator frequency in Hz, and p is the number of stator poles. The load torque is

produced by slip frequency. The motor speed is characterized by a slip sr:

n sl

( ns nr )

s r = -------------------- = -----ns

ns

[-]

(EQ 3-2.)

where nr is the rotor mechanical speed and nsl is the slip speed, both in rpm. Figure 3-1 illustrates the torque

characteristics and corresponding slip. As can be seen from EQ 3-1 and EQ 3-2, the motor speed is controlled

by variation of a stator frequency with the influence of the load torque.

Figure 3-1. Torque-Speed Characteristic at Constant Voltage and Frequency

3-Phase AC Motor Control with V/Hz Speed Closed Loop, Rev. 0

Freescale Semiconductor

Target Motor Theory

In adjustable speed applications, the AC motors are powered by inverters. The inverter converts DC power to

AC power at required frequency and amplitude. The typical 3-phase inverter is illustrated in Figure 3-2.

Figure 3-2. 3- Phase Inverter

The inverter consists of three half-bridge units; the upper and lower switches are controlled complementarily,

which means that when the upper one is turned on, the lower one must be turned off and vice versa. As the

power devices turn-off time is longer than its turn-on time, some dead time must be inserted between the

turn-off of one transistor of the half-bridge and the turn-on of its complementary device. The output voltage is

mostly created by a Pulse Width Modulation (PWM) technique, where an isosceles triangle carrier wave is

compared with a fundamental-frequency sine modulating wave, and the natural points of intersection

determine the switching points of the power devices of a half bridge inverter. This technique is shown in

Figure 3-3. The 3-phase voltage waves are shifted 120o to each other and thus a 3-phase motor can be

supplied.

3-Phase AC Motor Control with V/Hz Speed Closed Loop, Rev. 0

4

Freescale Semiconductor

Volts per Hertz Control

Figure 3-3. Pulse Width Modulation

The most popular power devices for motor control applications are Power MOSFETs and IGBTs.

A Power MOSFET is a voltage-controlled transistor. It is designed for high-frequency operation and has a low

voltage drop, resulting in low-power losses. However, the saturation temperature sensitivity limits the

MOSFET application in high-power applications.

An Insulated Gate Bipolar Transistor (IGBT) is a bipolar transistor controlled by a MOSFET on its base. The

IGBT requires low-drive current, has fast switching time, and is suitable for high-switching frequencies. The

disadvantage is the higher voltage drop of the bipolar transistor, causing higher conduction losses.

3.2 Volts per Hertz Control

The Volts per Hertz control method, the most popular technique of Scalar Control, controls the magnitude of

such variables as frequency, voltage or current. The command and feedback signals are DC quantities, and are

proportional to the respective variables.

The purpose of the Volts per Hertz control scheme is to maintain the air-gap flux of AC induction motor in

constant, achieving higher run-time efficiency. In steady-state operation, the machine air-gap flux is

approximately related to the ratio Vs/fs, where Vs is the amplitude of motor phase voltage and fs is the

synchronous electrical frequency applied to the motor. The control system is illustrated in Figure 3-4. The

characteristic is defined by the base point of the motor. Below the base point, the motor operates at optimum

excitation due to the constant Vs/fs ratio. Above this point, the motor operates under-excited because of the

DCBus voltage limit.

A simple closed-loop Volts per Hertz speed control for an induction motor is the control technique targeted for

low-performance drives. This basic scheme is unsatisfactory for more demanding applications, where speed

precision is required.

3-Phase AC Motor Control with V/Hz Speed Closed Loop, Rev. 0

Freescale Semiconductor

Target Motor Theory

Figure 3-4. Volts per Hertz Control Method

3.3 Speed Closed-Loop System

To improve system performance, a closed-loop Volts per Hertz control was introduced. In this method, a speed

sensor measures the actual motor speed and the system takes this input into consideration. A number of

applications use the closed-loop Volts per Hertz method because of its simple and relatively good speed

accuracy, but it is not suitable for systems requiring servo performance or excellent response to highly dynamic

torque/speed variations.

Figure 3-5 illustrates the general principle of the speed PI control loop.

Reference

Speed

(Omega_required)

Speed

Error

PI

Controller

Corrected

Speed

(Omega_command)

Controlled

System

Actual Motor

Speed

(Omega_actual)

Figure 3-5. Closed Loop Control System

The speed closed-loop control is characterized by the measurement of the actual motor speed. This information

is compared with the reference speed while the error signal is generated. The magnitude and polarity of the

error signal correspond to the difference between the actual and required speed. Based on the speed error, the

PI controller generates the corrected motor stator frequency to compensate for the error.

In an AC V/Hz closed-loop application, the feedback speed signal is derived from the incremental encoder

using the Quadrature Decoder. The speed controller constants have been experimentally tuned according to the

actual load.

3-Phase AC Motor Control with V/Hz Speed Closed Loop, Rev. 0

6

Freescale Semiconductor

Speed Closed-Loop System

4.

System Design Concept

The system is designed to drive a 3-phase AC induction motor. The application meets the following

performance specifications:

Targeted for 56F800/E EVM platforms

Running on 3-phase ACIM motor control development platform at variable line voltage 115 - 230V

AC

Control technique incorporates

motoring and generating mode

bi-directional rotation

V/Hz speed closed-loop

Manual interface (Start/Stop switch, Up/Down push button speed control, LED indication)

PC master software interface (motor start/stop, speed set-up)

Power stage identification

Overvoltage, undervoltage, overcurrent, and overheating fault protection

The AC drive introduced here is designed as a system that meets the general performance requirements in

Table 4-1.

Table 4-1. Motor / Drive Specification

Motor Characteristics

Drive Characteristics

Load Characteristic

Motor Type

Four poles

3-Phase, star-connected, squirrel cage

AC motor (standard industrial motor)

Speed Range

< 5000rpm

Base Electrical Frequency

50Hz

Max. Electrical Power

180 W

Delta Voltage (rms)

200V (Star)

Transducers

IRC -1024 pulses per revolution

Speed Range

<2250 rpm @ 230 V

<1200 rpm @ 115 V

Line Input

230V / 50Hz AC

115V / 60Hz AC

Maximum DCBus Voltage

400V

Control Algorithm

Closed-Loop Control

Optoisolation

Required

Type

Varying

The controller runs the main control algorithm and generates 3-phase PWM output signals for the motor

inverter according to the users interface input and feedback signals.

3-Phase AC Motor Control with V/Hz Speed Closed Loop, Rev. 0

Freescale Semiconductor

System Design Concept

A standard system concept is chosen for the drive, illustrated in Figure 4-1. The system incorporates the

following hardware boards:

Power supply rectifier

3-phase inverter

Feedback sensors:

Speed

DCBus voltage

DCBus current

Temperature

Optoisolation

Evaluation board

3-Phase AC Motor Control with V/Hz Speed Closed Loop, Rev. 0

8

Freescale Semiconductor

Speed Closed-Loop System

Rectifier

Three-Phase Inverter

Line

Voltage

230V/50Hz

DC-Bus

3 -p h

AC M

=

Isolation Barrier

Optoisolation

Optoisolation

Over Current

&

Over Voltage

Temperature

&

DC-Bus Voltage

Temperature

& Voltage

Processing

IRC

Temperature,

Current &

Voltage Sensing

ADC

PWM

Faults

Processing

DC Bus Voltage

V/Hz

PI

Regulator

Speed

Set-up

V1 DC-Bus V2

Ripple

Cancel.

PWM

Generator

with

Dead Time

E

Speed

Command

Processing

Actual Speed

Speed Processing

(Incremental Decoder)

DSP56F80x

Figure 4-1. System Concept

3-Phase AC Motor Control with V/Hz Speed Closed Loop, Rev. 0

Freescale Semiconductor

Hardware

The Control Process:

When the start command is accepted, using the Start/Stop switch, the state of the inputs is periodically

scanned. According to the state of the control signals (Start/Stop switch, speed up/down buttons or PC master

software set speed), the speed command is calculated using an acceleration/deceleration ramp.

The comparison between the actual speed command and the measured speed generates a speed error, E. The

speed error is brought to the speed PI controller, which generates a new corrected motor stator frequency. With

the use of the V/Hz ramp, the corresponding voltage is calculated and then DCBus ripple cancellation function

then eliminates the influence of the DCBus voltage ripples to the generated phase voltage amplitude. The

PWM generation process calculates a 3-phase voltage system at the required amplitude and frequency,

including dead time. Finally, the 3-phase PWM motor control signals are generated.

The DCBus voltage and power stage temperature are measured during the control process. They protect the

drive from overvoltage, undervoltage, and overheating. Both undervoltage protection and overheating are

performed by ADC and software, while the DCBus overcurrent and overvoltage fault signals are connected to

PWM fault inputs.

If any of the above-mentioned faults occurs, the motor control PWM outputs are disabled to protect the drive

and the fault state of the system is displayed in PC master software control page.

5.

Hardware

5.1 System Outline

The motor control system is designed to drive the 3-phase AC motor in a speed-closed loop.

Software is targeted for these controllers and evaluation modules (EVMs):

56F805

56F8346

The hardware set-up depends on the evaluation module (EVM) module used.

The software can run only on the high-voltage hardware set described in Section 5.2.

Other power module boards will be denied, due to the board identification build in the software. This feature

protects misuse of hardware module.

The hardware set-up is shown in Figure 4-1, but it can also be found in the documentation for the device being

implemented.

5.2 High-Voltage Hardware Set

The system configuration is shown in Figure 5-1.

3-Phase AC Motor Control with V/Hz Speed Closed Loop, Rev. 0

10

Freescale Semiconductor

High-Voltage Hardware Set

+12VDC

40w flat ribbon

cable, gray

U3

L

Black

Light Blue

PE

Green-Yellow

J11.1

J11.2

3ph AC/BLDC

High Voltage

Power Stage

GND

40w flat ribbon

cable, gray

U2

U1

JP1.1 JP1.2

J14

J1

Optoisolation

Board

Controller Board

J2

J1

ECOPT

J13.1 J13.2 J13.3

MB1

BlaW hi

ck te Red

Motor-Brake

AM40V

6 pin conn.

AMP A2510

ECOPTHIVACBLDC

Encoder Conn. Table

SG40N

Controler

56F803

56F805

56F807

J5

W hiBla

Re te ck

d

Incremental Encoder

Baumer Electric

BHK16.05A

1024-I2-5

Hall Sensor

Encoder

00126A

Conn.

J2

J23

J4

ECMTRHIVAC

Not used in

application

Incremental Encoder Cable -> Connector Table

Cable Wire Color

Desc.

Brown

White, Shielding

Green

Yellow

Pink

Unused

+5VDC

Ground and Shielding

Phase A

Phase B

Index

Unused

Figure 5-1. High-Voltage Hardware System Configuration

All the system parts are supplied and documented according the following references:

U1 - Controller board:

Supplied as: 56F80x or 56F83xx EVM

Described in: the 56F80x or 56F83xx Evaluation Module Hardware Users Manual for the

device being implemented

U2 - 3-phase AC/BLDC high-voltage power stage

Supplied in kit with optoisolation board, Order # ECOPTHIVACBLDC

Described in: Described in: 3-Phase Brushless DC High-Voltage Power Stage, Order #

MEMC3BLDCPSUM/D

U3 - Optoisolation board

Supplied with 3-phase AC/BLDC high-voltage power stage, Order # ECOPTHIVACBLDC

or

Supplied alone, Order # ECOPT

Described in: Optoisolation Board Users Manual

MB1 motor-brake AM40V + SG40N

Order # ECMTRHIVAC

Warning: It is strongly recommended that you use optoisolation (optocouplers and optoisolation

amplifiers) during development to avoid any damage to the development equipment.

Note:

A detailed description of individual boards can be found in the comprehensive users

manual for each board. The manual incorporates the schematic of the board, a

description of individual function blocks, and a bill of materials. Individual boards can be

ordered from Freescale as a standard product; see Section 9. for information.

3-Phase AC Motor Control with V/Hz Speed Closed Loop, Rev. 0

Freescale Semiconductor

11

Software Design

6.

Software Design

This section describes the design of the drives software blocks and includes data flow and state diagrams.

6.1 Data Flow

The drives requirements dictate that the software gather values from the user interface and sensors, process

them, and generate 3-phase PWM signals for the inverter.

The control algorithm of the closed-loop AC drive is described in Figure 6-1. The control algorithms

processes are described in the following subsections. The detailed description is given to the subroutines

3-phase PWM calculation and Volts per Hertz control algorithm.

PC

MASTER

Temperature DCBus Voltage

(A/D)

(A/D)

SPEED

SETTING

Omega_desired

u_dc_bus

INCREMENTAL

ENCODER

Speed Measurement

Acceleration/Deceleration Ramp

Omega_actual

Omega_required

Temperature

PI Controller

Omega_command

Fault Control

V/Hz Ramp

Drive Fault Status

PWM Faults

AmplitudeVoltScale

DCBus Voltage Ripple Elimination

(Overvoltage/Overcurrent)

Amplitude

PWM Generation

PVAL0

PVAL2

PVAL4

Figure 6-1. Data Flow

3-Phase AC Motor Control with V/Hz Speed Closed Loop, Rev. 0

12

Freescale Semiconductor

Data Flow

6.1.1 Acceleration/Deceleration Ramp

The process calculates the new actual speed command based on the required speed and according to the

acceleration/deceleration ramp. The desired speed is determined either by push buttons or by the PC master

software.

During deceleration, the motor can work as a generator. In the generator state, the DCBus capacitor is charged

and its voltage can easily exceed its maximum voltage. Therefore, the voltage level in the DCBus link is

controlled by a resistive brake, operating in case of overvoltage.

The process input parameter is Omega_desired, the desired speed.

The process output parameter is Omega_required, used as an input parameter of the PWM generation process.

6.1.2 Speed Measurement

The speed measurement process uses the on-chip Quadrature Decoder. The process output is MeasuredSpeed,

and is only used as an information value in PC master software.

6.1.3 PI Controller

The PI controller process takes the input parameters, actual speed command Omega_required, and actual

motor speed, measured by a incremental encoder Omega_actual, then calculates a speed error and performs the

speed PI control algorithm. The output of the PI controller is a frequency of the first harmonic sine wave to be

generated by the inverter, Omega_command.

6.1.4 V/Hz Ramp

The drive is designed as a Volts per Hertz drive, which means the control algorithm keeps the constant motors

magnetizing current (flux) by varying the stator voltage with frequency. A commonly used Volts per Hertz

ramp of a 3-phase AC induction motor is illustrated in Figure 6-2.

Figure 6-2. Volt per Hertz Ramp

3-Phase AC Motor Control with V/Hz Speed Closed Loop, Rev. 0

Freescale Semiconductor

13

Software Design

The Volts per Hertz ramp is defined by following parameters:

Base point - defined by fbase (usually 50Hz or 60Hz)

Boost point- defined by Vboostand fboost

Start point - defined by Vstart at zero frequency

The ramp profile fits to the specific motor and can be easily changed to accommodate different motors.

Process Description

This process provides voltage calculation according to Volts per Hertz ramp.

The input of this process is generated by desired inverter frequency, Omega_required.

The output of this process is AmplitudeVoltScale, a parameter required by DCBus voltage ripple elimination

process.

6.1.5 DCBus Voltage Ripple Elimination

Process Description

The voltage ripple elimination process eliminates the influence of the DCBus voltage ripples to the generated

phase voltage sine waves. In fact, it lowers the 50Hz or 60Hz acoustic noise of the motor. Another positive

aspect due to this function is the generated phase voltage, which is independent of the level of DCBus voltage,

making the application easily adapted to power supply systems worldwide.

The process is performed by the mcgenDCBVoltRippleElim method of the MC_WaveGenerate bean,

converting the phase voltage amplitude (AmplitudeVoltScale) to the sine wave amplitude (Amplitude), based

on the actual value of the DCBus voltage (u_dc_bus) and the inverse value of the modulation index

(ModulationIndexInverse).

The modulation index is the ratio between the maximum amplitude of the first harmonic of the phase voltage

(in voltage scale) and half of the DCBus voltage (in voltage scale), which is defined by the following formula:

(1)

U phasemax

2

m i = ------------------------- = ------1--3

u

2 DCBus

(EQ 6-1.)

The modulation index is specific to a given 3-phase generation algorithm; in this application, it is 1.27.

Note: The result of the modulation index is based on the 3rd harmonic injection PWM technique.

The first chart in Figure 6-3 demonstrates how the Amplitude (in scale of generated sine wave amplitude) is

counter-modulated to eliminate the DCBus ripples. The second chart delineates the duty cycles generated by

one of the 3-phase wave generation functions. The third chart contains symetrical sine waves of the

phase-to-phase voltages actually applied to the 3-phase motor.

3-Phase AC Motor Control with V/Hz Speed Closed Loop, Rev. 0

14

Freescale Semiconductor

Data Flow

0 .9 0

0 .8 0

0 .7 0

0 .6 0

0 .5 0

0 .4 0

0 .3 0

0 .2 0

u_dc_bus

0 .1 0

A m p litu d e V o lt S c a le [% U m a x ]

A m p litu d e

[% A m p l m a x ]

[% U m a x ]

0 .0 0

0 .9 0

0 .8 0

0 .7 0

0 .6 0

D u ty C y c le .P h a s e A

D u ty C y c le .P h a s e B

0 .5 0

D u ty C y c le .P h a s e C

0 .4 0

0 .3 0

0 .2 0

0 .1 0

0 .0 0

150

100

50

0

-5 0

-1 0 0

P h A -P h B [V ]

P h B -P h C [V ]

P h C -P h A [V ]

-1 5 0

Figure 6-3. 3-Phase Waveforms with DCBus Voltage Ripple Elimination

3-Phase AC Motor Control with V/Hz Speed Closed Loop, Rev. 0

Freescale Semiconductor

15

Software Design

6.1.6 PWM Generation

Process Description

This process generates a system of 3-phase sine waves with addition of third harmonic component shifted 120o

to each other using mcgen3PhWaveSine3rdHIntp function from the motor control function library.

The function is based on a fixed-wave table describing the first quadrant of sine wave stored in data memory of

the controller. Due to symmetry of sine function, data in other quadrants are calculated using the data of first

quadrant, which saves data memory. The sine wave generation for Phase A, simplicity, is explained in

Figure 6-4. Phases B and C are shifted 120o with respect to Phase A.

0x7fff

PhaseIncrement

ActualPhase(n-1)

amplitude

amplitude = 100%

ActualPhase(n)

0x4000

(DutyCycle.PhaseA)

0x0000

0x8000 = -180o

0x7fff = 180o

Figure 6-4. Sine Wave generation

3-Phase AC Motor Control with V/Hz Speed Closed Loop, Rev. 0

16

Freescale Semiconductor

Data Flow

Each time the waveform generation function is called, ActualPhase from previous step is updated by

PhaseIncrement, and, according to the calculated phase, the value of sine is fetched from the sine table by the

function tfr16SinPIxLUT, from the Trigonometric Function Library in Processor Expert. Its then multiplied

by amplitude and passed to the PWM. An explanation of the 3-phase waveform generation with 3rd harmonic

additionis found in the following formulas:

1

1

PWMA = ------- Amplitude sin + --- sin 3 + 0.5

6

3

1

1

PWMB = ------- Amplitude sin ( 120 0 ) + --- sin 3 + 0.5

6

3

(EQ 6-2.)

1

1

PWMC = ------- Amplitude sin ( 240 0 ) + --- sin 3 + 0.5

6

3

Where PWMA, PWMB and PWMC are calculated, duty cycles passed to the PWM driver and amplitude

determine the level of phase voltage amplitude.

The process performed in the PWM reload callback function, pwm_Reload_A_ISR, is accessed regularly at the

rate given by the set PWM reload frequency. This process is repeated often enough to compare it to the wave

frequency. Wave length comparisons are made to generate the correct wave shape. Therefore, for 16kHz PWM

frequency, it is called each fourth PWM pulse; thus, the PWM registers are updated in a 4kHz rate (every

250sec).

Figure 6-5 shows the duty cycles generated by the mcgen3PhWaveSine3rdHIntp function when Amplitude is 1

(100%).

1st Harmonic A

1.2

1st Harmonic B

1.1

1st Harmonic B

1.0

3rd Harmonic

DutyCycle.PhaseA

0.9

DutyCycle.PhaseB

0.8

DutyCycle.PhaseC

0.7

0.6

0.5

0.4

0.3

0.2

0.1

0.0

-0.1

-0.2

Figure 6-5. 3-Phase Sine Waves with 3rd Harmonic Injection, Amplitude = 100%

3-Phase AC Motor Control with V/Hz Speed Closed Loop, Rev. 0

Freescale Semiconductor

17

Software Design

Figure 6-6 defines the duty cycles generated by the mcgen3PhWaveSine3rdHIntp function when Amplitude is

0.5 (50%).

1st Harmonic A

1.2

1st Harmonic B

1.1

1st Harmonic B

1.0

3rd Harmonic

DutyCycle.PhaseA

0.9

DutyCycle.PhaseB

0.8

DutyCycle.PhaseC

0.7

0.6

0.5

0.4

0.3

0.2

0.1

0.0

-0.1

-0.2

Figure 6-6. 3-Phase Sine Waves with 3rd Harmonic Injection, Amplitude = 50%

Input process:

Amplitude is obtained from the DCBus ripple elimination process

Omega_required is obtained from acceleration/deceleration ramp process

Output process:

Results calculated by the mcgen3PhWaveSine3rdHIntp function are passed directly to the PWM value

registers using the PWM driver.

6.1.7 Fault Control

This process is responsible for fault handling. The software accommodates five fault inputs: overcurrent,

overvoltage, undervoltage, overheating and wrong identified hardware.

Overcurrent: If overcurrent occurs in the DCBus link, the external hardware provides a rising edge on the

controllers fault input pin, FAULTA1. This signal immediately disables all motor control PWM outputs

(PWM1 - PWM6) and sets the DC_Bus_OverCurrent bit of DriveFaultStatus variable.

Overvoltage: If overvoltage occurs in the DCBus link, the external hardware provides a rising edge on the

controllers fault input pin, FAULTA0. This signal immediately disables all motor control PWM outputs

(PWM1 - PWM6) and sets the DC_Bus_OverVoltage bit of DriveFaultStatus variable.

Undervoltage: The DCBus voltage sensed by ADC is compared with the limit set in the software. If

undervoltage occurs after a period defined by UNDERVOLTAGE_COUNT, all motor control PWM outputs

are disabled, and the DriveFaultStatus variable is set to DC_Bus_UnderVoltage.

3-Phase AC Motor Control with V/Hz Speed Closed Loop, Rev. 0

18

Freescale Semiconductor

Bean Modules

Overheating: The temperature of the power module sensed by ADC is compared with the limit set in the

software. If overheating occurs after a period defined by OVERHEATING_COUNT, all motor control PWM

outputs are disabled and the DriveFaultStatus variable is set to OverHeating.

Wrong Hardware: If the wrong hardware (for example, a different power module or missing optoisolation

board) is identified during initialization, the DriveFaultStatus variable is set to Wrong_Hardware.

If any of these faults occur, the program run into infinite loop and waits for reset. The fault is signaled by user

LEDs on the controller board and on the PC master software control screen.

7.

Software implementation

This project is implemented using Processor Expert plug-in and Embedded Beans technology in the

CodeWarrior Integrated Devolopment Environment (IDE). Processor Expert is designed for rapid application

development of embedded applications on many platforms.

7.1 Embedded Beans

Embedded Beans are design components which encapsulate functionality of basic elements of embedded

systems such as the controllers core; on-chip peripherals; stand-alone peripherals; virtual devices; and pure

software algorithms. Embedded Beans allow access to these facilities via simple and uniform interface of

properties, methods and events. Additional information can be found in Processor Expert help.

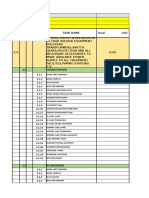

Table 7-1 lists the beans used in implementing the 56F805 application.

7.2 Bean Modules

Each peripheral on the controller chip or on the EVM board is accessible through a bean. Processor Expert

generates the source code modules containing the implementation of methods controlling the hardware which

provides the beans functionality.

The following steps are required to generate the code:

Add the beans to your project (Processor Expert tab of CodeWarriors project panel)

Set up the beans according to the hardware configuration

Generate the source code

Use beans methods in your code (generated functions for beans methods are named

beanName_MethodName)

You should not modify generated modules; generated code can be found in the Files folder of CodeWarriorss

project panel.

User modules, which are meant to be modified by the user, are found in the User Modules folder, where other

user modules could also be added. The Events module (events.c) contains the handling routines for beans

events, those caused by interrupt, for example. The Main module (projectName.c) contains the function main()

and all necessary declarations and variables.

3-Phase AC Motor Control with V/Hz Speed Closed Loop, Rev. 0

Freescale Semiconductor

19

Software implementation

All enabled methods are generated into appropriate bean modules during the code generation process. All

Methods of each bean inserted into the project are visible as a subtree of the bean in the Project panel

(Processor Expert tab of CodeWarriors project panel). Figure 7-1 and Figure 7-2 show the list of beans

inserted in the project for 56F805 and 56F8346 implementations. To see a detailed list of beans, see Table 7-1

and Table 7-2.

Figure 7-1. Beans Used in Implementing the 56F805

3-Phase AC Motor Control with V/Hz Speed Closed Loop, Rev. 0

20

Freescale Semiconductor

Bean Modules

Table 7-1. Beans Used in Implementing the 56F805

Bean name

Bean type

Description

PC_Master

PC_Master

Provides serial communication with the PC master software

running on a PC using the SCI0 on-chip device.

Communication speed is 9600bps.

UpButtonFD,

DownButtonFD

Button

Buttons are used for motor speed settings, with a 75rpm step.

Buttons are connected to IRQA and IRQB inputs.

Events:

LED1, LED2,

LED3

LED_Green, LED_Red,

LED_Yellow

Beans control the LEDs on the EVM connected to pins

GPIOB0, GPIOB1 and GPIOB2.

Methods:

SwitchFD

Switch_RUNSTOP

OnButton - Invoked by pressing the button

On - Switches the LED on

On - Switches the LED on

Toggle - Reverses the state of the LED

Sets the application state to RUN/STOP.

The bean uses the GPIOD5 input bit.

Methods:

Adc

ADC

GetVal - Reads the switch state

Measures the DCBus voltage and temperature.

The bean uses channels AD0 (voltage) and ADA5

(temperature) of the ADCA on-chip device.

Methods:

Measure - Start of the measurement (length of

the measurement is 1.7us)

GetChanValue - Reading of the measured value

from given channel

SetHighChanLimit - Sets the upper limit value for

a given channel

SetLowChanLimit - Sets lower limit value for a

given channel

Events:

OnEnd - End of conversion. This event watches

the values of voltage and temperature. When the

values overrun the allowed range, the motor is

disconnected.

OnHighLimit - Switches brake on

OnLowLimit - Switches brake off

3-Phase AC Motor Control with V/Hz Speed Closed Loop, Rev. 0

Freescale Semiconductor

21

Software implementation

Table 7-1. Beans Used in Implementing the 56F805 (Continued)

Bean name

Bean type

FC1

FreeCounter

Description

This timer bean watches the 100ms minimum delay between

presses of the Up and Down buttons.

The bean uses the on-chip device TMRD23.

TimerLED

TimerInt

This timer controls the LEDs blinking.

It uses the on-chip timer TMRA0.

Events:

TimerID

FreeCntr16

The timer used to identify hardware.

Methods:

TimerRamp

TimerInt

OnInterrupt - Toggles the LED on and off

Enable - Starts the timer

Disable - Disables the timer

The timer controlling the acceleration/decceleration ramp.

Methods:

Enable - Starts the timer

Events:

OnInterrupt - Sets the speed as needed

3-Phase AC Motor Control with V/Hz Speed Closed Loop, Rev. 0

22

Freescale Semiconductor

Bean Modules

Table 7-1. Beans Used in Implementing the 56F805 (Continued)

Bean name

Bean type

PwmFD

PWMMC

Description

Controls the state of the PWM module for motor applications.

Frequency of the PWM output is 16kHz; dead time is 2.5s.

Pulse width is controlled by the application.

Methods:

Enable - Enables PWM output

Disable - Disables PWM output

SetDuty - Sets duty on the appropriate PWM

channel

Load - Updates control registers

Swap - Swaps PWM pairs

OutputPadEnable - Enables signal output onto

CPU pins

OutputPadDisable - Disables signal output onto

CPU pins

Events:

Primary_UNI_3

PinIO

Onreload - This event:

Measures actual speed (MeasuredSpeed)

Eliminates DCBus voltage ripples

(mcgenDCBVoltRippleElim function)

Calculates waveform generator

(mcgen3PhWaveSine3rdHIntp function)

Updates PWM value registers

StartsADC conversion

OnFault0 - Switches the motor off and sets the

Overvoltage error flag

OnFault1 - Switches the motor off and sets the

Overcurrent error flag

Accesses the Primary Serial COM signal of

Primary UNI connector.

Uses the GPIOD7 input bit.

Methods:

BrakeFD

PinIO

GetVal - reads the input value

.Accesses the signal for switching brake on/off.

Methods:

SetVal - Switches brake on

ClrVal - Switches brake off

3-Phase AC Motor Control with V/Hz Speed Closed Loop, Rev. 0

Freescale Semiconductor

23

Software implementation

Table 7-1. Beans Used in Implementing the 56F805 (Continued)

Bean name

Bean type

QuadFD

QuadratureDecoder

Description

Computes the position and speed of the motor.

Uses the Quad Decoder0 on-chip device.

Methods:

mc_gen

MC_WaveGenerate

mc_lut

MC_LookUpTable

Algorithm used for determining the state of phases for motor

control.

Look-up table algorithm.

Methods:

MC_ramp

MR_Ramp

MC_PIController

lutGetValue - Gets the desired value from the

table

Sets the acceleration/decceleration ramp.

Methods:

MC1

CoeficientCalc - Computes parameters settings

GetScalePositionDifference - Computes position

and speed

rampGetValue - Gets the ramp value

Computes motor speed using the PI controller.

Methods:

controllerPItype1 - PI controller algorithm

3-Phase AC Motor Control with V/Hz Speed Closed Loop, Rev. 0

24

Freescale Semiconductor

Bean Modules

Figure 7-2. Beans Used in Implementing the 56F8346

3-Phase AC Motor Control with V/Hz Speed Closed Loop, Rev. 0

Freescale Semiconductor

25

Software implementation

Table 7-2. Beans Used in Implementation the 56F8346

Bean name

Bean type

Description

PC_Master

PC_Master

Provides serial communication with the PC master software

running on the PC using the SCI0 on-chip device.

Communication speed is 9600bps.

UpButtonFD,

DownButtonFD

Button

Buttons are used for motor speed settings, with a 75rpm step.

Buttons are connected to GPIOE4 and GPIOE7 inputs.

Events:

SwitchFD

Switch_RUNSTOP

OnButton - Invoked by pressing the button

Sets the applcation state to RUN/STOP.

The bean uses GPIOE5 input bit.

Methods:

Adc

ADC

GetVal - Reads the switch state

Measures the DCBus voltage and temperature.

The bean uses channels AD0 (voltage) and ADA5(temperature) of

the ADCB on-chip device.

Methods:

Measure - Start of the measurement (length of the

measurement is 1.7us)

GetChanValue - Reading of the measured value from

a given channel

SetHighChanLimit - Sets the upper limit value for a

given channel

SetLowChanLimit - Sets the lower limit value for a

given channel

Events:

FC1

FreeCounter

OnEnd - End of conversion. This event watches the

values of voltage and temperature. When the values

overrun the allowed range, the motor is

disconnected.

OnHighLimit - Switches brake on

OnLowLimit - Switches brake off

This timer bean watches the 100ms minimum delay between

presses of the Up and Down buttons.

The bean uses the on-chip device TMRD23.

3-Phase AC Motor Control with V/Hz Speed Closed Loop, Rev. 0

26

Freescale Semiconductor

Bean Modules

Table 7-2. Beans Used in Implementation the 56F8346 (Continued)

Bean name

Bean type

TimerLED

TimerInt

Description

This timer controls the LEDs blinking.

It uses the on-chip timer TMRB0.

Events:

TimerID

FreeCntr16

OnInterrupt - Toggles the LED on and off

The timer used to identify hardware.

Uses the TMRA0 on-chip device.

Methods:

TimerRamp

TimerInt

Enable - Starts the timer

Disable - Disables the timer

The timer controlling the acceleration/decceleration ramp.

Uses the TMRA1 on-chip device.

Methods:

Enable - Starts the timer

Events:

OnInterrupt - Sets the speed as needed

3-Phase AC Motor Control with V/Hz Speed Closed Loop, Rev. 0

Freescale Semiconductor

27

Software implementation

Table 7-2. Beans Used in Implementation the 56F8346 (Continued)

Bean name

Bean type

PwmFD

PWMMC

Description

Controls the state of PWM module for motor-application.

Frequency of the PWM output is 16kHz, Dead time is 2.5us.

Pulse width is controlled by the application.

Uses the PWM_B on-chip device.

Methods:

Enable - Enables PWM output

Disable - Disables PWM output

SetDuty - Sets duty on the appropriate PWM channel

Load - Updates control registers

Swap - Swaps PWM pairs

OutputPadEnable - Enables signal output onto CPU

pins

OutputPadDisable - Disables signal output onto CPU

pins

Events:

Primary_UNI_3

PinIO

Onreload - This event:

Measures actual speed (MeasuredSpeed)

Eliminates DCBus voltage ripples

(mcgenDCBVoltRippleElim function)

Calculate waveform generator

(mcgen3PhWaveSine3rdHIntp function)

Updates PWM value registers

Starts ADC conversion

OnFault0 - Switches the motor off and sets the

Overvoltage error flag

OnFault1 - Switches the motor off and sets the

Overcurrent error flag

Accesses the Primary Serial COM signal of the

Primary UNI connector.

Uses the GPIOE6 input bit.

Methods:

BrakeFD

PinIO

GetVal - Reads the input value

Accesses the signal for switching the break on and off on GPIOD7.

Methods:

SetVal - Switches brake on

ClrVal - Switches brake off

3-Phase AC Motor Control with V/Hz Speed Closed Loop, Rev. 0

28

Freescale Semiconductor

Bean Modules

Table 7-2. Beans Used in Implementation the 56F8346 (Continued)

Bean name

Bean type

QuadFD

QuadratureDecoder

Description

Computes the position and speed of the motor.

Uses the Quad Decoder1 on-chip device.

Methods:

mc_gen

MC_WaveGenerate

mc_lut

MC_LookUpTable

Algorithm used for determining the state of phases for motor

control.

Look-up table algorithm.

Methods:

MC_ramp

MR_Ramp

MC_PIController

PWMMC

rampGetValue - Gets the ramp value

Computes motor speed using the PI controller.

Methods:

PWMMC1

lutGetValue - Gets the desired value from the table

Sets the acceleration/decceleration ramp.

Methods:

MC1

CoeficientCalc - Computes parameters settings

GetScalePositionDifference - computes position and

speed

controllerPItype1 - PI controller algorithm

Sets the LEDs state on the EVM.

The bean uses LEDs connected to PWM outputs.

Methods:

Mask - Switches LEDs on/off

3-Phase AC Motor Control with V/Hz Speed Closed Loop, Rev. 0

Freescale Semiconductor

29

Software implementation

7.2.1 Initialization

The Main routine calls the PE_low_level_init() function generated by Processor Expert. This function pre-sets

the CPU internal peripherals to the initial state according to the beans settings.

The main method provides the following application initialization:

Sets the upper and lower limits of the A/D converter

Starts A/D conversion

Sets up aplication state

Identifies connected hardware

Establishes Quadrature Encoder settings for speed computation

Sets up PI controller

The board identification routine identifies the connected power stage board by decoding the identified message

sent from the power stage. If the wrong power stage is identified, the program goes to the infinite loop,

displaying the fault status on the LED. The state can be left only by a reset.

7.3 State Diagram

The general state diagram incorporates the main routine entered from reset and interrupt states. The main

routine includes the initialization of the CPU and the main loop. The main loop incorporates the initialization

state, the application state machine and checks the state of the Run/Stop switch.

The interrupt states calculates the actual speed of the motor, PWM reload event, ADC service, Limit analog

values handling, overcurrent and overvoltage PWM fault handler, and other tasks.

3-Phase AC Motor Control with V/Hz Speed Closed Loop, Rev. 0

30

Freescale Semiconductor

State Diagram

reset

Initialization

OC Timer for LED interrupt

done

Application

State Machine

Timer OC

LED

Subroutine

done

Check

Run/Stop Switch

done

OC Timer for Speed Ramp Interrupt

done

Timer OC

Speed Ramp

Subroutine

ADC low limit Interrupt

ADC

Low Limit Interrupt

Subroutine

done

done

ADC high limit Interrupt

ADC

High Limit Interrupt

Subroutine

PWM

Reload A Interrupt

Subroutine

done

done

ADC conversion complete Interrupt

ADC

Interrupt

Subroutine

done

PWM A Reload Interrupt

PWM A Fault Interrupt

PWM

Fault A Interrupt

Subroutine

done

Figure 7-3. State Diagram - General Overview

3-Phase AC Motor Control with V/Hz Speed Closed Loop, Rev. 0

Freescale Semiconductor

31

PC Master Software

7.3.1 Application State Machine

This state controls the main application functions, depicted in Figure 7-4.

Application State Machine - Begin

Test

Drive Fault Status

NO_FAULT

FAULT

Test

Application Mode

RUN

RESET

Emergency Stop

STOP

Enable PWM

Calculate V/Hz Ramp

Speed = 0

Disable PWM

done

done

Application State Machine - End

Figure 7-4. State - Application State Machine

7.3.2 Check Run/Stop Switch

In this state, the Run/Stop switch is checked according to the Application Mode setting and is set to RUN or

STOP as directed.

Individual driver functions are provided by special PE function calls, found under the Processor Expert tab.

8.

PC Master Software

PC master software was designed to provide a debugging, diagnostic and demonstration tool for the

development of algorithms and applications. It runs on a PC connected to the EVM via an RS-232 serial cable.

A small program resident in the controller communicates with the PC master software to parse commands,

return status information to the PC and process control information from the PC. PC master software uses part

of Microsoft's Internet Explorer as the user interface. To enable PC master software operation on the controller

target board application, add the PC master software bean to the project and configure it. This automatically

3-Phase AC Motor Control with V/Hz Speed Closed Loop, Rev. 0

32

Freescale Semiconductor

State Diagram

includes the SCI driver and installs all necessary services. The SCI communications default baud rate is

9600bd. It is set automatically by the PC master software driver and can be changed if needed. A detailed

description of PC master software is provided in a dedicated User's Manual.

The 3-phase AC Motor V/Hz Speed Open Loop application utilizes PC master software for remote control

from the PC. It enables the user to:

Set the motor speed

Set the close loop

PC master software reads and displays these variables to the user:

Required and actual motor speed

Application operational mode

Start/stop status

DCBus voltage

Temperature

Phase voltage amplitude

The PC master software Control Page is illustrated in Figure 8-1. Profiles of the required and actual speeds can

be seen in the Speed Scope window.

Figure 8-1. PC Control Window

3-Phase AC Motor Control with V/Hz Speed Closed Loop, Rev. 0

Freescale Semiconductor

33

References

9.

References

1. DSP56F800 Family Manual, DSP56F800FM, Freescale Semiconductor

2. DSP56F80x Users Manual, DSP56F801-7UM, Freescale Semiconductor

3. DSP56F805 Evaluation Module Hardware Users Manual, DSP56F805EVM, Freescale Semiconductor

4. DSP56800E Reference Manual, DSP56800ERM, Freescale Semiconductor

5. MC56F8300 Peripheral User Manual, MC56F8300UM, Freescale Semiconductor

6. MC56F8346 Evaluation Module Hardware Users Manual, MC56F8346EVMUM, Freescale

Semiconductor

7. 3-Phase AC Induction Motor Control V/Hz Application - Closed Loop, 805ACIMTD, Freescale

Semiconductor

8. 3-Phase AC Induction Motor Control V/Hz Application - Closed Loop, 8346ACIMTD, Freescale

Semiconductor

9. Low Cost 3-phase AC Motor Control System Based On MC68HC908MR24, AN1664, Freescale

Semiconductor

10. Processor Expert Embedded Beans, Processor Expert Help

For more information, go to:

www.freescale.com

3-Phase AC Motor Control with V/Hz Speed Closed Loop, Rev. 0

34

Freescale Semiconductor

State Diagram

3-Phase AC Motor Control with V/Hz Speed Closed Loop, Rev. 0

Freescale Semiconductor

35

How to Reach Us:

Home Page:

www.freescale.com

E-mail:

support@freescale.com

USA/Europe or Locations Not Listed:

Freescale Semiconductor

Technical Information Center, CH370

1300 N. Alma School Road

Chandler, Arizona 85224

+1-800-521-6274 or +1-480-768-2130

support@freescale.com

Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH

Technical Information Center

Schatzbogen 7

81829 Muenchen, Germany

+44 1296 380 456 (English)

+46 8 52200080 (English)

+49 89 92103 559 (German)

+33 1 69 35 48 48 (French)

support@freescale.com

Japan:

Freescale Semiconductor Japan Ltd.

Headquarters

ARCO Tower 15F

1-8-1, Shimo-Meguro, Meguro-ku,

Tokyo 153-0064, Japan

0120 191014 or +81 3 5437 9125

support.japan@freescale.com

Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd.

Technical Information Center

2 Dai King Street

Tai Po Industrial Estate

Tai Po, N.T., Hong Kong

+800 2666 8080

support.asia@freescale.com

For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center

P.O. Box 5405

Denver, Colorado 80217

1-800-441-2447 or 303-675-2140

Fax: 303-675-2150

LDCForFreescaleSemiconductor@hibbertgroup.com

Information in this document is provided solely to enable system and

software implementers to use Freescale Semiconductor products. There are

no express or implied copyright licenses granted hereunder to design or

fabricate any integrated circuits or integrated circuits based on the

information in this document.

Freescale Semiconductor reserves the right to make changes without further

notice to any products herein. Freescale Semiconductor makes no warranty,

representation or guarantee regarding the suitability of its products for any

particular purpose, nor does Freescale Semiconductor assume any liability

arising out of the application or use of any product or circuit, and specifically

disclaims any and all liability, including without limitation consequential or

incidental damages. Typical parameters that may be provided in Freescale

Semiconductor data sheets and/or specifications can and do vary in different

applications and actual performance may vary over time. All operating

parameters, including Typicals, must be validated for each customer

application by customers technical experts. Freescale Semiconductor does

not convey any license under its patent rights nor the rights of others.

Freescale Semiconductor products are not designed, intended, or authorized

for use as components in systems intended for surgical implant into the body,

or other applications intended to support or sustain life, or for any other

application in which the failure of the Freescale Semiconductor product could

create a situation where personal injury or death may occur. Should Buyer

purchase or use Freescale Semiconductor products for any such unintended

or unauthorized application, Buyer shall indemnify and hold Freescale

Semiconductor and its officers, employees, subsidiaries, affiliates, and

distributors harmless against all claims, costs, damages, and expenses, and

reasonable attorney fees arising out of, directly or indirectly, any claim of

personal injury or death associated with such unintended or unauthorized

use, even if such claim alleges that Freescale Semiconductor was negligent

regarding the design or manufacture of the part.

Freescale and the Freescale logo are trademarks of Freescale Semiconductor,

Inc. All other product or service names are the property of their respective owners.

This product incorporates SuperFlash technology licensed from SST.

Freescale Semiconductor, Inc. 2005. All rights reserved.

AN1958

Rev. 0

07/2005

S-ar putea să vă placă și

- ColomboDocument10 paginiColomboසම්පත් චන්ද්රරත්නÎncă nu există evaluări

- DC Power Flow EquationsDocument21 paginiDC Power Flow EquationsfpttmmÎncă nu există evaluări

- PIC16f877a Midrange InstructionDocument48 paginiPIC16f877a Midrange InstructionXaid HussainÎncă nu există evaluări

- Building Wires - Earth WireDocument1 paginăBuilding Wires - Earth WireMohamed KhanÎncă nu există evaluări

- IeslDocument1 paginăIeslසම්පත් චන්ද්රරත්නÎncă nu există evaluări

- Tutorial 8Document2 paginiTutorial 8සම්පත් චන්ද්රරත්නÎncă nu există evaluări

- Ejemplo Flujos UwaterlooDocument6 paginiEjemplo Flujos Uwaterlooසම්පත් චන්ද්රරත්නÎncă nu există evaluări

- EC 5001 - Memory 1Document56 paginiEC 5001 - Memory 1සම්පත් චන්ද්රරත්නÎncă nu există evaluări

- Hydraulic SystemsDocument63 paginiHydraulic SystemsBhaskar ReddyÎncă nu există evaluări

- Unsymmetrical Fault AnalysisDocument106 paginiUnsymmetrical Fault Analysisසම්පත් චන්ද්රරත්නÎncă nu există evaluări

- 6.0 High Voltage MeasurementDocument32 pagini6.0 High Voltage MeasurementGopala VetsaÎncă nu există evaluări

- Dynamic Programming: Ananth Grama, Anshul Gupta, George Karypis, and Vipin KumarDocument42 paginiDynamic Programming: Ananth Grama, Anshul Gupta, George Karypis, and Vipin Kumarසම්පත් චන්ද්රරත්නÎncă nu există evaluări

- Gamesa G58 850kwDocument6 paginiGamesa G58 850kwසම්පත් චන්ද්රරත්නÎncă nu există evaluări

- ECX4234 Lesson 2Document20 paginiECX4234 Lesson 2සම්පත් චන්ද්රරත්නÎncă nu există evaluări

- HV Chap1Document21 paginiHV Chap1sdsamarakkody0% (1)

- EE427 Answers Mar2008 PDFDocument13 paginiEE427 Answers Mar2008 PDFසම්පත් චන්ද්රරත්නÎncă nu există evaluări

- Gamesa G58 850kwDocument6 paginiGamesa G58 850kwසම්පත් චන්ද්රරත්නÎncă nu există evaluări

- Work ListDocument74 paginiWork Listසම්පත් චන්ද්රරත්නÎncă nu există evaluări

- The Pareto Principle: Rosie Dunford, Quanrong Su, Ekraj Tamang and Abigail WintourDocument9 paginiThe Pareto Principle: Rosie Dunford, Quanrong Su, Ekraj Tamang and Abigail Wintourසම්පත් චන්ද්රරත්නÎncă nu există evaluări

- Attendance Report 2017 - GDL. CLII. Sem04. Sem06 PDFDocument12 paginiAttendance Report 2017 - GDL. CLII. Sem04. Sem06 PDFසම්පත් චන්ද්රරත්නÎncă nu există evaluări

- cd6748 92Document24 paginicd6748 92සම්පත් චන්ද්රරත්නÎncă nu există evaluări

- Embedded Systems Model Paper PDFDocument4 paginiEmbedded Systems Model Paper PDFසම්පත් චන්ද්රරත්නÎncă nu există evaluări

- Embedded Systems Model Paper PDFDocument4 paginiEmbedded Systems Model Paper PDFසම්පත් චන්ද්රරත්නÎncă nu există evaluări

- EE427 Answers June2007 PDFDocument21 paginiEE427 Answers June2007 PDFසම්පත් චන්ද්රරත්නÎncă nu există evaluări

- High Voltage Engineering (Lucas)Document212 paginiHigh Voltage Engineering (Lucas)myerten100% (6)

- Thyristor Voltage Controller - 100494PDocument15 paginiThyristor Voltage Controller - 100494PNishanga SandamalÎncă nu există evaluări

- Bimba Ref HandbookDocument47 paginiBimba Ref HandbookRico AriezonaÎncă nu există evaluări

- UNIT 4 MechatronicsDocument21 paginiUNIT 4 MechatronicsMuthuvel M100% (1)

- EE402 Answers Feb2005Document8 paginiEE402 Answers Feb2005සම්පත් චන්ද්රරත්නÎncă nu există evaluări

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (895)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (266)

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (400)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (588)

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (74)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2259)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (121)

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)

- Philco H3410 Predicta Princess Sams 466 1Document21 paginiPhilco H3410 Predicta Princess Sams 466 1daviÎncă nu există evaluări

- Wcm2012f2s SeriesDocument4 paginiWcm2012f2s Seriesgoogi7Încă nu există evaluări

- Bist Tutorial 2 PDFDocument9 paginiBist Tutorial 2 PDFjcfermosellÎncă nu există evaluări

- Op Amp PresentationDocument23 paginiOp Amp Presentationboomadev6321Încă nu există evaluări

- R820 Technical DocumentationDocument5 paginiR820 Technical DocumentationZainul Abedin SayedÎncă nu există evaluări

- 3S0765R 3S0765RF PDFDocument14 pagini3S0765R 3S0765RF PDFhectorsevillaÎncă nu există evaluări

- Flux WeakningDocument4 paginiFlux WeakningShivendraSaurabhÎncă nu există evaluări

- How The Electric Car WorksDocument6 paginiHow The Electric Car WorksFreddy KurniawanÎncă nu există evaluări

- 7UT612 ProcedureDocument11 pagini7UT612 ProcedureArul Kumar100% (2)

- Data Sheet 6320 AisDocument139 paginiData Sheet 6320 Aisshahramkh59Încă nu există evaluări

- AC Ripple VoltageDocument5 paginiAC Ripple VoltageAgung Sugeng RiyadiÎncă nu există evaluări

- Ultra-Sensitive Dual-Channel Quadrature Hall-Effect Bipolar SwitchDocument17 paginiUltra-Sensitive Dual-Channel Quadrature Hall-Effect Bipolar SwitchMuhammad Jalal AldeenÎncă nu există evaluări

- RFSAS20EDRMDocument76 paginiRFSAS20EDRMJuan BoggianoÎncă nu există evaluări

- Service Manual: Colour TelevisionDocument48 paginiService Manual: Colour TelevisionRoosevelt Vega SanchezÎncă nu există evaluări

- Hauptkatalog 12-42kv GBDocument64 paginiHauptkatalog 12-42kv GBrabchabÎncă nu există evaluări

- 8096 MicrocontrollerDocument51 pagini8096 MicrocontrollerNarasimha Murthy Yayavaram67% (3)

- Shigley S Mechanical Engineering Design 9th Edition Solutions ManualDocument29 paginiShigley S Mechanical Engineering Design 9th Edition Solutions ManualZaim AkmalÎncă nu există evaluări

- Empr DMPR CatalogueDocument44 paginiEmpr DMPR CatalogueECATOnlineÎncă nu există evaluări

- Aiwa Nsx-s505 A508Document22 paginiAiwa Nsx-s505 A508RicardoÎncă nu există evaluări

- Aes in Fpga PDFDocument169 paginiAes in Fpga PDFChandan ChoudhuryÎncă nu există evaluări

- Basic Radar System Block DiagramDocument9 paginiBasic Radar System Block Diagrambapiraju saripellaÎncă nu există evaluări

- Cpu's PackageDocument1 paginăCpu's PackagepangaeaÎncă nu există evaluări

- POWER ELECTRONICS Tutorial HHDocument6 paginiPOWER ELECTRONICS Tutorial HHStreet EngineersÎncă nu există evaluări

- CycloconvertersDocument17 paginiCycloconverterssintakyut abieeztÎncă nu există evaluări

- Automatic Solar Irrigation SystemDocument16 paginiAutomatic Solar Irrigation SystemDebashishParidaÎncă nu există evaluări

- Microelectronics PDFDocument15 paginiMicroelectronics PDFJeanin Marquez ÜÎncă nu există evaluări

- Product Specification: Preliminary Specification (V) Final SpecificationDocument20 paginiProduct Specification: Preliminary Specification (V) Final Specificationเกียรติศักดิ์ ภูมิลาÎncă nu există evaluări

- Ece R13 2-1 PDFDocument12 paginiEce R13 2-1 PDFHassanÎncă nu există evaluări

- SU99Document95 paginiSU99saopauloÎncă nu există evaluări