Documente Academic

Documente Profesional

Documente Cultură

Vlsi Implementation of Physical Layer Coding Used in Super Speed Usb Using Verilog

Încărcat de

RenukaDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Vlsi Implementation of Physical Layer Coding Used in Super Speed Usb Using Verilog

Încărcat de

RenukaDrepturi de autor:

Formate disponibile

Global Journal of Advanced Engineering Technologies, Vol1, Issue4-2012

ISSN: 2277-6370

VLSI IMPLEMENTATION OF PHYSICAL LAYER

CODING USED IN SUPER SPEED USB USING

VERILOG

K.V.Suresh babu1 , Prof.A.S.Srinivasarao2 , D.Srinivasa Rao3

1

Student (M.Tech), Dept of ECE, AITAM, Tekkali, A.P

2

Professor &H.O.D., Dept of ECE, AITAM, Tekkali, A.P

3

Assistant. professor, Dept of ECE, AITAM, Tekkali, A.P

Abstract- This project implements the DC balanced 8B/10B

coding used in Super speed USB with employ a very fast FPGA

from Xilinx family is proposed. This technique can be used by

other high speed serial buses such as PCI Express, IEEE

1394b, Serial ATA, SAS, Fiber Channel, SSA, Gigabit

Ethernet, In fini Band, XAUI, Serial Rapid IO, DVI and

HDMI (Transition Minimized Differential Signalling)that use

the same coding. Using the look-up table and memory with

fast technique made this design efficient to be implemented.

Moreover, the proposed method has very low

complexity and fast to execute with minimum logic and also

easy to implement. The Scrambling and descrambling

modules are added in the above modules to support USB 30

physical layer transactions. The code is implemented in

VERILOG

keywords Usb, link layer, crc, ncverilog and cadence

I. INTRODUCTION

It is a specification to establish communication between

devices and a host controller (usually a personal computer),

developed and invented by Ajay Bhatt, while working for

Intel. USB has effectively replaced a variety of interfaces

such as serial and parallel ports. USB can connect computer

peripherals such as mice, keyboards, digital cameras,

printers, personal media players, flash drives, Network

Adapters, and external hard drives. For many of those

devices, USB has become the standard connection method.

A. Version history:

USB 0.7: Released in November 1994.

USB 0.8: Released in December 1994.

USB 0.9: Released in April 1995.

USB 0.99: Released in August 1995.

USB 1.0 Release Candidate: Released in November 1995.

USB 1.0: Released in January 1996.Specified data rates of

1.5Mbit/s (Low-Bandwidth) and 12Mbit/s (Full

Bandwidth). Does not allow for extension cables or passthrough monitors (due to timing and power limitations).

Few such devices actually made it to market.

USB 1.1: Released in September 1998.Fixed problems

identified in 1.0, mostly relating to hubs. Earliest revision

to be widely adopted.

USB 2.0: Released in April 2000.Added higher

maximum bandwidth of 480 Mbit/s [60 MB/s] (now called

"Hi-Speed").Micro-USB

Cables

and

Connectors

Specification 1.01: Released in April 2007. Motivation

Connection of the PC to the telephone: Ease-of-use:

Objective of the Specification.

II. INTRODUCTION TO USB 3.0

This paper is a brief review of the USB 3.0 implementation,

focusing on USB 2.0backward compatibility and on the

major features associated with the Super-Speed (SS) bus.

The goal is to provide the reader with a short and concise

description of USB 3.0, and enough detail to give a good

feel for the technology, protocols, and techniques. Due to

the limited scope of this paper, some terminology and

concepts are introduced but not fully developed.

a) Motivation for USB 3.0:

USB 3.0 enables more demanding applications

compared to USB 2.0 by addressing its limitations:

Bandwidth - 5.0 G b/sec Super Speed (SS) vs. 480

Mb/sec (High Speed) rate.

Power Conservation - link power states (U0 - U3)

and function power management.

Data Flow Control - poll once versus poll multiple times

Error Handling - End-to-end and port-to-port error

detection and retries versus only end-to-end retries with

USB 2.0.The additional bandwidth provided by USB SS

transactions can benefit applications like real-time audio

and video streaming that require higher bus bandwidth

at regular intervals. Mass storage applications can also

benefit from the SS bandwidth. For example, Table 2.1

lists approximate download times for the different

transmission rates.

b) USB 2.0 Host:

Hubs power downstream ports when directed by software

(USB 2.0) with Super Speed support disabled.

Device connects at high-speed.

Host system begins device enumeration at high-speed.

When the host is powered off, the hub does not

provide power to its downstream ports unless the hub

supports charging applications. When the host is

powered on and there is no Super Speed hardware

support, the following is the typical sequence of events:

Hub detects VBUS and connects as a high-speed device.

218

Global Journal of Advanced Engineering Technologies, Vol1, Issue4-2012

Host system begins hub enumeration at high-speed.

III. PHYSICAL LAYER

The physical layer defines the PHY portion of a port and

the physical connection between a downstream facing port (on

a host or hub) and the upstream facing port on a device. The

Super Speed physical connection is comprised of two

differential data pairs, one transmit path and one receive path.

The nominal signalling data rate is 5 Gbps.

Express protocol and signalling. This includes features such as;

data serialization and de-serialization, 8b/10b encoding, analog

buffers, elastic buffers and receiver detection

Some key features of the PCI Express PHY are:

Standard PHY interface enables multiple IP sources for

PCI Express Logical Layer and provides a target

interface for PCI Express PHY vendors.

Supports 2.5GT/s only or 2.5GT/s and 5.0 GT/s serial data

transmission rate.

Utilizes 8-bit, 16-bit or 32 -bit parallel interface

to transmit and receive PCI Express data.

Allows integration of high speed components into a

single functional block as seen by the End point device

designer.

Data and clock recovery from serial stream on the PCI

Express bus.

Holding registers to stage transmit and receive data.

Supports direct disparity control for use in transmitting

compliance pattern(s).

c)

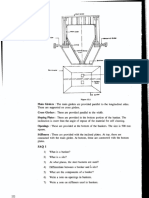

Figure 1: Super Speed Physical Layer

The electrical aspects of each path are characterized

as a transmitter, channel, and receiver; these

collectively represent a unidirectional differential

link. Each differential link is AC-coupled with

capacitors located on the transmitter side of the

differential link. The channel includes the electrical

characteristics of the cables and connectors. At an

electrical level, each differential link is initialized by

enabling its receiver termination.

a) Physical Layer Overview:

The physical layer defines the signalling technology for the

Super Speed bus.

This chapter defines the electrical

requirements of the Super Speed physical layer. This section

defines the electrical-layer parameters required for

interoperability between Super Speed components. The PHY

Interface for the PCI Express and USB Super Speed

Architectures (PIPE) is intended to enable the development of

functionally equivalent PCI Express and USB Super Speed

PHY's. Such PHY's can be delivered as discrete IC's or as

macro cells for inclusion in ASIC designs. The PIPE

specification is defined to allow various approaches to be used.

Where possible the PIPE specification references the PCI

Express base specification or USB 3.0Specification

rather than repeating its content. In case of conflicts, the

PCI-Express Base Specification and USB 3.0 Specification

shall supersede the PIPE spec. This spec provides some

information about how the MAC could use the PIPE interface

for various LTSSM states and Link states.

b) PCI Express PHY Layer:

The PCI Express PHY Layer handles the low level PCI

ISSN: 2277-6370

Physical Layer Transmission and Reception:

Transmission:

Scrambling- Scrambling reduces EMI problems

associated with repeated patterns in the data being

sent across an SS link. The scrambler output is simply

XORed with each byte of data to eliminate the repeated

patterns.

8/10b Encoding every byte that traverses the link is first

Converted into a10-bit value called a symbol (this is

a common encoding scheme in high-speed serial designs).

Parallel/Serial Conversion Bytes are converted to

bit stream LFPS Low Frequency Periodic Signaling

is typically used in situations where the link is in an

electrical idle state.

Differential Transmission Packets are clocked onto the

link at a 5.0 Gb/srate.

Reception:

Differential Reception the scrambled and encoded data

is received and forwarded to the recovery blocks.

Clock and Data Recovery the clock is extracted from

the bit stream and data is clocked into the serial/parallel

converter.

Serial/Parallel Conversion data is clocked into the

Converter and 10-bit symbols are clocked into the

elastic buffer.

Elastic Buffer The elastic buffer must absorb the worstcase clock variation between the transmitted

clock frequency (recovered) and the local receive

clock. The maximum variance is +300 to -300ppm. The

buffer must also accommodate variations resulting

from the Spread Spectrum clocking. Compensation is

achieved via SKP ordered sets that are periodically

inserted into the bit stream.

8/10b Decoding 10-bit symbols are converted back to

219

Global Journal of Advanced Engineering Technologies, Vol1, Issue4-2012

bytes. Un Scrambling the same scrambling output is

XORed with the scrambled data a second time to

recover the original data Rx Clk.

d) VLSI Implementation of physical coding layer

USB 3.0 ARCHITECTURE

Test bench:

The term test bench usually refers to simulation code used

to create a predetermined input sequence to a design, then

optionally to observe the response.

Today, in the era of multi-million gate ASICs and FPGAs,

reusable intellectual property (IP), and system-on-a-chip

(SoC) designs, verification consumes about 70% of the

design effort. Design teams, properly staffed to address the

verification challenge, include engineers dedicated to

verification. The number of verification engineers can be

up to twice the number of RTL designers. Higher abstraction

levels are usually accompanied by a reduction in control and

therefore must be chosen wisely. These higher abstraction

levels often require additional training to understand the

abstraction

mechanism and how the desired effect can be

produced. If a verification process uses higher abstraction

levels by working at the transaction- or bus-cycle levels (or

even higher ones), it will be easier to create large amount of

stimulus. But it may be difficult to produce a specific sequence

of low-level zeroes and ones.

ENCODER:

One of the major goals of 8b/10b encoding is to embed

a clock into the serial bit stream before transmission

across the link. This eliminates the need for a high

frequency 5.0 GHz clock signal on the link that could

ISSN: 2277-6370

generate significant EMI. Every byte to be sent is

converted to a 10-bit value, called a symbol a look-up table

associated with the encoder.

Data bytes consisting of every byte send across the

link except ordered Sets. The data lookup table must

support the 256 possible input values.

Control bytes used in ordered sets. The 8b/10b

encoding scheme is also designed to prevent DC

wander, meaning the possibility that too many bits of

one polarity could interfere with the ability of the

receiver to properly see them.

DECODER:

The 8b/10b Decoder uses two lookup tables (the D and K

tables) to convert the 10-bit symbol stream back into

bytes. Each symbol value is submitted to both lookup

tables but only one of the tables will find a match for the

symbol. The state of the D/K# signal indicates that the

received symbol is a:

Data (D) Symbol a match for the received symbol is

located in the D table. D/K# is driven High.

Control (K) Symbol a match for the received symbol

is located in the K table. D/K# is driven Low.

SCRAMBLER:

Scrambling reduces repeated patterns in the bit stream

and lowers EMI by preventing the concentration of

emitted energy at only a few frequencies. Scrambling

works by generating a pseudo-random data pattern that is

XORed with the outgoing bit stream. . The algorithm used

for scrambling data is expressed as a polynomial

implemented as a linear feedback shift register (LFSR).

DESCRAMBLER:

Disabling scrambling is intended to help simplify test

and debug equipment. Control of the exact data patterns is

useful in a test and debug environment. Since scrambling

is reset at the physical layer, there is no reasonable way to

reliably control the state of the data transitions through

software. The Disable Scrambling bit is provided in the

training sequence for this purpose. The mechanism(s)

and/or interface(s) used to notify the physical layer to

disable scrambling is component implementation specific

and beyond the scope of this specification.

IV.RESULTS

TOOLS USED FOR EXPERIMENTAL ANALYSIS: SIMULATORMODELSIM 6.3F, SYNTHESIS- ISE 9.2I, DEBUGGING TOOLCHIP SCOPE 9.2I, BOARD- SPARTAN 3E.

Figure 2: Clock and Reset generator signals

220

Global Journal of Advanced Engineering Technologies, Vol1, Issue4-2012

ISSN: 2277-6370

An synchronous clock with a total period of 20 ns or

50MHz was generated in the top level block for

synchronous operation, Asynchronous reset is generated for

negative edge Reset.

Figure 5: Port and internal logic signals of Encoder module

Generated 8 bit data from scrambler is given as input

encoder module and is observed as din signal, kin signal,

the result will be observed in dout which a 10 bit output from

the above figure.

Figure 3: Test bench generator signals

Using $random different values for input is generated and it

is sent via top module to Scrambler module in the

Architecture as shown in fig 3 .The results for randomly

generated input is shown above.

Figure 6: Port and internal logic signals of Decode module

Figure 4: Port and internal logic signals of Scrambler module

221

Global Journal of Advanced Engineering Technologies, Vol1, Issue4-2012

Fig. 7 Port and internal logic signals of Descrambler module

VI CONCLUSIONS

The Architecture of FPGA implementation of 8b/10b

coding used in super-speed USB is proposed and designed for

digital hardware implementation. All individual modules

have been designed individually and verified functionally

using random test bench using ModelSim 6.3f. It is observed

that the simulation results for the 8b 10b encoder, 8b 10b

decoder, scrambler and descrambler generated were

satisfactory and also the interconnections among all the

modules are perfect. A priority encoder method is used for 8b

10b encoder and decoder. The symbol errors for both D and

K symbols are verified in both encoder and decoder. The

entire above module are coded in VERILOG hardware

description language.

This work can extended by connecting this total module

in between Link layer and Physical analog layer of USB 3.0

architecture and transferring USB3.0 packets rigorously

from link layer to physical layer. Also the work can be

extended to do the FPGA implementation by using SPRTAN

3E or Vertex V XILINX FPGAs. The above project is best

suits as an IP (Intelectual Property) core of Physical Coding

Layer in USB 3.0 specification.

VII FUTURE SCOPE

The Design Physical coding layer can be rigorously

tested if soft cores of link layer, physical analog layer are

available. This can be an extended work for the present

project.

Complete USB 3.0 project can be done if one has

finished soft cores of link, protocol, application layers in

addition to our project. If analog PHYs are available in the

market hardware level validation can be done to our project.

ISSN: 2277-6370

REFERENCES

[1] A.X. Widmer and P.A. Franaszek, A dc-balanced,

partitioned block, 8B/10B transmission code, IBM Journal

of Research and Development, vol.27, no.5, pp. 440-451,

Sep 1983.

[2] Universal Serial Bus 3.0 Specification Revision0.9, July30,

2008.

[3] Ravi Budruk, Don Anderson & Tom Sanely, 2004.

PCI Express System Architecture - Mindshare Inc., pp 419434.

[4] Thatcher, Jonathan (1996-04-01). "Thoughts on Gigabit

Ethernet Physical". IBM. Retrieved on 2008-08-17.

[5] Jenming Wu & Yu-Ho Hsu ,8B/10B Codec for Efficient

PAPR Reduction in OFDM Communication Systems.

[6] J.Begeron, what is verification? in writing Test

benches: functional verification of HDL models.

[7] International technology roadmap for

semiconductors(ITRS)

[8] http://www.doulos.com/knowhow/sysverilog/ovm/tutorial

[9] http:// www.ovm.world.org/white_papers.php

[10] A.Shankara Rao and D.Rama Devi, FPGA

implementation of 8b/10b coding used in super-speed USB

in an international conference on CEMC-2011, ILAHIA

College Of Engineering, Kerala. (Communicated).

222

S-ar putea să vă placă și

- How To Read Music Notation in Just 30 MinutesDocument5 paginiHow To Read Music Notation in Just 30 MinutesLuvonga Caleb0% (1)

- Serial Port Complete: COM Ports, USB Virtual COM Ports, and Ports for Embedded SystemsDe la EverandSerial Port Complete: COM Ports, USB Virtual COM Ports, and Ports for Embedded SystemsEvaluare: 3.5 din 5 stele3.5/5 (9)

- Standard Cost EstimateDocument21 paginiStandard Cost EstimateMOORTHYÎncă nu există evaluări

- Eldritch HighDocument39 paginiEldritch Highteam_moÎncă nu există evaluări

- Native Data Sheet Asme b73.1Document4 paginiNative Data Sheet Asme b73.1Akhmad Faruq Alhikami100% (1)

- MindShare Intro To PCIeDocument18 paginiMindShare Intro To PCIeharinisasÎncă nu există evaluări

- EngDocument166 paginiEngEzequiel AnayaÎncă nu există evaluări

- InfiniBand and High-Speed Ethernet For DummiesDocument134 paginiInfiniBand and High-Speed Ethernet For DummiessmallakeÎncă nu există evaluări

- CCNA Interview Questions You'll Most Likely Be AskedDe la EverandCCNA Interview Questions You'll Most Likely Be AskedÎncă nu există evaluări

- Networking Basics Notes - v2Document45 paginiNetworking Basics Notes - v2Gherasa Marius BogdanÎncă nu există evaluări

- NsaDocument21 paginiNsafarfi_2100% (2)

- SAN Administration BasicsDocument62 paginiSAN Administration BasicsNithya RajÎncă nu există evaluări

- PCI Express White PaperDocument8 paginiPCI Express White PaperUday KumarÎncă nu există evaluări

- 2.sys Bus ArchDocument14 pagini2.sys Bus ArchChar MondeÎncă nu există evaluări

- 2.1. Overview of PCI Express BusDocument19 pagini2.1. Overview of PCI Express BusSomasekhar ChepuriÎncă nu există evaluări

- Stepan Formulation 926Document2 paginiStepan Formulation 926Moaz SiddigÎncă nu există evaluări

- Tuberculosis PowerpointDocument69 paginiTuberculosis PowerpointCeline Villo100% (1)

- Computer Buses and InterfacesDocument34 paginiComputer Buses and InterfacesSholeh FirmansyahÎncă nu există evaluări

- Training Report On Self Contained Breathing ApparatusDocument4 paginiTraining Report On Self Contained Breathing ApparatusHiren MahetaÎncă nu există evaluări

- I2c Bus OverviewDocument158 paginiI2c Bus OverviewSkyline Dv100% (2)

- Pci BusDocument17 paginiPci BusA TÎncă nu există evaluări

- Vlsi Implementation of Physical Layer Coding Used in Super Speed Usb Using Verilog PDFDocument5 paginiVlsi Implementation of Physical Layer Coding Used in Super Speed Usb Using Verilog PDFRenukaÎncă nu există evaluări

- Notes:-Different Bus StandardsDocument31 paginiNotes:-Different Bus StandardsDarmoni LaishramÎncă nu există evaluări

- Documentation of USB 3.0Document26 paginiDocumentation of USB 3.0srinidhi2allÎncă nu există evaluări

- Stm32 & Usb: Roman LudinDocument33 paginiStm32 & Usb: Roman LudinAnonymous 1OlQQ3cW100% (1)

- Unit - III - Interfacing: Anusha.K Ap, SiteDocument26 paginiUnit - III - Interfacing: Anusha.K Ap, SiterajgantÎncă nu există evaluări

- Hyper Transport TechnologyDocument27 paginiHyper Transport Technologyapi-3827000100% (1)

- Computer Buses and InterfacesDocument29 paginiComputer Buses and InterfacesNolduatiga TiÎncă nu există evaluări

- Study and Implementation of Physical Layer Coding Used in Super Speed USBDocument4 paginiStudy and Implementation of Physical Layer Coding Used in Super Speed USBRoshini M SÎncă nu există evaluări

- Embedded System PresentationDocument53 paginiEmbedded System PresentationMitali DixitÎncă nu există evaluări

- CA Ex S1M09 EthernetDocument136 paginiCA Ex S1M09 Ethernethttp://heiserz.com/Încă nu există evaluări

- Submitted By: Rahul Yadav 07EI 438 4/7/2011 4/7/2011Document18 paginiSubmitted By: Rahul Yadav 07EI 438 4/7/2011 4/7/2011Praveen RatheeÎncă nu există evaluări

- The PCI Local BusDocument56 paginiThe PCI Local Busatorresh090675Încă nu există evaluări

- S. E. A College of Engineering and Technology: Pavan Kumar S 1SP08IS030Document35 paginiS. E. A College of Engineering and Technology: Pavan Kumar S 1SP08IS030pavan1619Încă nu există evaluări

- A 720Mbps Fast Auxiliary Channel Design For Display Port 1.2Document4 paginiA 720Mbps Fast Auxiliary Channel Design For Display Port 1.2余明士Încă nu există evaluări

- 100 Gigabit Ethernet: Jenson K A S7 Cs Roll No:17Document26 pagini100 Gigabit Ethernet: Jenson K A S7 Cs Roll No:17jensonÎncă nu există evaluări

- l3 - Part 2 - Computer Buses - v22Document35 paginil3 - Part 2 - Computer Buses - v22Pham Xuan ThuyÎncă nu există evaluări

- Assignment No 4 EmbeddedDocument5 paginiAssignment No 4 Embeddedsatinder singhÎncă nu există evaluări

- AS-interface Simple, Robust, Device-Level BusDocument20 paginiAS-interface Simple, Robust, Device-Level BusmdarwishbpÎncă nu există evaluări

- I C-Bus Specification and User ManualDocument50 paginiI C-Bus Specification and User ManualAll4UyenÎncă nu există evaluări

- Microprocessor & Computer Architecture (Μpca) : Unit 4: Usb, Pci, Scsi,Amba And Asb Bus ArchitectureDocument12 paginiMicroprocessor & Computer Architecture (Μpca) : Unit 4: Usb, Pci, Scsi,Amba And Asb Bus ArchitecturePranathi PraveenÎncă nu există evaluări

- Introduction To Input/Output PortsDocument36 paginiIntroduction To Input/Output Portsextreme_gamerÎncă nu există evaluări

- San BasicsDocument64 paginiSan BasicsRajesh MkÎncă nu există evaluări

- 5992-1205EN Impedance Analyzers and Vector Network Analyzers Optimizing Connections Using USB and LAN Interfaces (Jan 2018)Document9 pagini5992-1205EN Impedance Analyzers and Vector Network Analyzers Optimizing Connections Using USB and LAN Interfaces (Jan 2018)郑登宇Încă nu există evaluări

- Universal Serial Bus (USB) : A Seminar Report OnDocument22 paginiUniversal Serial Bus (USB) : A Seminar Report OnAbdulkhadar KitturÎncă nu există evaluări

- 10 Gigabit Ethernet Vs InfinibandbasicDocument122 pagini10 Gigabit Ethernet Vs InfinibandbasicHarsh NarangÎncă nu există evaluări

- Ijarets V-2-3-13Document9 paginiIjarets V-2-3-13swapnil tiwariÎncă nu există evaluări

- IOT Wired ProtocolsDocument6 paginiIOT Wired ProtocolsutpolaÎncă nu există evaluări

- 5.high Speed LANDocument29 pagini5.high Speed LANUtsav Kakkad100% (1)

- Chapter No. Title Page NoDocument23 paginiChapter No. Title Page NoVibin C BhaskarÎncă nu există evaluări

- Verilog HDL Implementation of Usb To Ethernet ConverterDocument6 paginiVerilog HDL Implementation of Usb To Ethernet ConverterRenukaÎncă nu există evaluări

- Peripheral PortsDocument24 paginiPeripheral PortsAlekhSharma100% (1)

- Cisco MWR 2941-DC Mobile Wireless Router: Product OverviewDocument7 paginiCisco MWR 2941-DC Mobile Wireless Router: Product Overviewmansour14Încă nu există evaluări

- Certified Wireless USBDocument27 paginiCertified Wireless USBApple Ball CÎncă nu există evaluări

- Thisyear LectDocument420 paginiThisyear Lectsantosh vighneshwar hegdeÎncă nu există evaluări

- My Lecture1 Introductiona PDFDocument28 paginiMy Lecture1 Introductiona PDFchaitu4Încă nu există evaluări

- LAN7430 LAN7431 Data - Sheet DS00002631B 1534924Document78 paginiLAN7430 LAN7431 Data - Sheet DS00002631B 1534924Tiago DutraÎncă nu există evaluări

- Coa Unit-3Document11 paginiCoa Unit-3singhshiva8082Încă nu există evaluări

- MMC Unit 8Document59 paginiMMC Unit 8SOMESH B SÎncă nu există evaluări

- BluetoothDocument97 paginiBluetoothDivya DmÎncă nu există evaluări

- First PresentationDocument18 paginiFirst PresentationansiyaeshackÎncă nu există evaluări

- Selecting A Serial Bus: Application Note 3967Document7 paginiSelecting A Serial Bus: Application Note 3967nevdullÎncă nu există evaluări

- Project Report 2Document62 paginiProject Report 2Alex VPÎncă nu există evaluări

- Using FPGAs To Design Gigabit Serial Backplanes - XilinxDocument34 paginiUsing FPGAs To Design Gigabit Serial Backplanes - XilinxA. VillaÎncă nu există evaluări

- Standard I/O Interfances Reference: Call Hamacher, "Computer Organization"Document10 paginiStandard I/O Interfances Reference: Call Hamacher, "Computer Organization"JochumÎncă nu există evaluări

- Common Source Amplifier With Resistor Load Vin 10mV VDD 1V R 10k F 1k Vout 1V G - 100Document3 paginiCommon Source Amplifier With Resistor Load Vin 10mV VDD 1V R 10k F 1k Vout 1V G - 100RenukaÎncă nu există evaluări

- Two Finger Concept 1. NOT GateDocument3 paginiTwo Finger Concept 1. NOT GateRenukaÎncă nu există evaluări

- Two Finger Concept 1. NOT GateDocument3 paginiTwo Finger Concept 1. NOT GateRenukaÎncă nu există evaluări

- Lec 10 ScriptDocument7 paginiLec 10 ScriptRenukaÎncă nu există evaluări

- Common Source Amplifier With Resistor Load Vin 10mV VDD 1V R 10k F 1k Vout 1V G - 100Document3 paginiCommon Source Amplifier With Resistor Load Vin 10mV VDD 1V R 10k F 1k Vout 1V G - 100RenukaÎncă nu există evaluări

- Chapter07 - Electronic Analysis of CMOS Logic GatesDocument38 paginiChapter07 - Electronic Analysis of CMOS Logic GatesRenukaÎncă nu există evaluări

- Inverter - Nand - Nor - DF Common Source, Drain, Gate - Voltage Follower - Diferential Amp - Op Amp Current MirrorDocument10 paginiInverter - Nand - Nor - DF Common Source, Drain, Gate - Voltage Follower - Diferential Amp - Op Amp Current MirrorRenukaÎncă nu există evaluări

- Inverter - Nand - Nor - DF Common Source, Drain, Gate - Voltage Follower - Diferential Amp - Op Amp Current MirrorDocument10 paginiInverter - Nand - Nor - DF Common Source, Drain, Gate - Voltage Follower - Diferential Amp - Op Amp Current MirrorRenukaÎncă nu există evaluări

- VLSIDocument9 paginiVLSIRenukaÎncă nu există evaluări

- Parallel Prefix Adders PresentationDocument35 paginiParallel Prefix Adders Presentations akhilaÎncă nu există evaluări

- L10 - Finite State Recognizers PDFDocument33 paginiL10 - Finite State Recognizers PDFRenukaÎncă nu există evaluări

- Jaipur: Rajasthan Trip January 2016Document1 paginăJaipur: Rajasthan Trip January 2016RenukaÎncă nu există evaluări

- sn74ls90 PDFDocument24 paginisn74ls90 PDFRenukaÎncă nu există evaluări

- Csave AddDocument1 paginăCsave Addsunayana_ghosh2001Încă nu există evaluări

- PX C 3896571Document5 paginiPX C 3896571RenukaÎncă nu există evaluări

- pxc3896571 PDFDocument5 paginipxc3896571 PDFRenukaÎncă nu există evaluări

- Data in A Research TtutDocument65 paginiData in A Research TtutRenuka0% (1)

- Verilog HDL Implementation of Usb To Ethernet ConverterDocument6 paginiVerilog HDL Implementation of Usb To Ethernet ConverterRenukaÎncă nu există evaluări

- Serial Bus Communication Protocols - CAN: Lesson - 19Document22 paginiSerial Bus Communication Protocols - CAN: Lesson - 19jasonÎncă nu există evaluări

- Right ThinkingDocument128 paginiRight ThinkingRenukaÎncă nu există evaluări

- Asa Man ThinkethDocument47 paginiAsa Man ThinkethRenukaÎncă nu există evaluări

- MEMS-based Optical Mini-And Microspectrometers For The Visible and Infrared Spectral RangeDocument8 paginiMEMS-based Optical Mini-And Microspectrometers For The Visible and Infrared Spectral RangeRenukaÎncă nu există evaluări

- Course Registration SlipDocument2 paginiCourse Registration SlipMics EntertainmentÎncă nu există evaluări

- Significance of GodboleDocument5 paginiSignificance of GodbolehickeyvÎncă nu există evaluări

- 3-History Rock Cut MonumentDocument136 pagini3-History Rock Cut MonumentkrishnaÎncă nu există evaluări

- Structural Analysis and Design of Pressure Hulls - The State of The Art and Future TrendsDocument118 paginiStructural Analysis and Design of Pressure Hulls - The State of The Art and Future TrendsRISHABH JAMBHULKARÎncă nu există evaluări

- Lesson 1 Chapter 9 ErosiondepositionDocument1 paginăLesson 1 Chapter 9 Erosiondepositionapi-249320969Încă nu există evaluări

- Main Girders: CrossDocument3 paginiMain Girders: Crossmn4webÎncă nu există evaluări

- Effects of Climate ChangeDocument3 paginiEffects of Climate Changejiofjij100% (1)

- Someone Who Believes in YouDocument1 paginăSomeone Who Believes in YouMANOLO C. LUCENECIOÎncă nu există evaluări

- Astm C892 - 00Document5 paginiAstm C892 - 00reneeÎncă nu există evaluări

- WPBSA Official Rules of The Games of Snooker and Billiards 2020 PDFDocument88 paginiWPBSA Official Rules of The Games of Snooker and Billiards 2020 PDFbabuzducÎncă nu există evaluări

- The Acceptability of Rubber Tree Sap (A As An Alternative Roof SealantDocument7 paginiThe Acceptability of Rubber Tree Sap (A As An Alternative Roof SealantHannilyn Caldeo100% (2)

- Surface TensionDocument13 paginiSurface TensionElizebeth GÎncă nu există evaluări

- Math COT 3Document18 paginiMath COT 3Icy Mae SenadosÎncă nu există evaluări

- Syllabus Unit Iv Unit Commitment and Economic DispatchDocument23 paginiSyllabus Unit Iv Unit Commitment and Economic DispatchBALAKRISHNANÎncă nu există evaluări

- Fully Automatic Coffee Machine - Slimissimo - IB - SCOTT UK - 2019Document20 paginiFully Automatic Coffee Machine - Slimissimo - IB - SCOTT UK - 2019lazareviciÎncă nu există evaluări

- AssessmentDocument9 paginiAssessmentJuan Miguel Sapad AlpañoÎncă nu există evaluări

- The Broadband ForumDocument21 paginiThe Broadband ForumAnouar AleyaÎncă nu există evaluări

- LET General Math ReviewerDocument7 paginiLET General Math ReviewerMarco Rhonel Eusebio100% (1)

- TM-8000 HD Manual PDFDocument37 paginiTM-8000 HD Manual PDFRoxana BirtumÎncă nu există evaluări

- Emw 2007 FP 02093Document390 paginiEmw 2007 FP 02093boj87Încă nu există evaluări

- SCM (Subway Project Report)Document13 paginiSCM (Subway Project Report)Beast aÎncă nu există evaluări

- 4 Force & ExtensionDocument13 pagini4 Force & ExtensionSelwah Hj AkipÎncă nu există evaluări

- Assignment 1Document3 paginiAssignment 1farhang_tÎncă nu există evaluări

- AKI in ChildrenDocument43 paginiAKI in ChildrenYonas AwgichewÎncă nu există evaluări