Documente Academic

Documente Profesional

Documente Cultură

A e 2 004

Încărcat de

CarlosTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

A e 2 004

Încărcat de

CarlosDrepturi de autor:

Formate disponibile

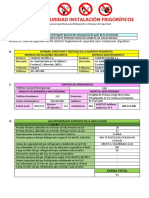

SEGUNDA ACTIVIDAD EVALUABLE

1: Asignatura:

FUNDAMENTOS de SISTEMAS DIGITALES

2: Ttulo de la Actividad: Diseo, Implementacin y Simulacin de un Circuito en Lgica

Secuencial

3: Datos personales:

- Nombre y Apellidos: Luis Pastor Nuevo

- DNI:

03112504Y

- Centro asociado:

Las Tablas (Madrid)

4: Cdigo de la actividad que le ha correspondido realizar : A-E-2-004

5: Enunciado.

Enunciado A-E-2-004

Esta actividad consiste en el diseo e implementacin en el un circuito secuencial que consta

de tres bloque funcionales que realizan funciones claramente diferentes. El primer bloque consiste

en construir un reloj con el circuito de tiempo 555 funcionando como astable. El segundo bloque

consiste en obtener, a partir de este reloj, una onda cuadrada de mayor periodo y, por ultimo, el

tercer bloque consiste en construir un autmata finito controlado por el tren de pulsos anterior y que

acte de una forma u otra en funcin de si este pulso est en alta o en baja. Por tanto, el esquema

a nivel de diagrama de bloques del circuito a disear y simular es el de la siguiente figura:

Reloj

555

Reloj

t1 t2

Generador

de la seal

de control,

x

Circuito

secuencial

de 2 bits

Q1

Q0

Reloj

X

tm = 4T

tm = 4T

Disee el sistema lgico secuencial de la figura para que el circuito secuencial de 2 bits

realice las siguientes funciones:

- Si x=0 el circuito secuencial sigue la secuencia siguiente: 00 10 11 01 00 10 ...

- Si x=1 el circuito secuencial sigue la secuencia siguiente: 00 01 11 00 01 11 ...

pero si est en el estado 10 cuando le llega x=1 se queda en ese estado y no cambia.

Apellidos, nombre: Pastor Nuevo, Luis

DNI: 03112504Y

1/13

Fundamentos de Sistemas Digitales

6: Realizacin del diseo y explicacin de los pasos seguidos para la realizacin del diseo de

los distintos bloques funcionales.

7: Esquemas capturados del simulador, primero presente los esquemas de cada uno de los

bloques funcionales por separado y despus presente el del circuito completo.

8: Descripcin de los parmetros de los componentes utilizados.

9: Cronograma de todas las seales (entrada, control y salida).

10: Explicacin del funcionamiento y verificacin de que el circuito funciona de acuerdo con

las especificaciones del diseo.

11: Explicacin de los problemas/dificultades encontrados y explicacin de la forma y el medio

por el que se han resuelto.

*********

El enunciado de la prctica se divide en tres partes diferenciadas. La

primera consiste en construir un reloj con un circuito de tiempo tipo

555 configurado como astable, seguidamente obtendremos, a partir del

reloj 555 una onda cuadrada de mayor tamao y finalmente

construiremos un autmata finito controlado con el tren de pulsos

anterior.

PRIMER BLOQUE

Empezamos construyendo el circuito de tiempo tipo 555 configurado

como astable. Usaremos el circuito integrado 555D. Se deben colocar 2

resistencias que llamaremos RA y RB para que controlen la carga y

descarga del condensador C. Cuanto menor sea la resistencia, ms

rpido se carga y se descarga el condensador, con lo que es menor el

tiempo en el que la onda est en alta y en baja.

Apellidos, nombre: Pastor Nuevo, Luis

DNI: 03112504Y

2/13

Fundamentos de Sistemas Digitales

El circuito de tiempo 555 diseado sera el siguiente:

A la patilla Control se ha conectado un condensador de 1nF

conectado a tierra, ya que no se va a utilizar, evitando los disparos por

ruido.

El reloj estar conectado a una batera de 5 V, cuyo negativo estar

conectado a tierra. La onda ser de 5V en alta y 0V en baja.

Los tiempos t1 (tiempo en alta) y t2 (tiempo en baja) tendrn que ser

iguales para poder generar una onda cuadrada. Por lo tanto t1 t2 .

Inicialmente se ha dado un valor de 100K tanto a RA como a RB.

Para obtener una onda cuadrada se han modificado los valores de R A,

establecindolo en 85K y de RB, ajustndolo a 105K.

Para que el circuito funcione de un modo ms eficiente se ha

insertado un diodo D1 funcionando en paralelo con RB. De este modo

Apellidos, nombre: Pastor Nuevo, Luis

DNI: 03112504Y

3/13

Fundamentos de Sistemas Digitales

conseguimos que la corriente de carga pase por R A y D1 y que se

descargue nicamente RB.

Llamaremos tiempo de carga a t 1 y tiempo de descarga a t2. Ambos

dependen del valor que tomen las resistencias. A mayor resistencia

mayor ser el tiempo de carga y descarga del condensador.

Sus frmulas seran las siguientes:

t1 0,69* RA*C1 y

t2 0,69* RB* C1

La frecuencia (tiempo total de carga y descarga), tendra la siguiente

frmula:

T= t1+ t2 = 0,69*( RA+ RB)* C1

Los valores seran los siguientes:

t1 = 0,69*100K*10nF = 690seg.

t2 = 0,69*100K*10nF = 690seg.

T= 690+690 = 1380 seg. = 1,380ms.

Pero al modificar el valor de RA y el de RB con el fin de obtener una

onda cuadrada, los tiempos seran los siguientes:

t1 = 0,69*85K*10nF = 586,5seg.

t2 = 0,69*105K*10nF = 724,5seg.

T= 586,5+724,5 = 1311 seg. = 1,311 ms.

Al modificar el valor de RA de 100K a 85K y aumentar RB de

100 K a 105 K se ha reducido la frecuencia (T) en 69seg,

0,069ms. El error tras esta modificacin es mnimo, prcticamente

despreciable.

Apellidos, nombre: Pastor Nuevo, Luis

DNI: 03112504Y

4/13

Fundamentos de Sistemas Digitales

Realizada la simulacin de este circuito, obtenemos el siguiente

cronograma:

Cronograma de circuito 555:

En este cronograma podemos apreciar la onda cuadrada y los picos

de tensin.

La lnea de carga del condensador aparece representada en verde.

En el programa PsPice se han configurado los valores de Transient

de 1 ms a 10 ms. y en el men de anlisis el flip-flop reiniciado a 0.

SEGUNDO BLOQUE

Generador de la seal de control.

Para la realizacin de este segundo bloque el enunciado nos dice que

el periodo de la seal de control, al que llamaremos X, durar 4 veces

la seal generada por el circuito de tiempo 555 del primer bloque. Cada

periodo est formado por la suma del tiempo en alta y el tiempo en

baja.

Vamos a utilizar un contador integrado SN74393.

Apellidos, nombre: Pastor Nuevo, Luis

DNI: 03112504Y

5/13

Fundamentos de Sistemas Digitales

El diseo sera el siguiente:

El contador SN74393 es un contador de pulsos negativos, que

cambia de estado cuando recibe n pulsos negativos.

Se ha elegido la salida QC porque cambia de estado cada 4 pulsos de

reloj. La salida QA cambia con 1 pulso de reloj, QB cambia cada 2

pulsos de reloj y QD cambia cada 8 pulsos de reloj.

Usaremos la salida QC para generar la seal de control X, ya que el

enunciado del ejercicio nos indica que tm = 4T, y QC cumple ese

requisito.

El cronograma de este segundo bloque sera el siguiente:

Apellidos, nombre: Pastor Nuevo, Luis

DNI: 03112504Y

6/13

Fundamentos de Sistemas Digitales

TERCER BLOQUE

Circuito secuencial

En este bloque vamos a sintetizar el circuito secuencial de 2 bits.

Segn nos indica el enunciado, los diagramas de transicin de dicho

circuito seran los siguientes:

X=0

S0

S1

X=1

X=1

X=1

X=0

X=0

S3

S2

X=1

X=0

ESTADO

S0

S1

S2

S3

Q1

0

0

1

1

Q0

0

1

0

1

Segn se nos indica en la gua de estudio de la asignatura, hemos de

sintetizar el circuito secuencial con biestables D. Como tenemos 4

estados distintos nos harn falta 2 bsculas D. Sabiendo que el valor

que toma D es el mismo que el valor de Qt+1 podemos construir la tabla

de verdad del circuito.

Apellidos, nombre: Pastor Nuevo, Luis

DNI: 03112504Y

7/13

Fundamentos de Sistemas Digitales

La tabla de la verdad sera la siguiente:

Q1 Q0 Q1(t+1) Q0(t+1) D1 D0

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

1

0

1

0

0

1

1

0

0

0

1

1

1

1

0

0

1

0

1

0

0

1

1

0

0

0

1

1

1

1

0

0

A partir de esta tabla se pueden sacar las matrices de transicin, que

seran:

0

1

0

0

M(x)=

0

0

0

1

0

1

0

0

0

X

1

0

0

0

0

0

1

0

1

0

0

0

0

0

1

0

0

0

0

1

X

0

0

0

X

0

Apellidos, nombre: Pastor Nuevo, Luis

DNI: 03112504Y

x=

+ x

0

0

0

1

1

0

0

0

0

0

0

1

0

0

1

0

0

1

0

0

1 0 0

0 0 1

0 1 0

0 0 0

0

X

8/13

Fundamentos de Sistemas Digitales

Para poder sintetizar el circuito, hay que sacar de la tabla de la verdad

anterior los valores de Q1(t+1) y de Q0(t+1).

Q1(t+1) = D1 = 10

1 +Q10+X1Q0+XQ10= +Q1 +X Q0

Q0(t+1) = D0 = Q10+Q1Q0+X10

1 +X1Q0 = Q1+X1=X(+)Q1

+

El circuito del bloque 3 quedara del siguiente modo:

Se ha colocado un inversor entre el generador de pulsos y la patilla de

Clear, ya que las bsculas D utilizadas llevan el Clear invertido. A la

entrada de las patillas de Preset se conecta un generador Hi.

Apellidos, nombre: Pastor Nuevo, Luis

DNI: 03112504Y

9/13

Fundamentos de Sistemas Digitales

El cronograma del bloque 3 quedara del siguiente modo:

El circuito completo sera el siguiente:

Apellidos, nombre: Pastor Nuevo, Luis

DNI: 03112504Y

10/13

Fundamentos de Sistemas Digitales

Y el cronograma del circuito completo aparecera del siguiente

modo:

Como se puede apreciar en el cronograma del circuito completo y en el

del bloque 3, los valores Q de salida cambian a medida que X pasa de 0

a 1 o viceversa. Eso si, para que cambien de valor, tiene que coincidir

que Clear se encuentre en baja, ya que de lo contrario los valores de Q

seran 0.

Vamos a comprobar que el circuito funciona correctamente con el

mismo cronograma, configurando el Transient con un valor de tiempo

ms alto:

Apellidos, nombre: Pastor Nuevo, Luis

DNI: 03112504Y

11/13

Fundamentos de Sistemas Digitales

Se puede observar lo siguente:

Periodo

Q1

Q0

D1

D0

2useg

4useg

6useg

10useg

20useg

22useg

24useg

0

0

0

0

1

1

1

0

1

1

0

0

0

1

0

0

1

1

0

1

1

1

1

0

0

0

1

0

0

1

1

0

1

1

0

Comportamiento del

Biestable

X=0 Pasa de 00 a 10

X=0 Pasa de 10 a 11

X=0 Pasa de 11 a 01

X=0 Pasa de 01 a 00

X=1 Pasa de 00 a 01

X=1 Pasa de 01 a 11

X=1 Pasa de 11 a 00

Falta por comprobar si cuando est en el estado 10 y le llega X=1

se queda en ese estado y no cambia.

Como este supuesto no se da en el circuito diseado, para

comprobar que en esas condiciones se comportara como dictamina el

enunciado, lo que se ha hecho es, utilizando generadores Hi y Lo,

atacar las patillas Preset y Clear de ambos biestables D de tal modo

que queden en el estado 10 de manera constante. Estas bsculas D

tienen el Preset y el Clear invertido, por lo que conectando una seal

en baja al Preset y una en alta al Clear, conseguimos que Q tome el

valor constante 1. Hacindolo a la inversa Q toma el valor 0.

El cronograma resultante sera el siguiente:

Apellidos, nombre: Pastor Nuevo, Luis

DNI: 03112504Y

12/13

Fundamentos de Sistemas Digitales

Podemos observar que cuando llega la seal X=1, teniendo Q1 y Q0

valor constante 1 y 0 respectivamente, D1 y D0 no cambian de estado

hasta que no lo hace la seal X. D1 y D0 se mantienen en el estado 10.

Lo podemos observar, por ejemplo, a los 25 useg. , y como D 1 toma

siempre el mismo valor que Q1 y D0 el mismo que Q0 llegamos a la

conclusin de que el circuito cumple con esa condicin que se nos

exiga en el enunciado del ejercicio.

Con estas comprobaciones realizadas podemos afirmar que el

circuito est diseado de manera eficiente.

Para sintetizar el circuito se han utilizado un reloj integrado 555D, un

contador SN94393, 2 bsculas D, 2 condensadores, un diodo

D1N4148, 3 resistencias, 2 tomas tierra, una pila de 5V, 2

generadores de pulsos, 2 puertas AND de 2 entradas, 3 inversores, 1

puerta AND de 3 entradas, 2 puertas OR, 1 puerta XOR, un generador

HI y un generador LO.

Las principales dificultades encontradas han sido dar el valor correcto a

las resistencias para configurar el circuito 555 como astable, as como

encontrar los parmetros de tiempo adecuados en el programa de

simulacin, para que los cronogramas salieran del modo adecuado.

El ejercicio es muy completo, ya que hay que tener bien asimilados

temas distintos de la asignatura, desde relojes a biestables tipo D,

pasando por contadores.

Luis Pastor Nuevo

DNI: 03112504Y

Ejercicio: A-E-2-004

Centro Asociado: Las Tablas

Apellidos, nombre: Pastor Nuevo, Luis

DNI: 03112504Y

13/13

S-ar putea să vă placă și

- Cardenas Mendez Christian M18S3AI5Document4 paginiCardenas Mendez Christian M18S3AI5Martha Iveth100% (1)

- Periodo Pendulo SimpleDocument3 paginiPeriodo Pendulo Simplejesus castilloÎncă nu există evaluări

- Cerro AzulDocument17 paginiCerro AzulVelko Marusic VerdeguerÎncă nu există evaluări

- 2a Sesión-CT-UDEEIDocument12 pagini2a Sesión-CT-UDEEISamira MascorroÎncă nu există evaluări

- Tarea 8 - Silogismos Válidos o InválidosDocument2 paginiTarea 8 - Silogismos Válidos o InválidosMynor Lopez50% (2)

- Elementos Pasivos y Activos de Una Red PDFDocument10 paginiElementos Pasivos y Activos de Una Red PDFオヘダ ウィルマーÎncă nu există evaluări

- Actividad 3 Ensayo Nomina ElectronicaDocument4 paginiActividad 3 Ensayo Nomina ElectronicaBelquis Del Carmen TINOCO DIAZÎncă nu există evaluări

- Manejo Técnico de PacoDocument29 paginiManejo Técnico de PacoNelson Roger Saire Choquenaira100% (3)

- IItebameDocument176 paginiIItebameFidel Huanco RamosÎncă nu există evaluări

- Taller de EconomiaDocument13 paginiTaller de EconomiaBrayanÎncă nu există evaluări

- PáginaDocument193 paginiPáginaWalter Emilio Murillo SernaÎncă nu există evaluări

- Coherencia y CohesionDocument37 paginiCoherencia y CohesionAlejandro Parra75% (8)

- La Planificacion Estrategica de Una Empresa TuristicaDocument2 paginiLa Planificacion Estrategica de Una Empresa TuristicaPam Palomino AlegreÎncă nu există evaluări

- ¿Debemos Seguir Empleando El Concepto de Raza?Document4 pagini¿Debemos Seguir Empleando El Concepto de Raza?Russel Garcia buendiaÎncă nu există evaluări

- Apuntes Semana 10 y 11Document8 paginiApuntes Semana 10 y 11coniÎncă nu există evaluări

- Anomalias IntermaxilaresDocument10 paginiAnomalias IntermaxilaresValentina Alejandra Pedreros PavezÎncă nu există evaluări

- Resumen Del Libro La MetaDocument6 paginiResumen Del Libro La MetaCLAUDIA CUACIALPUD LASSO0% (1)

- Carta Revision Instalaciones ElectricaDocument2 paginiCarta Revision Instalaciones ElectricaAbimael seguraÎncă nu există evaluări

- Cartel Inspeccion TortosaDocument2 paginiCartel Inspeccion Tortosavideos gym VictorPascualÎncă nu există evaluări

- Manual Sap 2000 (Español)Document211 paginiManual Sap 2000 (Español)Peter100% (1)

- Clase 2Document40 paginiClase 2Nelson Cornejo MirandaÎncă nu există evaluări

- Wa0056.Document9 paginiWa0056.Laura PadillaÎncă nu există evaluări

- Edgardo Javier Morillo Revelo, Modelo PACIE InvestigaciónDocument6 paginiEdgardo Javier Morillo Revelo, Modelo PACIE InvestigaciónJavier120427Încă nu există evaluări

- La Filosofía MedievalDocument18 paginiLa Filosofía MedievalCASTRO NIVELA GISELLAÎncă nu există evaluări

- Atados de Hierbas para Sahumar PDFDocument2 paginiAtados de Hierbas para Sahumar PDFMarina Torcivia50% (2)

- Portafolio de Evidencias - VistaDocument9 paginiPortafolio de Evidencias - VistaAileen LandinÎncă nu există evaluări

- Matematica Discreta 2017Document4 paginiMatematica Discreta 2017Esteban NicolauÎncă nu există evaluări

- Dansa Spa R.U.T.:76.810.719-K Factura Electronica Nº276: S.I.I. - Santiago OrienteDocument2 paginiDansa Spa R.U.T.:76.810.719-K Factura Electronica Nº276: S.I.I. - Santiago OrienteRaida RodriguezÎncă nu există evaluări

- Clase - AcotamientoDocument25 paginiClase - AcotamientoEdwin GomezÎncă nu există evaluări

- Aplicación de Políticas Públicas en Las Instituciones de EducativasDocument18 paginiAplicación de Políticas Públicas en Las Instituciones de EducativasSantiago Htc100% (1)