Documente Academic

Documente Profesional

Documente Cultură

2.2 Basic Integrated Circuit Processes: Objective

Încărcat de

Lalit BurrakTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

2.2 Basic Integrated Circuit Processes: Objective

Încărcat de

Lalit BurrakDrepturi de autor:

Formate disponibile

Basic IC Processes (5/30/00)

Page 1

2.2 BASIC INTEGRATED CIRCUIT PROCESSES

INTRODUCTION

Objective

The objective of this presentation is:

1.) Introduce the fabrication of integrated circuits

2.) Describe the basic fabrication process steps by which an integrated circuit is made

Outline

Integrated circuit fabrication

Basic processing steps

ECE 4430 - Analog Integrated Circuits and Systems

P.E. Allen, 2000

Basic IC Processes (5/30/00)

Page 2

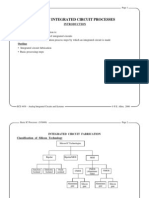

INTEGRATED CIRCUIT FABRICATION

Classification of Silicon Technology

Silicon IC Technologies

Bipolar

Junction

Isolated

Dielectric

Isolated

Bipolar/MOS

Oxide

isolated

CMOS

Aluminum

gate

ECE 4430 - Analog Integrated Circuits and Systems

MOS

PMOS

(Aluminum

Gate)

Silicon

gate

NMOS

Aluminum

gate

Silicon

gate

P.E. Allen, 2000

Basic IC Processes (5/30/00)

Page 3

Comparison of Bipolar and CMOS Technologies

Comparison of BJT and MOSFET technology from an analog viewpoint:

Feature

BJT

MOSFET

Cutoff Frequency(fT)

100 GHz

50 GHz (0.25m)

Noise (thermal about the same)

Less 1/f

More 1/f

DC Range of Operation

9 decades of exponential

current versus vBE

2-3 decades of square law

behavior

Small Signal Output Resistance

Slightly larger

Smaller for short channel

Switch Implementation

Poor

Good

Capacitor Implementation

Voltage dependent

Reasonably good

Which is best?

Almost every comparison favors the BJT, however a similar comparison made from a digital viewpoint

would come up on the side of CMOS.

Therefore, since large-volume technology will be driven by digital demands, CMOS is an obvious

result as the technology of availability.

Other factors:

The potential for technology improvement for CMOS is greater than for BJT

Performance generally increases with decreasing channel length

BiCMOS may be the best compromise for the mixed signal system on a chip.

ECE 4430 - Analog Integrated Circuits and Systems

P.E. Allen, 2000

Basic IC Processes (5/30/00)

Page 4

BASIC FABRICATION PROCESSES

Basic steps

Oxide growth

Thermal diffusion

Ion implantation

Deposition

Etching

Epitaxy

Photolithography

Photolithography is the means by which the above steps are applied to selected areas of the silicon wafer.

Silicon wafer

125-200 mm

(5"-8")

n-type: 3-5 -cm

p-type: 14-16 -cm

ECE 4430 - Analog Integrated Circuits and Systems

0.5-0.8mm

Fig. 2.1-1r

P.E. Allen, 2000

Basic IC Processes (5/30/00)

Page 5

Oxidation

Description:

Oxidation is the process by which a layer of silicon dioxide is grown on the surface of a silicon wafer.

Original silicon surface

tox

Silicon dioxide

0.44 tox

Silicon substrate

Fig. 2.1-2

Uses:

Protect the underlying material from contamination

Provide isolation between two layers.

Very thin oxides (100 to 1000) are grown using dry oxidation techniques. Thicker oxides (>1000)

are grown using wet oxidation techniques.

ECE 4430 - Analog Integrated Circuits and Systems

P.E. Allen, 2000

Basic IC Processes (5/30/00)

Page 6

Diffusion

Diffusion is the movement of impurity atoms at the surface of the silicon into the bulk of the silicon.

Always in the direction from higher concentration to lower concentration.

Low

Concentration

High

Concentration

Fig. 2.1-3

Diffusion is typically done at high temperatures: 800 to 1400C

ERFC

Gaussian

N0

N0

t1 < t2 < t3

t1 < t2 < t3

N(x)

NB

NB

N(x)

t1

t2

Depth (x)

(a) Infinite source of impurities at the surface.

ECE 4430 - Analog Integrated Circuits and Systems

t3

t1

t2

t3

Depth (x)

(b) a finite source of impurities at the surface.)

P.E. Allen, 2000

Basic IC Processes (5/30/00)

Page 7

Ion Implantation

Ion implantation is the process by which impurity ions are accelerated to a high velocity and physically

lodged into the target material.

Path of

impurity

atom

Fixed Atom

Fixed Atom

Impurity Atom

final resting place

Fixed Atom

Fig. 2.1-5

Anneal is required to activate the impurity atoms and repair the physical damage to the crystal lattice.

This step is done at 500 to 800C.

Ion implantation is a lower temperature process compared to diffusion.

Can implant through surface layers, thus it is useful for fieldConcentration peak

threshold adjustment.

N(x)

Can achieve unique doping profile such as buried concentration

peak.

NB

0

ECE 4430 - Analog Integrated Circuits and Systems

Depth (x)

Fig. 2.1-6

P.E. Allen, 2000

Basic IC Processes (5/30/00)

Page 8

Deposition

Deposition is the means by which various materials are deposited on the silicon wafer.

Examples:

Silicon nitride (Si3N4)

Silicon dioxide (SiO2)

Aluminum

Polysilicon

There are various ways to deposit a material on a substrate:

Chemical-vapor deposition (CVD)

Low-pressure chemical-vapor deposition (LPCVD)

Plasma-assisted chemical-vapor deposition (PECVD)

Sputter deposition

Material that is being deposited using these techniques cover the entire wafer.

ECE 4430 - Analog Integrated Circuits and Systems

P.E. Allen, 2000

Basic IC Processes (5/30/00)

Page 9

Etching

Etching is the process of selectively removing a layer of material.

When etching is performed, the etchant may remove portions or all of:

The desired material

The underlying layer

The masking layer

Important considerations:

Anisotropy of the etch is defined as,

A = 1-(lateral etch rate/vertical etch rate)

Selectivity of the etch (film to mask and film to substrate) is defined as,

film etch rate

Sfilm-mask = mask etch rate

A = 1 and Sfilm-mask = are desired.

There are basically two types of etches:

Wet etch which uses chemicals

Dry etch which uses chemically active ionized gases.

a

Fig. 2.1-7

Mask

Film

Selectivity

Mask

Film

Underlying layer

(a) Portion of the top layer ready for etching.

ECE 4430 - Analog Integrated Circuits and Systems

c

Selectivity

Anisotropy

Underlying layer

(b) Horizontal etching and etching of underlying layer.

P.E. Allen, 2000

Basic IC Processes (5/30/00)

Page 10

Epitaxy

Epitaxial growth consists of the formation of a layer of single-crystal silicon on the surface of the silicon

material so that the crystal structure of the silicon is continuous across the interfaces.

It is done externally to the material as opposed to diffusion which is internal

The epitaxial layer (epi) can be doped differently, even oppositely, of the material on which it grown

It accomplished at high temperatures using a chemical reaction at the surface

The epi layer can be any thickness, typically 1-20 microns

Gaseous cloud containing SiCL4 or SiH4

Si +

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

- Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

+

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Fig. 2.1-7.5

ECE 4430 - Analog Integrated Circuits and Systems

P.E. Allen, 2000

Basic IC Processes (5/30/00)

Page 11

Photolithography

Components

Photoresist material

Mask

Material to be patterned (e.g., oxide)

Positive photoresist

Areas exposed to UV light are soluble in the developer

Negative photoresist

Areas not exposed to UV light are soluble in the developer

Steps

1. Apply photoresist

2. Soft bake (drives off solvents in the photoresist)

3. Expose the photoresist to UV light through a mask

4. Develop (remove unwanted photoresist using solvents)

5. Hard bake ( 100C)

6. Remove photoresist (solvents)

ECE 4430 - Analog Integrated Circuits and Systems

P.E. Allen, 2000

Basic IC Processes (5/30/00)

Page 12

Illustration of Photolithography - Exposure

Photomask

The process of exposing selective

areas to light through a photomask is called printing.

Types of printing include:

Contact printing

Proximity printing

Projection printing

UV Light

Photomask

Photoresist

Polysilicon

Fig. 2.1-8

ECE 4430 - Analog Integrated Circuits and Systems

P.E. Allen, 2000

Basic IC Processes (5/30/00)

Page 13

Illustration of Photolithography - Positive Photoresist

Develop

Polysilicon

Photoresist

Etch

Photoresist

Polysilicon

Remove

photoresist

Polysilicon

Fig. 2.1-9

ECE 4430 - Analog Integrated Circuits and Systems

P.E. Allen, 2000

Basic IC Processes (5/30/00)

Page 14

Illustration of Photolithography - Negative Photoresist

(Not used much any more)

Photoresist

Underlying Layer

Photoresist

SiO2

Underlying Layer

SiO2

SiO2

Underlying Layer

ECE 4430 - Analog Integrated Circuits and Systems

Fig. 2.1-10

P.E. Allen, 2000

Basic IC Processes (5/30/00)

Page 15

SUMMARY

Fabrication is the means by which the circuit components, both active and passive, are built as an

integrated circuit.

Basic process steps include:

Oxide growth

Thermal diffusion

Ion implantation

Deposition

Etching

Epitaxy

These steps are restricted to a physical area by the use of photolithography.

The use of photolithography to apply a process to a certain area is called a masking step.

The complexity of a process can be measured in the terms of the number of masking steps or masks

required to implement the process.

ECE 4430 - Analog Integrated Circuits and Systems

P.E. Allen, 2000

S-ar putea să vă placă și

- 2.2 Basic Integrated Circuit Processes: ObjectiveDocument15 pagini2.2 Basic Integrated Circuit Processes: Objectivetutul_kÎncă nu există evaluări

- CMOS Tech-2UP (12 - 11 - 03)Document29 paginiCMOS Tech-2UP (12 - 11 - 03)Mountsinai CscÎncă nu există evaluări

- Unit - IDocument69 paginiUnit - IsaravananÎncă nu există evaluări

- Ic FabricationDocument7 paginiIc FabricationphooolÎncă nu există evaluări

- How Semicon WorksDocument15 paginiHow Semicon WorkskrisÎncă nu există evaluări

- M Group: Linear Integrated Circuits (Ec1313) IC FabricationDocument17 paginiM Group: Linear Integrated Circuits (Ec1313) IC Fabricationscribdm100% (1)

- EC1313 Two Marks Linear Integrated CircuitsDocument11 paginiEC1313 Two Marks Linear Integrated Circuitsmoney_kandan2004Încă nu există evaluări

- IC FabricationDocument27 paginiIC FabricationJohn PaulÎncă nu există evaluări

- Unit I Ic FabricationDocument23 paginiUnit I Ic FabricationBhuvana VaradharajÎncă nu există evaluări

- EE6303-Linear Integrated Circuits and Applications Q&ADocument24 paginiEE6303-Linear Integrated Circuits and Applications Q&AY RohitÎncă nu există evaluări

- Chapter 4fabricationofICDocument20 paginiChapter 4fabricationofICManikandan RadhakrishnanÎncă nu există evaluări

- Ic FabricationDocument31 paginiIc FabricationMukesh Nexus100% (1)

- Ic Fabrication Ansaf RmahDocument27 paginiIc Fabrication Ansaf RmahkaisobaiedÎncă nu există evaluări

- Ee2254 Lica QBDocument0 paginiEe2254 Lica QBnjparÎncă nu există evaluări

- Integrated CircuitDocument51 paginiIntegrated Circuitparthos100% (1)

- Chapter 5 Fabrication of Microelectronic DevicesDocument35 paginiChapter 5 Fabrication of Microelectronic Devicesmuhamadsaidi60% (5)

- Eem413e Lecture-Week4Document47 paginiEem413e Lecture-Week4Furkan AvcıoğluÎncă nu există evaluări

- Microfabrication: Yash V. Kankal Roll No.Document31 paginiMicrofabrication: Yash V. Kankal Roll No.yogesh_lonkarÎncă nu există evaluări

- Thermal Oxidation Process BasicsDocument104 paginiThermal Oxidation Process BasicsBalamurugan Velayutham100% (1)

- Lec 4 CMOS Technology ICFabricationDocument46 paginiLec 4 CMOS Technology ICFabricationMainak TarafdarÎncă nu există evaluări

- LIC Unit 1Document20 paginiLIC Unit 1sietgunaÎncă nu există evaluări

- Introduction To Integrated Circuit TechnologyDocument45 paginiIntroduction To Integrated Circuit TechnologyShrikant JagtapÎncă nu există evaluări

- 5 LicaDocument26 pagini5 LicaVantharAlaÎncă nu există evaluări

- EE2254 LIC 2marks 2013Document16 paginiEE2254 LIC 2marks 2013sivagamiÎncă nu există evaluări

- 1 Fabrication 20130218 PDFDocument108 pagini1 Fabrication 20130218 PDFAjay kr PradhanÎncă nu există evaluări

- IC Fabrication Process: Course: VLSI DesignDocument14 paginiIC Fabrication Process: Course: VLSI DesignDwayne WaltonÎncă nu există evaluări

- Fabrication of Ic'sDocument14 paginiFabrication of Ic'sBhaskar Rao OndruÎncă nu există evaluări

- Technology Brief 7: Integrated Circuit Fabrication Process: Semiconductor Processing BasicsDocument4 paginiTechnology Brief 7: Integrated Circuit Fabrication Process: Semiconductor Processing BasicsAshima PatleyÎncă nu există evaluări

- Basic of Device Fabrication: Introduction to Key StepsDocument60 paginiBasic of Device Fabrication: Introduction to Key StepsSerwan BamerniÎncă nu există evaluări

- IC Manufacturing Process: SudhaDocument13 paginiIC Manufacturing Process: SudhaSudha KÎncă nu există evaluări

- Manufacturing of Microprocessor: Farooq Ahmad ShahDocument18 paginiManufacturing of Microprocessor: Farooq Ahmad ShahCristianCristianHerreraÎncă nu există evaluări

- CM - MEMS - TWO MARKS Five UNITSDocument7 paginiCM - MEMS - TWO MARKS Five UNITSSandhiyaÎncă nu există evaluări

- LINEAR INTEGRATED CIRUITS - 2 Marks Question Bank - IV Sem ECEDocument19 paginiLINEAR INTEGRATED CIRUITS - 2 Marks Question Bank - IV Sem ECEJOHN PETER100% (7)

- CMOS Fabrication: (With Extended Comments)Document26 paginiCMOS Fabrication: (With Extended Comments)srivardhana7Încă nu există evaluări

- Semiconductor Device Fabrication ProcessDocument13 paginiSemiconductor Device Fabrication ProcessHasi De RustafariÎncă nu există evaluări

- Unit 1Document66 paginiUnit 1srgperumalÎncă nu există evaluări

- MODULEDocument53 paginiMODULENithin GopalÎncă nu există evaluări

- Presentation 1 LicDocument28 paginiPresentation 1 LicreporterrajiniÎncă nu există evaluări

- Vlsi FabDocument8 paginiVlsi FabhaheÎncă nu există evaluări

- Aezy Joy T. Lascano Engr. May C. Layson Bsece-5ADocument5 paginiAezy Joy T. Lascano Engr. May C. Layson Bsece-5AAljon Ticsay LascanoÎncă nu există evaluări

- Midterm Exam 1Document9 paginiMidterm Exam 1Hemal ShahporiaÎncă nu există evaluări

- Fab StepsDocument20 paginiFab StepsShwethÎncă nu există evaluări

- Ee6303 - Linear Integrated CircuitsDocument13 paginiEe6303 - Linear Integrated CircuitsSaran ArunÎncă nu există evaluări

- Unit - I: Vlsi Fabrication TechniquesDocument64 paginiUnit - I: Vlsi Fabrication TechniquesAnand KumarÎncă nu există evaluări

- Ee6303 Uw LicDocument125 paginiEe6303 Uw LicVijay KumarÎncă nu există evaluări

- C-1 CMOS Processing FlowDocument76 paginiC-1 CMOS Processing FlowKu Ble YanÎncă nu există evaluări

- IC Production Process by PhaniDocument30 paginiIC Production Process by PhaniPhani HarimanikyamÎncă nu există evaluări

- IC Fabrication TechnologyDocument12 paginiIC Fabrication TechnologyBiswajit BeheraÎncă nu există evaluări

- Silicon On Insulator TechnologyDocument32 paginiSilicon On Insulator TechnologyJayanth bemesettyÎncă nu există evaluări

- Epitaxy GrowthDocument24 paginiEpitaxy GrowthMD. MEHEDI HASAN100% (3)

- CMOS TechnologiesDocument27 paginiCMOS TechnologiesDebela TesfayeÎncă nu există evaluări

- Integrated Circuit Fabrication ProcessDocument14 paginiIntegrated Circuit Fabrication ProcessSanthosh DheerajÎncă nu există evaluări

- Lecture 42Document18 paginiLecture 42Nathan KemboÎncă nu există evaluări

- Unit IDocument37 paginiUnit IDINESH KUMAR DRAVIDAMANIÎncă nu există evaluări

- Steps For IC Manufacturing - VLSI Tutorials - MepitsDocument6 paginiSteps For IC Manufacturing - VLSI Tutorials - MepitsAbhiÎncă nu există evaluări

- Index of IC Fabrication and Op-Amp CharacteristicsDocument20 paginiIndex of IC Fabrication and Op-Amp Characteristicssimbu oneoneÎncă nu există evaluări

- Ceramic Materials for Energy Applications VIDe la EverandCeramic Materials for Energy Applications VIHua-Tay LinÎncă nu există evaluări

- Compendium of Atomic Alkali Resistant Optical Thin Films, Diffusion and Electrical Mobility in Diode Pumped Alkali Lasers (DPALs)De la EverandCompendium of Atomic Alkali Resistant Optical Thin Films, Diffusion and Electrical Mobility in Diode Pumped Alkali Lasers (DPALs)Încă nu există evaluări

- Plasma Etching Processes for Interconnect Realization in VLSIDe la EverandPlasma Etching Processes for Interconnect Realization in VLSINicolas PossemeÎncă nu există evaluări

- Isc BD933F/935F/937F/939F/941F: Isc Silicon NPN Power TransistorDocument2 paginiIsc BD933F/935F/937F/939F/941F: Isc Silicon NPN Power TransistorjuanangelmallorquinÎncă nu există evaluări

- Bel 06 Field Effect TransistorDocument17 paginiBel 06 Field Effect TransistorBharavi K SÎncă nu există evaluări

- C5440 PanasonicSemiconductorDocument2 paginiC5440 PanasonicSemiconductorteniÎncă nu există evaluări

- 06 Programmable Logic DevicesDocument28 pagini06 Programmable Logic DevicesChen ShyanÎncă nu există evaluări

- Bipolar Junction Transistors (BJTS)Document28 paginiBipolar Junction Transistors (BJTS)Musa MagaulaÎncă nu există evaluări

- Determining Boltzmann Constant Using Silicon Diode I-V CharacteristicsDocument7 paginiDetermining Boltzmann Constant Using Silicon Diode I-V CharacteristicsRoy RickyÎncă nu există evaluări

- Semiconductor Devices and Diodes NotesDocument19 paginiSemiconductor Devices and Diodes Notesعبدالرحمن محمد جاسم حمودÎncă nu există evaluări

- How Zener Diodes Regulate VoltageDocument22 paginiHow Zener Diodes Regulate VoltageRafath UmaimathÎncă nu există evaluări

- Unisonic Technologies Co.,Ltd: High Voltage High Speed SwitchingDocument5 paginiUnisonic Technologies Co.,Ltd: High Voltage High Speed SwitchingEngin UzunÎncă nu există evaluări

- CS3205 A8Document10 paginiCS3205 A8Rian BattlaxÎncă nu există evaluări

- A New Buried-Oxide-In-Drift Region Trench-Gate Power MOSFET With Improved Breakdown VoltageDocument3 paginiA New Buried-Oxide-In-Drift Region Trench-Gate Power MOSFET With Improved Breakdown VoltageMamidala Jagadesh KumarÎncă nu există evaluări

- I-V Characteristics of SCR, DIAC, TRIACDocument14 paginiI-V Characteristics of SCR, DIAC, TRIACShouvik MitraÎncă nu există evaluări

- I-V Characteristic of A Solar CellDocument4 paginiI-V Characteristic of A Solar Cellzubair100% (1)

- Regras de Projeto AMS CMOS 0.35Document32 paginiRegras de Projeto AMS CMOS 0.35Bárbara BrittoÎncă nu există evaluări

- Carrier Generation and RecombinationDocument4 paginiCarrier Generation and RecombinationArendra RajputÎncă nu există evaluări

- BJT Cut-Off/active/saturation ModeDocument5 paginiBJT Cut-Off/active/saturation ModeDildar Khan BhatiÎncă nu există evaluări

- Choosing Power Switching Devices For SMPS Designs: Mosfets or Igbts?Document6 paginiChoosing Power Switching Devices For SMPS Designs: Mosfets or Igbts?RubenG200Încă nu există evaluări

- High Current Silicon Darlington Transistors NTE2349 & NTE2350Document2 paginiHigh Current Silicon Darlington Transistors NTE2349 & NTE2350Saem BachÎncă nu există evaluări

- Syllabus ECE 30500 - SchubertDocument2 paginiSyllabus ECE 30500 - Schubertnawinnawmu1026Încă nu există evaluări

- Power Electronics: Prof. Shete Omkar M. SRCOE, Pune Department of Electrical Engineering University of PuneDocument84 paginiPower Electronics: Prof. Shete Omkar M. SRCOE, Pune Department of Electrical Engineering University of PuneOmkar SheteÎncă nu există evaluări

- In CIrcuit Transistor TesterDocument2 paginiIn CIrcuit Transistor TesterCJ7WYÎncă nu există evaluări

- Course Name ClassstartdateDocument276 paginiCourse Name ClassstartdateRishabh GuptaÎncă nu există evaluări

- Data Transistor 2241Document2 paginiData Transistor 2241heruÎncă nu există evaluări

- Alexander Wuerch ResumeDocument1 paginăAlexander Wuerch Resumeapi-640178684Încă nu există evaluări

- The Depletion LoadDocument5 paginiThe Depletion LoadVidhya DsÎncă nu există evaluări

- Transistor Transistor LogicDocument33 paginiTransistor Transistor LogicCaranto Lois CarantoÎncă nu există evaluări

- STD16NF06: N-Channel 60V - 0.060 - 16A - DPAK Stripfet™ Ii Power MosfetDocument11 paginiSTD16NF06: N-Channel 60V - 0.060 - 16A - DPAK Stripfet™ Ii Power MosfetJose AlbertoÎncă nu există evaluări

- AIMBG120R020M1Document15 paginiAIMBG120R020M1Maike SongÎncă nu există evaluări

- SAED90DR Rev1 2 21.01.2011Document24 paginiSAED90DR Rev1 2 21.01.2011Cherry AbhiÎncă nu există evaluări