Documente Academic

Documente Profesional

Documente Cultură

DS0026 Dual High-Speed MOS Driver: General Description Features

Încărcat de

lujorebTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

DS0026 Dual High-Speed MOS Driver: General Description Features

Încărcat de

lujorebDrepturi de autor:

Formate disponibile

DS0026

Dual High-Speed MOS Driver

General Description

Features

DS0026 is a low cost monolithic high speed two phase MOS

clock driver and interface circuit. Unique circuit design provides both very high speed operation and the ability to drive

large capacitive loads. The device accepts standard TTL outputs and converts them to MOS logic levels. The device may

be driven from standard 54/74 series and 54S/74S series

gates and flip-flops or from drivers such as the DS8830 or

DM7440. The DS0026 is intended for applications in which

the output pulse width is logically controlled; i.e., the output

pulse width is equal to the input pulse width.

The DS0026 is designed to fulfill a wide variety of MOS interface requirements. Information on the correct usage of the

DS0026 in these as well as other systems is included in the

application note AN-76.

n

n

n

n

n

Fast rise and fall times 20 ns 1000 pF load

High output swing 20V

High output current drive 1.5 amps

TTL compatible inputs

High rep rate 5 to 10 MHz depending on power

dissipation

n Low power consumption in MOS 0 state 2 mW

n Drives to 0.4V of GND for RAM address drive

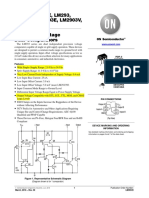

Connection Diagrams (Top Views)

Dual-In-Line Package

DS005853-2

Order Number DS0026CN

See NS Package Number N08E

2000 National Semiconductor Corporation

DS005853

www.national.com

DS0026 Dual High-Speed MOS Driver

February 2000

DS0026

Absolute Maximum Ratings (Note 1)

Maximum Power Dissipation* at TA =

25C

Operating Temperature Range

Storage Temperature Range

Lead Temperature

(Soldering, 10 sec.)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

V+ V Differential Voltage

Input Current

Input Voltage (VIN V)

Peak Output Current

22V

100 mA

5.5V

1.5A

420mW

0C to +70C

65C to +150C

300C

Note: *Derate N08E package 9.3 mW/C for TA above 25C.JA = 107C/W

Electrical Characteristics (Notes 2, 3, 4)

Symbol

Parameter

Conditions

VIH

Logic 1 Input Voltage

V = 0V

IIH

Logic 1 Input Current

VIL

Logic 0 Input Voltage

VIN V = 2.4V

V = 0V

IIL

Logic 0 Input Current

VOL

Logic 1 Output Voltage

VOH

Logic 0 Output Voltage

ICC(ON)

ON Supply Current

(one side on)

ICC(OFF)

OFF Supply Current

Min

Typ

1.5

V+ 1.0

Units

15

mA

10

VIN V = 0V

VIN V = 2.4V, IOL = 1 mA

VIN V = 0.4V, VSS V+ + 1.0V

IOH = 1 mA

V+ V = 20V, VIN V = 2.4V

Max

0.6

0.4

10

V+0.7

V+1.0

V+0.8

V+ V = 20V,

VIN V = 0V

30

40

mA

10

100

Switching Characteristics

(TA = 25C) (Notes 5, 6)

Symbol

Parameter

tON

Turn-On Delay

tOFF

Turn-Off Delay

Conditions

(Figure 1)

Rise Time

tf

Fall Time

Typ

Max

Units

7.5

12

ns

15

ns

(Figure 2)

11

(Figure 1)

12

(Figure 2)

tr

Min

ns

13

ns

(Figure 1),

(Note 5)

CL = 500 pF

CL = 1000 pF

15

18

ns

20

35

ns

(Figure 2),

(Note 5)

CL = 500 pF

CL = 1000 pF

CL = 500 pF

30

40

ns

36

50

ns

12

16

ns

CL = 1000 pF

CL = 500 pF

CL = 1000 pF

17

25

ns

28

35

ns

31

40

ns

(Figure 1),

(Note 5)

(Figure 2),

(Note 5)

Note 1: Absolute Maximum Ratings are those values beyond which the safety of the device cannot be guaranteed. Except for Operating Temperature Range they

are not meant to imply that the devices should be operated at these limits. The table of Electrical Characteristics provides conditions for actual device operation.

Note 2: These specifications apply for V+ V = 10V to 20V, CL = 1000 pF, over the temperature range of 0C to +70C for the DS0026CN.

Note 3: All currents into device pins shown as positive, out of device pins as negative, all voltages referenced to ground unless otherwise noted. All values shown

as max or min on absolute value basis.

Note 4: All typical values for TA = 25C.

Note 5: Rise and fall time are given for MOS logic levels; i.e., rise time is transition from logic 0 to logic 1 which is voltage fall.

Note 6: The high current transient (as high as 1.5A) through the resistance of the internal interconnecting V lead during the output transition from the high state to

the low state can appear as negative feedback to the input. If the external interconnecting lead from the driving circuit to V is electrically long, or has significant dc

resistance, it can subtract from the switching response.

www.national.com

DS0026

Typical VBB Connection

DS005853-8

Typical Performance Characteristics

Input Current vs Input Voltage

Supply Current vs Temperature

Turn-On and Turn-Off Delay

vs Temperature

DS005853-23

DS005853-22

DS005853-24

Rise Time vs Load

Capacitance

Fall Time vs Load

Capacitance

DS005853-25

DS005853-26

www.national.com

DS0026

Typical Performance Characteristics

(Continued)

Recommended Input Coding

Capacitance

DC Power (PDC) vs

Duty Cycle

DS005853-28

DS005853-27

Schematic Diagram

1/2 DS0026

DS005853-10

www.national.com

DS0026

AC Test Circuits and Switching Time Waveforms

DS005853-13

DS005853-12

FIGURE 1.

DS005853-15

DS005853-14

FIGURE 2.

Typical Applications

Application Hints

DRIVING THE MM5262 WITH THE

DS0026 CLOCK DRIVER

The clock signals for the MM5262 have three requirements

which have the potential of generating problems for the user.

These requirements, high speed, large voltage swing and

large capacitive loads, combine to provide ample opportunity

for inductive ringing on clock lines, coupling clock signals to

other clocks and/or inputs and outputs and generating noise

on the power supplies. All of these problems have the potential of causing the memory system to malfunction. Recognizing the source and potential of these problems early in the

design of a memory system is the most critical step. The object here is to point out the source of these problems and

give a quantitative feel for their magnitude.

Line ringing comes from the fact that at a high enough frequency any line must be considered as a transmission line

with distributed inductance and capacitance. To see how

much ringing can be tolerated we must examine the clock

voltage specification. Figure 3 shows the clock specification,

in diagram form, with idealized ringing sketched in. The ringing of the clock about the VSS level is particularly critical. If

the VSS 1 VOH is not maintained, at all times, the information stored in the memory could be altered. Referring to Figure 1, if the threshold voltage of a transistor were 1.3V, the

clock going to VSS 1 would mean that all the devices,

whose gates are tied to that clock, would be only 300 mV

from turning on. The internal circuitry needs this noise margin and from the functional description of the RAM it is easy

to see that turning a clock on at the wrong time can have disastrous results.

AC Coupled MOS Clock Driver

DS005853-16

DC Coupled RAM Memory Address or Precharge

Driver (Positive Supply Only)

DS005853-17

www.national.com

DS0026

Application Hints

(Continued)

DS005853-18

FIGURE 3. Clock Waveform

Controlling the clock ringing is particularly difficult because of

the relative magnitude of the allowable ringing, compared to

magnitude of the transition. In this case it is 1V out of 20V or

only 5%. Ringing can be controlled by damping the clock

driver and minimizing the line inductance.

Damping the clock driver by placing a resistance in series

with its output is effective, but there is a limit since it also

slows down the rise and fall time of the clock signal. Because

the typical clock driver can be much faster than the worst

case driver, the damping resistor serves the useful function

of limiting the minimum rise and fall time. This is very important because the faster the rise and fall times, the worse the

ringing problem becomes. The size of the damping resistor

varies because it is dependent on the details of the actual

application. It must be determined empirically. In practice a

resistance of 10 to 20 is usually optimum.

Limiting the inductance of the clock lines can be accomplished by minimizing their length and by laying out the lines

such that the return current is closely coupled to the clock

lines. When minimizing the length of clock lines it is important to minimize the distance from the clock driver output to

the furthest point being driven. Because of this, memory

boards are usually designed with clock drivers in the center

of the memory array, rather than on one side, reducing the

maximum distance by a factor of 2.

Using multilayer printed circuit boards with clock lines sandwiched between the VDD and VSS power plains minimizes

the inductance of the clock lines. It also serves the function

of preventing the clocks from coupling noise into input and

output lines. Unfortunately multilayer printed circuit boards

are more expensive than two sided boards. The user must

make the decision as to the necessity of multilayer boards.

Suffice it to say here, that reliable memory boards can be designed using two sided printed circuit boards.

www.national.com

DS005853-19

FIGURE 4. Clock Waveforms (Voltage and Current)

Because of the amount of current that the clock driver must

supply to its capacitive load, the distribution of power to the

clock driver must be considered. Figure 4 gives the idealized

voltage and current waveforms for a clock driver driving a

1000 pF capacitor with 20 ns rise and fall time.

As can be seen the current is significant. This current flows

in the VDD and VSS power lines. Any significant inductance in

the lines will produce large voltage transients on the power

supplies. A bypass capacitor, as close as possible to the

clock driver, is helpful in minimizing this problem. This bypass is most effective when connected between the VSS and

VDD supplies. The size of the bypass capacitor depends on

the amount of capacitance being driven. Using a low inductance capacitor, such as a ceramic or silver mica, is most effective. Another helpful technique is to run the VDD and VSS

lines, to the clock driver, adjacent to each other. This tends to

reduce the lines inductance and therefore the magnitude of

the voltage transients.

While discussing the clock driver, it should be pointed out

that the DS0026 is a relatively low input impedance device.

It is possible to couple current noise into the input without

seeing a significant voltage. Since the noise is difficult to detect with an oscilloscope it is often overlooked.

Lastly, the clock lines must be considered as noise generators. Figure 5 shows a clock coupled through a parasitic coupling capacitor, CC, to eight data input lines being driven by

a 7404. A parasitic lumped line inductance, L, is also shown.

Let us assume, for the sake of argument, that CC is 1 pF and

that the rise time of the clock is high enough to completely

isolate the clock transient from the 7404 because of the inductance, L.

6

tance could cause system malfunction, because a 7404

without a pull up resistor has typically only 0.3V of noise margin in the 1 state at 25C. Of course it is stretching things to

assume that the inductance, L, completely isolates the clock

transient from the 7404. However, it does point out the need

to minimize inductance in input/output as well as clock lines.

(Continued)

The output is current, so it is more meaningful to examine

the current that is coupled through a 1 pF parasitic capacitance. The current would be:

This exceeds the total output current swing so it is obviously

significant.

Clock coupling to inputs and outputs can be minimized by

using multilayer printed circuit boards, as mentioned previously, physically isolating clock lines and/or running clock

lines at right angles to input/output lines. All of these techniques tend to minimize parasitic coupling capacitance from

the clocks to the signals in question.

In considering clock coupling it is also important to have a

detailed knowledge of the functional characteristics of the

device being used. As an example, for the MM5262, coupling noise from the 2 clock to the address lines is of no particular consequence. On the other hand the address inputs

will be sensitive to noise coupled from 1 clock.

DS005853-20

FIGURE 5. Clock Coupling

With a clock transition of 20V the magnitude of the voltage

generated across CL is:

This has been a hypothetical example to emphasize that

with 20V low rise/fall time transitions, parasitic elements can

not be neglected. In this example, 1 pF of parasitic capaci-

www.national.com

DS0026

Application Hints

DS0026 Dual High-Speed MOS Driver

Packaging Information

Physical Dimensions

inches (millimeters) unless otherwise noted

Molded Dual-In-Line Package (N)

Order Number DS0026CN

NS Package Number N08E

LIFE SUPPORT POLICY

NATIONALS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL

COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are devices or

systems which, (a) are intended for surgical implant

into the body, or (b) support or sustain life, and

whose failure to perform when properly used in

accordance with instructions for use provided in the

labeling, can be reasonably expected to result in a

significant injury to the user.

National Semiconductor

Corporation

Americas

Tel: 1-800-272-9959

Fax: 1-800-737-7018

Email: support@nsc.com

www.national.com

National Semiconductor

Europe

Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Franais Tel: +33 (0) 1 41 91 8790

2. A critical component is any component of a life

support device or system whose failure to perform

can be reasonably expected to cause the failure of

the life support device or system, or to affect its

safety or effectiveness.

National Semiconductor

Asia Pacific Customer

Response Group

Tel: 65-2544466

Fax: 65-2504466

Email: ap.support@nsc.com

National Semiconductor

Japan Ltd.

Tel: 81-3-5639-7560

Fax: 81-3-5639-7507

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

S-ar putea să vă placă și

- WT4 Server Side TechnologyDocument18 paginiWT4 Server Side TechnologySagun Raj Basnet75% (4)

- List of PracticalsDocument6 paginiList of Practicalsshankarcr50% (2)

- How To Set Up A Call Centre From Scratch - The Checklist PDFDocument12 paginiHow To Set Up A Call Centre From Scratch - The Checklist PDFOmar BenkiraneÎncă nu există evaluări

- Ds 0026Document10 paginiDs 0026dcastrelos2000Încă nu există evaluări

- Ncl30160 1.0A Constant-Current Buck Regulator For Driving High Power LedsDocument10 paginiNcl30160 1.0A Constant-Current Buck Regulator For Driving High Power LedsKhúc Hành QuânÎncă nu există evaluări

- HV7802 14068Document6 paginiHV7802 14068Djzedamendoa Jose LopesÎncă nu există evaluări

- Data Sheet: IC Timers 555 and 556Document8 paginiData Sheet: IC Timers 555 and 556Adenilson MatiasÎncă nu există evaluări

- Mtw8n60e DDocument9 paginiMtw8n60e DAtiqurrehman UmairÎncă nu există evaluări

- 100 VOLT 30 AMP H-Bridge PWM Motor Driver/Amplifier: M.S.Kennedy CorpDocument7 pagini100 VOLT 30 AMP H-Bridge PWM Motor Driver/Amplifier: M.S.Kennedy CorpDaniel SanchezÎncă nu există evaluări

- LMC555 CMOS Timer: General Description FeaturesDocument10 paginiLMC555 CMOS Timer: General Description FeaturesJeremy ObriotÎncă nu există evaluări

- LM393 DDocument10 paginiLM393 DPardeep KumarÎncă nu există evaluări

- 4 Zener Voltage Regulator Diode Clippers ClampersDocument7 pagini4 Zener Voltage Regulator Diode Clippers ClampersmakreloadedÎncă nu există evaluări

- LMC555 CMOS Timer: General Description FeaturesDocument12 paginiLMC555 CMOS Timer: General Description FeaturesNicolas FontanaÎncă nu există evaluări

- LM393, LM393E, LM293, LM2903, LM2903E, LM2903V, NCV2903 Low Offset Voltage Dual ComparatorsDocument10 paginiLM393, LM393E, LM293, LM2903, LM2903E, LM2903V, NCV2903 Low Offset Voltage Dual Comparatorssam2Încă nu există evaluări

- DS90LV018A 3V LVDS Single CMOS Differential Line Receiver: General Description FeaturesDocument9 paginiDS90LV018A 3V LVDS Single CMOS Differential Line Receiver: General Description FeaturesIan McNairÎncă nu există evaluări

- FT SMDDocument6 paginiFT SMDajitajimalÎncă nu există evaluări

- LM392Document6 paginiLM392Brzata PticaÎncă nu există evaluări

- MTP3055Document9 paginiMTP3055lisandroantonÎncă nu există evaluări

- 004 Pwm-OcxiDocument7 pagini004 Pwm-OcxiNeodymeÎncă nu există evaluări

- Understanding Output Voltage Limitations of DC/DC Buck ConvertersDocument4 paginiUnderstanding Output Voltage Limitations of DC/DC Buck ConvertersLatif KurniaÎncă nu există evaluări

- Measurement of Current With A Voltage DAQDocument3 paginiMeasurement of Current With A Voltage DAQKh SabÎncă nu există evaluări

- UntitledDocument35 paginiUntitledPARVATHI P KARUNÎncă nu există evaluări

- V Series Rectifier 102407 PDFDocument6 paginiV Series Rectifier 102407 PDFchiquilin2Încă nu există evaluări

- Tda 7293Document16 paginiTda 7293Gerson FelipeÎncă nu există evaluări

- MTW14N50EDocument8 paginiMTW14N50EroozbehxoxÎncă nu există evaluări

- 250T Frequency TransmitterDocument13 pagini250T Frequency Transmitterreality88Încă nu există evaluări

- Float DriveDocument24 paginiFloat DriveEdy AchalmaÎncă nu există evaluări

- An-978 HV Floating MOS Gate DriversDocument21 paginiAn-978 HV Floating MOS Gate DriversPeter RueÎncă nu există evaluări

- Designing DC Converters With SI9110Document19 paginiDesigning DC Converters With SI9110Liem NguyenÎncă nu există evaluări

- DiDocument5 paginiDiTao Quang BinhÎncă nu există evaluări

- Tda 7294Document17 paginiTda 7294Abubakar SidikÎncă nu există evaluări

- AND8241/D A 5.0 V/2.0 A Standby Power Supply For INTEL Compliant ATX ApplicationsDocument16 paginiAND8241/D A 5.0 V/2.0 A Standby Power Supply For INTEL Compliant ATX ApplicationsJonatan LunaÎncă nu există evaluări

- And8142 DDocument10 paginiAnd8142 DJonatan LunaÎncă nu există evaluări

- PWM Module Drv101Document20 paginiPWM Module Drv101DTPHawkÎncă nu există evaluări

- VO3120 2.5 A Output Current IGBT and MOSFET Driver: Vishay SemiconductorsDocument10 paginiVO3120 2.5 A Output Current IGBT and MOSFET Driver: Vishay Semiconductorsfadapow4uÎncă nu există evaluări

- DatasheetDocument13 paginiDatasheetebertecnicoÎncă nu există evaluări

- DPM 1As-Bl: Product DescriptionDocument4 paginiDPM 1As-Bl: Product DescriptionFane PelinÎncă nu există evaluări

- 132KV 2 Line Metering PanelDocument11 pagini132KV 2 Line Metering PanelUsman RasheedÎncă nu există evaluări

- LM2852 Synchronous BuckDocument14 paginiLM2852 Synchronous BuckAndrew CavanaughÎncă nu există evaluări

- DCpower SuplyDocument12 paginiDCpower Suplymm30973097Încă nu există evaluări

- Power ConverterDocument26 paginiPower Converterhardih123Încă nu există evaluări

- Dap006 Dap6a DataDocument15 paginiDap006 Dap6a DataluisfeipezzÎncă nu există evaluări

- ZXSC410 420Document12 paginiZXSC410 420Catalin TirtanÎncă nu există evaluări

- 12 Volt Smps Circuit DiagramDocument7 pagini12 Volt Smps Circuit DiagramAnura MaddumageÎncă nu există evaluări

- Data Sheet TC 14433Document20 paginiData Sheet TC 14433Heriberto Flores AmpieÎncă nu există evaluări

- LIT1011 DelconRelaysDocument4 paginiLIT1011 DelconRelaysalltheloveintheworldÎncă nu există evaluări

- N-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical DataDocument8 paginiN-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical Datameroka2000Încă nu există evaluări

- Obsolete Product(s) - Obsolete Product(s) : Control Circuit For Switch Mode Power Supplies Using Mos TransistorsDocument7 paginiObsolete Product(s) - Obsolete Product(s) : Control Circuit For Switch Mode Power Supplies Using Mos Transistorsbookreader1968Încă nu există evaluări

- 1/2/3-Phase Quick-PWM IMVP-6.5 VID Controllers: General Description FeaturesDocument39 pagini1/2/3-Phase Quick-PWM IMVP-6.5 VID Controllers: General Description FeaturesSunil SuwarnkarÎncă nu există evaluări

- Antenna Analyzer vk5jst Version 1 Instructions PDFDocument10 paginiAntenna Analyzer vk5jst Version 1 Instructions PDFPisu Miau Pisu MiauÎncă nu există evaluări

- As34 GDocument9 paginiAs34 GraranmruÎncă nu există evaluări

- Advanced Monolithic Systems: Rohs CompliantDocument8 paginiAdvanced Monolithic Systems: Rohs CompliantWilliam BlackÎncă nu există evaluări

- dt97 3Document6 paginidt97 3ofilipÎncă nu există evaluări

- MC 1496Document12 paginiMC 1496Alejandro GarciaÎncă nu există evaluări

- AMS1117-5.0-Adjustable and Fixed Voltage Regulators de 1 ADocument8 paginiAMS1117-5.0-Adjustable and Fixed Voltage Regulators de 1 AKrista Tran100% (1)

- N-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical DataDocument8 paginiN-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical Datauim0% (1)

- 4200 Pulsed-IV ApplicationsGuideDocument75 pagini4200 Pulsed-IV ApplicationsGuideStefan-Marian IordacheÎncă nu există evaluări

- 2020 16 How To Select Silicon TVS DevicesDocument3 pagini2020 16 How To Select Silicon TVS DevicesSateesh TalisettyÎncă nu există evaluări

- Low Power VLSI Unit 2Document14 paginiLow Power VLSI Unit 2JAI ROYALÎncă nu există evaluări

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2De la EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Încă nu există evaluări

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1De la EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Evaluare: 2.5 din 5 stele2.5/5 (3)

- ENER002-2PI User Guide PDFDocument2 paginiENER002-2PI User Guide PDFlujorebÎncă nu există evaluări

- Ao4801 PDFDocument5 paginiAo4801 PDFlujorebÎncă nu există evaluări

- TCL 32M61 - MS19 Service Manual PDFDocument72 paginiTCL 32M61 - MS19 Service Manual PDFlujorebÎncă nu există evaluări

- 2SK2837 Datasheet en 20090929Document6 pagini2SK2837 Datasheet en 20090929mirelaÎncă nu există evaluări

- Catalogo UJU ConectoresDocument27 paginiCatalogo UJU Conectoreslujoreb100% (1)

- Auo t315xw02 VTDocument30 paginiAuo t315xw02 VTlujorebÎncă nu există evaluări

- Auo t315xw02 VTDocument30 paginiAuo t315xw02 VTlujorebÎncă nu există evaluări

- Power DiodeDocument3 paginiPower DiodeMohd ShahzadÎncă nu există evaluări

- Plasma Symptoms and CuresDocument91 paginiPlasma Symptoms and Curesvideoson100% (4)

- Auo M185XW01-V8 (Los Derechos de Autor Son Los Creadores Del Documento)Document27 paginiAuo M185XW01-V8 (Los Derechos de Autor Son Los Creadores Del Documento)lujorebÎncă nu există evaluări

- Dell Latitude d500 d505 d510 Quanta Dm1 Rev 1a SCHDocument46 paginiDell Latitude d500 d505 d510 Quanta Dm1 Rev 1a SCHZoranÎncă nu există evaluări

- Blackdiamond Bd156aDocument1 paginăBlackdiamond Bd156alujorebÎncă nu există evaluări

- Electrovoice ELX 115Document1 paginăElectrovoice ELX 115lujorebÎncă nu există evaluări

- Plugins Check - in Maintenance Mode-2022!01!17-Jam11.10Document4 paginiPlugins Check - in Maintenance Mode-2022!01!17-Jam11.10peterÎncă nu există evaluări

- Pre Gtu Exam PaperDocument1 paginăPre Gtu Exam PaperAum MangeÎncă nu există evaluări

- AVI Eehal: E-Mail: Mobile: 312.451.8811Document5 paginiAVI Eehal: E-Mail: Mobile: 312.451.8811CHAVAMOHITHBALAJI SchoolÎncă nu există evaluări

- 1-19#-LS-909-SIZE ANALYSIS MACHINE-user Manual PDFDocument101 pagini1-19#-LS-909-SIZE ANALYSIS MACHINE-user Manual PDFscribd birdÎncă nu există evaluări

- VersionDocument4 paginiVersionJuanMolanoÎncă nu există evaluări

- Module 2 ACA NotesDocument31 paginiModule 2 ACA NotesShylaja100% (1)

- Course Overview Guide - Intro To CS MakeCode MicrobitDocument26 paginiCourse Overview Guide - Intro To CS MakeCode MicrobitUmair AbdullahÎncă nu există evaluări

- Average RTWPDocument135 paginiAverage RTWPSoumaya DahechÎncă nu există evaluări

- Build Business Web Applications Phpopenbiz Framework: Cubi PlatformDocument30 paginiBuild Business Web Applications Phpopenbiz Framework: Cubi PlatformEko TriyantoÎncă nu există evaluări

- MSDP-02-Commencing Project and Scope-LV1Document26 paginiMSDP-02-Commencing Project and Scope-LV1Wavda AÎncă nu există evaluări

- Releasenote Turbo HD DVR V4.75.000 Release NotesDocument34 paginiReleasenote Turbo HD DVR V4.75.000 Release NotesyusrilÎncă nu există evaluări

- Quick Guide Vm134-k8076 UkDocument16 paginiQuick Guide Vm134-k8076 UkCapsule CorpÎncă nu există evaluări

- Using Density 12MFDocument3 paginiUsing Density 12MFM Ahmed LatifÎncă nu există evaluări

- Growbyten - Offer LetterDocument2 paginiGrowbyten - Offer LetterHariharan MadeswaranÎncă nu există evaluări

- Week 01 - Introduction To IT Services ManagementDocument41 paginiWeek 01 - Introduction To IT Services ManagementSonam TseringÎncă nu există evaluări

- Quick Start Guide For Colubris/HP Gateways: 2008, Wifi-Soft Solutions All Rights ReservedDocument10 paginiQuick Start Guide For Colubris/HP Gateways: 2008, Wifi-Soft Solutions All Rights ReservedTùng LâmÎncă nu există evaluări

- TC TRK 2p Brochure Eng 210x297mm Rev7 17072021 Lrs Single PagesDocument8 paginiTC TRK 2p Brochure Eng 210x297mm Rev7 17072021 Lrs Single Pagesneophantom00Încă nu există evaluări

- Selection StatementsDocument26 paginiSelection StatementsyaazelÎncă nu există evaluări

- 7000 Um150g en P Jan07Document478 pagini7000 Um150g en P Jan07harlyganÎncă nu există evaluări

- Truptti GaikwadDocument4 paginiTruptti GaikwadAnubhav Singh PratiharÎncă nu există evaluări

- Anchor Bolt FAZ IIDocument4 paginiAnchor Bolt FAZ IImmaleniÎncă nu există evaluări

- Job Description FOR SAPDocument3 paginiJob Description FOR SAPp6tzk7Încă nu există evaluări

- Reward Your CuriosityDocument1 paginăReward Your CuriosityKimjoonsÎncă nu există evaluări

- SPACE GASS Installation GuideDocument9 paginiSPACE GASS Installation GuideozbuildÎncă nu există evaluări

- Mind Mapping: Relasi Dan FungsiDocument33 paginiMind Mapping: Relasi Dan FungsiResy MonitasariÎncă nu există evaluări

- MAC Address and MAC FilteringDocument2 paginiMAC Address and MAC FilteringCleo RubinoÎncă nu există evaluări

- CCCY 225 - ProjectDocument3 paginiCCCY 225 - ProjectTestsashahÎncă nu există evaluări