Documente Academic

Documente Profesional

Documente Cultură

Design of Ultra-Low Leakage Power Sequential Circuits

Încărcat de

Pasumarthy SrikanthTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Design of Ultra-Low Leakage Power Sequential Circuits

Încărcat de

Pasumarthy SrikanthDrepturi de autor:

Formate disponibile

ISSN:2229-6093

P Srikanth et al ,Int.J.Computer Technology & Applications,Vol 3 (3), 1254-1259

Design of Ultra-low Leakage Power Sequential Circuits

P.Srikanth#1, Prof.R.Ramana Reddy#2

Department of ECE, MVGR COLLEGE OF ENGINEERING

Visakhapatnam, A.P., INDIA

1

srikanth3033@gmail.com

2

profrrreddy@yahoo.co.in

Abstract

Reduction in leakage power has become an important frequency scaling, focused on dynamic power

concern in low-voltage, low-power, and high- reduction. However, as the feature size shrinks, e.g.,

performance applications. International Technology to 0.09 and 0.065m, static power has become a great

Roadmap for Semiconductors projects that leakage challenge for current and future technologies.

power consumption may come to dominate total chip

power consumption as the technology feature size There are several VLSI techniques to reduce leakage

shrinks. A novel approach for ultra-low leakage power. Each technique provides an efficient way to

CMOS circuit structure is Sleepy keeper. Sleepy reduce leakage power, but disadvantages of each

keeper uses traditional sleep transistors plus two technique limit the application of each technique. The

additional transistors driven by a gates already proposed new approach, provides a new choice to

calculated output to save state during sleep mode. low-leakage power VLSI designers. Previous

Dual Vth values can be applied to sleepy keeper in techniques are summarized and compared with new

order to dramatically reduce sub-threshold leakage approach are presented in this paper.

current. Unlike many other previous approaches,

sleepy keeper can retain logic state during sleep 2. Methodology

mode while achieving ultra-low leakage power This paper evaluates all considered approaches for

consumption. For applications spending the vast a D- Flip Flop and JK Master-Slave Flip Flop using

majority of time in sleep or standby mode, requires nand gates and inverters as a test case. The base case

low area, high performance and maintenance of for this test circuit is a basic Complementary Metal

exact logic state, the sleepy keeper approach Oxide Semiconductor (CMOS) implementation. In

provides a new weapon. all approaches, transistors are placed in-between two

parallel rows of continuous VDD and GND. For the

1. Introduction base case, a D-Flip Flop is implemented as the shown

Power consumption is one of the top concerns of in Fig (1). Different low power techniques are

VLSI circuit design, for which CMOS is the primary applied on the same circuit and also on JK Master-

technology. In order to achieve high density and high Slave flip flop circuit and the results are compared

performance, CMOS technology feature size and for 0.18m, 0.09m, 0.065m & 0.045m

threshold voltage have been scaling down for technologies.

decades. Because of this technology trend, transistor

leakage power has increased exponentially. However, 3. Previous Work

there is no universal way to avoid tradeoffs between In order to compare with the sleepy keeper

power, delay, and area, and thus, designers are approach, this section explains several previous

required to choose appropriate techniques that satisfy leakage reduction approaches: transistor stacking,

application and product needs. Power consumption of source gating via sleep transistors, selective source

CMOS consists of dynamic and static components. gating via alternating sleep transistors (the so-called

Dynamic power is consumed when transistors are zigzag approach), and a combination of stack and

switching and static power is consumed regardless of sleep approach called sleepy stack. Each technique is

transistor switching. Dynamic power consumption described in detail below and the base case of the

was previously (at 0.18-m technology and above) nand gate is shown in Fig (2).

the single largest concern for low-power chip

designers since dynamic power accounted for 90% or

more of the total chip power. Therefore, many

previously proposed techniques, such as voltage and

IJCTA | MAY-JUNE 2012 1254

Available online@www.ijcta.com

ISSN:2229-6093

P Srikanth et al ,Int.J.Computer Technology & Applications,Vol 3 (3), 1254-1259

output is 0, then a pull-up sleep transistor is applied.

By applying, prior to going to sleep, the particular

input pattern chosen prior to chip fabrication, the

zigzag technique can prevent floating.

Although the zigzag technique retains the

particular state chosen prior to chip fabrication, any

other arbitrary state during regular operation is lost in

power-down mode. The zigzag technique may need

extra circuitry to generate a specific input vector. By

using the zigzag approach, the nand gate schematic is

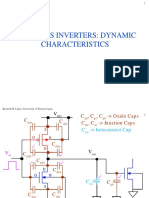

Fig 1.Schematic diagram of D-flip flop (base case) implemented as shown in Fig (4).

.

3.3. Stack Approach

In this every transistor in the base case network

is duplicated with both original and duplicate bearing

half the original transistor width as shown in Fig(5).

Duplicated transistors cause a slight reverse bias

between the gate and source when both transistors are

turned off. Because sub-threshold current is

exponentially dependent on gate bias, a substantial

current reduction is obtained .Since all transistors are

placed in-between two parallel rows of continuous

VDD and GND, stack approach design forces an

increase in row length because of an increase in the

Fig 2. Two-input NAND gate (base case) number of transistors and decrease in transistor width

which increases the delay significantly and could

3.1. Sleep Approach limit the usefulness of the approach.

For the sleep approach, transistors gating VDD

and GND are added to the base case. The added 3.4. Sleepy Stack Approach

transistors cut off supply of power when in sleep The circuit of sleepy stack approach for low

mode. Each added transistor is referred to as a sleep leakage power design is shown Fig (6) below. The

transistor and takes the width of the largest sleepy stack approach has a structure combining the

transistor in the base case. As shown in Fig (3) a stack and sleep approaches by dividing every

PMOS sleep transistor is placed between VDD and transistor into two transistors of half width and

the pull-up network, and an NMOS sleep transistor is placing a sleep transistor in parallel with one of the

placed between GND and the pull-down network. divided transistor. As shown in Fig (6), sleep

The sleep transistors are driven by Sleep (S) and transistors are placed in parallel to the divided

Sleep (S) signals. transistor closest to VDD for pull-up and in parallel

to the divided transistor closest to GND for pull-

The sleep transistors disconnect the circuit from down. The stacked transistors suppress leakage

VDD and GND when the logic circuit is not in use current while saving state. While each sleep transistor

(i.e., when in sleep mode). By cutting off the power placed in parallel to the one of the stacked transistors,

source, this technique can reduce leakage power reduces resistance of the path, so delay is decreased

effectively. However, output will be floating after during active mode. However, area penalty is a

sleep mode, so the technique results in destruction of significant matter for this approach since every

state plus a floating output voltage. transistor is replaced by three transistors.

3.2. Zig-zag Approach

To reduce the wake-up delay of the sleep

transistor technique, the zigzag technique is

introduced. The zigzag technique reduces the wake-

up overhead by choosing a particular circuit state and

then, for the exact circuit state chosen, turning off the

pull-down network for each gate whose output is

high while conversely turning off the pull-up network

for each gate whose output is low. If the output is 1,

then a pull-down sleep transistor is applied; if the

IJCTA | MAY-JUNE 2012 1255

Available online@www.ijcta.com

ISSN:2229-6093

P Srikanth et al ,Int.J.Computer Technology & Applications,Vol 3 (3), 1254-1259

4. Proposed Approach-Sleepy Keeper

The structure of the proposed sleepy keeper

approach is shown in the Fig (7) below. The basic

problem with traditional CMOS is that the transistors

are used only in their most efficient, and naturally

inverting, way: namely, PMOS transistors connect to

VDD and NMOS transistors connect to GND. It is

well known that PMOS transistors are not efficient at

passing GND; similarly, NMOS transistors are not

efficient at passing VDD.

Fig 3. Two-input NAND gate (Sleep)

Fig 4. Two-input NAND gate (Zig-Zag) Fig 7. Sleepy keeper approach

The advantages of this approach are Ultra-low

leakage with dual Vth, State-saving, less area penalty

and faster than sleepy stack approach. Sleepy keeper

approach for the design of the nand gate schematic is

as shown below in Fig (8). For the sleep, zigzag and

sleepy, dual Vth technology can be applied to obtain

greater leakage power reduction. Since high-Vth

results in less leakage but lowers performance, high-

Vth is applied only to leakage reduction transistors,

which are sleep transistors, and any transistors in

parallel to the sleep transistors; on the other hand,

low-Vth is applied to the remaining transistors to

maintain logic performance.

Fig 5. Two-input NAND gate (Stack)

Fig 6. Two-input NAND gate (Sleepy Stack) Fig 8. Sleepy Keeper approach for Nand gate

IJCTA | MAY-JUNE 2012 1256

Available online@www.ijcta.com

ISSN:2229-6093

P Srikanth et al ,Int.J.Computer Technology & Applications,Vol 3 (3), 1254-1259

5. Experimental Results Table 3. Results for D-flip flop (65nm)

In order to compare the results of proposed

approach with prior leakage reduction approaches 65nm De lay(s)

Static Dynamic

Are a(m 2 )

like, stack, sleep, zigzag, sleepy stack and leakage Powe r (W) Powe r (W)

Base Case 8.53E-11 3.53E-08 9.98E-07 1.25E+02

feedback approaches experiments are carried out

Stack 2.14E-10 4.92E-09 8.51E-07 2.93E+02

considering D-Flip Flop as a base case. The nand Sle e p 1.24E-10 1.19E-08 1.12E-06 2.41E+02

gate with sleepy keeper approach along with their Zigz ag 1.07E-10 1.34E-08 1.09E-06 1.89E+02

transistor sizes shown in Figure (8) is used in D-Flip Sle e py Stack 1.53E-10 7.66E-09 8.32E-07 4.61E+02

Flop in Fig (1) and JK Master-Slave flipflop in Sle e py Ke e pe r 1.37E-10 5.24E-09 6.01E-07 3.26E+02

Fig(9). Schematics are designed for all considered Sle e p dVth 2.60E-10 4.70E-11 1.30E-06 2.41E+02

Zigz ag dVth 1.96E-10 1.50E-10 1.31E-06 1.89E+02

techniques using TANNER EDA tool and netlists of

SS dVth 3.62E-10 1.13E-10 8.52E-07 4.61E+02

test circuits for different techniques are extracted SK dVth 3.07E-10 1.21E-10 6.97E-07 3.26E+02

from the schematics. The netlists are modified to fit

into all silicon technologies targeted using the

Table 4. Results for D-flip flop (45nm)

BPTM. HSPICE simulation is used to estimate delay

and power consumption. Experimental results for

Static Dynamic

delay, static power, dynamic power and area for D- 45nm De lay(s)

Powe r (W) Powe r (W)

Are a(m 2 )

Flip Flop are presented in Fig (10-13) and JK Master- Base Case 6.58E-12 1.83E-06 2.39E-06 5.98E+01

Slave flip flop in Fig (14-17). Stack 4.16E-11 2.96E-07 4.69E-07 1.40E+02

Sle e p 1.95E-11 6.07E-07 2.25E-06 1.16E+02

Zigz ag 9.74E-12 7.26E-07 2.35E-06 9.05E+01

Sle e py Stack 1.98E-11 4.42E-07 1.11E-06 2.21E+02

Sle e py Ke e pe r 1.97E-11 2.74E-07 1.09E-06 1.56E+02

Sle e p dVth 2.27E-11 1.59E-08 2.20E-06 1.16E+02

Zigz ag dVth 7.18E-12 3.16E-08 2.36E-06 9.05E+01

SS dVth 3.08E-11 2.12E-08 1.02E-06 2.21E+02

SK dVth 2.72E-11 1.18E-08 1.06E-06 1.56E+02

Fig 9. Schematic diagram of JK Master-Slave

Table 1. Results for D-flip flop (180nm)

Static Dynamic

180nm De lay(s) Are a(m 2 )

Powe r (W) Powe r (W)

Base Case 6.00E-11 8.22E-09 1.72E-05 8.71E+02

Stack 1.57E-10 6.84E-10 1.34E-05 2.04E+03

Sle e p 8.46E-11 1.14E-09 1.84E-05 1.68E+03

Zigz ag 7.25E-11 1.81E-09 1.89E-05 1.32E+03

Sle e py Stack 1.17E-10 1.19E-09 1.37E-05 3.21E+03 Fig 10. Propagation delay of D-flip flop

Sle e py Ke e pe r 1.02E-10 4.37E-10 1.04E-05 2.27E+03

Sle e p dVth 9.85E-11 1.95E-12 1.90E-05 1.68E+03

Zigz ag dVth 7.77E-11 1.65E-12 1.97E-05 1.32E+03

SS dVth 1.33E-10 2.48E-12 1.31E-05 3.21E+03

SK dVth 1.21E-10 4.20E-12 1.08E-05 2.27E+03

Table 2. Results for D-flip flop (90nm)

Static Dynamic

90nm De lay(s) Are a(m 2 )

Powe r (W) Powe r (W)

Base Case 5.71E-11 7.34E-09 1.54E-06 2.39E+02

Stack 1.46E-10 4.23E-10 1.34E-06 5.62E+02

Sle e p 8.20E-11 8.14E-10 1.66E-06 4.62E+02

Zigz ag 7.07E-11 1.38E-09 1.65E-06 3.62E+02 Fig 11. Static power of D-flip flop

Sle e py Stack 1.07E-10 7.46E-10 1.27E-06 8.83E+02

Sle e py Ke e pe r 9.52E-11 3.49E-10 9.54E-07 6.24E+02

Sle e p dVth 1.12E-10 9.80E-13 1.73E-06 4.62E+02

Zigz ag dVth 9.34E-11 9.17E-13 1.75E-06 3.62E+02

SS dVth 1.50E-10 2.17E-12 1.24E-06 8.83E+02

SK dVth 1.32E-10 2.03E-12 1.01E-06 6.24E+02

IJCTA | MAY-JUNE 2012 1257

Available online@www.ijcta.com

ISSN:2229-6093

P Srikanth et al ,Int.J.Computer Technology & Applications,Vol 3 (3), 1254-1259

Table 7. Results for JK Master-Slave (65nm)

Static Dynamic

65nm De lay(s) Are a(m 2 )

Powe r (W) Powe r (W)

Base Case 1.76E-10 9.55E-07 2.67E-06 3.42E+02

Stack 5.53E-10 4.11E-07 2.33E-06 7.49E+02

Sle e p 3.24E-10 2.43E-08 4.30E-06 5.70E+02

Zigz ag 2.72E-10 3.06E-08 2.59E-06 5.04E+02

Sle e py Stack 3.80E-10 1.43E-08 2.58E-06 1.28E+03

Sle e py Ke e pe r 3.29E-10 1.14E-08 1.52E-06 8.11E+02

Sle e p dVth 8.55E-10 9.00E-11 2.85E-06 5.70E+02

Zigz ag dVth 7.17E-10 2.74E-10 3.01E-06 5.04E+02

SS dVth 1.04E-09 3.00E-10 2.06E-06 1.28E+03

Fig 12. Dynamic power of D-flip flop SK dVth 8.42E-10 6.41E-11 1.85E-06 8.11E+02

Table 8. Results for JK Master-Slave (45nm)

Static Dynamic

45nm De lay(s) Are a(m 2 )

Powe r (W) Powe r (W)

Base Case 1.95E-11 2.32E-05 4.14E-06 1.64E+02

Stack 6.87E-11 3.07E-06 9.20E-07 3.59E+02

Sle e p 3.73E-11 1.37E-06 4.03E-06 2.73E+02

Zigz ag 3.35E-11 1.57E-06 4.11E-06 2.41E+02

Sle e py Stack 4.23E-11 8.73E-06 2.92E-06 6.12E+02

Sle e py Ke e pe r 3.73E-11 5.95E-07 3.12E-06 3.89E+02

Sle e p dVth 4.92E-11 3.12E-08 3.95E-06 2.73E+02

Zigz ag dVth 3.91E-11 8.07E-08 4.05E-06 2.41E+02

SS dVth 5.54E-11 1.45E-06 2.56E-06 6.12E+02

Fig 13. Area of D-flip flop SK dVth 5.21E-11 1.88E-08 1.90E-06 3.89E+02

Table 5. Results for JK Master-Slave (180nm)

Static Dynamic

180nm De lay(s) Are a(m 2 )

Powe r (W) Powe r (W)

Base Case 1.19E-10 2.05E-04 1.00E-04 2.39E+03

Stack 3.89E-10 1.10E-09 3.51E-05 5.22E+03

Sle e p 2.06E-10 1.97E-09 3.64E-05 3.97E+03

Zigz ag 1.84E-10 3.51E-09 4.00E-05 3.51E+03

Sle e py Stack 2.97E-10 1.84E-09 3.30E-05 8.90E+03

Sle e py Ke e pe r 2.27E-10 9.02E-10 2.39E-05 5.65E+03

Sle e p dVth 2.73E-10 3.87E-12 4.49E-05 3.97E+03

Zigz ag dVth 2.27E-10 6.87E-12 3.66E-05 3.51E+03

SS dVth 3.38E-10 8.70E-12 3.16E-05 8.90E+03

SK dVth 2.83E-10 4.03E-12 2.44E-05 5.65E+03

Fig 14. Propagation delay of JK Master-Slave

Table 6. Results for JK Master-Slave (90nm)

Static Dynamic

90nm De lay(s) Are a(m 2 )

Powe r (W) Powe r (W)

Base Case 1.18E-10 8.83E-06 3.30E-06 6.57E+02

Stack 3.68E-10 7.58E-10 3.67E-06 1.44E+03

Sle e p 2.08E-10 1.70E-09 4.32E-06 1.09E+03

Zigz ag 1.76E-10 3.18E-09 4.28E-06 9.66E+02

Sle e py Stack 2.74E-10 1.32E-09 3.65E-06 2.45E+03

Sle e py Ke e pe r 2.18E-10 8.76E-10 2.41E-06 1.55E+03

Sle e p dVth 3.34E-10 1.91E-12 4.13E-06 1.09E+03

Zigz ag dVth 2.85E-10 2.00E-12 4.08E-06 9.66E+02

SS dVth 3.87E-10 5.16E-12 3.17E-06 2.45E+03

SK dVth 3.47E-10 1.09E-12 2.48E-06 1.55E+03

Fig 15. Static power of JK Master-Slave

IJCTA | MAY-JUNE 2012 1258

Available online@www.ijcta.com

ISSN:2229-6093

P Srikanth et al ,Int.J.Computer Technology & Applications,Vol 3 (3), 1254-1259

7. References

[1] Se Hun Kim, Vincent J. Mooney III Sleepy Keeper: a

New Approach to Low-leakage Power VLSI Design, VLSI,

2006 IFIP international conference.

[2] J.C. Park, V. J. Mooney III and P. Pfeiffenberger,

Sleepy Stack Reduction of Leakage Power, Proceeding

of the International Workshop on Power and Timing

Modeling, Optimization and Simulation, pp.148-158,

September 2004. N. Azizi, A. Moshovos, F. N. Najm.

[3] S.Nadara, S. Borkar, V. De, D. Antoniadis and A.

Chandrakasan, Scaling of Stack Effect and its Application

for Leakage Reduction, International Symposium on Low

Fig 16. Dynamic power of JK Master-Slave Power Electronics and Design, pp. 195-200, August 2001.

[4] K.S. Min, H. Kawaguchi and T. Sakurai, Zigzag Super

Cut-off CMOS (ZSCCMOS) Block Activation with Self-

Adaptive Voltage Level Controller: An Alternative to

Clock-gating Scheme in Leakage Dominant Era, IEEE

International Solid-State Circuits Conference, pp. 400-401,

February 2003.

[5] Berkeley Predictive Technology Model (BPTM),

http://www.eas.asu.edu/~ptm/.

[6] International Technology Roadmap for Semiconductors

by Semiconductor Industry Association,

http://public.itrs.net

[7] Z. Chen, M. Johnson, L. Wei and K. Roy, Estimation

of Standby Leakage Power in CMOS Circuits Considering

Fig 17. Static power of JK Master-Slave Accurate Modeling of Transistor Stacks, International

Symposium on Low Power Electronics and Design, pp.

6. Conclusions 239-244, August 1998.

Scaling down of the CMOS technology feature [8] N. S. Kim et al., Leakage Current: Moores Law

size and threshold voltage for achieving high Meets Static Power, IEEE Computer, Vol. 36, Issue 12,

performance has resulted in increase of leakage pp. 68-75, December 2003.

power dissipation. This paper presents an efficient

[9] A. P. Chandrakasan, S. Sheng, and R. W. Brodersen,

methodology for reducing leakage power in VLSI Low-power CMOS digital design, IEEE J. Solid-State

design. The sleepy keeper technique results in ultra Circuits, vol. 27, p. 473, Apr. 1992.

low static power consumption with state saving.

Furthermore, the sleepy keeper approach is

applicable to single and multiple threshold voltages.

With application of dual Vth, sleepy keeper is the

most efficient approach to reduce leakage current

with the smallest delay and area increases while

simultaneously preserving precise logic state in sleep

mode. In terms of area, the sleepy keeper approach is

expected to be more attractive for complex logic

circuits, because the portion of increased area for the

required additional transistors will be smaller for

complex logic circuits than for simple logic circuits

(e.g., for an inverter). For the future work, the plan to

investigate why the sleepy keeper approach increases

dynamic power consumption over the sleepy stack

approach, aiming to reduce this increase in dynamic

power consumption.

IJCTA | MAY-JUNE 2012 1259

Available online@www.ijcta.com

S-ar putea să vă placă și

- DeleeppaperDocument7 paginiDeleeppaperDEEPAK PRAJAPATIÎncă nu există evaluări

- Efficient Design of 1Document7 paginiEfficient Design of 1sumathiÎncă nu există evaluări

- Different Sleep MethodsDocument6 paginiDifferent Sleep MethodsSanthoshReddyÎncă nu există evaluări

- Literature Survey of Low Power Strategies andDocument4 paginiLiterature Survey of Low Power Strategies andFarah MohmadÎncă nu există evaluări

- 05682957Document4 pagini05682957Praveenkumar ViswanathanÎncă nu există evaluări

- Design of Modified Low Power CMOS Differential Ring Oscillator Using Sleepy Transistor ConceptDocument19 paginiDesign of Modified Low Power CMOS Differential Ring Oscillator Using Sleepy Transistor ConceptPrajwal GowdaÎncă nu există evaluări

- Ijesrt: Leakage Current Reduction Techniques For CMOS CircuitsDocument4 paginiIjesrt: Leakage Current Reduction Techniques For CMOS CircuitsShailendra YadavÎncă nu există evaluări

- IJEAS0203039Document6 paginiIJEAS0203039erpublicationÎncă nu există evaluări

- Low Leakage Power-Lector-Mux, Gates PDFDocument6 paginiLow Leakage Power-Lector-Mux, Gates PDFAkÎncă nu există evaluări

- IJEAS0201005Document4 paginiIJEAS0201005erpublicationÎncă nu există evaluări

- Design & Analysis of Different Types of Sleepy Methods For Future TechnologiesDocument6 paginiDesign & Analysis of Different Types of Sleepy Methods For Future TechnologiesseventhsensegroupÎncă nu există evaluări

- Low-Power VLSI Design Using Dynamic-Threshold LogicDocument6 paginiLow-Power VLSI Design Using Dynamic-Threshold LogicravindarsinghÎncă nu există evaluări

- Ijaerv12n2 02Document6 paginiIjaerv12n2 02Hardik MakwanaÎncă nu există evaluări

- Efecto PielDocument9 paginiEfecto PielMilena AlarconÎncă nu există evaluări

- Power Optimization For Low Power VLSI CircuitsDocument4 paginiPower Optimization For Low Power VLSI CircuitsCHARANÎncă nu există evaluări

- Design and Analysis of Multi-Threshold Cmos Full Adder Using 90nmDocument8 paginiDesign and Analysis of Multi-Threshold Cmos Full Adder Using 90nmSaravanakumar KalaimaniÎncă nu există evaluări

- FORTRAN Based ApproachDocument22 paginiFORTRAN Based ApproachGS EKTAÎncă nu există evaluări

- Pousia 2021 IOP Conf. Ser. Mater. Sci. Eng. 1084 012058 PDFDocument9 paginiPousia 2021 IOP Conf. Ser. Mater. Sci. Eng. 1084 012058 PDFneelima422Încă nu există evaluări

- Low Power SramDocument5 paginiLow Power SramPromit MandalÎncă nu există evaluări

- A High Performance Dynamic Logic With nMOS Based Resistive Keeper CircuitDocument5 paginiA High Performance Dynamic Logic With nMOS Based Resistive Keeper CircuitET181018 Md Maharaj KabirÎncă nu există evaluări

- Static Power Reduction Techniques For Asynchronous Circuits: Carlos Ortega, Jonathan Tse, and Rajit ManoharDocument10 paginiStatic Power Reduction Techniques For Asynchronous Circuits: Carlos Ortega, Jonathan Tse, and Rajit ManoharK HoneeyÎncă nu există evaluări

- Design and Analysis of Different Circuits Using DCVSL & Static CMOS TechniqueDocument7 paginiDesign and Analysis of Different Circuits Using DCVSL & Static CMOS TechniqueGRD JournalsÎncă nu există evaluări

- A Continuous-Time Delta-Sigma Modulator Using ELD-Compensation-Embedded SAB and DWA-Inherent Time-Domain QuantizerDocument11 paginiA Continuous-Time Delta-Sigma Modulator Using ELD-Compensation-Embedded SAB and DWA-Inherent Time-Domain QuantizerHamdy HamadaÎncă nu există evaluări

- Leakage Current Reduction 6TDocument3 paginiLeakage Current Reduction 6Tshoaib nadeemÎncă nu există evaluări

- Lasc As 2010Document4 paginiLasc As 2010Rahul ShandilyaÎncă nu există evaluări

- DTMOS-Based 0.4V Ultra Low-Voltage Low-Power VDTA Design and Its Application To EEG Data ProcessingDocument9 paginiDTMOS-Based 0.4V Ultra Low-Voltage Low-Power VDTA Design and Its Application To EEG Data ProcessingBüşra AkyıldızÎncă nu există evaluări

- Low-Power Circuits Using Dynamic Threshold DevicesDocument5 paginiLow-Power Circuits Using Dynamic Threshold DevicesGiang Nguyễn VănÎncă nu există evaluări

- A Literature Review On Leakage and Power Reduction Techniques in CMOS VLSI DesignDocument5 paginiA Literature Review On Leakage and Power Reduction Techniques in CMOS VLSI DesignEditor IJRITCC0% (1)

- SurajpaperDocument79 paginiSurajpaperSooraj SattirajuÎncă nu există evaluări

- 2014 - Design and Synthesis of Ultralow Energy Spin-Memristor Threshold LogicDocument10 pagini2014 - Design and Synthesis of Ultralow Energy Spin-Memristor Threshold Logicfromthedepth@gmail.comÎncă nu există evaluări

- A Survey On Leakage Power Reduction Techniques by Using Power Gating MethodologyDocument6 paginiA Survey On Leakage Power Reduction Techniques by Using Power Gating MethodologySasi Kiran SÎncă nu există evaluări

- Ieib D 22 00311Document9 paginiIeib D 22 00311saurabhguptasgsits123Încă nu există evaluări

- Low Power Design Techniques and Implementation Strategies Adopted in VLSI CircuitsDocument4 paginiLow Power Design Techniques and Implementation Strategies Adopted in VLSI CircuitsCHARANÎncă nu există evaluări

- Analysis and Design of RF CMOS aTTENUATORSDocument15 paginiAnalysis and Design of RF CMOS aTTENUATORSDejanÎncă nu există evaluări

- Analysis of Subthreshold Leakage Reduction in CMOS CircuitsDocument8 paginiAnalysis of Subthreshold Leakage Reduction in CMOS Circuitsetherealgmail.comÎncă nu există evaluări

- Selected PDFDocument6 paginiSelected PDFMadhu SudhanÎncă nu există evaluări

- Design and Implementation of Full Adder Using Different XOR GatesDocument5 paginiDesign and Implementation of Full Adder Using Different XOR GatesEvans MuokiÎncă nu există evaluări

- Low-Voltage High-Speed CML D-Latches in Nanometer CMOS TechnologiesDocument12 paginiLow-Voltage High-Speed CML D-Latches in Nanometer CMOS TechnologiesHemanthÎncă nu există evaluări

- Dual-Threshold Voltage Techniques For Low-Power Digital CircuitsDocument10 paginiDual-Threshold Voltage Techniques For Low-Power Digital CircuitsSeizalal SingsonÎncă nu există evaluări

- Cmos Low PowerDocument5 paginiCmos Low PowerbhoomikachawlaÎncă nu există evaluări

- Chapter 1Document10 paginiChapter 1Sanjay ChÎncă nu există evaluări

- A 32-Bit ALU With Sleep Mode For Leakage Power Reduction: AbstractDocument7 paginiA 32-Bit ALU With Sleep Mode For Leakage Power Reduction: Abstractig77Încă nu există evaluări

- Low Voltage Low Power Pipelined ADC For Video Applications: Hameed Zohaib Samad, Patri Sriharirao, K. SarangamDocument5 paginiLow Voltage Low Power Pipelined ADC For Video Applications: Hameed Zohaib Samad, Patri Sriharirao, K. SarangamGayathri SrinivasaÎncă nu există evaluări

- Isolation Retention DefinitionDocument10 paginiIsolation Retention DefinitionSuma P RÎncă nu există evaluări

- Gated VDD PDFDocument5 paginiGated VDD PDFkruthikah apÎncă nu există evaluări

- INTEGRATION, The VLSI Journal: Keivan Navi, Mehrdad Maeen, Vahid Foroutan, Somayeh Timarchi, Omid KaveheiDocument11 paginiINTEGRATION, The VLSI Journal: Keivan Navi, Mehrdad Maeen, Vahid Foroutan, Somayeh Timarchi, Omid KaveheiDeepak RajeshÎncă nu există evaluări

- A Dynamic Voltage Restorer (DVR) Based Interface Scheme For MicrogridsDocument7 paginiA Dynamic Voltage Restorer (DVR) Based Interface Scheme For MicrogridsrajapandiyaÎncă nu există evaluări

- AnnepuBaburao TSrinivasaRao 62Document5 paginiAnnepuBaburao TSrinivasaRao 62Ahmed HussainÎncă nu există evaluări

- De1999 LPVLSI PaperDocument6 paginiDe1999 LPVLSI PaperKavyashreeMÎncă nu există evaluări

- k1 FCL DigSilentDocument8 paginik1 FCL DigSilentksg9731Încă nu există evaluări

- IJETR032239Document5 paginiIJETR032239erpublicationÎncă nu există evaluări

- An Innovative Ultra Low Voltage Sub-32nm SRAM Voltage Sense Amplifier in DG-SOI TechnologyDocument4 paginiAn Innovative Ultra Low Voltage Sub-32nm SRAM Voltage Sense Amplifier in DG-SOI Technologyapi-19668941Încă nu există evaluări

- A CMOS Based Low Power Digitally Controlled OscillDocument12 paginiA CMOS Based Low Power Digitally Controlled OscillDEEPAK PRAJAPATIÎncă nu există evaluări

- Analysis and Reduction of Power Using Gating Techniques Near Subthreshold RegionDocument7 paginiAnalysis and Reduction of Power Using Gating Techniques Near Subthreshold RegionIOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalÎncă nu există evaluări

- Low Voltage Analog Circuit Design Techniques: IEEE Circuits and Systems Magazine September 2002Document20 paginiLow Voltage Analog Circuit Design Techniques: IEEE Circuits and Systems Magazine September 2002sidhjajÎncă nu există evaluări

- Solid-State Circuit Breakers and Current Limiters For Medium-Voltage Systems Having Distributed Power SystemsDocument8 paginiSolid-State Circuit Breakers and Current Limiters For Medium-Voltage Systems Having Distributed Power Systemsrazila rasheedÎncă nu există evaluări

- Designing of Low Power Full Adder by Submicron Ultra Deep TechnologyDocument4 paginiDesigning of Low Power Full Adder by Submicron Ultra Deep TechnologyInternational Journal of Innovative Science and Research TechnologyÎncă nu există evaluări

- Survey On Power Optimization Techniques For Low Power Vlsi Circuit in Deep Submicron TechnologyDocument15 paginiSurvey On Power Optimization Techniques For Low Power Vlsi Circuit in Deep Submicron TechnologyAnonymous e4UpOQEPÎncă nu există evaluări

- Aka She 2011Document4 paginiAka She 2011SubbuNaiduÎncă nu există evaluări

- Chapter 7 Mosfets in Ics - Scaling, Leakage, and Other TopicsDocument43 paginiChapter 7 Mosfets in Ics - Scaling, Leakage, and Other Topicsmorcov19Încă nu există evaluări

- Silicon NPN Transistor Color TV Horizontal Deflection Output /damper DiodeDocument2 paginiSilicon NPN Transistor Color TV Horizontal Deflection Output /damper DiodeEdgar Rodriguez100% (3)

- Depletion Type MOSFET BiasingDocument3 paginiDepletion Type MOSFET BiasingML010 LakshmiÎncă nu există evaluări

- Ee 560 Mos Inverters: Dynamic CharacteristicsDocument41 paginiEe 560 Mos Inverters: Dynamic CharacteristicssallyÎncă nu există evaluări

- Fabrication Mod 2Document16 paginiFabrication Mod 2albin shajanÎncă nu există evaluări

- EC4068D-Analog MOS Integrated Circuits Dhanaraj K. J. Associate Professor ECED, NIT CalicutDocument12 paginiEC4068D-Analog MOS Integrated Circuits Dhanaraj K. J. Associate Professor ECED, NIT CalicutM KIRITI SAI KUMARÎncă nu există evaluări

- 13-Chapter 13 - TransistorsDocument28 pagini13-Chapter 13 - Transistorssrinu247100% (3)

- Photocouplers and Photorelays: Selection Guide 2019Document48 paginiPhotocouplers and Photorelays: Selection Guide 2019jimmy146Încă nu există evaluări

- RD06HVF1 MitsubishiElectricSemiconductorDocument8 paginiRD06HVF1 MitsubishiElectricSemiconductorandreasmonÎncă nu există evaluări

- Eeng 590j Ch01 - SzeDocument16 paginiEeng 590j Ch01 - SzeAswad ShakurÎncă nu există evaluări

- Vlsidesign MCQDocument18 paginiVlsidesign MCQAkanksha DixitÎncă nu există evaluări

- LGBTDocument2 paginiLGBTgdgdgdgÎncă nu există evaluări

- P 6010 DTFGDocument5 paginiP 6010 DTFGJohnsan DrummerÎncă nu există evaluări

- 2 N 3054Document4 pagini2 N 3054yogendra.shethÎncă nu există evaluări

- Assignment # 2 Introduction To Computer Bscs-1A: Name: Roll No.: Instructor: Q.1)Document3 paginiAssignment # 2 Introduction To Computer Bscs-1A: Name: Roll No.: Instructor: Q.1)Obaidullah MansoorÎncă nu există evaluări

- FDDSFDocument8 paginiFDDSFLUis PEpeÎncă nu există evaluări

- Description of TTL, ECL and CMOS Glue Logic FamiliesDocument2 paginiDescription of TTL, ECL and CMOS Glue Logic Familiesapi-26100966Încă nu există evaluări

- Module II Shrink Down ApproachesDocument20 paginiModule II Shrink Down ApproachesArighna BasakÎncă nu există evaluări

- 2 Sa 1020Document3 pagini2 Sa 1020Luiz Clemente PimentaÎncă nu există evaluări

- NMOS - Inverter - PDF Version 1Document50 paginiNMOS - Inverter - PDF Version 1Al AminÎncă nu există evaluări

- 2 SK 3569Document2 pagini2 SK 3569Bruno GustavoÎncă nu există evaluări

- Principles of Semiconductor Devices-Lecture36Document23 paginiPrinciples of Semiconductor Devices-Lecture36LIAKMANÎncă nu există evaluări

- IgbtDocument11 paginiIgbtRajeev VaranwalÎncă nu există evaluări

- UntitledDocument25 paginiUntitledAconatic tvhomeÎncă nu există evaluări

- Software - Experiment 5. Frequency Response of Common Source Ac Amplifier PDFDocument5 paginiSoftware - Experiment 5. Frequency Response of Common Source Ac Amplifier PDFSatadru DasÎncă nu există evaluări

- Part 2 - Module 4 - ED - Fundamentals of BJT OperationDocument45 paginiPart 2 - Module 4 - ED - Fundamentals of BJT OperationKRISHNENDU CHAKRABARTYÎncă nu există evaluări

- Catalogo 2010Document190 paginiCatalogo 2010kolke16Încă nu există evaluări

- Determination of Pull Up RatioDocument1 paginăDetermination of Pull Up Ratiomayamohan72520% (5)

- Unisonic Technologies Co., LTD: Power Amplifier Applications Power Switching ApplicationsDocument4 paginiUnisonic Technologies Co., LTD: Power Amplifier Applications Power Switching ApplicationsNewsr PrintÎncă nu există evaluări

- Sample Question 3Document11 paginiSample Question 3lavishÎncă nu există evaluări

- Programming the Raspberry Pi, Third Edition: Getting Started with PythonDe la EverandProgramming the Raspberry Pi, Third Edition: Getting Started with PythonEvaluare: 5 din 5 stele5/5 (2)

- Multiplexed Networks for Embedded Systems: CAN, LIN, FlexRay, Safe-by-Wire...De la EverandMultiplexed Networks for Embedded Systems: CAN, LIN, FlexRay, Safe-by-Wire...Încă nu există evaluări

- The Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionDe la EverandThe Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionEvaluare: 4.5 din 5 stele4.5/5 (543)

- Electrical Engineering 101: Everything You Should Have Learned in School...but Probably Didn'tDe la EverandElectrical Engineering 101: Everything You Should Have Learned in School...but Probably Didn'tEvaluare: 4.5 din 5 stele4.5/5 (27)

- Digital Filmmaking: The Ultimate Guide to Web Video Production for Beginners and Non-Professionals, Learn Useful Tips and Advice on How You Can Create, Film and Edit Your VideosDe la EverandDigital Filmmaking: The Ultimate Guide to Web Video Production for Beginners and Non-Professionals, Learn Useful Tips and Advice on How You Can Create, Film and Edit Your VideosEvaluare: 5 din 5 stele5/5 (1)

- Retro Gaming with Raspberry Pi: Nearly 200 Pages of Video Game ProjectsDe la EverandRetro Gaming with Raspberry Pi: Nearly 200 Pages of Video Game ProjectsÎncă nu există evaluări

- Power System Control and ProtectionDe la EverandPower System Control and ProtectionB. Don RussellEvaluare: 4 din 5 stele4/5 (11)

- 2022 Adobe® Premiere Pro Guide For Filmmakers and YouTubersDe la Everand2022 Adobe® Premiere Pro Guide For Filmmakers and YouTubersEvaluare: 5 din 5 stele5/5 (1)

- The Journeyman Electrician Exam Study Guide: Proven Methods for Successfully Passing the Journeyman Electrician Exam with ConfidenceDe la EverandThe Journeyman Electrician Exam Study Guide: Proven Methods for Successfully Passing the Journeyman Electrician Exam with ConfidenceÎncă nu există evaluări

- Conquering the Electron: The Geniuses, Visionaries, Egomaniacs, and Scoundrels Who Built Our Electronic AgeDe la EverandConquering the Electron: The Geniuses, Visionaries, Egomaniacs, and Scoundrels Who Built Our Electronic AgeEvaluare: 4.5 din 5 stele4.5/5 (10)

- The Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionDe la EverandThe Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionEvaluare: 4 din 5 stele4/5 (331)

- INCOSE Systems Engineering Handbook: A Guide for System Life Cycle Processes and ActivitiesDe la EverandINCOSE Systems Engineering Handbook: A Guide for System Life Cycle Processes and ActivitiesEvaluare: 5 din 5 stele5/5 (1)

- Guide to the IET Wiring Regulations: IET Wiring Regulations (BS 7671:2008 incorporating Amendment No 1:2011)De la EverandGuide to the IET Wiring Regulations: IET Wiring Regulations (BS 7671:2008 incorporating Amendment No 1:2011)Evaluare: 4 din 5 stele4/5 (2)

- Hacking Electronics: An Illustrated DIY Guide for Makers and HobbyistsDe la EverandHacking Electronics: An Illustrated DIY Guide for Makers and HobbyistsEvaluare: 3.5 din 5 stele3.5/5 (2)

- Teach Yourself Electricity and Electronics, 6th EditionDe la EverandTeach Yourself Electricity and Electronics, 6th EditionEvaluare: 3.5 din 5 stele3.5/5 (15)

- Build Your Own Electronics WorkshopDe la EverandBuild Your Own Electronics WorkshopEvaluare: 3.5 din 5 stele3.5/5 (3)

- Empires of Light: Edison, Tesla, Westinghouse, and the Race to Electrify the WorldDe la EverandEmpires of Light: Edison, Tesla, Westinghouse, and the Race to Electrify the WorldEvaluare: 4 din 5 stele4/5 (87)

- C++ Programming Language: Simple, Short, and Straightforward Way of Learning C++ ProgrammingDe la EverandC++ Programming Language: Simple, Short, and Straightforward Way of Learning C++ ProgrammingEvaluare: 4 din 5 stele4/5 (1)