Documente Academic

Documente Profesional

Documente Cultură

93c46 Serial Eeprom

Încărcat de

nudufoqiDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

93c46 Serial Eeprom

Încărcat de

nudufoqiDrepturi de autor:

Formate disponibile

GEN FR

ALO

EE

CAT93C46/56/57/66/86

H

1K/2K/2K/4K/16K-Bit Microwire Serial EEPROM

LE

A D F R E ETM

FEATURES

High speed operation: Power-up inadvertant write protection

93C46/56/57/66: 1MHz 1,000,000 Program/erase cycles

93C86: 3MHz 100 year data retention

Low power CMOS technology Commercial, industrial and automotive

1.8 to 6.0 volt operation temperature ranges

Selectable x8 or x16 memory organization Sequential read (except CAT93C46)

Self-timed write cycle with auto-clear Program enable (PE) pin (CAT93C86 only)

Hardware and software write protection Green package option available

DESCRIPTION

The CAT93C46/56/57/66/86 are 1K/2K/2K/4K/16K-bit CMOS EEPROM floating gate technology. The devices

Serial EEPROM memory devices which are configured are designed to endure 1,000,000 program/erase cycles

as either registers of 16 bits (ORG pin at VCC) or 8 bits and have a data retention of 100 years. The devices are

(ORG pin at GND). Each register can be written (or read) available in 8-pin DIP, 8-pin SOIC, 8-pin TSSOP and 8-

serially by using the DI (or DO) pin. The CAT93C46/56/ pad TDFN packages.

57/66/86 are manufactured using Catalysts advanced

PIN CONFIGURATION

DIP Package (P, L) SOIC Package (J,W) SOIC Package (S,V) SOIC Package (K,X) TSSOP Package (U,Y)

CS 1 8 VCC 1 8 ORG CS 1 8 VCC CS 1 8 VCC CS 1 8 VCC

NC (PE*)

SK 2 7 NC (PE*) VCC 2 7 GND SK 2 7 NC (PE*) SK 2 7 NC (PE*) SK 2 7 NC

DI 3 6 ORG CS 3 6 DO DI 3 6 ORG DI 3 6 ORG DI 3 6 ORG

DO 4 5 GND SK 4 5 DI DO 4 5 GND DO 4 5 GND DO 4 5 GND

*Only For 93C86 ** TSSOP (U/Y) package only available for 93C46/56/57/66 TDFN Package (RD4, ZD4)

PIN FUNCTIONS BLOCK DIAGRAM VCC 8 1 CS

Pin Name Function VCC GND NC 7 CAT93C46 2 SK

CAT93C56

CS Chip Select ORG 6 3 DI

CAT93C66

GND 5 4 DO

SK Clock Input

DI Serial Data Input MEMORY ARRAY ADDRESS

ORG

ORGANIZATION DECODER Bottom View

DO Serial Data Output

VCC +1.8 to 6.0V Power Supply

GND Ground

DATA

ORG Memory Organization REGISTER

DI OUTPUT

NC No Connection BUFFER

MODE DECODE

PE* Program Enable CS LOGIC

PE*

Note: When the ORG pin is connected to VCC,

the x16 organization is selected. When it is CLOCK DO

connected to ground, the x8 pin is selected. If SK GENERATOR

the ORG pin is left unconnected, then an internal

pullup device will select the x16 organization.

2003 by Catalyst Semiconductor, Inc.

Doc. No. 1023, Rev. J

Characteristics subject to change without notice.

93C46/56/57/66/86

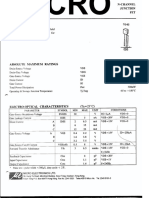

ABSOLUTE MAXIMUM RATINGS* *COMMENT

Temperature Under Bias .................. -55C to +125C Stresses above those listed under Absolute Maximum

Storage Temperature ........................ -65C to +150C Ratings may cause permanent damage to the device.

Voltage on any Pin with These are stress ratings only, and functional operation of

Respect to Ground(1) ............. -2.0V to +VCC +2.0V the device at these or any other conditions outside of those

VCC with Respect to Ground ................ -2.0V to +7.0V listed in the operational sections of this specification is not

implied. Exposure to any absolute maximum rating for

Package Power Dissipation extended periods may affect device performance and

Capability (TA = 25C) ................................... 1.0W

reliability.

Lead Soldering Temperature (10 secs) ............ 300C

Output Short Circuit Current(2) ........................ 100 mA

RELIABILITY CHARACTERISTICS

Symbol Parameter Reference Test Method Min Typ Max Units

NEND(3) Endurance MIL-STD-883, Test Method 1033 1,000,000 Cycles/Byte

TDR(3) Data Retention MIL-STD-883, Test Method 1008 100 Years

VZAP(3) ESD Susceptibility MIL-STD-883, Test Method 3015 2000 Volts

ILTH (3)(4) Latch-Up JEDEC Standard 17 100 mA

D.C. OPERATING CHARACTERISTICS

VCC = +1.8V to +6.0V, unless otherwise specified.

Symbol Parameter Test Conditions Min Typ Max Units

ICC1 Power Supply Current fSK = 1MHz 3 mA

(Operating Write) VCC = 5.0V

ICC2 Power Supply Current fSK = 1MHz 500 A

(Operating Read) VCC = 5.0V

ISB1 Power Supply Current CS = 0V 10 A

(Standby) (x8 Mode) ORG=GND

ISB2(5) Power Supply Current CS=0V 0 A

(Standby) (x16Mode) ORG=Float or VCC

ILI Input Leakage Current VIN = 0V to VCC 1 A

ILO Output Leakage Current VOUT = 0V to VCC, 1 A

(Including ORG pin) CS = 0V

VIL1 Input Low Voltage 4.5V VCC < 5.5V -0.1 0.8 V

VIH1 Input High Voltage 4.5V VCC < 5.5V 2 VCC + 1 V

VIL2 Input Low Voltage 1.8V VCC < 4.5V 0 VCC x 0.2 V

VIH2 Input High Voltage 4.8V VCC < 4.5V VCC x 0.7 VCC+1 V

VOL1 Output Low Voltage 4.5V VCC < 5.5V 0.4 V

IOL = 2.1mA

VOH1 Output High Voltage 4.5V VCC < 5.5V 2.4 V

IOH = -400A

VOL2 Output Low Voltage 1.8V VCC < 4.5V 0.2 V

IOL = 1mA

VOH2 Output High Voltage 1.8V VCC < 4.5V VCC - 0.2 V

IOH = -100A

Note:

(1) The minimum DC input voltage is 0.5V. During transitions, inputs may undershoot to 2.0V for periods of less than 20 ns. Maximum DC

voltage on output pins is VCC +0.5V, which may overshoot to VCC +2.0V for periods of less than 20 ns.

(2) Output shorted for no more than one second. No more than one output shorted at a time.

(3) This parameter is tested initially and after a design or process change that affects the parameter.

(4) Latch-up protection is provided for stresses up to 100 mA on address and data pins from 1V to VCC +1V.

(5) Standby Current (ISB2)=0A (<900nA) for 93C46/56/57/66, (ISB2)=2A for 93C86.

Doc. No. 1023, Rev. J 2

93C46/56/57/66/86

PIN CAPACITANCE

Symbol Test Conditions Min Typ Max Units

COUT (3) Output Capacitance (DO) VOUT=0V 5 pF

CIN(3) Input Capacitance (CS, SK, DI, ORG) VIN=0V 5 pF

INSTRUCTION SET

Instruction Device Start Opcode Address Data Comments PE(2)

Type Bit x8 x16 x8 x16

READ 93C46 1 10 A6-A0 A5-A0 Read Address ANA0

93C56(1) 1 10 A8-A0 A7-A0

93C66 1 10 A8-A0 A7-A0

93C57 1 10 A7-A0 A6-A0

93C86 1 10 A10-A0 A9-A0 X

ERASE 93C46 1 11 A6-A0 A5-A0 Clear Address ANA0

93C56(1) 1 11 A8-A0 A7-A0

93C66 1 11 A8-A0 A7-A0

93C57 1 11 A7-A0 A6-A0

93C86 1 11 A10-A0 A9-A0 I

WRITE 93C46 1 01 A6-A0 A5-A0 D7-D0 D15-D0 Write Address ANA0

93C56(1) 1 01 A8-A0 A7-A0 D7-D0 D15-D0

93C66 1 01 A8-A0 A7-A0 D7-D0 D15-D0

93C57 1 01 A7-A0 A6-A0 D7-D0 D15-D0

93C86 1 01 A10-A0 A9-A0 D7-D0 D15-D0 I

EWEN 93C46 1 00 11XXXXX 11XXXX Write Enable

93C56 1 00 11XXXXXXX 11XXXXXX

93C66 1 00 11XXXXXXX 11XXXXXX

93C57 1 00 11XXXXXX 11XXXXX

93C86 1 00 11XXXXXXXXX 11XXXXXXXX X

EWDS 93C46 1 00 00XXXXX 00XXXX Write Disable

93C56 1 00 00XXXXXXX 00XXXXXX

93C66 1 00 00XXXXXXX 00XXXXXX

93C57 1 00 00XXXXXX 00XXXXX

93C86 1 00 00XXXXXXXXX 00XXXXXXXX X

ERAL 93C46 1 00 10XXXXX 10XXXX Clear All Addresses

93C56 1 00 10XXXXXXX 10XXXXXX

93C66 1 00 10XXXXXXX 10XXXXXX

93C57 1 00 10XXXXXX 10XXXXX

93C86 1 00 10XXXXXXXXX 10XXXXXXXX I

WRAL 93C46 1 00 01XXXXX 01XXXX D7-D0 D15-D0 Write All Addresses

93C56 1 00 01XXXXXXX 01XXXXXX D7-D0 D15-D0

93C66 1 00 01XXXXXXX 01XXXXXX D7-D0 D15-D0

93C57 1 00 01XXXXXX 01XXXXX D7-D0 D15-D0

93C86 1 00 01XXXXXXXXX 01XXXXXXXX D7-D0 D15-D0 I

Note:

(1) Address bit A8 for 256x8 ORG and A7 for 128x16 ORG are "Don't Care" bits, but must be kept at either a "1" or "0" for READ, WRITE

and ERASE commands.

(2) Applicable only to 93C86

(3) This parameter is tested initially and after a design or process change that affects the parameter.

Doc. No. 1023, Rev. J

3

93C46/56/57/66/86

A.C. CHARACTERISTICS (93C46/56/57/66)

Limits

VCC = VCC = VCC =

1.8V-6V 2.5V-6V 4.5V-5.5V

Test

SYMBOL PARAMETER Conditions Min Max Min Max Min Max Units

tCSS CS Setup Time 200 100 50 ns

tCSH CS Hold Time 0 0 0 ns

tDIS DI Setup Time 400 200 100 ns

tDIH DI Hold Time 400 200 100 ns

tPD1 Output Delay to 1 1 0.5 0.25 s

tPD0 Output Delay to 0 CL = 100pF 1 0.5 0.25 s

(3)

tHZ(1) Output Delay to High-Z 400 200 100 ns

tEW Program/Erase Pulse Width 10 10 10 ms

tCSMIN Minimum CS Low Time 1 0.5 0.25 s

tSKHI Minimum SK High Time 1 0.5 0.25 s

tSKLOW Minimum SK Low Time 1 0.5 0.25 s

tSV Output Delay to Status Valid 1 0.5 0.25 s

SKMAX Maximum Clock Frequency DC 250 DC 500 DC 1000 kHz

A.C. CHARACTERISTICS (93C86)

Limits

VCC = VCC = VCC =

Test 1.8V-6V 2.5V-6V 4.5V-5.5V

SYMBOL PARAMETER Conditions Min Max Min Max Min Max Units

tCSS CS Setup Time 200 100 50 ns

tCSH CS Hold Time 0 0 0 ns

tDIS DI Setup Time 200 100 50 ns

tDIH DI Hold Time 200 100 50 ns

tPD1 Output Delay to 1 1 0.5 0.15 s

tPD0 Output Delay to 0 CL = 100pF 1 0.5 0.15 s

tHZ(1) Output Delay to High-Z (3) 400 200 100 ns

tEW Program/Erase Pulse Width 5 5 5 ms

tCSMIN Minimum CS Low Time 1 0.5 0.15 s

tSKHI Minimum SK High Time 1 0.5 0.15 s

tSKLOW Minimum SK Low Time 1 0.5 0.15 s

tSV Output Delay to Status Valid 1 0.5 0.1 s

SKMAX Maximum Clock Frequency DC 500 DC 1000 DC 3000 kHz

NOTE:

(1) This parameter is tested initially and after a design or process change that affects the parameter.

Doc. No. 1023, Rev. J 4

93C46/56/57/66/86

POWER-UP TIMING (1)(2)

SYMBOL PARAMETER Max Units

tPUR Power-up to Read Operation 1 ms

tPUW Power-up to Write Operation 1 ms

NOTE:

(1) This parameter is tested initially and after a design or process change that affects the parameter.

(2) tPUR and tPUW are the delays required from the time VCC is stable until the specified operation can be initiated.

(3) The input levels and timing reference points are shown in AC Test Conditions table.

A.C. TEST CONDITIONS

Input Rise and Fall Times 50ns

Input Pulse Voltages 0.4V to 2.4V 4.5V VCC 5.5V

Timing Reference Voltages 0.8V, 2.0V 4.5V VCC 5.5V

Input Pulse Voltages 0.2VCC to 0.7VCC 1.8V VCC 4.5V

Timing Reference Voltages 0.5VCC 1.8V VCC 4.5V

Doc. No. 1023, Rev. J

5

93C46/56/57/66/86

DEVICE OPERATION

The CAT93C46/56(57)66/86 is a 1024/2048/4096/ the DI pin on the rising edge of the clock (SK). The DO

16,384-bit nonvolatile memory intended for use with pin is normally in a high impedance state except when

industry standard microprocessors. The CAT93C46/56/ reading data from the device, or when checking the

57/66/86 can be organized as either registers of 16 bits ready/busy status after a write operation.

or 8 bits. When organized as X16, seven 9-bit instruc-

tions for 93C46; seven 10-bit instructions for 93C57; The ready/busy status can be determined after the start

seven 11-bit instructions for 93C56 and 93C66; seven of a write operation by selecting the device (CS high) and

13-bit instructions for 93C86; control the reading, writing polling the DO pin; DO low indicates that the write

and erase operations of the device. When organized as operation is not completed, while DO high indicates that

X8, seven 10-bit instructions for 93C46; seven 11-bit the device is ready for the next instruction. If necessary,

instructions for 93C57; seven 12-bit instructions for the DO pin may be placed back into a high impedance

93C56 and 93C66: seven 14-bit instructions for 93C86; state during chip select by shifting a dummy 1 into the

control the reading, writing and erase operations of the DI pin. The DO pin will enter the high impedance state on

device. The CAT93C46/56/57/66/86 operates on a single the falling edge of the clock (SK). Placing the DO pin into

power supply and will generate on chip, the high voltage the high impedance state is recommended in applica-

required during any write operation. tions where the DI pin and the DO pin are to be tied

together to form a common DI/O pin.

Instructions, addresses, and write data are clocked into

Figure 1. Sychronous Data Timing

tSKHI tSKLOW tCSH

SK

tDIS tDIH

DI VALID VALID

tCSS

CS

tDIS tPD0,tPD1 tCSMIN

DO DATA VALID

93C46/56/57/66/86 F03

Figure 2a. Read Instruction Timing (93C46)

SK

tCSMIN

CS

STANDBY

AN AN1 A0

DI 1 1 0

tHZ

HIGH-Z tPD0 HIGH-Z

DO 0

DN DN1 D1 D0

93C46/56/57/66/86 F04

Doc. No. 1023, Rev. J 6

93C46/56/57/66/86

The format for all instructions sent to the device is a increment to the next address and shift out the next data

logical "1" start bit, a 2-bit (or 4-bit) opcode, 6-bit (93C46)/ word in a sequential READ mode. As long as CS is

/7-bit (93C57)/ 8-bit (93C56 or 93C66)/10-bit (93C86) continuously asserted and SK continues to toggle, the

(an additional bit when organized X8) and for write device will keep incrementing to the next address

operations a 16-bit data field (8-bit for X8 organizations). automatically until it reaches to the end of the address

space, then loops back to address 0. In the sequential

Note: This note is applicable only to 93C86. The Write, READ mode, only the initial data word is preceeded by

Erase, Write all and Erase all instructions require PE=1. a dummy zero bit. All subsequent data words will follow

If PE is left floating, 93C86 is in Program Enabled mode. without a dummy zero bit.

For Write Enable and Write Disable instruction PE=dont

care. Write

Read After receiving a WRITE command, address and the

Upon receiving a READ command and an address data, the CS (Chip Select) pin must be deselected for a

(clocked into the DI pin), the DO pin of the CAT93C46/ minimum of tCSMIN. The falling edge of CS will start the

56/57/66/86 will come out of the high impedance state self clocking clear and data store cycle of the memory

and, after sending an initial dummy zero bit, will begin location specified in the instruction. The clocking of the

shifting out the data addressed (MSB first). The output SK pin is not necessary after the device has entered the

data bits will toggle on the rising edge of the SK clock and self clocking mode. The ready/busy status of the

are stable after the specified time delay (tPD0 or tPD1). CAT93C46/56/57/66/86 can be determined by selecting

the device and polling the DO pin. Since this device

For the CAT93C56/57/66/86, after the initial data word features Auto-Clear before write, it is NOT necessary to

has been shifted out and CS remains asserted with the erase a memory location before it is written into.

SK clock continuing to toggle, the device will automatically

Figure 2b. Read Instruction Timing (93C56/57/66/86)

SK

1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

CS

Don't Care

AN AN1 A0

DI 1 1 0

HIGH-Z

DO

Dummy 0

D15 . . . D0 Address + 1 Address + 2 Address + n

or D15 . . . D0 D15 . . . D0 D15 . . .

D7 . . . D0 or or or

D7 . . . D0 D7 . . . D0 D7 . . .

Figure 3. Write Instruction Timing

SK

tCSMIN

CS STATUS STANDBY

VERIFY

AN AN-1 A0 DN D0

DI 1 0 1

tSV tHZ

BUSY

HIGH-Z

DO READY

HIGH-Z

tEW

93C46/56/57/66/86 F05

Doc. No. 1023, Rev. J

7

93C46/56/57/66/86

Erase Erase All

Upon receiving an ERASE command and address, the Upon receiving an ERAL command, the CS (Chip Select)

CS (Chip Select) pin must be deasserted for a minimum pin must be deselected for a minimum of tCSMIN. The

of tCSMIN. The falling edge of CS will start the self clocking falling edge of CS will start the self clocking clear cycle

clear cycle of the selected memory location. The clocking of all memory locations in the device. The clocking of the

of the SK pin is not necessary after the device has SK pin is not necessary after the device has entered the

entered the self clocking mode. The ready/busy status of self clocking mode. The ready/busy status of the

the CAT93C46/56/57/66/86 can be determined by CAT93C46/56/57/66/86 can be determined by selecting

selecting the device and polling the DO pin. Once the device and polling the DO pin. Once cleared, the

cleared, the content of a cleared location returns to a contents of all memory bits return to a logical 1 state.

logical 1 state.

Write All

Erase/Write Enable and Disable

Upon receiving a WRAL command and data, the CS

The CAT93C46/56/57/66/86 powers up in the write (Chip Select) pin must be deselected for a minimum of

disable state. Any writing after power-up or after an tCSMIN. The falling edge of CS will start the self clocking

EWDS (write disable) instruction must first be preceded data write to all memory locations in the device. The

by the EWEN (write enable) instruction. Once the write clocking of the SK pin is not necessary after the device

instruction is enabled, it will remain enabled until power has entered the self clocking mode. (Note 1.) The ready/

to the device is removed, or the EWDS instruction is busy status of the CAT93C46/56/57/66/86 can be

sent. The EWDS instruction can be used to disable all determined by selecting the device and polling the DO

CAT93C46/56/57/66/86 write and clear instructions, pin. It is not necessary for all memory locations to be

and will prevent any accidental writing or clearing of the cleared before the WRAL command is executed.

device. Data can be read normally from the device

regardless of the write enable/disable status.

Figure 4. Erase Instruction Timing

SK

CS STATUS VERIFY STANDBY

tCS

AN AN-1 A0

DI 1 1 1

tSV tHZ

HIGH-Z

DO BUSY READY

HIGH-Z

tEW

93C46/56/57/66/86 F06

Doc. No. 1023, Rev. J 8

93C46/56/57/66/86

Figure 5. EWEN/EWDS Instruction Timing

SK

CS STANDBY

DI 1 0 0 *

* ENABLE=11

DISABLE=00

93C46/56/57/66/86 F07

Figure 6. ERAL Instruction Timing

SK

CS STATUS VERIFY STANDBY

tCS

DI 1 0 0 1 0

tSV tHZ

HIGH-Z

DO BUSY READY

HIGH-Z

tEW

93C46/56/57/66/86 F08

Figure 7. WRAL Instruction Timing

SK

CS STATUS VERIFY STANDBY

tCSMIN

DI 1 0 0 0 1 DN D0

tSV tHZ

DO BUSY READY

HIGH-Z

tEW

93C46/56/57/66/86 F09

Doc. No. 1023, Rev. J

9

93C46/56/57/66/86

ORDERING INFORMATION

Prefix Device # Suffix

CAT 93C46 S I -1.8 TE13

Optional Product Temperature Range Tape & Reel

Company ID Number Blank = Commercial (0 - 70C) TE13: 2000/Reel

93C46: 1K I = Industrial (-40 - 85C)

93C56: 2K A = Automotive (-40 - 105C)

93C57: 2K E = Extended (-40C to + 125C)

93C66: 4K

93C86: 16K Operating Voltage

Package

P = PDIP Blank (Vcc=2.5 to 6.0V)

S = SOIC (JEDEC) 1.8 (Vcc=1.8 to 6.0V)

J = SOIC (JEDEC)

K = SOIC (EIAJ)

U = TSSOP*

RD4 = TDFN (3x3mm)

ZD4 = TDFN (3x3mm, Lead free, Halogen free)

L = PDIP (Lead free, Halogen free)

V = SOIC, JEDEC (Lead free, Halogen free)

W= SOIC, JEDEC (Lead free, Halogen free)

X = SOIC, EIAJ (Lead free, Halogen free)

Y = TSSOP (Lead free, Halogen free)*

*CAT93C46/56/57/66 only

Notes:

(1) The device used in the above example is a 93C46SI-1.8TE13 (SOIC, Industrial Temperature, 1.8 Volt to 6 Volt Operating Voltage,

Tape & Reel)

(2) TSSOP (U/Y) package only available for 93C46/56/57/66

Copyrights, Trademarks and Patents

Trademarks and registered trademarks of Catalyst Semiconductor include each of the following:

DPP AE2

Catalyst Semiconductor has been issued U.S. and foreign patents and has patent applications pending that protect its products. For a complete list of patents

issued to Catalyst Semiconductor contact the Companys corporate office at 408.542.1000.

CATALYST SEMICONDUCTOR MAKES NO WARRANTY, REPRESENTATION OR GUARANTEE, EXPRESS OR IMPLIED, REGARDING THE SUITABILITY OF ITS

PRODUCTS FOR ANY PARTICULAR PURPOSE, NOR THAT THE USE OF ITS PRODUCTS WILL NOT INFRINGE ITS INTELLECTUAL PROPERTY RIGHTS OR THE

RIGHTS OF THIRD PARTIES WITH RESPECT TO ANY PARTICULAR USE OR APPLICATION AND SPECIFICALLY DISCLAIMS ANY AND ALL LIABILITY ARISING

OUT OF ANY SUCH USE OR APPLICATION, INCLUDING BUT NOT LIMITED TO, CONSEQUENTIAL OR INCIDENTAL DAMAGES.

Catalyst Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or

other applications intended to support or sustain life, or for any other application in which the failure of the Catalyst Semiconductor product could create a

situation where personal injury or death may occur.

Catalyst Semiconductor reserves the right to make changes to or discontinue any product or service described herein without notice. Products with data sheets

labeled "Advance Information" or "Preliminary" and other products described herein may not be in production or offered for sale.

Catalyst Semiconductor advises customers to obtain the current version of the relevant product information before placing orders. Circuit diagrams illustrate

typical semiconductor applications and may not be complete.

Catalyst Semiconductor, Inc.

Corporate Headquarters

1250 Borregas Avenue

Sunnyvale, CA 94089 Publication #: 1023

Phone: 408.542.1000 Revison: J

Fax: 408.542.1200 Issue date: 6/23/03

www.catalyst-semiconductor.com Type: Final

Doc. No. 1023, Rev. J 10

S-ar putea să vă placă și

- TMC93LC46Document15 paginiTMC93LC46Agustin AndrokaitesÎncă nu există evaluări

- Doc0172 PDFDocument20 paginiDoc0172 PDFnarayanÎncă nu există evaluări

- Three-Wire Serial EEPROM: 1. FeaturesDocument17 paginiThree-Wire Serial EEPROM: 1. FeatureskppsadiÎncă nu există evaluări

- Three-Wire Serial Eeprom: FeaturesDocument21 paginiThree-Wire Serial Eeprom: FeaturesАлександр СаральповÎncă nu există evaluări

- 16K Microwire Compatible Serial EEPROM: 93AA86A/B/C, 93LC86A/B/C, 93C86A/B/CDocument27 pagini16K Microwire Compatible Serial EEPROM: 93AA86A/B/C, 93LC86A/B/C, 93C86A/B/CJesús GutiérrezÎncă nu există evaluări

- 8K/16K 5.0V Microwire Serial EEPROM: FeaturesDocument12 pagini8K/16K 5.0V Microwire Serial EEPROM: FeaturesStephensonÎncă nu există evaluări

- Three-Wire Serial Eeproms: FeaturesDocument21 paginiThree-Wire Serial Eeproms: FeaturesX'mix DreamerÎncă nu există evaluări

- CAT93C4611J-25TE13 To CAT93C8634UI-45TE13Document11 paginiCAT93C4611J-25TE13 To CAT93C8634UI-45TE13rolandseÎncă nu există evaluări

- 2K Microwire Compatible Serial EEPROM: 93AA56A/B/C, 93LC56A/B/C, 93C56A/B/CDocument30 pagini2K Microwire Compatible Serial EEPROM: 93AA56A/B/C, 93LC56A/B/C, 93C56A/B/CAndrea MartinezÎncă nu există evaluări

- Asus K46CDocument62 paginiAsus K46CBintangCompÎncă nu există evaluări

- 93C66 PDFDocument22 pagini93C66 PDFCristian Esteban TamashiroÎncă nu există evaluări

- 93LC46Document30 pagini93LC46DCTRONICSÎncă nu există evaluări

- AT93CXXDocument15 paginiAT93CXXcallkalaiÎncă nu există evaluări

- 3-Wire Serial Eeproms: FeaturesDocument18 pagini3-Wire Serial Eeproms: FeaturesAriana ScheiderÎncă nu există evaluări

- 8K/16K 5.0V Microwire Serial EEPROM: Features: Package TypesDocument20 pagini8K/16K 5.0V Microwire Serial EEPROM: Features: Package Typesfarhood ranjbarkhanghahÎncă nu există evaluări

- 主板硬體線路分析Document47 pagini主板硬體線路分析bingkong100% (2)

- Xmc-Xm25qh64ahig C328461Document75 paginiXmc-Xm25qh64ahig C328461c4rl0slinuxÎncă nu există evaluări

- 1K-16K Microwire Compatible Serial Eeproms: Features: DescriptionDocument38 pagini1K-16K Microwire Compatible Serial Eeproms: Features: DescriptionStuxnetÎncă nu există evaluări

- Low Power Serial E2PROM with Wide Voltage RangeDocument42 paginiLow Power Serial E2PROM with Wide Voltage RangeCOZLÎncă nu există evaluări

- Acer Aspire 1710 (Quanta DT3) PDFDocument35 paginiAcer Aspire 1710 (Quanta DT3) PDFMustafa AkanÎncă nu există evaluări

- 93LC46ADocument34 pagini93LC46AmordiscoverdeÎncă nu există evaluări

- Toshiba Osaka NM-CS1 200400329 TC7778zba000 6050A0059801-MB-A01 SchematicDocument55 paginiToshiba Osaka NM-CS1 200400329 TC7778zba000 6050A0059801-MB-A01 Schematicdeppa lannaÎncă nu există evaluări

- S-93C46B/56B/66B: Cmos Serial E PromDocument45 paginiS-93C46B/56B/66B: Cmos Serial E PromBruno Garido PerezÎncă nu există evaluări

- CDocument35 paginiCJagopati Jr.Încă nu există evaluări

- Fujitsu Siemens Amilo Pa 1538 PTB51Document46 paginiFujitsu Siemens Amilo Pa 1538 PTB51IvanM72Încă nu există evaluări

- Manual Programacao Argox As 8000Document34 paginiManual Programacao Argox As 8000satishÎncă nu există evaluări

- Mainboard ESC Model CRU51 M7Document39 paginiMainboard ESC Model CRU51 M7ivo rodriguesÎncă nu există evaluări

- Mainboard ESC Model P4M800PRO MDocument29 paginiMainboard ESC Model P4M800PRO MHo Thanh BinhÎncă nu există evaluări

- F59L1G81MA EliteSemiconductorDocument44 paginiF59L1G81MA EliteSemiconductorjustin tiongcoÎncă nu există evaluări

- CAT93C46B 1-Kb Microwire Serial Eeprom: DescriptionDocument14 paginiCAT93C46B 1-Kb Microwire Serial Eeprom: DescriptionJose Polan VillalobosÎncă nu există evaluări

- En25qh64a EonDocument75 paginiEn25qh64a EonMarcelituz RojasÎncă nu există evaluări

- Macronix MX25L8005M2C 15G DatasheetDocument44 paginiMacronix MX25L8005M2C 15G DatasheetAlex CrofordÎncă nu există evaluări

- Foxconn h61mxe-V h61m06 Rev. ADocument45 paginiFoxconn h61mxe-V h61m06 Rev. AĐạt NguyễnÎncă nu există evaluări

- Acer Aspire 1700 (Quanta DT1) PDFDocument35 paginiAcer Aspire 1700 (Quanta DT1) PDFMustafa AkanÎncă nu există evaluări

- In-System Programming Cable ATDH2225 Fpga Configuration Eeprom MemoryDocument7 paginiIn-System Programming Cable ATDH2225 Fpga Configuration Eeprom Memorym3y54mÎncă nu există evaluări

- Scheme Fujitsu Siemens Livebook Amilo Pa1538 (Fic ptb50 xtb70 Rev0.4) PDFDocument46 paginiScheme Fujitsu Siemens Livebook Amilo Pa1538 (Fic ptb50 xtb70 Rev0.4) PDFRoxana Aldea-CiaciruÎncă nu există evaluări

- COMODORE-FIC MY040 PY640 Rev0.3Document58 paginiCOMODORE-FIC MY040 PY640 Rev0.3Rodrigo EdÎncă nu există evaluări

- AMILO PA1538 PTB50 x500Document57 paginiAMILO PA1538 PTB50 x500EduardoSobrinhoÎncă nu există evaluări

- P4m800pro-M2 V2 OkDocument27 paginiP4m800pro-M2 V2 Oknow2moreÎncă nu există evaluări

- hn29v1g91t30 NANDDocument92 paginihn29v1g91t30 NANDValoha VlÎncă nu există evaluări

- 93C86Document20 pagini93C86cgmannerheimÎncă nu există evaluări

- Sony Vaio VGN-AW Series MBX-194 M780 SD FOXCONN M780 CantigaP WPCE775LDocument77 paginiSony Vaio VGN-AW Series MBX-194 M780 SD FOXCONN M780 CantigaP WPCE775LChetin TekinÎncă nu există evaluări

- NM A931Document98 paginiNM A931mitusharmaÎncă nu există evaluări

- EN25Q32C 32 Megabit Serial Flash Memory With 4kbyte Uniform SectorDocument62 paginiEN25Q32C 32 Megabit Serial Flash Memory With 4kbyte Uniform Sectoramir baroughÎncă nu există evaluări

- 7C13 10 PDFDocument48 pagini7C13 10 PDFdavid pintoÎncă nu există evaluări

- Common OCD Pinouts: Signals Specified by The ManufacturerDocument4 paginiCommon OCD Pinouts: Signals Specified by The ManufacturerMarcelo BaptistaÎncă nu există evaluări

- Esquema Placa Mae BiostarDocument39 paginiEsquema Placa Mae BiostarERICO STRAMANDINOLIÎncă nu există evaluări

- 89c51ed2 Datasheet PDFDocument137 pagini89c51ed2 Datasheet PDFAbdulhussain AmravatiwalaÎncă nu există evaluări

- s29190 DatasheetDocument44 paginis29190 Datasheetsamsularief03Încă nu există evaluări

- MSI MS-7978 Block DiagramDocument58 paginiMSI MS-7978 Block DiagramZlenox Luis Leonardo Taboada ErmenegildoÎncă nu există evaluări

- I2C-Compatible 32-Kbit Serial E2PROM Data SheetDocument22 paginiI2C-Compatible 32-Kbit Serial E2PROM Data SheetJorge Humberto DuqueÎncă nu există evaluări

- Msi ms-7309 Rev 0a SCH PDFDocument35 paginiMsi ms-7309 Rev 0a SCH PDFPavel SuminÎncă nu există evaluări

- Msis-Rma 羅覓林 2091109: Krishna (MS-7647)Document38 paginiMsis-Rma 羅覓林 2091109: Krishna (MS-7647)Multiservicio DELEDENÎncă nu există evaluări

- Microprocessors & their Operating Systems: A Comprehensive Guide to 8, 16 & 32 Bit Hardware, Assembly Language & Computer ArchitectureDe la EverandMicroprocessors & their Operating Systems: A Comprehensive Guide to 8, 16 & 32 Bit Hardware, Assembly Language & Computer ArchitectureEvaluare: 1 din 5 stele1/5 (1)

- 8051 Microcontroller: An Applications Based IntroductionDe la Everand8051 Microcontroller: An Applications Based IntroductionEvaluare: 5 din 5 stele5/5 (6)

- 8-Bit, 250 Msps Adc With Demuxed Outputs Technical Data: Applications FeaturesDocument11 pagini8-Bit, 250 Msps Adc With Demuxed Outputs Technical Data: Applications FeaturesnudufoqiÎncă nu există evaluări

- Irf 9 Z 34 NDocument9 paginiIrf 9 Z 34 NHugoÎncă nu există evaluări

- MCR22-6, MCR22-8 Sensitive Gate Silicon Controlled RectifiersDocument8 paginiMCR22-6, MCR22-8 Sensitive Gate Silicon Controlled RectifiersnudufoqiÎncă nu există evaluări

- NPN Switching Transistor: Absolute Maximum RatingsDocument7 paginiNPN Switching Transistor: Absolute Maximum RatingsnudufoqiÎncă nu există evaluări

- Stepper Motor Driver MC3479: ON SemiconductorDocument12 paginiStepper Motor Driver MC3479: ON SemiconductornudufoqiÎncă nu există evaluări

- Hgtd7N60B3S, Hgt1S7N60B3S, Hgtp7N60B3: 14A, 600V, Ufs Series N-Channel Igbts FeaturesDocument7 paginiHgtd7N60B3S, Hgt1S7N60B3S, Hgtp7N60B3: 14A, 600V, Ufs Series N-Channel Igbts FeaturesnudufoqiÎncă nu există evaluări

- BFR92/BFR92R: Silicon NPN Planar RF TransistorDocument6 paginiBFR92/BFR92R: Silicon NPN Planar RF TransistornudufoqiÎncă nu există evaluări

- Advanced Micro Devices 2 Megabit (262,144 X 8-Bit) CMOS EPROMDocument12 paginiAdvanced Micro Devices 2 Megabit (262,144 X 8-Bit) CMOS EPROMnudufoqiÎncă nu există evaluări

- 4-Pin Phototransistor Optocouplers: H11Aa814 Series H11A617 Series H11A817 SeriesDocument9 pagini4-Pin Phototransistor Optocouplers: H11Aa814 Series H11A617 Series H11A817 SeriesnudufoqiÎncă nu există evaluări

- NPN General Purpose Amplifier: Symbol Parameter Value UnitsDocument5 paginiNPN General Purpose Amplifier: Symbol Parameter Value UnitsnudufoqiÎncă nu există evaluări

- Applications Description: General Purpose NPN Transistor ArrayDocument5 paginiApplications Description: General Purpose NPN Transistor ArraynudufoqiÎncă nu există evaluări

- D D D D D D D D: NE5532, NE5532A Dual Low-Noise Operational AmplifiersDocument4 paginiD D D D D D D D: NE5532, NE5532A Dual Low-Noise Operational AmplifiersnudufoqiÎncă nu există evaluări

- 512K (64K X 8) CMOS EPROM: Features Package TypesDocument8 pagini512K (64K X 8) CMOS EPROM: Features Package Types81968Încă nu există evaluări

- NPN General Purpose Amplifier: Symbol Parameter Value UnitsDocument5 paginiNPN General Purpose Amplifier: Symbol Parameter Value UnitsnudufoqiÎncă nu există evaluări

- IRFZ48Document9 paginiIRFZ48Тодор ГенчевÎncă nu există evaluări

- 2N2222 Transistor BJTDocument2 pagini2N2222 Transistor BJTMauricioGSÎncă nu există evaluări

- PIC18F4550 DatasheetDocument426 paginiPIC18F4550 DatasheetFelipe Luis JarekÎncă nu există evaluări

- Data Sheet: PNP Darlington TransistorDocument6 paginiData Sheet: PNP Darlington TransistornudufoqiÎncă nu există evaluări

- Data Sheet: PNP Switching TransistorDocument7 paginiData Sheet: PNP Switching TransistornudufoqiÎncă nu există evaluări

- BF245Document2 paginiBF245nudufoqiÎncă nu există evaluări

- Off-Highway 6600 Series Transmission SpecsDocument2 paginiOff-Highway 6600 Series Transmission SpecsIng Dimatiguz0% (1)

- Handout 4: Course Notes Were Prepared by Dr. R.M.A.P. Rajatheva and Revised by Dr. Poompat SaengudomlertDocument7 paginiHandout 4: Course Notes Were Prepared by Dr. R.M.A.P. Rajatheva and Revised by Dr. Poompat SaengudomlertBryan YaranonÎncă nu există evaluări

- SAP PPM 5.0 Certification Exam TopicsDocument7 paginiSAP PPM 5.0 Certification Exam TopicsongkecanthoÎncă nu există evaluări

- Nursing ProcessDocument88 paginiNursing ProcessGerard On LineÎncă nu există evaluări

- Specification of PCB800099 Controller Board V1.0Document10 paginiSpecification of PCB800099 Controller Board V1.0benabdullahÎncă nu există evaluări

- Organizational Development and EvaluationDocument22 paginiOrganizational Development and EvaluationFransisca RosalinÎncă nu există evaluări

- VUCG Guia de Instalacion y Comisionamiento en Ingles 1ZSC000562-AAY en Rev 1 - LowDocument56 paginiVUCG Guia de Instalacion y Comisionamiento en Ingles 1ZSC000562-AAY en Rev 1 - Lowarmandoa71565Încă nu există evaluări

- Preview-9780429675119 A38620781Document53 paginiPreview-9780429675119 A38620781Milton Alexandre ZiehlsdorffÎncă nu există evaluări

- 2022 MSK Poster JonDocument1 pagină2022 MSK Poster Jonjonathan wijayaÎncă nu există evaluări

- Daily Dawn Newspaper Vocabulary with Urdu MeaningsDocument4 paginiDaily Dawn Newspaper Vocabulary with Urdu MeaningsBahawal Khan JamaliÎncă nu există evaluări

- Checklist of Bats From Iraq-Mammalian Biology 2020Document14 paginiChecklist of Bats From Iraq-Mammalian Biology 2020Adil DalafÎncă nu există evaluări

- Paper 2Document17 paginiPaper 2Khushil100% (1)

- ECOSYS FS-2100D Ecosys Fs-2100Dn Ecosys Fs-4100Dn Ecosys Fs-4200Dn Ecosys Fs-4300Dn Ecosys Ls-2100Dn Ecosys Ls-4200Dn Ecosys Ls-4300DnDocument33 paginiECOSYS FS-2100D Ecosys Fs-2100Dn Ecosys Fs-4100Dn Ecosys Fs-4200Dn Ecosys Fs-4300Dn Ecosys Ls-2100Dn Ecosys Ls-4200Dn Ecosys Ls-4300DnJosé Bonifácio Marques de AmorimÎncă nu există evaluări

- Viavi: Variable Optical Attenuators (mVOA-C1)Document6 paginiViavi: Variable Optical Attenuators (mVOA-C1)gwÎncă nu există evaluări

- Even Sem - Odd Sem - MD MS - MA, MSC, MCom - Previous - Final Main Exam Result 2021 - Mahatma Jyotiba Phule Rohilkhand UniversityDocument2 paginiEven Sem - Odd Sem - MD MS - MA, MSC, MCom - Previous - Final Main Exam Result 2021 - Mahatma Jyotiba Phule Rohilkhand UniversityprashantÎncă nu există evaluări

- Mastercam 8.1 Beta 4: New Verification Engine in Beta 4! Sub-Programs Post ChangesDocument48 paginiMastercam 8.1 Beta 4: New Verification Engine in Beta 4! Sub-Programs Post ChangesSaul Saldana LoyaÎncă nu există evaluări

- L1Document7 paginiL1Francisco Roberto Trujillo LeonÎncă nu există evaluări

- GF - 4 - GF - 6 - 790 700 337 - 01 - enDocument2 paginiGF - 4 - GF - 6 - 790 700 337 - 01 - enAdrianÎncă nu există evaluări

- 3.dummy VariablesDocument25 pagini3.dummy VariablesUnushka ShresthaÎncă nu există evaluări

- ATT III - 13. Prevent, Control and Fight Fires On BoardDocument9 paginiATT III - 13. Prevent, Control and Fight Fires On BoardPak WeÎncă nu există evaluări

- Microsoft Word - JOB DESCRIPTION Staff AccountantDocument2 paginiMicrosoft Word - JOB DESCRIPTION Staff Accountantanon-634050100% (3)

- POOJA TRADING CO. Price List for FRP Manhole CoversDocument1 paginăPOOJA TRADING CO. Price List for FRP Manhole Coversmitesh20281Încă nu există evaluări

- PBS CCMD CVMD Administrator GuideDocument40 paginiPBS CCMD CVMD Administrator GuidesharadcsinghÎncă nu există evaluări

- Aadhaar is proof of identity, not citizenshipDocument1 paginăAadhaar is proof of identity, not citizenshipPARTAPÎncă nu există evaluări

- The Importance of Understanding A CommunityDocument23 paginiThe Importance of Understanding A Communityra sÎncă nu există evaluări

- (Acta Universitatis Gothoburgensis) Tryggve Göransson - Albinus, Alcinous, Arius Didymus (1995) PDFDocument128 pagini(Acta Universitatis Gothoburgensis) Tryggve Göransson - Albinus, Alcinous, Arius Didymus (1995) PDFMarcos EstevamÎncă nu există evaluări

- In The Shadow of The CathedralDocument342 paginiIn The Shadow of The CathedralJoy MenezesÎncă nu există evaluări

- Project Equipment Load AnalysisDocument54 paginiProject Equipment Load Analysisrajeshmk2002100% (6)

- Yoshimi Advanced User ManualDocument297 paginiYoshimi Advanced User Manualfby999Încă nu există evaluări

- Concept MappingDocument8 paginiConcept MappingRashid LatiefÎncă nu există evaluări