Documente Academic

Documente Profesional

Documente Cultură

It May Thus Terminate An Output Pulse Prematurely

Încărcat de

ogeh jeffrey jeremiahTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

It May Thus Terminate An Output Pulse Prematurely

Încărcat de

ogeh jeffrey jeremiahDrepturi de autor:

Formate disponibile

voltage level of 2/3 V+ (the normal voltage on pin 5).

The action of the threshold pin is level

sensitive, allowing slow rate-of-change waveforms. The voltage range that can safely be

applied to the threshold pin is between V+ and ground. A dc current, termed thethreshold

current, must also flow into this terminal from the external circuit. This current is typically

0.1A, and will define the upper limit of total resistance allowable from pin 6 to V+. For

either timing configuration operating at V+ = 5 volts, this resistance is 16 Mega- ohm. For 15

volt operation, the maximum value of resistance is 20 MegaOhms.

Pin 7 (Discharge):This pin is connected to the open collector of a npn transistor (Q14), the

emitter of which goes to ground, so that when the transistor is

turned "on", pin 7 is effectively shorted to ground. Usually the timing capacitor is connected

between pin 7 and ground and is discharged when the transistor turns "on". The conduction

state of this transistor is identical in timing to that of the output stage. It is "on" (low

resistance to ground) when the output is low and "off" (high resistance to ground) when the

output is high. In both the monostable and astable time modes, this transistor switch is used to

clamp the

appropriate nodes of the timing network to ground. Saturation voltage is typically below

100mV (milli-Volt) .

Pin 8 (V +):The V+ pin (also referred to as Vcc) is the positive supply voltage terminal of the

555 timer IC. Supply-voltage operating range for the 555 is +4.5 volts (minimum) to +16

volts (maximum), and it is specified for operation between +5 volts and +15 volts. The device

will operate essentially the same over this range of voltages without change in timing period.

Actually, the most significant operational difference is the output drive capability, which

increases for both current and voltage range as the supply voltage is increased. Sensitivity of

time interval to supply voltage change is low, typically 0.1% per volt. There are special and

military devices available that operate at voltages as high as 18 volts.

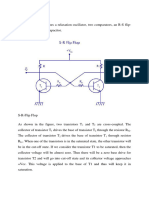

3.5. Monostable Multivibrator Circuit details

Pin 1 is grounded. Trigger input is applied to pin 2. In quiescent condition of output this input

is kept at + VCC. To obtain transition of output from stable state to quasi-stable state, a

negative-going pulse of narrow width (a width smaller than expected pulse width of output

waveform) and amplitude of greater than + 2/3 VCC is applied to pin 2. Output is taken from

pin 3. Pin 4 is usually connected to + VCC to avoid accidental reset. Pin 5 is grounded through

a 0.01 u F capacitor to avoid noise problem. Pin 6 (threshold) is shorted to pin 7. A resistor

RA is connected between pins 6 and 8. At pins 7 a discharge capacitor is connected while pin

8 is connected to supply VCC.

3.6. 555 monostable-multivibrator-operation

The operation of the circuit is explained below:

Initially, when the output at pin 3 is low i.e. the circuit is in a stable state, the transistor is on

and capacitor- C is shorted to ground. When a negative pulse is applied to pin 2, the trigger

input falls below +1/3 VCC, the output of comparator goes high which resets the flip-flop and

consequently the transistor turns off and the output at pin 3 goes high. This is the transition of

the output from stable to quasi-stable state, as shown in figure. As the discharge transistor is

cutoff, the capacitor C begins charging toward +VCC through resistance RA with a time

constant equal to RAC. When the increasing capacitor voltage becomes slightly greater than

+2/3 VCC, the output of comparator 1 goes high, which sets the flip-flop. The transistor goes

to saturation, thereby discharging the capacitor C and the output of the timer goes low, as

illustrated in figure.Thus the

S-ar putea să vă placă și

- 555 TimerDocument12 pagini555 Timerlalaine reginaldoÎncă nu există evaluări

- The 555 Timer IC (Adapted From) : CaseDocument12 paginiThe 555 Timer IC (Adapted From) : CaseBiswajit Sarkar100% (1)

- Theory:The 555 Timer Configured For Monostable OperationDocument3 paginiTheory:The 555 Timer Configured For Monostable OperationkumararguruÎncă nu există evaluări

- 555 Timer Integrated CircuitDocument8 pagini555 Timer Integrated CircuitTalha WaqarÎncă nu există evaluări

- Operation 555 Timer/OscillatorDocument7 paginiOperation 555 Timer/OscillatoryuvakiraniÎncă nu există evaluări

- 555 TimerDocument3 pagini555 TimerchandrakanthÎncă nu există evaluări

- 6.1 IC555 TIMER: Circuit ComponentsDocument8 pagini6.1 IC555 TIMER: Circuit ComponentsManish PradhanÎncă nu există evaluări

- IC555 TimerDocument8 paginiIC555 TimerRaflysyah PutraÎncă nu există evaluări

- The Important Features of The 555 Timer AreDocument7 paginiThe Important Features of The 555 Timer ArePathella SudhakarÎncă nu există evaluări

- Electronics Lab ManualDocument92 paginiElectronics Lab ManualVolodya SmolyakÎncă nu există evaluări

- Ic Applications Lab NewDocument12 paginiIc Applications Lab NewSandy RonaldoÎncă nu există evaluări

- SE/NE 555 Timer. It Is Basically A Monolithic Timing Circuit That Produces Accurate and Highly Stable Time Delays orDocument12 paginiSE/NE 555 Timer. It Is Basically A Monolithic Timing Circuit That Produces Accurate and Highly Stable Time Delays orEFraim Manzano FranciscoÎncă nu există evaluări

- Multivibrador Com Ci 555Document11 paginiMultivibrador Com Ci 555joselito1juniorÎncă nu există evaluări

- Lica ManualDocument99 paginiLica Manualspeak2dasÎncă nu există evaluări

- Multivibrator CircuitsDocument11 paginiMultivibrator CircuitsSatyaki ChowdhuryÎncă nu există evaluări

- ME 455/555 - Lab 2 - 555 TimersDocument10 paginiME 455/555 - Lab 2 - 555 TimersGustavo KernÎncă nu există evaluări

- Timer 555 - ManualDocument20 paginiTimer 555 - ManualXen XeonÎncă nu există evaluări

- Ci 555Document25 paginiCi 555Cristian VacaÎncă nu există evaluări

- 555 Timer IC: The Important Features of The 555 Timer AreDocument5 pagini555 Timer IC: The Important Features of The 555 Timer AreChara GalaÎncă nu există evaluări

- KDAS OPAMP APPLICATIONsDocument24 paginiKDAS OPAMP APPLICATIONsKingshuk GuptaÎncă nu există evaluări

- Report IC 555 TimerDocument17 paginiReport IC 555 TimerSantosh YadavÎncă nu există evaluări

- 555 Timer: by D.V.Kamat, Faculty Department of E&C Engg., MITDocument21 pagini555 Timer: by D.V.Kamat, Faculty Department of E&C Engg., MITRupsa SahaÎncă nu există evaluări

- Lab#10: Design and Study of IC 555 Multivibrator Circuits (2 Turns)Document11 paginiLab#10: Design and Study of IC 555 Multivibrator Circuits (2 Turns)Ayushman ChoudharyÎncă nu există evaluări

- Control Ics For Switched-Mode Power Supplies Tda 4601: Bipolar IcDocument27 paginiControl Ics For Switched-Mode Power Supplies Tda 4601: Bipolar IcMircea PanzariuÎncă nu există evaluări

- IC 555 TimerDocument6 paginiIC 555 Timeraditya pandeyÎncă nu există evaluări

- List The Features of 555 TimersDocument3 paginiList The Features of 555 TimersDivyesh DivakarÎncă nu există evaluări

- 555 Timer IC-Block Diagram-Working-Pin Out Configuration-Data SheetDocument13 pagini555 Timer IC-Block Diagram-Working-Pin Out Configuration-Data SheetΔημητριος ΣταθηςÎncă nu există evaluări

- Ic 555Document25 paginiIc 555Ahmed SaȜed El-HadyÎncă nu există evaluări

- 555Document80 pagini555elpasanteÎncă nu există evaluări

- 3.1555 TIMER:: Schematic SymbolDocument10 pagini3.1555 TIMER:: Schematic SymbolnagpradasÎncă nu există evaluări

- Principles Applications ICL7660Document10 paginiPrinciples Applications ICL7660Juan F. RamosÎncă nu există evaluări

- 555 Timer As Monostable MultivibratorDocument5 pagini555 Timer As Monostable MultivibratorDarshan BhansaliÎncă nu există evaluări

- IC 555 Multivibrator CircuitsDocument11 paginiIC 555 Multivibrator CircuitsKaran YadavÎncă nu există evaluări

- Clap SwitchDocument14 paginiClap SwitchAkilesh ArigelaÎncă nu există evaluări

- Opamp Applicationpart30Document31 paginiOpamp Applicationpart30KUNTALA DASÎncă nu există evaluări

- Ica WithoutreadingsmanualDocument90 paginiIca WithoutreadingsmanualAhmed Al MansurÎncă nu există evaluări

- Ica Withoutreadingsmanual PDFDocument90 paginiIca Withoutreadingsmanual PDFKimharly VersozaÎncă nu există evaluări

- Dsa 265104Document20 paginiDsa 265104foxx034Încă nu există evaluări

- High Current Switching Regulator: DescriptionDocument13 paginiHigh Current Switching Regulator: DescriptionEfrain PadronÎncă nu există evaluări

- A Mono Stable Multi Vibrato 1Document4 paginiA Mono Stable Multi Vibrato 1Noemi CaluzaÎncă nu există evaluări

- Data Sheet L298 PDFDocument13 paginiData Sheet L298 PDFbaymax love spideyÎncă nu există evaluări

- 100 VOLT 30 AMP H-Bridge PWM Motor Driver/Amplifier: M.S.Kennedy CorpDocument7 pagini100 VOLT 30 AMP H-Bridge PWM Motor Driver/Amplifier: M.S.Kennedy CorpDaniel SanchezÎncă nu există evaluări

- E L RelayDocument31 paginiE L RelayBal SubramaniÎncă nu există evaluări

- ElectronicIII - L3Document14 paginiElectronicIII - L3Aya MazinÎncă nu există evaluări

- Integrated Circuits:) of Flip-Flop ThroughDocument13 paginiIntegrated Circuits:) of Flip-Flop ThroughShubh MishraÎncă nu există evaluări

- 555 Timer - Oscillator TutorialDocument14 pagini555 Timer - Oscillator TutorialfgaluppoÎncă nu există evaluări

- Data Sheet: TDA8380ADocument21 paginiData Sheet: TDA8380Ajvazquez501Încă nu există evaluări

- Mini Project Report (CLAP SWITCH)Document22 paginiMini Project Report (CLAP SWITCH)Om Prakash Singh100% (4)

- UNIT-4 Special Ics The 555 Timer IcDocument10 paginiUNIT-4 Special Ics The 555 Timer IcVerloves LoveÎncă nu există evaluări

- Tl494 5v Power SupplyDocument5 paginiTl494 5v Power Supplysyed_hafeez_2Încă nu există evaluări

- Dual Full-Bridge Driver: DescriptionDocument12 paginiDual Full-Bridge Driver: DescriptionBastian RamadhanÎncă nu există evaluări

- UC3842 DesignDocument7 paginiUC3842 DesignCui BapÎncă nu există evaluări

- Chapter-1 Objective: 1.1 Objective of The ProjectDocument23 paginiChapter-1 Objective: 1.1 Objective of The ProjectPrashanth CooldudeÎncă nu există evaluări

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2De la EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Încă nu există evaluări

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1De la EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Evaluare: 2.5 din 5 stele2.5/5 (3)

- 2.6. Light Emitting DiodeDocument4 pagini2.6. Light Emitting Diodeogeh jeffrey jeremiahÎncă nu există evaluări

- Chapter One 1.1) Background of StudyDocument2 paginiChapter One 1.1) Background of Studyogeh jeffrey jeremiahÎncă nu există evaluări

- Resistor Resistance: Chapter TwoDocument2 paginiResistor Resistance: Chapter Twoogeh jeffrey jeremiahÎncă nu există evaluări

- How To Write Chapter 2Document16 paginiHow To Write Chapter 2ogeh jeffrey jeremiahÎncă nu există evaluări

- Chapter 2Document3 paginiChapter 2ogeh jeffrey jeremiahÎncă nu există evaluări

- HuanyangVFD Mach3SettingsDocument3 paginiHuanyangVFD Mach3SettingsEdy PutrantoÎncă nu există evaluări

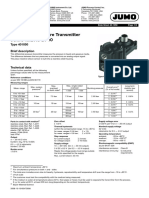

- Differential Pressure Transmitter Jumo Midas Dp10: Type 401050 Brief DescriptionDocument3 paginiDifferential Pressure Transmitter Jumo Midas Dp10: Type 401050 Brief Descriptionguruh anindraÎncă nu există evaluări

- Lamborghini URUSPERFORMANTE AIW081 23.05.23Document18 paginiLamborghini URUSPERFORMANTE AIW081 23.05.23Rafael FreitasÎncă nu există evaluări

- SERVICE MANUAL FOR SECA 766,767 (17-05-01-309-A)Document39 paginiSERVICE MANUAL FOR SECA 766,767 (17-05-01-309-A)Pañares Neil100% (3)

- TR10RS1 User Manual WindowsDocument14 paginiTR10RS1 User Manual WindowsMarquez JuanÎncă nu există evaluări

- Power Supply System Guardian Access 3U Instruction ManualDocument54 paginiPower Supply System Guardian Access 3U Instruction ManualMohammad KilaniÎncă nu există evaluări

- Final TELP 2019 AppDocument23 paginiFinal TELP 2019 AppRajib Kumar PaulÎncă nu există evaluări

- T-602 Test ReportDocument31 paginiT-602 Test Reportnaveendevi13Încă nu există evaluări

- Grade 6 Performance Task TleDocument6 paginiGrade 6 Performance Task TlepatrixiaÎncă nu există evaluări

- New Holland L865, Lx865, Lx885, Lx985 Skid Steer Loader Service Repair ManualDocument1.000 paginiNew Holland L865, Lx865, Lx885, Lx985 Skid Steer Loader Service Repair ManualRev'em uP Channel74% (35)

- Helical Hydraulic Rotary Actuators: Series L and TDocument20 paginiHelical Hydraulic Rotary Actuators: Series L and TDesign IPGEÎncă nu există evaluări

- Audi A4 b5 1.8t 13-1 Engine AssemblingDocument0 paginiAudi A4 b5 1.8t 13-1 Engine AssemblingDieter Bruck100% (1)

- USER MANUALLiebert-NXr-30kVA-200kVA-400VDocument95 paginiUSER MANUALLiebert-NXr-30kVA-200kVA-400VCesar CesarÎncă nu există evaluări

- DSG 03 Series Solenoid Operated Directional ValvesDocument12 paginiDSG 03 Series Solenoid Operated Directional ValvesSita Rama Raju PÎncă nu există evaluări

- DVD Player Repair Guide Humphrey KimathiDocument49 paginiDVD Player Repair Guide Humphrey KimathiNarcisseGuei100% (4)

- R 2 KyDocument3 paginiR 2 KyJorge AzurduyÎncă nu există evaluări

- SRF LCV 709 Bus: (Parts List)Document10 paginiSRF LCV 709 Bus: (Parts List)AnbarasanÎncă nu există evaluări

- Natural Gas Generator Set QSK60 Series Engine - Cummins West AfricaDocument4 paginiNatural Gas Generator Set QSK60 Series Engine - Cummins West AfricaVILAS VIJAYANÎncă nu există evaluări

- Laboratory Report Cover SheetDocument6 paginiLaboratory Report Cover SheetPre DatorÎncă nu există evaluări

- EOP of Instrument Air Failure-FinalDocument3 paginiEOP of Instrument Air Failure-FinalSantanu BasakÎncă nu există evaluări

- 725C and 730C Articulated Truck Hydraulic System (Interactive), 372-5143 (UENR3202)Document14 pagini725C and 730C Articulated Truck Hydraulic System (Interactive), 372-5143 (UENR3202)JHORDAN ANDR�S ARANCIBIA GODOYÎncă nu există evaluări

- Load SchedDocument10 paginiLoad SchedGary CudalÎncă nu există evaluări

- Heatsink: HSF Models 1000-1600 SCFMDocument34 paginiHeatsink: HSF Models 1000-1600 SCFMpedroÎncă nu există evaluări

- Solar PV System Technical Specifications SampleDocument4 paginiSolar PV System Technical Specifications SampleCharlie AycoÎncă nu există evaluări

- Advantech Protocol Bundle SolutionsDocument5 paginiAdvantech Protocol Bundle SolutionsBiswjit DeyÎncă nu există evaluări

- Regenerative Braking System On A Conventional BikeDocument14 paginiRegenerative Braking System On A Conventional Bike199 HDÎncă nu există evaluări

- CR 10Document16 paginiCR 10PETER LOCKÎncă nu există evaluări

- VSX 417 KDocument90 paginiVSX 417 KИгорьÎncă nu există evaluări

- Design and Fabrication of Development of Sand Filter and Separator Pedal PoweredDocument5 paginiDesign and Fabrication of Development of Sand Filter and Separator Pedal PoweredJithin V KÎncă nu există evaluări

- Catalog Fortuner GR Sport CompressedDocument8 paginiCatalog Fortuner GR Sport CompressedAbdul AjisÎncă nu există evaluări