Documente Academic

Documente Profesional

Documente Cultură

AMS Manual

Încărcat de

Paramesh WaranDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

AMS Manual

Încărcat de

Paramesh WaranDrepturi de autor:

Formate disponibile

Analog & Mixed Signal

Labs

Revision 4.0

IC615

ASSURA410

MMSIM121

IES122

Developed By

University Support Team

Cadence Design Systems, Bangalore

AMS Lab Manual

1

2013 Cadence Design Systems, Inc

Table of Contents:

NAND Gate in AMS Flow ............................................................................................................. 3

Creating New Library ..................................................................................................................... 4

Verilog Entry .................................................................................................................................. 6

Creating a New cell View ................................................................................................... 6

Verilog Design for AND Gate ............................................................................................ 7

Schematic Entry Inverter ............................................................................................................. 8

Adding Components to schematic ...................................................................................... 8

Adding pins to Schematic ................................................................................................. 11

Adding Wires to a Schematic ........................................................................................... 12

Saving the Design ............................................................................................................. 12

Symbol Creation ........................................................................................................................... 13

Objective: To create a symbol for the Inverter ................................................................. 13

Editing a Symbol............................................................................................................... 15

Schematic Entry NAND ............................................................................................................ 16

Creating a Schematic Cellview ......................................................................................... 16

Adding Components to schematic .................................................................................... 16

Adding pins to Schematic ................................................................................................. 17

Adding Wires to a Schematic ........................................................................................... 18

Saving the Design ............................................................................................................. 18

Building the Test Design .............................................................................................................. 20

Creating the Configuration View .................................................................................................. 21

Simulation of config View with AMS .......................................................................................... 25

Objective: To set up and run simulations on the NAND_Gate design ............................. 25

Starting the Simulation Environment................................................................................ 25

Choosing a Simulator ........................................................................................................ 25

Setting Connect Rules ....................................................................................................... 25

Setting the Model Libraries .............................................................................................. 26

Choosing Analyses............................................................................................................ 27

Selecting Signals for Plotting............................................................................................ 28

Running the Simulation .................................................................................................... 29

Saving the Simulator State ................................................................................................ 30

Loading the Simulator State.............................................................................................. 31

Measuring Power, Voltage and Current Level in the Circuit. ...................................................... 32

Measuring the Propagation Delay................................................................................................. 34

AMS Lab Manual

2

2013 Cadence Design Systems, Inc

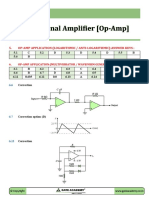

NAND Gate in AMS Flow

Schematic Capture

AMS Lab Manual

3

2013 Cadence Design Systems, Inc

Creating New Library

1. Execute Tools Library Manager in the CIW (Command Interpreter Window) to open

Library Manager.

2. In the Library Manager, execute File New Library. The new library form appears.

3. In the New Library form, type MyDesignLib in the Name section.

4. In the field of Directory section, verify that the path to the library is set to

~/Database/cadence_analog_labs_615 and click OK.

Note: New library an also be created directly from the CIW by executing File - New Library

5. A Technology File for New library form appears, select option Attach to an

existing technology library and click OK.

AMS Lab Manual

4

2013 Cadence Design Systems, Inc

Note: A technology file is not required if you are not interested to do the layouts for the design.

6. A Attach library to Technology Library form appears, select option gpdk180

from the cyclic field and click OK

7. After creating a new library we can verify it from the Library Manager

8. If we right click on the MyDesignLib and select properties, we can find that

gpdk180 library is attached as techLib to MyDesignLib.

AMS Lab Manual

5

2013 Cadence Design Systems, Inc

Verilog Entry

We create the cellviews under MyDesignLib library

Creating a New cell View

1. In the CIW or Library manager, execute File New Cellview.

2. Set up the New File window as follows:

Note: - Do not edit the Library path file and the one above might be different from the path

shown in your window.

3. Click OK when done the above settings, a vi Editor window appears.

AMS Lab Manual

6

2013 Cadence Design Systems, Inc

Verilog Design for AND Gate

1) In the vi Editor, type the design code for AND gate.

2) After completing the design, press Esc and type :wq to save the design and exit from the vi

editor.

3) After exiting from the vi Editor, a dialog window appears asking whether to create the

symbol for the design. Click Yes

Automatically the symbol for AND_Gate will be generated.

AMS Lab Manual

7

2013 Cadence Design Systems, Inc

Schematic Entry Inverter

In this section we will learn how to open new schematic window in the new MyDesignLib

library and build the inverter schematic design.

1. In the CIW or Library manager, execute File New Cellview.

2. Set up the New File window as follows:

Note: Do not edit the Library path file and the one above might be different from the path shown

in your window.

3. Click OK when done the above settings. A blank schematic window for the Inverter design

appears.

Note: Make sure the Library name is same as what we created earlier, MyDesignLib.

Adding Components to schematic

1. In the Inverter schematic window, click the Instance fixed menu icon to display the Add

Instance form.

Tip: You can also execute Create Instance or press i.

AMS Lab Manual

8

2013 Cadence Design Systems, Inc

2. Click on the Browse button. This opens up a Library browser from which you can select

components and the symbol view.

You will update the Library Name, Cell Name, and the property values given in the table on the

next page as you place each component.

AMS Lab Manual

9

2013 Cadence Design Systems, Inc

Instantiating the nmos symbol is shown below as an example

3. After you complete the Add Instance form, move your cursor to the Schematic window and

left click to place a component.

4. After entering components, click Cancel in the Add Instance form or press Esc.

This is a table of components for building the Inverter schematic.

Library name Cell Name Properties

gpdk180 pmos Total Width= 3u, Length=180n

gpdk180 nmos Total Width = 1u, Length=180n

AMS Lab Manual

10

2013 Cadence Design Systems, Inc

If you place a component with the wrong parameter values, use the Edit Properties

Objects command to change the parameters.

Use the Edit Move command if you place components in the wrong location.

You can rotate components at the time you place them, or use the Edit Rotate command after

they are placed.

Adding pins to Schematic

1. Click the Pin fixed menu icon in the schematic window.

Tip: You can also execute Create Pin or press p.

The Add pin form appears.

2. Type the following in the Add pin form in the exact order leaving space between the pin

names.

Pin Names Direction

in, Vdd, Vss input

out output

Make sure that the direction field is set to input/output/inputOutput when placing the

input/output/inout pins respectively and the Usage field is set to schematic.

AMS Lab Manual

11

2013 Cadence Design Systems, Inc

3. Select Cancel from the Add pin form after placing the pins.

In the schematic window, execute Window Fit or press f to fit all the components to the

schematic editor window.

Adding Wires to a Schematic

Add wires to connect components and pins in the design.

1. Click the Wire (narrow) icon in the schematic window.

Tip: You can also press the w key, or execute Create Wire (narrow).

2. In the schematic window, click on a pin of one of your components as the first point for your

wiring. A diamond shape appears over the starting point of this wire.

3. Follow the prompts at the bottom of the design window and left click on the destination point

for your wire. A wire is routed between the source and destination points.

4. Complete the wiring as shown in figure and when done wiring press ESC key in the schematic

window to cancel wiring.

Note: A single node cannot have more than 3 branches.

Saving the Design

1. Click the Check and Save icon in the schematic editor window.

2. Observe the CIW output area for any errors.

AMS Lab Manual

12

2013 Cadence Design Systems, Inc

Symbol Creation

Objective: To create a symbol for the Inverter

In this section, you will create a symbol for your inverter design so you can place it in a test

circuit for simulation. A symbol view is extremely important step in the design process. The

symbol view must exist for the schematic to be used in a hierarchy. In addition, the symbol has

attached properties (cdsParam) that facilitate the simulation and the design of the circuit.

1. In the Inverter schematic window, execute Create Cellview From Cellview.

The Cellview From Cellview window appears. With the Edit Options function active, you can

control the appearance of the symbol to generate.

2. Verify that the From View Name field is set to schematic, and the To View Name field is set

to symbol, with the Tool/Data Type set as schematicSymbol.

3. Click OK in the Cellview From Cellview form.

4. The Symbol Generation options window appears. Arrange the pins the way the symbol

should have them.

AMS Lab Manual

13

2013 Cadence Design Systems, Inc

5. Click OK in the Symbol Generation Options form.

6. A new window displays with an automatically created Inverter symbol as shown here.

AMS Lab Manual

14

2013 Cadence Design Systems, Inc

Editing a Symbol

In this section we will modify the inverter symbol to look like an Inverter gate symbol.

1. Move the cursor over the automatically generated symbol, until the green rectangle is

highlighted, left click to select it.

2. Click Delete icon in the symbol window, similarly select and delete the outer red rectangle.

3. Execute Create Shape polygon, and draw a shape similar to triangle.

4. After creating the triangle press Esc key.

5. Execute Create Shape Circle to make a circle at the end of triangle.

6. You can move the pin names according to the location.

7. Execute Create Selection Box. In the Add Selection Box form, click Automatic. A new red

selection box is automatically added.

8. After creating symbol, click on the save icon in the symbol editor window to save the symbol.

In the symbol editor, execute File Close to close the symbol view window.

AMS Lab Manual

15

2013 Cadence Design Systems, Inc

Schematic Entry NAND

Creating a Schematic Cellview

In this section we will open a new schematic window under MyDesignLib library and build

the inverter schematic as shown in the figure at the start of this lab.

1. In the CIW or Library manager, execute File New Cellview.

2. Set up the New File window as follows:

Note: Do not edit the Library path file and the one above might be different from the path shown

in your window.

3. Click OK when done the above settings. A blank schematic window for the NAND_Gate

design appears.

Note: Make sure the Library name is same as what we created earlier, MyDesignLib.

Adding Components to schematic

1. In the Inverter schematic window, click the Instance fixed menu icon to display the Add

Instance form.

Tip: You can also execute Create Instance or press i.

2. Click on the Browse button. This opens up a Library browser from which you can select

components and the symbol view.

AMS Lab Manual

16

2013 Cadence Design Systems, Inc

3. After you complete the Add Instance form, move your cursor to the Schematic window and

left click to place a component.

4. After entering components, click Cancel in the Add Instance form or press Esc.

To design the schematic for NAND, we require the components mentioned in the table below.

Library Name Cell Name

MyDesignLib AND_Gate

MyDesignLib Inverter

If you place a component with the wrong parameter values, use the Edit Properties

Objects command to change the parameters.

Use the Edit Move command if you place components in the wrong location.

You can rotate components at the time you place them, or use the Edit Rotate command after

they are placed.

Adding pins to Schematic

1. Click the Pin fixed menu icon in the schematic window.

Tip: You can also execute Create Pin or press p.

The Add pin form appears.

2. Type the following in the Add pin form in the exact order leaving space between the pin

names.

Pin Name Direction

A,B,Vdd,Vss input

out output

Make sure that the direction field is set to input/output/inputOutput when placing the

input/output/inout pins respectively and the Usage field is set to schematic.

AMS Lab Manual

17

2013 Cadence Design Systems, Inc

3. Select Cancel from the Add pin form after placing the pins.

In the schematic window, execute Window Fit or press f to fit all the components to the

schematic editor window.

Adding Wires to a Schematic

Add wires to connect components and pins in the design.

1. Click the Wire (narrow) icon in the schematic window.

Tip: You can also press the w key, or execute Create Wire (narrow).

2. In the schematic window, click on a pin of one of your components as the first point for your

wiring. A diamond shape appears over the starting point of this wire.

3. Follow the prompts at the bottom of the design window and left click on the destination point

for your wire. A wire is routed between the source and destination points.

4. Complete the wiring as shown in figure and when done wiring press Esc key in the schematic

window to cancel wiring.

Note: A single node cannot have more than 3 branches.

Saving the Design

1. Click the Check and Save icon in the schematic editor window.

2. Observe the CIW output area for any errors.

AMS Lab Manual

18

2013 Cadence Design Systems, Inc

Note: - By following the above procedure in AMS flow, we cant create top level symbol for the

design. To create a top level symbol for AMS design, follow the procedure mentioned below.

1) Open a new Editor (vi, gedit, nedit, gvim etc), type the verilog code and save it with .v

extension.

2) Import the verilog design to the Virtuoso Schematic Editor.

3) Automatically a symbol for the design will be created.

4) We can instantiate this symbol in the Schematic Editor of NAND_Gate, do the

connections and create a top level symbol.

AMS Lab Manual

19

2013 Cadence Design Systems, Inc

Building the Test Design

In this process we will attach the input and supply signals to the schematic design.

1. Using the component list and Properties in this table, to build the test schematic.

Library name Cellview name Properties

vpulse for A voltage1=0, voltage2=1.8,period =40n,

analogLib pulse width= 20n.

vpulse for B voltage1=0, voltage2=1.8,period =20n,

pulse width= 10n.

analogLib vdc DC voltage=1.8

analogLib gnd

2.Click on the Check and Save icon to save the design.

AMS Lab Manual

20

2013 Cadence Design Systems, Inc

Creating the Configuration View

In this section we will create a config view and with this config view we will run the

simulation.

1. In the CIW or Library Manager, execute File New Cellview.

2. In the New File form, set the following:

3. Click OK in New File form. The Hierarchy Editor form opens and a New

Configuration form opens in front of it.

AMS Lab Manual

21

2013 Cadence Design Systems, Inc

4. Click Use Template at the bottom of the New Configuration form and select AMS in the

cyclic field and click OK.

5. Change the Top Cell - View to schematic and remove the default entry from the Library List

field and Click OK in the New Configuration form.

The hierarchy editor displays the hierarchy for this design using table format.

AMS Lab Manual

22

2013 Cadence Design Systems, Inc

Note: - In the hierarchy window, if the View Found field for AND_Gate is not verilog, change to

verilog by right click on View Found field for AND_Gate and choose verilog under Set Cell

View verilog.

6. Save the current configuration and Close the Hierarchy Editor window. Execute File

Close Window.

7. From CIW, execute Tools Library Manager

AMS Lab Manual

23

2013 Cadence Design Systems, Inc

8. In the library Manager window, select the following

Library MyDesignLib

Cell NAND_Gate

Double click on config under View

9. A new Open Configuration or Top CellView form appears. Choose yes in both the cyclic

fields and click OK.

The Schematic Editor and Hierarchy Editor window appears. Notice the window banner of

schematic also states Config: MyDesignLib NAND_Gate config.

AMS Lab Manual

24

2013 Cadence Design Systems, Inc

Simulation of config View with AMS

Objective: To set up and run simulations on the NAND_Gate design

In this section, we will run the simulation for NAND_Gate and plot the Transient Analysis.

Starting the Simulation Environment

1. In the NAND_Gate schematic window, execute Launch ADE L

The Virtuoso Analog Design Environment (ADE) simulation window appears.

Choosing a Simulator

Set the environment to use the ams tool, a high speed, highly accurate mixed signal simulator.

1. In the simulation window (ADE), execute Setup Simulator/Directory/Host.

2. In the Choosing Simulator form, set the Simulator field to ams and click OK.

Setting Connect Rules

1. In the simulation window, execute Setup- Connect rules.

2. In the select connect rules window, set the Rules name field under Built-in and customized

rules to connectLib.Connrules_18V_full_fast.

AMS Lab Manual

25

2013 Cadence Design Systems, Inc

Setting the Model Libraries

The Model Library file contains the model files that describe the nmos and pmos devices during

simulation.

1. In the simulation window (ADE L), execute Setup - Model Libraries.

The Model Library Setup form appears. Click the browse button to add gpdk.scs if

not added by default as shown in the Model Library Setup form.

Remember to select the section type as stat in front of the gpdk.scs file.

The Model Library Setup window should looks like the figure below.

AMS Lab Manual

26

2013 Cadence Design Systems, Inc

To view the model file, highlight the expression in the Model Library File field and Click Edit

File.

2. To complete the Model Library Setup, move the cursor and click OK.

Choosing Analyses

This section demonstrates how to view and select the different types of analyses and to run the

simulation.

1. In the Simulation window (ADE), execute Analysis - Choose Analysis or click the

Choose - Analysis icon.

The Choosing Analysis form appears. This is a dynamic form, the bottom of the form changes

based on the selection above.

2. To setup for transient analysis

a. In the Analysis section select tran.

b. Set the stop time as 200n.

c. Click at the moderate and Enabled buttons at the bottom, and then click Apply.

AMS Lab Manual

27

2013 Cadence Design Systems, Inc

3. Click OK in the Choosing Analyses Form.

Selecting Signals for Plotting

1. Execute Outputs To be plotted Select on Schematic in the simulation window.

2. Follow the prompt at the bottom of the schematic window, Click on output net vout, input nets

vin_1 and vin_2 of the NAND_Gate. Press Esc with the cursor in the schematic after selecting

it.

After setting the transient analysis and also the signals for wave plotting, the ADE L window

will look like the figure in next page.

AMS Lab Manual

28

2013 Cadence Design Systems, Inc

Running the Simulation

1. Execute Simulation Netlist and Run in the simulation window to start the Simulation or the

Netlist and Run icon present in the ADE L window, this will create the netlist as well as

run the simulation.

2. When simulation finishes, the Transient plot automatically pops up along with log file.

3. Click on the Split Current Strip icon to separate the wave plots.

AMS Lab Manual

29

2013 Cadence Design Systems, Inc

Saving the Simulator State

We can save the simulator state, which stores information such as model library file, outputs,

analysis, variable etc. This information restores the simulation environment without having to

type in all of setting again.

1. In the Simulation window, execute Session Save State. The Saving State form appears.

2. Set the Save State Directory field to the directory in which the state should be saved. Change

the Save as field to state_ams (any valid identifier) and make sure all options are selected under

What to save field.

3. Click OK in the saving state form. The Simulator state is saved.

AMS Lab Manual

30

2013 Cadence Design Systems, Inc

Loading the Simulator State

1. From the ADE window execute Session Load State.

2. In the Loading State window, set the State name to state_ams as shown

3. Click OK in the Loading State window.

AMS Lab Manual

31

2013 Cadence Design Systems, Inc

Measuring Power, Voltage and Current Level

in the Circuit.

1. In the waveform window, execute Browse Results Open results.

2. A Select Waveform Database form appears. Double click on the psf option.

AMS Lab Manual

32

2013 Cadence Design Systems, Inc

3. A Brower form appears on left side of the waveform window. Open tranOp NAND_Gate

V2 (supply signal).

We can find the values for current, power and voltage level under signals field below

browser form.

AMS Lab Manual

33

2013 Cadence Design Systems, Inc

Measuring the Propagation Delay

1. In the waveform window execute Tools Calculator. The calculator window

appears.

2. Click on the Clear buffer icon to remove the previously calculated value from the

tool buffer.

3. From the functions select delay, this will open the delay data panel.

4. Place the cursor in the text box for Signal1, select the wave button and select the input

waveform from the waveform window.

5. Repeat the same for Signal2, and select the output waveform.

AMS Lab Manual

34

2013 Cadence Design Systems, Inc

6. Set the Threshold value 1 and Threshold value 2 to 0.9; this directs the calculator to

calculate delay at 50% i.e. at 0.9 volts.

7. Execute OK and observe the expression created in the calculator buffer.

AMS Lab Manual

35

2013 Cadence Design Systems, Inc

8. Click on Evaluate the buffer icon to perform the calculation, note down the value

returned after execution and close the window.

END OF THE LAB

AMS Lab Manual

36

2013 Cadence Design Systems, Inc

S-ar putea să vă placă și

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (587)

- EDCLABDocument80 paginiEDCLABAmbikaÎncă nu există evaluări

- Assignment - 1 Basics of VLSI: Submitted By: Name - Roll no.-M.Tech VLSI SystemsDocument5 paginiAssignment - 1 Basics of VLSI: Submitted By: Name - Roll no.-M.Tech VLSI SystemsParamesh WaranÎncă nu există evaluări

- Elec. Devices Lab Manual 2-1Document98 paginiElec. Devices Lab Manual 2-1Paramesh WaranÎncă nu există evaluări

- ELECTRONIC DEVICES AND CIRCUITS LAB MANUALDocument94 paginiELECTRONIC DEVICES AND CIRCUITS LAB MANUALvamshi krishnaÎncă nu există evaluări

- CircuitsDocument474 paginiCircuitsSriramÎncă nu există evaluări

- Op Amp Application (Logarithmic / Anti Logarithmic) Answer KeysDocument15 paginiOp Amp Application (Logarithmic / Anti Logarithmic) Answer KeysAlpha VictorÎncă nu există evaluări

- CombinationalDocument9 paginiCombinationalParamesh WaranÎncă nu există evaluări

- Monday Lab QPDocument6 paginiMonday Lab QPParamesh WaranÎncă nu există evaluări

- Digital Communications: Lab Manual (Student Copy)Document78 paginiDigital Communications: Lab Manual (Student Copy)dhileepan DilipÎncă nu există evaluări

- 1580719993php8g9tQQ PDFDocument7 pagini1580719993php8g9tQQ PDFParamesh WaranÎncă nu există evaluări

- DE Lec 33Document12 paginiDE Lec 33Paramesh WaranÎncă nu există evaluări

- DE-LEC-Boolean Algebra-1Document19 paginiDE-LEC-Boolean Algebra-1Paramesh WaranÎncă nu există evaluări

- Op-Amp - Part - 1 Answer + Correction + Sol PDFDocument21 paginiOp-Amp - Part - 1 Answer + Correction + Sol PDFHimanshu guptaÎncă nu există evaluări

- 1580719993php8g9tQQ PDFDocument7 pagini1580719993php8g9tQQ PDFParamesh WaranÎncă nu există evaluări

- 669purl EC GATE 2020 Session (02-02-20)Document33 pagini669purl EC GATE 2020 Session (02-02-20)venkatÎncă nu există evaluări

- DSP AssignmentDocument8 paginiDSP AssignmentParamesh WaranÎncă nu există evaluări

- Tancet Maths PDFDocument8 paginiTancet Maths PDFParamesh WaranÎncă nu există evaluări

- BlockDocument28 paginiBlockParamesh WaranÎncă nu există evaluări

- DFT, FFT, Filter Design and Discrete-Time Systems ProblemsDocument2 paginiDFT, FFT, Filter Design and Discrete-Time Systems ProblemsParamesh WaranÎncă nu există evaluări

- Adaptive Sampling With The Ensemble Transform KalmDocument18 paginiAdaptive Sampling With The Ensemble Transform KalmParamesh WaranÎncă nu există evaluări

- An Energy Efficient Adaptive Sampling Algorithm in A Sensor Network For Automated Water Quality MonitoringDocument14 paginiAn Energy Efficient Adaptive Sampling Algorithm in A Sensor Network For Automated Water Quality MonitoringParamesh WaranÎncă nu există evaluări

- A-High Frequency Sampling Monitoring System For Environmenal and Structural Applications PartADocument31 paginiA-High Frequency Sampling Monitoring System For Environmenal and Structural Applications PartAParamesh WaranÎncă nu există evaluări

- Indian Institute of Information Technology Tiruchirappalli Department of Electronics & Communication EngineeringDocument3 paginiIndian Institute of Information Technology Tiruchirappalli Department of Electronics & Communication EngineeringParamesh WaranÎncă nu există evaluări

- Indian Institute of Information Technology Tiruchirappalli Department of Electronics & Communication EngineeringDocument2 paginiIndian Institute of Information Technology Tiruchirappalli Department of Electronics & Communication EngineeringParamesh WaranÎncă nu există evaluări

- DSPWCDocument2 paginiDSPWCParamesh WaranÎncă nu există evaluări

- DSP AssignmentDocument2 paginiDSP AssignmentParamesh WaranÎncă nu există evaluări

- PassDocument1 paginăPassParamesh WaranÎncă nu există evaluări

- Multi RateDocument4 paginiMulti RateParamesh WaranÎncă nu există evaluări

- DSP QPDocument54 paginiDSP QPParamesh WaranÎncă nu există evaluări

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (894)

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (399)

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (73)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5794)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2219)

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (344)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (265)

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (119)

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)

- Week 3 SEED in Role ActivityDocument2 paginiWeek 3 SEED in Role ActivityPrince DenhaagÎncă nu există evaluări

- Supplier Quality Requirement Form (SSQRF) : Inspection NotificationDocument1 paginăSupplier Quality Requirement Form (SSQRF) : Inspection Notificationsonnu151Încă nu există evaluări

- Understanding CTS Log MessagesDocument63 paginiUnderstanding CTS Log MessagesStudentÎncă nu există evaluări

- Bernardo Corporation Statement of Financial Position As of Year 2019 AssetsDocument3 paginiBernardo Corporation Statement of Financial Position As of Year 2019 AssetsJean Marie DelgadoÎncă nu există evaluări

- Overall Dimensions and Mounting: Solar Water Pump Controller Mu - G3 Solar Mu - G5 Solar Mu - G7.5 Solar Mu - G10 SolarDocument2 paginiOverall Dimensions and Mounting: Solar Water Pump Controller Mu - G3 Solar Mu - G5 Solar Mu - G7.5 Solar Mu - G10 SolarVishak ThebossÎncă nu există evaluări

- ABBBADocument151 paginiABBBAJeremy MaraveÎncă nu există evaluări

- Keya PandeyDocument15 paginiKeya Pandeykeya pandeyÎncă nu există evaluări

- Conplast SP430 0407Document4 paginiConplast SP430 0407Harz IndÎncă nu există evaluări

- Case Study - Soren ChemicalDocument3 paginiCase Study - Soren ChemicalSallySakhvadzeÎncă nu există evaluări

- Top Brand Story Bar Supervisor Jobs Chennai Apply Now Latest Fresher Experienced Bar Supervisor Jobs in Various Location July 18 2021Document1 paginăTop Brand Story Bar Supervisor Jobs Chennai Apply Now Latest Fresher Experienced Bar Supervisor Jobs in Various Location July 18 2021Surya JamesÎncă nu există evaluări

- COVID-19's Impact on Business PresentationsDocument2 paginiCOVID-19's Impact on Business PresentationsRetmo NandoÎncă nu există evaluări

- Tyron Butson (Order #37627400)Document74 paginiTyron Butson (Order #37627400)tyron100% (2)

- ECON Value of The FirmDocument4 paginiECON Value of The FirmDomsÎncă nu există evaluări

- Teleprotection Terminal InterfaceDocument6 paginiTeleprotection Terminal InterfaceHemanth Kumar MahadevaÎncă nu există evaluări

- Digital Booklet - Bach ConcertosDocument14 paginiDigital Booklet - Bach Concertosppopgod33% (3)

- The SAGE Handbook of Digital JournalismDocument497 paginiThe SAGE Handbook of Digital JournalismK JÎncă nu există evaluări

- Computers As Components 2nd Edi - Wayne WolfDocument815 paginiComputers As Components 2nd Edi - Wayne WolfShubham RajÎncă nu există evaluări

- EWAIRDocument1 paginăEWAIRKissy AndarzaÎncă nu există evaluări

- Academy Broadcasting Services Managerial MapDocument1 paginăAcademy Broadcasting Services Managerial MapAnthony WinklesonÎncă nu există evaluări

- Railway RRB Group D Book PDFDocument368 paginiRailway RRB Group D Book PDFAshish mishraÎncă nu există evaluări

- E2 PTAct 9 7 1 DirectionsDocument4 paginiE2 PTAct 9 7 1 DirectionsEmzy SorianoÎncă nu există evaluări

- Complaint Handling Policy and ProceduresDocument2 paginiComplaint Handling Policy and Proceduresjyoti singhÎncă nu există evaluări

- Pyrometallurgical Refining of Copper in An Anode Furnace: January 2005Document13 paginiPyrometallurgical Refining of Copper in An Anode Furnace: January 2005maxi roaÎncă nu există evaluări

- Mayor Byron Brown's 2019 State of The City SpeechDocument19 paginiMayor Byron Brown's 2019 State of The City SpeechMichael McAndrewÎncă nu există evaluări

- (SIRI Assessor Training) AM Guide Book - v2Document19 pagini(SIRI Assessor Training) AM Guide Book - v2hadeelÎncă nu există evaluări

- Quezon City Department of The Building OfficialDocument2 paginiQuezon City Department of The Building OfficialBrightNotes86% (7)

- Circular 09/2014 (ISM) : SubjectDocument7 paginiCircular 09/2014 (ISM) : SubjectDenise AhrendÎncă nu există evaluări

- 2.8 V6 5V (Aha & Atq)Document200 pagini2.8 V6 5V (Aha & Atq)Vladimir Socin ShakhbazyanÎncă nu există evaluări

- C79 Service Kit and Parts List GuideDocument32 paginiC79 Service Kit and Parts List Guiderobert100% (2)

- Resume Ajeet KumarDocument2 paginiResume Ajeet KumarEr Suraj KumarÎncă nu există evaluări