Documente Academic

Documente Profesional

Documente Cultură

Teoria Biestabilidad

Încărcat de

Manuel AbrahamDescriere originală:

Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Teoria Biestabilidad

Încărcat de

Manuel AbrahamDrepturi de autor:

Formate disponibile

Introduccin al biestable RS con compuertas

NOR y NAND

En el curso EloTrain 6 de "Biestables RS-NOR y RS-NAND" se transmiten

los conocimientos fundamentales acerca de estos componentes.

Biestables

Se conoce como biestable o flip flop al circuito electrnico que tiene dos posibles

estados elctricos de carcter estable y en el que se puede pasar del uno al otro

aplicando las correspondientes seales de entrada. Los distintos tipos de biestables

se controlan de distintas maneras, sus entradas operan de forma diferente y cambian

de estado solamente si se cumplen determinadas condiciones establecidas.

Un biestable mantiene el estado de salida incluso en ausencia de seales de

entrada.

Por tanto, estos componentes se prestan para conformar las memorias de trabajo

(RAM) de los sistemas de computacin.

El biestable ms sencillo consta de dos puertas NOR con realimentacin.

Posee una entrada de activacin (S de "set" en ingls) y otra de reset (R).

Este biestable RS (as denominado por las palabras "reset y set") es un componente

asncrono.

Existen diferentes tipos de biestables:

Biestable de control de estado:

Un biestable de control de estado es aquel cuya activacin y reset solo tiene efecto si

se aade una seal de reloj suplementaria en la entrada.

Al biestable RS se le agrega una entrada de reloj

C1.

Biestable con control por flanco nico:

Un biestable controlado por un solo flanco es aquel cuya entrada de activacin y

reset solamente vara durante el cambio del estado de la seal de reloj.

El control por flanco de reloj se muestra en el

smbolo grfico mediante un tringulo.

Ventaja del control por flanco:

La propensin a la interferencia de seales se

reduce

mediante el breve tiempo que dura el flanco de

reloj.

Biestable con control de dos flancos:

Un control mediante dos flancos en un biestable registra los estados de la entrada

durante un flanco de reloj y los entrega a la salida tras el siguiente flanco.

El control mediante dos flancos reduce

claramente ms la propensin a las seales de

interferencia.

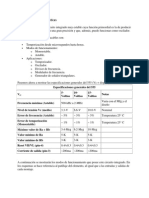

Contenidos de aprendizaje

Una vez realizado el ejercicio, los estudiantes estarn en condiciones de:

Montar un biestable RS con compuertas NOR y NAND.

Determinar la respuesta de un biestable RS y representarla en una tabla de

verdad.

Describir el funcionamiento general de un biestable RS.

Emplear los trminos "guardar/retener", "activar" y "resetear" para la

identificacin de las fases de un proceso informtico y asignarlos a las

correspondientes asignaciones de entradas.

Reconocer que si se estimulan las entradas de activacin y reset al mismo

tiempo se provoca en la salida un estado lgico indeterminado o irregular.

Requisitos

Para un exitoso trabajo con el curso se requiere:

Elaborar tablas de verdad.

Conocimientos de circuitos bsicos.

S-ar putea să vă placă și

- Ejercicios prácticos con Electrónica: Proyectos de electrónica con Arduino y Raspberry PiDe la EverandEjercicios prácticos con Electrónica: Proyectos de electrónica con Arduino y Raspberry PiEvaluare: 5 din 5 stele5/5 (1)

- Logica Secuencial 2020Document37 paginiLogica Secuencial 2020Diego V-aÎncă nu există evaluări

- BiestableDocument8 paginiBiestableObeth Ortiz SedeñoÎncă nu există evaluări

- Programacion de PLCDocument57 paginiProgramacion de PLCAle KeyÎncă nu există evaluări

- Familias de MicrocontroladoresDocument11 paginiFamilias de MicrocontroladoresfranciscoÎncă nu există evaluări

- Lab 02 Motor - MonofásicoDocument25 paginiLab 02 Motor - MonofásicoManuel AbrahamÎncă nu există evaluări

- Lab 01 Fundamentos de MediciónDocument21 paginiLab 01 Fundamentos de MediciónManuel Abraham100% (1)

- Flip FlopDocument23 paginiFlip FlopJoseph JesusÎncă nu există evaluări

- UT 03 Analisis de Circuitos Secuenciales by FranDocument11 paginiUT 03 Analisis de Circuitos Secuenciales by FranFrancisco BaenaÎncă nu există evaluări

- MULTIVIBRADORESDocument20 paginiMULTIVIBRADORESRicardo TorresÎncă nu există evaluări

- Flip FlopsDocument7 paginiFlip FlopsJuan LainaÎncă nu există evaluări

- Sistemas Eléctricos y Electrónicos Tarea 2Document11 paginiSistemas Eléctricos y Electrónicos Tarea 2Cristian LopezÎncă nu există evaluări

- Laboratorio 04 BiestablesDocument26 paginiLaboratorio 04 BiestablesJorddy Peralta IruriÎncă nu există evaluări

- Previo 7 MedicionDocument13 paginiPrevio 7 MedicionLeslie Vp67% (3)

- 1 Latchs FlipFlopsDocument46 pagini1 Latchs FlipFlopsJavier Negrette100% (1)

- El Circuito Integrado 555Document2 paginiEl Circuito Integrado 555Julio Fernando Antezana HinojosaÎncă nu există evaluări

- Sistema Lógico Secuencial Asincrónico y SincrónicoDocument38 paginiSistema Lógico Secuencial Asincrónico y SincrónicoNemessis Pacheco100% (1)

- Previo N°1 Digitales IiDocument15 paginiPrevio N°1 Digitales IiMervin TCÎncă nu există evaluări

- Implementación de un multivibrador astable con flip flopsDocument18 paginiImplementación de un multivibrador astable con flip flopscesarÎncă nu există evaluări

- Sistemas Electricos y ElectronicosDocument7 paginiSistemas Electricos y ElectronicosCristian LopezÎncă nu există evaluări

- FLIP FlopsDocument9 paginiFLIP FlopsDelfino OlivaresÎncă nu există evaluări

- Clase7 - Circuitos Secuenciales IntroduccionDocument9 paginiClase7 - Circuitos Secuenciales IntroduccionvalentinapetitereuÎncă nu există evaluări

- Biestable - Wikipedia, La Enciclopedia LibreDocument38 paginiBiestable - Wikipedia, La Enciclopedia LibreDIEGO ARON MILLAN COLQUEÎncă nu există evaluări

- Informe Previo 1Document19 paginiInforme Previo 1Pamela KarenÎncă nu există evaluări

- 2 Logica SecuencialDocument6 pagini2 Logica SecuencialJosue ChavarriaÎncă nu există evaluări

- FLIP FLOP Marco Teorico + 2pregDocument17 paginiFLIP FLOP Marco Teorico + 2pregrobertitoÎncă nu există evaluări

- Laboratorio Latch Flip Flops MAEFNDocument28 paginiLaboratorio Latch Flip Flops MAEFNItaloCardenasÎncă nu există evaluări

- PrevioDocument16 paginiPrevioFranck JonhsonÎncă nu există evaluări

- Bies TableDocument37 paginiBies TableLuz Karina Lopez SaavedraÎncă nu există evaluări

- Registro de DesplazamientoDocument6 paginiRegistro de DesplazamientojosegrabandoÎncă nu există evaluări

- Cto. SecuencialDocument32 paginiCto. SecuencialAlonso HernándezÎncă nu există evaluări

- ¿Qué Es Un Flip Flop?Document6 pagini¿Qué Es Un Flip Flop?OLIVER ALVARADO MART�NEZÎncă nu există evaluări

- Multivibrador Biestable CircuitosDocument14 paginiMultivibrador Biestable CircuitosMario GonzalesÎncă nu există evaluări

- Bie StablesDocument18 paginiBie Stableslady67lauraÎncă nu există evaluări

- Latch Flip FlopDocument6 paginiLatch Flip FlopRICHARD DÍAZ YGNACIOÎncă nu există evaluări

- CircuitosSecuencialesDocument11 paginiCircuitosSecuencialesJesusÎncă nu există evaluări

- Registros FinalDocument8 paginiRegistros Finalceleste claroÎncă nu există evaluări

- Flip FlopDocument6 paginiFlip FlopJesus VelasquezÎncă nu există evaluări

- Biestables Asincronos y SincronosDocument13 paginiBiestables Asincronos y SincronosOmar Ruiz Rodríguez80% (5)

- Sesion 12 LSCDocument6 paginiSesion 12 LSCYonder SalazarÎncă nu există evaluări

- Informe Previo N°1Document15 paginiInforme Previo N°1hhenrirÎncă nu există evaluări

- Tema5 Circuitos BiestablesDocument31 paginiTema5 Circuitos BiestablesbriceriveÎncă nu există evaluări

- Flip FlopDocument12 paginiFlip FlopEmilys QuijadaÎncă nu există evaluări

- Control y Programación de Sistemas AutomáticosDocument14 paginiControl y Programación de Sistemas AutomáticosMartin Viruel DzibÎncă nu există evaluări

- Digital II Biestables PDFDocument16 paginiDigital II Biestables PDFMauricio CaballeroÎncă nu există evaluări

- Iesnumero 1 RibeiraDocument4 paginiIesnumero 1 RibeiraFernando Sobrino-Manzanares MasÎncă nu există evaluări

- Tipos de Biestables: RS, D, T, JK y sus Tablas de VerdadDocument7 paginiTipos de Biestables: RS, D, T, JK y sus Tablas de VerdadYefer Solis MazaÎncă nu există evaluări

- Funcionamiento del flip-flop RS implementado con compuertas NOR y NANDDocument5 paginiFuncionamiento del flip-flop RS implementado con compuertas NOR y NANDChristian Aros Bobadilla100% (1)

- Guia de Laboratorio 02 Circ DigitalesDocument66 paginiGuia de Laboratorio 02 Circ DigitalesrenatohurtadoÎncă nu există evaluări

- Circuitos secuenciales básicosDocument18 paginiCircuitos secuenciales básicosvaleria LopezÎncă nu există evaluări

- Circuito Conversor de Digital A Análogo (Contador + Sumador) "Document12 paginiCircuito Conversor de Digital A Análogo (Contador + Sumador) "Luis ChasiluisaÎncă nu există evaluări

- cd2 Final1Document8 paginicd2 Final1Eleazar CastilloÎncă nu există evaluări

- 555 circuito temporizadorDocument4 pagini555 circuito temporizadorGym Centro Masaje EsperanzaÎncă nu există evaluări

- Cuestionarios Resueltos 2019Document3 paginiCuestionarios Resueltos 2019Vanina Maria Ayala MarecoÎncă nu există evaluări

- BiestableDocument3 paginiBiestableAlejandra VasquezÎncă nu există evaluări

- Biestable JKDocument7 paginiBiestable JKMelina MoncayoÎncă nu există evaluări

- Logica SecuencialDocument9 paginiLogica SecuencialBruno Hernández MartínezÎncă nu există evaluări

- Circuitos Logicos SecuencialesDocument6 paginiCircuitos Logicos SecuencialescesarÎncă nu există evaluări

- Informe Proyecto - Reloj BinarioDocument10 paginiInforme Proyecto - Reloj BinarioAlex TipantuñaÎncă nu există evaluări

- Multivibradores y Temporizadores 333Document11 paginiMultivibradores y Temporizadores 333Pablo CancinoÎncă nu există evaluări

- Informe 7 Aulestia PabloDocument5 paginiInforme 7 Aulestia PabloSHADOWFREE8000Încă nu există evaluări

- Laboratorio 1 Cirucitos DgitalesDocument30 paginiLaboratorio 1 Cirucitos DgitalesIan JosephÎncă nu există evaluări

- Laboratorio 11 Valvula de DiafragmaDocument14 paginiLaboratorio 11 Valvula de DiafragmaManuel AbrahamÎncă nu există evaluări

- Laboratorio 11 Valvula de DiafragmaDocument14 paginiLaboratorio 11 Valvula de DiafragmaManuel AbrahamÎncă nu există evaluări

- Informe de LaboratorioDocument13 paginiInforme de LaboratorioManuel AbrahamÎncă nu există evaluări

- Informe de Seleccion de MotoresDocument18 paginiInforme de Seleccion de MotoresManuel AbrahamÎncă nu există evaluări

- S03 - Seminario Diodos - 2016Document33 paginiS03 - Seminario Diodos - 2016juanÎncă nu există evaluări

- Laboratorio 2Document9 paginiLaboratorio 2roxanaÎncă nu există evaluări

- Fuentes de Alimentación ReguladaDocument28 paginiFuentes de Alimentación ReguladaManuel AbrahamÎncă nu există evaluări

- Variadores de VelocidadDocument35 paginiVariadores de VelocidadManuel AbrahamÎncă nu există evaluări

- Selección de Conductores Desde El Punto de Vista EconómicoDocument22 paginiSelección de Conductores Desde El Punto de Vista EconómicoManuel AbrahamÎncă nu există evaluări

- FILTROSDocument28 paginiFILTROSManuel AbrahamÎncă nu există evaluări

- Informe de Laboratorio 3Document14 paginiInforme de Laboratorio 3Manuel AbrahamÎncă nu există evaluări

- Transistor BJT EjerciciosDocument21 paginiTransistor BJT EjerciciosManuel AbrahamÎncă nu există evaluări

- Sociedad y Desarrollo SDS VIDocument18 paginiSociedad y Desarrollo SDS VIManuel AbrahamÎncă nu există evaluări

- Buscadores en InternetDocument1 paginăBuscadores en InternetManuel AbrahamÎncă nu există evaluări

- Informe de Estatica 1Document33 paginiInforme de Estatica 1Manuel AbrahamÎncă nu există evaluări

- Texto5 Geo PDFDocument23 paginiTexto5 Geo PDFManuel AbrahamÎncă nu există evaluări

- Buscadores en InternetDocument1 paginăBuscadores en InternetManuel AbrahamÎncă nu există evaluări

- Lab 01 InformeDocument18 paginiLab 01 InformeManuel AbrahamÎncă nu există evaluări

- Comparadores y LimitesDocument32 paginiComparadores y LimitesManuel AbrahamÎncă nu există evaluări

- Lab 05 - Mandos en Función Al DesplazamientoDocument11 paginiLab 05 - Mandos en Función Al DesplazamientoManuel AbrahamÎncă nu există evaluări

- Circuitos TrifásicosDocument42 paginiCircuitos TrifásicosManuel AbrahamÎncă nu există evaluări

- Dibujo Tecnico ComputarizadoDocument12 paginiDibujo Tecnico ComputarizadoManuel AbrahamÎncă nu există evaluări

- Método Del Ranking de Factores Ponderados PDFDocument5 paginiMétodo Del Ranking de Factores Ponderados PDFManuel AbrahamÎncă nu există evaluări

- Calidad de La EnergíaDocument60 paginiCalidad de La EnergíaManuel AbrahamÎncă nu există evaluări

- Trabajo de Investigación Calculo 1 ProdasDocument4 paginiTrabajo de Investigación Calculo 1 ProdasManuel AbrahamÎncă nu există evaluări

- InformeDocument16 paginiInformeManuel AbrahamÎncă nu există evaluări

- Informe de BobinadosDocument8 paginiInforme de BobinadosManuel AbrahamÎncă nu există evaluări

- Impresión 3D - Información PDFDocument17 paginiImpresión 3D - Información PDFManuel AbrahamÎncă nu există evaluări

- Archivetemppreinforme 4Document10 paginiArchivetemppreinforme 4Jean Carlos MedinaÎncă nu există evaluări

- 82 - Diseño de ContadoresDocument14 pagini82 - Diseño de ContadoresDarwin.pilloÎncă nu există evaluări

- CIrcuitos DigitalesTrabajo N02Document5 paginiCIrcuitos DigitalesTrabajo N02VR CinthiaÎncă nu există evaluări

- Tarea 2 - Freylis Rivera - 31Document18 paginiTarea 2 - Freylis Rivera - 31andresÎncă nu există evaluări

- Sumador de Dos Números Binarios de 2 BitsDocument6 paginiSumador de Dos Números Binarios de 2 BitsAfir MinayaÎncă nu există evaluări

- Arquitectura de Computadoras y Microprocesadores 8085-8086, I3, I5, I7, I9 y PeriféricosDocument83 paginiArquitectura de Computadoras y Microprocesadores 8085-8086, I3, I5, I7, I9 y PeriféricoseliasÎncă nu există evaluări

- Lab N°1 Fpga Spartan2 V4Document27 paginiLab N°1 Fpga Spartan2 V4Diego Fernando Ramirez MuñozÎncă nu există evaluări

- Tema IDocument14 paginiTema IBeatriz Márquez BalderasÎncă nu există evaluări

- RTL, DTL, I2lDocument6 paginiRTL, DTL, I2lJose GaliciaÎncă nu există evaluări

- Interfaces - OperacionalesDocument11 paginiInterfaces - OperacionalesFranco RibaÎncă nu există evaluări

- Cap 5Document77 paginiCap 5Red Ingenieros Mecánicos Electromecánicos0% (1)

- Lab FuncionalesDocument10 paginiLab FuncionalesRonaldo0% (1)

- FPGA Cyclone II GuíaDocument32 paginiFPGA Cyclone II GuíaPedro LandaetaÎncă nu există evaluări

- Práctica 2Document4 paginiPráctica 2julieta pulidoÎncă nu există evaluări

- MicroDocument2 paginiMicroAlexander SantanderÎncă nu există evaluări

- ALTIUMDocument5 paginiALTIUMSergio VeraÎncă nu există evaluări

- MultivibradoresDocument9 paginiMultivibradoresRyofenixÎncă nu există evaluări

- 9 Diseño de Sistemas Secuenciales TeamsDocument35 pagini9 Diseño de Sistemas Secuenciales TeamsPaola de LeonÎncă nu există evaluări

- Mercado de Los MicrocontroladoresDocument22 paginiMercado de Los MicrocontroladoresJuan Camilo Naranjo0% (1)

- Circuitos Combinacionales VHDLDocument20 paginiCircuitos Combinacionales VHDLNick CohechaÎncă nu există evaluări

- Informe 3 MsiDocument18 paginiInforme 3 MsiAnthony CardenasÎncă nu există evaluări

- Microcontroladores Mapa MentalDocument1 paginăMicrocontroladores Mapa Mentalemilio estebanÎncă nu există evaluări

- Tipos de MemoriaDocument8 paginiTipos de MemoriaDanny PalaciosÎncă nu există evaluări

- Prácticas para El Laboratorio de Diseño Lógico 2015.......Document52 paginiPrácticas para El Laboratorio de Diseño Lógico 2015.......mOB&mOBÎncă nu există evaluări

- Evaluacion 3ºDocument3 paginiEvaluacion 3ºFlor Stella Martinez Heredia100% (2)

- Laboratorio 2 - Logica Digital - Giovanny Varón - Estefania MontoyaDocument8 paginiLaboratorio 2 - Logica Digital - Giovanny Varón - Estefania MontoyaGiovanny VarónÎncă nu există evaluări

- Analisis+del+transistor+bjt+en+ca Elizabeth+aDocument10 paginiAnalisis+del+transistor+bjt+en+ca Elizabeth+aJohnÎncă nu există evaluări

- Practica 8G2 Contador Sincrono FlipFlop DLDocument4 paginiPractica 8G2 Contador Sincrono FlipFlop DLAlexander Robles CaicedoÎncă nu există evaluări

- Trabajo FinalDocument15 paginiTrabajo FinalasdÎncă nu există evaluări