Documente Academic

Documente Profesional

Documente Cultură

Di22 HP 70 W 19 V External Laptop Adapter Schematic Diagram

Încărcat de

Tonpitonpi Ton PiTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Di22 HP 70 W 19 V External Laptop Adapter Schematic Diagram

Încărcat de

Tonpitonpi Ton PiDrepturi de autor:

Formate disponibile

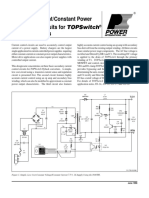

DI-22 Design Idea

TOPSwitch-GX

70 W, 19 V External Laptop Adapter

Application Device Power Output Input Voltage Output Voltage Topology

Laptop Adapter TOP249YN 70 W 85 265 VAC 19 V Flyback

Design Highlights eliminates power-up/down glitches and overvoltage provides line

High efciency: 84% at 85 VAC (with 50 C external ambient transient and long duration power system surge protection.

temperature) Resistor R10 programs the internal current limit to 75% of nominal

Low component count and high power density, 7 W/in.3 at the UV threshold. As a function of input voltage the current limit

Very compact design (4.1 in. 2.225 in. 1.06 in.) is further reduced by R9 to provide approximately constant

No surface mount components required overload power. The larger TOPSwitch-GX selection reduces con-

Low zero load power consumption, <370 mW at 115 VAC duction losses, raising efciency (without circuit changes or

Approximately constant overload power with line voltage increased overload power) and permits a higher inductance

Line undervoltage detection (UV) and overvoltage (OV) shut- design for reduced primary RMS currents, further increasing

down efciency.

Low EMI - switching frequency jitter helps meet CISPR22B/

EN55022B limits To reduce winding and diode dissipation the secondary is split into

Fully protected for overload, short circuit and thermal faults two windings and diode ORed into the output capacitors (C2, 3).

Regulation is provided by a secondary side reference (U3), the

Operation output voltage sensed by R4, R13 and R6.

The design utilizes a TOP249YN in a yback converter providing a

70 W output in a sealed enclosure at an external ambient of

50 C. Line UV and OV (100 V and 450 V, respectively) are

implemented using a single 2 M resistor (R1). Undervoltage

C7

2.2 nF D2

C13 C12 C11 MBR20100

0.33 MF 0.022 MF 0.01 MF

400 V 400 V 400 V Y1 Safety

1 2

VR1 D3

9 MBR20100

P6KE-

200 C3 C14

2 820 MF L1 0.1 MF

BR1 25 V 200 MH 50 V 19 V, 3.6 A

RS805 D1

8 A 600 V UF4006 11

3 8 RTN

C2 C4

820 MF R1 820 MF

D4 25 V 25 V

1N4148 270 7

L2 R11

820 MH 2 M7 R4

2A 6 U2 31.6 k7

1/2 W R8 PC817A

4.7 7 1%

C1 T1 5

150 MF R2

C15 1 k7 R13

400 V 1 MF

C6 TOPSwitch-GX 562 7

0.1 MF D L 50 V C9 1%

U1

X2 L3 TOP249YN 4.7 nF 50 V

CONTROL

RT1 75 MH R9 C

10 7 to 2A 13 M7

1.7 A C10

R3 R7 0.1 MF

S X F 6.8 7 50 V

F1 56 k7

3.15 A C8 U3

R10 TL431

20.5 k7 0.1 MF R6

50 V C5 4.75 k7

85 - 265 47 MF 1%

VAC 16 V

PI-2691-100608

Figure 1. TOPSwitch-GX 70 W Laptop Adapter Schematic.

www.powerint.com October 2008

Key Design Points

Transformer Parameters

D1 and VR1 clamp leakage inductance spikes. A Zener clamp

provides lower zero load consumption than an RCD clamp and FPQ26/20-A TDK PC40, gapped for ALG

Core Material

higher efciency below full load. of 843 nH/t

C11 reduces VR1 dissipation, raising efciency.

Bobbin TDK BPQ26/20-1112CP

Additional differential ltering is provided by C13 and L3.

C12 provides high frequency bypass, reducing high frequency

Primary: 9T + 9T, 2 26 AWG

Shield: 1T, 8 mm 0.015 mm Cu foil

EMI.

Winding Details Secondary 1: 3T, 3 26 AWG T.I.W.

Use foil windings to reduce dissipation and reduce leakage

Secondary 2: 3T, 3 26 AWG T.I.W.

inductance. Bias: 2T, 8 mm 0.015 mm Cu foil

Sandwich secondary winding between two halves of primary to

reduce leakage inductance. Primary (21), Shield (1NC), Tape,

Winding Order Secondary 1 (129), Secondary 2 (118),

High core temperature reduces saturation ux density. Keep (pin numbers)

Bias (65), Tape, Primary (32), Tape

ux density below 3000 gauss (0.3 T) to prevent saturation.

Use 100 V Schottky diodes for highest efciency. Primary: 273 H, 10%

Inductance

Good layout practices should be followed: Leakage: 3 H (maximum)

Locate C8, R3, C5, R9, R10 and R11 close to U1. Primary Resonant 1.5 MHz (minimum)

Power and signal source currents should be separated,

Frequency

joined using a Kelvin connection at the SOURCE pin. Table 1. Transformer Parameters. (AWG = American Wire Gauge,

T.I.W. = Triple Insulated Wire, NC = No Connection)

Minimize the primary and secondary loop areas to reduce

parasitic leakage and EMI.

Consult DAK-11 and EPR-11 for more information.

Power Integrations Power Integrations reserves the right to make changes to its products at any time to improve reliability or manufacturability. Power

5245 Hellyer Avenue Integrations does not assume any liability arising from the use of any device or circuit described herein. POWER INTEGRATIONS

San Jose, CA 95138, USA. MAKES NO WARRANTY HEREIN AND SPECIFICALLY DISCLAIMS ALL WARRANTIES INCLUDING, WITHOUT LIMITATION, THE IMPLIED

Main: +1 408-414-9200 WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF THIRD PARTY RIGHTS.

Customer Service The products and applications illustrated herein (transformer construction and circuits external to the products) may be covered by

Phone: +1-408-414-9665 one or more U.S. and foreign patents or potentially by pending U.S. and foreign patent applications assigned to Power Integrations.

Fax: +1-408-414-9765 A complete list of Power Integrations' patents may be found at www.powerint.com. Power Integrations grants

Email: usasales@powerint.com its customers a license under certain patent rights as set forth at http://www.powerint.com/ip.htm.

The PI logo, TOPSwitch, TinySwitch, LinkSwitch, DPA-Switch, PeakSwitch, EcoSmart, Clampless, E-Shield, Filterfuse, StackFET,

On the Web PI Expert and PI FACTS are trademarks of Power Integrations, Inc. Other trademarks are property of their respective companies.

www.powerint.com 2002, Power Integrations, Inc.

B

10/08 DI-22

S-ar putea să vă placă și

- Reference Design-6 STR-W6756 Universal-Input 140 W Power SupplyDocument2 paginiReference Design-6 STR-W6756 Universal-Input 140 W Power SupplyShamol KormokerÎncă nu există evaluări

- 10A 70V SMPS For Power Amplifier - Electronic CircuitDocument2 pagini10A 70V SMPS For Power Amplifier - Electronic CircuitK Raja SekarÎncă nu există evaluări

- Hakko936 150812042846 Lva1 App6891 PDFDocument14 paginiHakko936 150812042846 Lva1 App6891 PDFLeoned Cova OrozcoÎncă nu există evaluări

- Series: Ultra Light Load High Efficiency, VIN 17V, Current Mode Step-Down Io 3A Buck Regulator ICDocument15 paginiSeries: Ultra Light Load High Efficiency, VIN 17V, Current Mode Step-Down Io 3A Buck Regulator ICCube7 GeronimoÎncă nu există evaluări

- EasyArc Zx7-200 Igbt Inverter WelderDocument1 paginăEasyArc Zx7-200 Igbt Inverter WelderSandeep Kumar67% (12)

- Samsung Plasma Training ManualDocument57 paginiSamsung Plasma Training ManualevaristoÎncă nu există evaluări

- LG Mdd104k (Mds104v)Document59 paginiLG Mdd104k (Mds104v)boroda241082% (11)

- Disable Protection of The Inverter-3Document19 paginiDisable Protection of The Inverter-3fox787880% (44)

- Panasonic TH l24c20dDocument39 paginiPanasonic TH l24c20dKingsleen33% (3)

- Elenos Hf1000 1000w Power AmplifierDocument63 paginiElenos Hf1000 1000w Power AmplifierΔημήτρης Χατζηβασιλείου100% (3)

- Details PDF: Image Part Number Description Manufacturer QuantityDocument1 paginăDetails PDF: Image Part Number Description Manufacturer QuantityLautiSenn100% (5)

- Inverter ADocument46 paginiInverter AGustavoLopezGuardadoÎncă nu există evaluări

- 5L0380R CircuitDocument1 pagină5L0380R CircuitMahmoud Digital-Digital100% (5)

- uP9011Q DS F0000Document15 paginiuP9011Q DS F0000Blue StacksÎncă nu există evaluări

- Mini Hi-Fi System: Service ManualDocument85 paginiMini Hi-Fi System: Service ManualIvanilto Martins da Cruz100% (3)

- High Quality Tone Control Circuit by Transistor Low NoiseDocument17 paginiHigh Quality Tone Control Circuit by Transistor Low NoiseJavier Güerino Palacios100% (1)

- BN44 00851a+l40msf FHSDocument2 paginiBN44 00851a+l40msf FHSLuiz Roberto Honório Alves Filho100% (2)

- Repairing & Testing YSUS & Buffers For Samsung 50" Plasma PS50Q96HD PS50Q97HDDocument5 paginiRepairing & Testing YSUS & Buffers For Samsung 50" Plasma PS50Q96HD PS50Q97HDEhduard Vehov75% (4)

- HDVX9 As V59 V4 - 1 SpecificationDocument12 paginiHDVX9 As V59 V4 - 1 SpecificationAnonymous L8SBZMyw88% (8)

- Samsung UA32N4300AK Chassis UAV81Document55 paginiSamsung UA32N4300AK Chassis UAV81Francisco NavarroÎncă nu există evaluări

- Acer Veriton Z291G Emachines EZ1711 Wistron Pi010L 09194 1 E VMARR PDFDocument31 paginiAcer Veriton Z291G Emachines EZ1711 Wistron Pi010L 09194 1 E VMARR PDFSebastian Matias100% (1)

- HV320WX2-176-BOE LCD PanelDocument23 paginiHV320WX2-176-BOE LCD PanelEdwin OndoyÎncă nu există evaluări

- Panasonic Th-l32c30d Chassis Km10Document107 paginiPanasonic Th-l32c30d Chassis Km10Subhash.2084 S0% (1)

- Another 6 Pin SMD IC in LED & LCD TV/Monitor: Home Articles Download Page Recommend Contact UsDocument10 paginiAnother 6 Pin SMD IC in LED & LCD TV/Monitor: Home Articles Download Page Recommend Contact UsHaze Garcia HechanovaÎncă nu există evaluări

- Akai 21CTU91BC CRT TV SM PDFDocument27 paginiAkai 21CTU91BC CRT TV SM PDFAllah RakhaÎncă nu există evaluări

- L32S & L40S Service ManualDocument39 paginiL32S & L40S Service ManualClubedoTecnico100% (2)

- Analog Soldering Station Schematic PDFDocument1 paginăAnalog Soldering Station Schematic PDFMladen PorubovicÎncă nu există evaluări

- MIXER 6+ Channel in EnglishDocument8 paginiMIXER 6+ Channel in EnglishjedrespoÎncă nu există evaluări

- Analog Soldering Station SchematicDocument1 paginăAnalog Soldering Station Schematiczoran_stev86% (7)

- TP - MS358.PB802 A Schematic DiagramDocument13 paginiTP - MS358.PB802 A Schematic DiagramMunhuu Tumee63% (8)

- STK StrbookDocument31 paginiSTK StrbookJuan Coronel57% (14)

- 300VA Power Inverter SchematicDocument1 pagină300VA Power Inverter SchematicArturo Gómez100% (1)

- GM328A User ManualDocument3 paginiGM328A User ManualRosu Eugen100% (1)

- Digital Soldering Station Atmega8 Schematic PDFDocument1 paginăDigital Soldering Station Atmega8 Schematic PDFzoran_stev75% (4)

- Power Amplifier With Lm1875 and Ne5532Document7 paginiPower Amplifier With Lm1875 and Ne5532Engine Tuning UpÎncă nu există evaluări

- CV59SH-ASM - Placa Main - Service ManualDocument55 paginiCV59SH-ASM - Placa Main - Service Manualjose4445Încă nu există evaluări

- T-Con DatasheetDocument37 paginiT-Con DatasheetRafael CrespoÎncă nu există evaluări

- MC 84A ChassisDocument19 paginiMC 84A ChassisKapila Gunawardena100% (1)

- Notebook Power System Introduction TroubleshootingDocument44 paginiNotebook Power System Introduction TroubleshootingDhruv Gonawala89% (9)

- Soldering Station Hakko 936 - Instruction and SchematicsDocument9 paginiSoldering Station Hakko 936 - Instruction and SchematicsE.n. Elango80% (5)

- 300W Subwoofer Power AmplifierDocument5 pagini300W Subwoofer Power AmplifierhovukiemÎncă nu există evaluări

- NT71710MFG 000Document1 paginăNT71710MFG 000Tahir Hussain50% (4)

- Sharp AQUOS LC - (32/40/46/52) LE700UN Service ManualDocument156 paginiSharp AQUOS LC - (32/40/46/52) LE700UN Service Manualvobios78% (32)

- CV59SH U32 Datasheet PDFDocument33 paginiCV59SH U32 Datasheet PDFlcd_vinay3480% (5)

- HP Power Source HewlettDocument5 paginiHP Power Source HewlettManjunath Shenoy50% (2)

- TSUMV59XU DatasheetDocument33 paginiTSUMV59XU DatasheetMuhammad Shamrez89% (9)

- LCD Power - VG2021WM-2 - LD7575Document1 paginăLCD Power - VG2021WM-2 - LD7575taviÎncă nu există evaluări

- Top259en PDFDocument2 paginiTop259en PDFJose BenavidesÎncă nu există evaluări

- TNY264PNDocument6 paginiTNY264PNJose Benavides100% (1)

- DatasheetDocument2 paginiDatasheetRyanz Nayrz100% (1)

- TNY278PNDocument4 paginiTNY278PNJose BenavidesÎncă nu există evaluări

- Di-91 Design Idea Tinyswitch-Iii: 12 W Universal Input CV AdapterDocument2 paginiDi-91 Design Idea Tinyswitch-Iii: 12 W Universal Input CV Adapterahmed chaouki ChamiÎncă nu există evaluări

- Constant Current/Constant Power Regulation Circuits For: TopswitchDocument16 paginiConstant Current/Constant Power Regulation Circuits For: TopswitchBharat Singh AhluwaliaÎncă nu există evaluări

- Slyt 391Document5 paginiSlyt 391deedeeÎncă nu există evaluări

- Di-198 Design Idea Linkswitch-Cv: Wide Range DVD Player Multiple Output Power Supply Without Need For OptocouplerDocument2 paginiDi-198 Design Idea Linkswitch-Cv: Wide Range DVD Player Multiple Output Power Supply Without Need For OptocouplerAllyfranhy Nunes AlvesÎncă nu există evaluări

- Reference Design - 1 STR-A6151 Universal-Input, 10 W Power SupplyDocument2 paginiReference Design - 1 STR-A6151 Universal-Input, 10 W Power Supplygary omanaÎncă nu există evaluări

- Di-123 Design Idea Tinyswitch-Iii: 9.65 W, Dual Output Power Supply For Residential Heating ControlDocument2 paginiDi-123 Design Idea Tinyswitch-Iii: 9.65 W, Dual Output Power Supply For Residential Heating Controlahmed chaouki ChamiÎncă nu există evaluări

- Application Note An-45 Linkswitch-Cv Family: Design GuideDocument18 paginiApplication Note An-45 Linkswitch-Cv Family: Design Guidebharath prabhuÎncă nu există evaluări

- Tops WithDocument8 paginiTops Withtiburcio2000Încă nu există evaluări

- Dual PolarityDocument2 paginiDual Polaritysavour99Încă nu există evaluări

- DF6113-Led Backlight DriverDocument7 paginiDF6113-Led Backlight DriverTonpitonpi Ton Pi100% (1)

- Understanding Instrument CablesDocument7 paginiUnderstanding Instrument CablesrjeceÎncă nu există evaluări

- Chap 2Document11 paginiChap 2EphremSenaitÎncă nu există evaluări

- Understanding Microphone CablesDocument9 paginiUnderstanding Microphone CablesdeodhaixÎncă nu există evaluări

- PRESBYOPIA May 2014Document93 paginiPRESBYOPIA May 2014Tonpitonpi Ton PiÎncă nu există evaluări

- Construccion de Un Medidor ESR Kit Modelo k7214Document14 paginiConstruccion de Un Medidor ESR Kit Modelo k7214Tonpitonpi Ton PiÎncă nu există evaluări

- Micro-USB ConnectorsDocument4 paginiMicro-USB ConnectorsTonpitonpi Ton PiÎncă nu există evaluări

- ESR MeterDocument21 paginiESR MeterTonpitonpi Ton Pi100% (1)

- Complete Manual For AVR Multi-Tester Version 1.12kDocument128 paginiComplete Manual For AVR Multi-Tester Version 1.12kBenjamin Dover100% (1)

- TesterDocument18 paginiTesterantoninoxxxÎncă nu există evaluări

- Assembly Manual: In-Circuit LOPT/FBT Tester K 7205Document6 paginiAssembly Manual: In-Circuit LOPT/FBT Tester K 7205majanaam100% (1)

- Inductance Checker ARTestManualDocument8 paginiInductance Checker ARTestManualTonpitonpi Ton PiÎncă nu există evaluări

- S2035K-SCR 200 V 35a To-218Document12 paginiS2035K-SCR 200 V 35a To-218Roberto MendesÎncă nu există evaluări

- 03-5 - Resistor Color Code ChartDocument1 pagină03-5 - Resistor Color Code Chartsandeep_2262Încă nu există evaluări

- Servicemodes TVDocument54 paginiServicemodes TVpravin_rdiu100% (2)

- SLDC008 LCD Diagnostic POST Card User ManualDocument3 paginiSLDC008 LCD Diagnostic POST Card User ManualTonpitonpi Ton Pi0% (1)

- Manual Postcard LCD 60 PDFDocument32 paginiManual Postcard LCD 60 PDFTonpitonpi Ton Pi100% (1)

- Diagnostic Card User ManualDocument28 paginiDiagnostic Card User ManualNSunÎncă nu există evaluări

- Carrier Service Manual Airconditioner Split TypeDocument115 paginiCarrier Service Manual Airconditioner Split TypeTonpitonpi Ton PiÎncă nu există evaluări

- Energy - Batteries in A Portable World - A Handbook On Rechargeable Batteries For Non-Engineers - 2Nd Ed - I Buchman (Cadex Electronics) - 2001Document149 paginiEnergy - Batteries in A Portable World - A Handbook On Rechargeable Batteries For Non-Engineers - 2Nd Ed - I Buchman (Cadex Electronics) - 2001fabioffÎncă nu există evaluări

- Circuitos Refrig - Whirlpool Wiring DiagramDocument2 paginiCircuitos Refrig - Whirlpool Wiring DiagramTonpitonpi Ton Pi0% (1)

- Daewoo SERVICE MANUAL NO-FROST COMBI-REFRIGERATOR ERF-364 - 367 - ALL AR-EU MODELS PDFDocument56 paginiDaewoo SERVICE MANUAL NO-FROST COMBI-REFRIGERATOR ERF-364 - 367 - ALL AR-EU MODELS PDFTonpitonpi Ton PiÎncă nu există evaluări

- Document View PDFDocument4 paginiDocument View PDFCeberus233Încă nu există evaluări

- Overview of Data Tiering Options in SAP HANA and Sap Hana CloudDocument38 paginiOverview of Data Tiering Options in SAP HANA and Sap Hana Cloudarban bÎncă nu există evaluări

- Salonga Vs Cruz PanoDocument1 paginăSalonga Vs Cruz PanoGeorge Demegillo Rocero100% (3)

- Synopsis For DPC 190101131Document4 paginiSynopsis For DPC 190101131Sonal YadavÎncă nu există evaluări

- PFRS 3 Business CombinationDocument3 paginiPFRS 3 Business CombinationRay Allen UyÎncă nu există evaluări

- 2023 Korean Honor Scholarship (KHS) GuidelinesDocument8 pagini2023 Korean Honor Scholarship (KHS) GuidelinesBình NguyênÎncă nu există evaluări

- A Risk-Based Approach To Compliant Electronic RecordsDocument59 paginiA Risk-Based Approach To Compliant Electronic RecordsNeo0% (1)

- The Argumentative Indian Amartya SenDocument12 paginiThe Argumentative Indian Amartya SenVipin Bajaj100% (2)

- Hydrolics-Ch 4Document21 paginiHydrolics-Ch 4solxÎncă nu există evaluări

- HSE Policy Statement, SchlumbergerDocument1 paginăHSE Policy Statement, SchlumbergerProf C.S.PurushothamanÎncă nu există evaluări

- AptitudeDocument2 paginiAptitudedodaf78186Încă nu există evaluări

- RAWLINGS (TRAWLING) LIMITED - Company Accounts From Level BusinessDocument7 paginiRAWLINGS (TRAWLING) LIMITED - Company Accounts From Level BusinessLevel BusinessÎncă nu există evaluări

- The Mysterious Benedict Society and The Prisoner's Dilemma (Book 3) by Trenton Lee Stewart (Preview)Document47 paginiThe Mysterious Benedict Society and The Prisoner's Dilemma (Book 3) by Trenton Lee Stewart (Preview)Little, Brown Books for Young Readers63% (16)

- Giannasca FAR As Filed 10-10-2019 AcceptedDocument39 paginiGiannasca FAR As Filed 10-10-2019 AcceptedRussinatorÎncă nu există evaluări

- CS-Fin Mkts-Buyback of Shares by MNCs in IndiaDocument9 paginiCS-Fin Mkts-Buyback of Shares by MNCs in IndiaPramod Kumar MitraÎncă nu există evaluări

- Spouses Firme Vs BukalDocument2 paginiSpouses Firme Vs Bukalpayumomichael2276Încă nu există evaluări

- Address: Purok 4, Brgy. Odiongan, Gingoog City Email: Jacintomalimasnhs@deped - Gov.phDocument2 paginiAddress: Purok 4, Brgy. Odiongan, Gingoog City Email: Jacintomalimasnhs@deped - Gov.phJeffrey Lois Sereño MaestradoÎncă nu există evaluări

- Deed of Absolute Sale of Portion of The LandDocument5 paginiDeed of Absolute Sale of Portion of The LandgongsilogÎncă nu există evaluări

- Trip ID: 230329124846: New Delhi To Gorakhpur 11:15 GOPDocument2 paginiTrip ID: 230329124846: New Delhi To Gorakhpur 11:15 GOPRishu KumarÎncă nu există evaluări

- Company: ManufacturingDocument8 paginiCompany: Manufacturingzain khalidÎncă nu există evaluări

- 2-Test Report of Ambroxol HCL 2Document1 pagină2-Test Report of Ambroxol HCL 2ShagorShagorÎncă nu există evaluări

- Eou FTZ EpzDocument18 paginiEou FTZ EpzNaveen Kumar0% (1)

- Certified Patent Valuation Analyst - TrainingDocument8 paginiCertified Patent Valuation Analyst - TrainingDavid WanetickÎncă nu există evaluări

- Australia - Prison Police State - Thanks Anthony AlbaneseDocument40 paginiAustralia - Prison Police State - Thanks Anthony AlbaneseLloyd T VanceÎncă nu există evaluări

- 1854 - (Ennemoser) - The History of Magic Vol 1Document531 pagini1854 - (Ennemoser) - The History of Magic Vol 1GreyHermitÎncă nu există evaluări

- 06 - StreamUP & Umap User ManualDocument98 pagini06 - StreamUP & Umap User ManualRené RuaultÎncă nu există evaluări

- Sept. 2021 INSET Notice and Minutes of MeetingDocument8 paginiSept. 2021 INSET Notice and Minutes of MeetingSonny MatiasÎncă nu există evaluări

- Republic Vs HerbietoDocument2 paginiRepublic Vs HerbietoMichelle Vale CruzÎncă nu există evaluări

- The Life'S and Works of Jose Rizal Rizal'S Life and The Philippines in The Nineteenth Century As Rizal'S ContextDocument6 paginiThe Life'S and Works of Jose Rizal Rizal'S Life and The Philippines in The Nineteenth Century As Rizal'S ContextVanessa Del RosarioÎncă nu există evaluări

- Remedial Law Q and ADocument17 paginiRemedial Law Q and Akonvan100% (2)