Documente Academic

Documente Profesional

Documente Cultură

TLE7209 - Motor CC PDF

Încărcat de

MecaSoftwareTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

TLE7209 - Motor CC PDF

Încărcat de

MecaSoftwareDrepturi de autor:

Formate disponibile

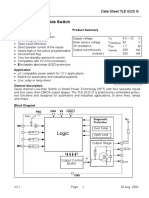

7 A H-Bridge for DC-Motor Applications TLE 7209-2R

Final Datasheet

1 Overview

1.1 Features

Operating supply voltage 5 V to 28 V

Typical RDSon = 150 m for each output transistor

(at 25 C)

Continuous DC load current 5 A (TC < 100 C)

Output current limitation at typ. 6.6 A 1.1 A

Short circuit shut-down for output currents over 8 A

Logic- inputs TTL/CMOS-compatible

Output switching frequency up to 30 kHz

Rise and fall times optimized for 0.5-2 kHz

Over-temperature protection

Short circuit protection

Undervoltage disable function

Diagnostic by SPI or Status-Flag (configurable)

Enable and Disable inputs

P-DSO-20-12 power package

Type Ordering Code Package

TLE 7209-2R Q67007-A9702 P-DSO-20-12

Functional Description

The TLE 7209-2R is an intelligent full H-Bridge, designed for the control of DC and

stepper motors in safety critical applications and under extreme environmental

conditions.

The H-Bridge is protected against over-temperature and short circuits and has an under

voltage lockout for all the supply voltages VS (main DC power supply). All malfunctions

cause the output stages to go tristate.

The device is configurable by the DMS pin. When grounded, the device gives diagnostic

information via a simple error flag. When supplied with VCC = 5 V, the device works in

SPI mode. In this mode, detailed failure diagnosis is available via the serial interface.

Final Datasheet 1 V1.2, 2004-jul-01

TLE 7209-2R

Overview

1.2 Pin Configuration

GND 1 20 GND

S C K /S F 2 19 IN 2

IN 1 3 18 D IS

VS CP 4 17 CSN

VS 5 16 VS

O UT1 6 15 O U T2

O UT1 7 14 O U T2

SDO 8 13 EN

SDI 9 12 DMS

GND 10 11 GND

M etal slug is

connected to G N D

pins internally

Figure 1 Pinout TLE 7209-2R

Table 1 Pin Definitions and Functions

Pin. No. Symbol Function

1 GND Ground

2 SCK/SF SPI-Clock/Status-flag

3 IN1 Input 1

4 VSCP Supply voltage for internal charge pump

5, 16 VS Supply voltage; connect pins externally

6, 7 OUT1 Output 1; connect pins externally

8 SDO Serial data out

9 SDI Serial data in

10 GND Ground

11 GND Ground

Final Datasheet 2 V1.2, 2004-jul-01

TLE 7209-2R

Overview

Table 1 Pin Definitions and Functions (contd)

Pin. No. Symbol Function

12 DMS Diagnostic-Mode selection

(+ Supply voltage for SPI-Interface)

13 EN Enable

14, 15 OUT2 Output 2; connect pins externally

17 CSN Chip Select (low active)

18 DIS Disable

19 IN2 Input 2

20 GND Ground

Final Datasheet 3 V1.2, 2004-jul-01

TLE 7209-2R

Overview

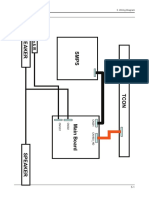

1.3 Block Diagram

DMS VSCP VS

Charge

Bias

Pump

Fault-

Detect

EN

DIS

Driver

CSN 8 Bit OUT 1

SDI Logic &

SPI

SDO and

Latch Gate- OUT 2

SCK/SF

Control

IN1 Direct

IN2 Input

Under

Voltage

Over

Temperature

GND

Figure 2 Block Diagram TLE 7209-2R

Final Datasheet 4 V1.2, 2004-jul-01

TLE 7209-2R

Circuit Description

2 Circuit Description

2.1 Control Inputs

The bridge is controlled by the Inputs IN1, IN2, DIS and EN as shown in Table 2. The

outputs OUT1 and OUT2 are set to High or Low by the parallel inputs IN1 and IN2,

respectively. In addition, the outputs can be disabled (set to tristate) by the Disable and

Enable inputs DIS and EN.

Inputs IN1, IN2 and DIS have an internal pull-up. Input EN has an internal pull-down.

Table 2 Functional Truth Table

Pos. DIS EN IN1 IN2 OUT1 OUT2 SF1) SPI2)

DIA_REG

1. Forward L H H L H L H see

2. Reverse L H L H L H H Chapter 2.4.2

3. Free-wheeling low L H L L L L H

4. Free-wheeling high L H H H H H H

5. Disable H X X X Z Z L

6. Enable X L X X Z Z L

7. IN1 disconnected L H Z X H X H

8. IN2 disconnected L H X Z X H H

9. DIS disconnected Z X X X Z Z L

10. EN disconnected X Z X X Z Z L

11. Current limit. active L H X X Z Z H

12. Under Voltage X X X X Z Z L

13. Over-temperature X X X X Z Z L

14. Over-current X X X X Z Z L

1)

If Mode Status-Flag is selected (see Chapter 2.4)

2)

If Mode SPI-Diagnosis is selected (see Chapter 2.4)

Final Datasheet 5 V1.2, 2004-jul-01

TLE 7209-2R

Circuit Description

2.2 Power Stages

Four n-channel power-DMOS transistors build up the output H-bridge. Integrated circuits

protect the outputs against over current and over-temperature if there is a short-circuit to

ground, to the supply voltage or across the load. Positive and negative voltage spikes,

which occur when switching inductive loads, are limited by integrated freewheeling

diodes. To drive the gates of the high-side DMOS, an internal charge pump is integrated

to generate a voltage higher than the supply voltage.

2.2.1 Chopper Current Limitation

To limit the output current at low power loss, a chopper current limitation is integrated as

shown in Figure 3. The current is measured by sense cells integrated in the low-side

switches. When the current limit IL has been exceeded for a time tb, all output stages are

switched off for a fixed time ta.

Blanking time tb

Current limit IL

IOUT

Switch-off time ta

time

Figure 3 Chopper current limitation

Final Datasheet 6 V1.2, 2004-jul-01

TLE 7209-2R

Circuit Description

2.2.2 Temperature-depending Current Reduction

For TILR < Tj < TSD the current limit decreases from IL = 6.6 A 1.1 A to

IL = 2.5 A 1.1 A as shown in Figure 4

A

6.6A

tolerance of temperature range of over-

dependent current temperature shut-down

IL

reduction

2.5A

Tj TILR TSD C

Figure 4 Temperature dependent current reduction

2.3 Protection

The TLE 7209-2R is protected against short circuits, overload and invalid supply voltage

by the following measures:

2.3.1 Short circuit to Ground

The high-side switches are protected against a short of the output to ground by an over

current shut-down. If a high-side switch is turned on and the current rises above the short

circuit detection current IOUK all output transistors are turned off after a typical filter time

of 2 s, and the error bit Short Circuit to Ground on output 1 (2), SCG1 (SCG2) is stored

in the internal status register.

2.3.2 Short circuit to VS

Due to the chopper current regulation, the low-side switches are already protected

against a short to the supply voltage. To be able to distinguish a short circuit from normal

current limit operation, the current limitation is deactivated for the blanking time tb after

the current has exceeded the current limit threshold IL. If the short circuit detection

current IOUK is reached within this blanking time, a short circuit is detected (see

Figure 5). All output transistors are turned OFF and the according error bit Short Circuit

to Battery on output 1 (2), SCB1 (SCB2) is set.

Final Datasheet 7 V1.2, 2004-jul-01

TLE 7209-2R

Circuit Description

IN

IN

IOUK IOUK

tb ta tb tb

IL IL

IOUT

IOUT

time time

Figure 5 Short to Vs detection. Left: normal operation. Right: short circuit is

detected

2.3.3 Short circuit across the load

If short circuit messages from high- and low-side switch occur simultaneously within a

delay time of typically 2s, the error bit Short Circuit Over Load, SCOL is set.

2.3.4 Over-Temperature

In case of high DC-currents, insufficient cooling or high ambient temperature, the chip

temperature may rise above the thermal shut-down temperature TSD. In that case, all

output transistors are shut-down and the error-bit Over-Temperature, OT is set.

2.3.5 Under-Voltage shut-down

If the supply-voltage at the VS pins falls below the under-voltage detection threshold, the

outputs are set to tristate and the error-bit Under-Voltage at VS is set.

2.4 Diagnosis

The Diagnosis-Mode can be selected between SPI-Diagnosis and Status-Flag

Diagnosis. The choice of the Diagnosis-Mode is selected by the voltage-level on Pin 12

(DMS Diagnosis Mode Selection):

DMS = GND, Status-Flag Mode

DMS = VCC, SPI-Diagnosis Mode

For the connection of Pins SDI, SDO, CSN and SCK/SF see Figure 14 and Figure 15.

Final Datasheet 8 V1.2, 2004-jul-01

TLE 7209-2R

Circuit Description

2.4.1 Status-Flag (SF) Mode (DMS = GND)

2.4.1.1 SF output

In SF-mode, pin 2 is used as an open-drain output status-flag. The pin has to be pulled

to the logic supply voltage with a pull-up resistor, 47 kOhm recommended.

In case of any failure that leads to a shut-down of the outputs, the status-flag is set (e.g.

SF pin pulled to low). These failures are:

Under Voltage on VS

Short circuit of OUT1 or OUT2 against VS or GND

Short circuit between OUT1 and OUT2

Over-current

Over-temperature

SF is also pulled low when the outputs are disabled by EN or DIS.

2.4.1.2 Fault storage and reset

In case of under-Voltage, the failure is not latched. As soon as VS falls below the

under-Voltage detection threshold, the output stage switches in tristate and the status-

flag is set from high level to low-level. If the voltage has risen above the specified value

again, the output stage switches on again and the status-flag is reset to high-level.

The Under Voltage failure is shown at the SF pin for VS in the voltage range below the

detection threshold (typical 4.2V) down to 2.5V.

In the SF-mode, all internal circuitry is supplied by the voltage on VS. For that reason,

a loss of VS supply voltage leads to a reset of all stored information (Power-ON-

Reset). This Power-ON-Reset occurs as soon as under-Voltage is detected on VS

In case of short circuit, over-current or over-temperature, the fault will be stored.

The output stage remains in tristate and the status-flag at low-level until the error is

reset by one of the following conditions: H -> L on DIS, L -> H on EN or Power-ON

Reset.

2.4.2 SPI-Mode (DMS = 5V)

2.4.2.1 SPI-Interface

The serial SPI interface establishes a communication link between TLE 7209-2R and the

systems microcontroller. The TLE 7209-2R always operates in slave mode whereas the

controller provides the master function. The maximum baud rate is 2 MBaud (200pF on

SDO).

By applying an active slave select signal at CSN the TLE 7209-2R is selected by the SPI

master. SDI is the data input (Slave In), SDO the data output (Slave Out). Via SCK

(Serial Clock Input) the SPI clock is provided by the master. In case of inactive slave

select signal (High) the data output SDO goes into tristate.

Final Datasheet 9 V1.2, 2004-jul-01

TLE 7209-2R

Circuit Description

The first two bits of an instruction may be used to establish an extended device-

addressing. This gives the opportunity to operate up to 4 Slave-devices sharing one

common CSN signal from the Master-Unit (see Figure 7)

S P I p o w e r-

DMS

s u p p ly

CSN S P I - C o n t r o l:

SCK

- > s t a t e m a c h in e

- > c lo c k c o u n t e r

- > in s t r u c t io n r e c o g n i t io n

SDI

s h if t - r e g i s t e r 8

SDO

D IA _ R E G 8

R eset

D ia g n o s t ic s

D IS

OR DMS

EN U n d e r-

v o lt a g e

Figure 6 SPI block-diagram

2.4.2.2 Characteristics of the SPI Interface

1. When DMS is > 3.5V, the SPI is active, independently of the state of EN or DIS. During

active reset conditions (DMS < 3.5V) the SPI is driven into its default state. When reset

becomes inactive, the state machine enters into a wait-state for the next instruction.

2. If the slave select signal at CSN is inactive (high), the state machine is forced to enter

the wait-state, i.e. the state machine waits for the following instruction.

3. During active (low) state of the select signal CSN the falling edge of the serial clock

signal SCK will be used to latch the input data at SDI. Output data at SDO are driven

with the rising edge of SCK (see timing diagram Figure 13)

4. Chip-address:

In order to establish the option of extended addressing the uppermost two bits of the

instruction-byte (i.e the first two SDI-bits of a Frame) are reserved to send a chip-

address. To avoid a bus conflict the output SDO must stay high impedance during the

addressing phase of a frame (i.e. until the address-bits are recognized as valid chip-

address). If the chip-address does not match, the data at SDI will be ignored and SDO

remains high impedance for the complete frame. See also Figure 7

5. Verification byte:

Simultaneously to the receipt of an SPI instruction TLE 7209-2R transmits a

verification byte via the output SDO to the controller. Refer to Figure 8. This byte

indicates normal or abnormal operation of the SPI. It contains an initial bit pattern and

a flag indicating an error occurred during the previous access.

Final Datasheet 10 V1.2, 2004-jul-01

TLE 7209-2R

Circuit Description

6. Because only read access is used in the TLE 7209-2R, the SDI data-bits (2nd byte)

are not used

7. Invalid instruction/access:

An instruction is invalid if an unused instruction code is detected (see tables with SPI

instructions). In case an unused instruction code occurred, the data byte ffhex (no

error) will be transmitted after having sent the verification byte. This transmission

takes place within the same SPI-frame that contained the unused instruction byte. In

addition any transmission is invalid if the number of SPI clock pulses (falling edge)

counted during active CSN differs from exactly 16 clock pulses. If an invalid instruction

is detected, bit TRANS_F in the following verification byte (next SPI transmission) is

set to HIGH. The TRANS_F bit must not be cleared before it has been sent to the

microcontroller.

8. Transfer error bit TRANS_F:

The bit TRANS_F indicates an error during the previous transfer. An error is

considered to have occurred when an invalid command was sent, the number of SPI

clock pulses (falling edge) counted during active CSN was less than or greater than

16 clock pulses, or SPI clock (SCK) was logical high during falling edge of CSN.

Final Datasheet 11 V1.2, 2004-jul-01

TLE 7209-2R

Circuit Description

SDO remains tristated Address sent by Correct addres is recognized,

after CSN active master is "00" data transmitted to SDO

CSN

SCK 7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0

SDI 7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0

SDO Z 5 4 3 2 1 0 7 6 5 4 3 2 1 0

SDO remains tristated Address sent by master Correct addres is not recognized, SDO

after CSN active is differnt from "00" remains tristated and SDI data are ignored

CSN

SCK 7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0

SDI 7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0

SDO Z

Figure 7 Bus-arbitration by chip-address

Final Datasheet 12 V1.2, 2004-jul-01

TLE 7209-2R

Circuit Description

2.4.2.3 SPI-Communication

The 16 input bits consist of the SPI-instruction byte and a second, unused byte. The 16

output bits consist of the verification-byte and the data-byte (see also Figure 8). The

definition of these bytes is given in the subsequent sections.

CSN

SCK 7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0

SDI MSB SPI Instruction LSB not used

SDO MSB Verification byte LSB MSB data-byte LSB

Figure 8 SPI communication

2.4.2.4 SPI instruction

The uppermost 2 bit of the instruction byte contain the chip-address. The chip-address

of the TLE 7209-2R is 00. During read-access, the output data according to the register

requested in the instruction byte are applied to SDO within the same SPI frame. That

means, the output data corresponding to an instruction byte sent during one SPI frame

are transmitted to SDO during the same SPI frame.

Table 3 SPI Instruction Format

MSB

7 6 5 4 3 2 1 0

0 0 INSTR4 INSTR3 INSTR2 INSTR1 INSTR0 INSW

Table 4 SPI instruction Description

Bit Name Description

7,6 CPAD1,0 Chip Address (has to be 0, 0)

5-1 INSTR (4-0) SPI instruction (encoding)

0 INSW Even parity

Final Datasheet 13 V1.2, 2004-jul-01

TLE 7209-2R

Circuit Description

Table 5 SPI Instruction-Bytes Encoding

SPI Instruction Encoding Description

bit 7,6 bit 5-1 Bit 0

CPAD1,0 INSTR(4-0) INSW

RD_IDENT 00 00000 0 read identifier

RD_VERSION 00 00001 1 read version

RD_DIA 00 00100 1 read DIA_REG

00 all others x unused, TRANS_F is set to high,

ff_hex is sent as data bit

all others xxxxx x invalid address, SDO remains

tristate during entire SPI frame

2.4.2.5 Verification Byte

Table 6 Verification Byte Format

MSB

7 6 5 4 3 2 1 0

Z Z 1 0 1 0 1 TRANS_F

Table 7 Verification Byte Description

Bit Name Description

0 TRANS_F Bit = 1: error detected during previous transfer

Bit = 0: previous transfer was recognized as valid

1 Fixed to High

2 Fixed to Low

3 Fixed to High

4 Fixed to Low

5 Fixed to High

6 send as high impedance

7 send as high impedance

The default value after power-up at DMS of the TRANS_F bit is L (previous transfer valid)

Final Datasheet 14 V1.2, 2004-jul-01

TLE 7209-2R

Circuit Description

2.4.2.6 Data-byte: Diagnostics/Encoding of Failures

(Register DIA_REG, SPI Instruction RD_DIA)

)

Table 8 DIA_REG Format

MSB

7 6 5 4 3 2 1 0

EN/DIS OT CurrRed CurrLim DIA21 DIA20 DIA11 DIA10

Table 9 DIA_REG Description

Default value after reset is FFhex. Access by controller is read only

Bit Name Description latch

behavior

0 DIA 10 Diagnosis-Bit1 of OUT1 see below

1 DIA 11 Diagnosis-Bit2 of OUT1 see below

2 DIA 20 Diagnosis-Bit1 of OUT2 see below

3 DIA 21 Diagnosis-Bit2 of OUT2 see below

4 CurrLim is set to 0 in case of current limitation. latched

5 CurrRed is set to 0 in case of temperature dependent latched

current limitation

6 OT is set to 0 in case of over-temperature latched

7 EN/DIS is set to 0 in case of EN = L or DIS = H not latched

EN DIS DIA_REG_7

H L 1

L L 0

H H 0

L H 0

Final Datasheet 15 V1.2, 2004-jul-01

TLE 7209-2R

Circuit Description

Table 10 Encoding of the Diagnostic Bits of OUT1 and OUT2

DIA21 DIA20 DIA11 DIA10 Description latch

behavior

1 1 0 0 Short circuit over load (SCOL) latched

- - 0 1 Short circuit to battery on OUT1 (SCB1) latched

- - 1 0 Short circuit to ground on OUT1 (SCG1) latched

- - 1 1 No error detected on OUT1 -

0 0 1 1 Open load (OL) latched

0 1 - - Short circuit to battery on OUT2 (SCB2) latched

1 0 - - Short circuit to ground on OUT2 (SCG2) latched

1 1 - - No error detected on OUT2 -

0 0 0 0 Under Voltage on Pin Vs not latched

Failure Encoding in case of multiple faults

If multiple faults are stored in the failure register, the faults that are encoded in the DIAxx

bits can not be displayed simultaneously due to the encoding scheme that is used. In this

case, errors are encoded according to the following priority list.

Priority 1: Under Voltage (please note that after removal of Under Voltage, the original

error will be restored, see below)

Priority 2: Short circuit across the load

Priority 3: all other short circuits

Priority 4: open load

If a failure of higher priority is detected, the failures of lower priority are no longer visible

in the encoded SPI message.

Fault storage and reset of the Diagnosis Register DIA_REG

Register DIA_REG is reset upon the following conditions:

With the rising edge of the CSN-Signal after the SPI-instruction RD_DIA. This reset

only takes place if the correct number of 16 SCK pulses has been counted.

When the voltage on DMS exceeds the threshold for detecting SPI-Mode (after Under

Voltage condition). Under Voltage on Vs (typ. < 5,0V) sets Bit 0.... Bit 3 of DIA_REG

to 0000. If Vs rises above the Under Voltage level, Bits of DIA_REG are restored

(when DMS > 3.5V).

A rising edge on EN while DIS=0 or a falling edge on DIS while EN=1 re-activates the

output power-stages, and resets the DIA_REG register.

Final Datasheet 16 V1.2, 2004-jul-01

TLE 7209-2R

Circuit Description

2.4.2.7 Data-byte: Device Identifier and Version

(SPI instructions RD_IDENT and RD_VERSION)

The ICs identifier (device ID) and version number are used for production test purposes

and features plug & play functionality depending on the systems software release. The

two numbers are read-only accessible via the SPI instructions RD_IDENT and

RD_VERSION as described in Section 2.4.2.4.

The device ID is defined to allow identification of different IC-Types by software and is

fixed for the TLE 7209-2R.

The Version number may be utilized to distinguish different states of hardware and is

updated with each redesign of the TLE 7209-2R. The contents is divided into an upper

4 bit field reserved to define revisions (SWR) corresponding to specific software releases

and a lower 4 bit field utilized to identify the actual mask set revision (MSR).

Both (SWR and MSR) will start with 0000b and are increased by 1 every time an

according modification of the hardware is introduced.

Reading the IC Identifier (SPI Instruction: RD_IDENT):

Table 11 Device Identifier Format

MSB

7 6 5 4 3 2 1 0

ID7 ID6 ID5 ID4 ID3 ID2 ID1 ID0

Table 12 Device Identifier Description

Bit Name Description

7...0 device-ID(7...0) ID-No.: 10100010

Reading the IC version number (SPI Instruction: RD_VERSION):

Table 13 IC version number Format

MSB

7 6 5 4 3 2 1 0

SWR3 SWR2 SWR1 SWR0 MSR3 MSR2 MSR1 MSR0

Table 14 IC version number Description

Bit Name Description

7...4 SWR(3...0) This register is set to 0

3...0 MSR(3...0) Version corresponding to Mask set

Final Datasheet 17 V1.2, 2004-jul-01

TLE 7209-2R

Circuit Description

2.4.2.8 Open-Load Diagnosis

Open-load diagnostic in OFF-state is only possible in the SPI-mode (DMS = 5 V) if the

device is Disabled (EN = L or DIS = H). The detection mechanism is depicted in

Figure 9. The according diagnostic information can be read out via the SPI diagnostic

register. The resulting overall diagnostic truth-table is shown as Table 15

VS VS

DMS

1.5mA

-

+

AND

DIS

OR OUT1 OUT2

EN

1V

- to diagnostic

+ register

1V

1mA

1 AND

Figure 9 Functional block diagram of open-load detection

Table 15 Diagnosis Truth Table for open load detection

Output stage inactive, EN = low or DIS = high, DMS > 4.5 V

OUT1 OUT2

Load available H H

Open Load H L OL detected

SC -> GND on OUT1 and Open Load L L OL not detected double Fault

SC -> GND on OUT2 and Open Load H L OL detected

SC -> VS on OUT1 and Open Load H L OL detected

SC -> VS on OUT2 and Open Load H H OL not detected double Fault

Final Datasheet 18 V1.2, 2004-jul-01

TLE 7209-2R

Electrical Characteristics

3 Electrical Characteristics

3.1 Absolute Maximum Ratings

Pos. Parameter Sym- Limit Values Unit Test Conditions

bol min. max.

3.1.1 Junction temperature Tj -40 +150 C

+175 C dynamic: t < 1 s

3.1.2 Storage temperature Ts -55 +125 C

3.1.3 Ambient temperature Ta -40 +125 C

3.1.4 Supply voltage VS -1 40 V static destruction proof

-2 40 V dynamic destruction proof

t < 0.5 s

(single pulse, Tj < 85 C)

3.1.5 Voltage at logic V -0.5 18 V In status-flag-mode, SF

inputs pull-up R 10 k

IN1, IN2, DIS, EN,

SDI, SCK/SF

3.1.6 Voltage at logic input V -0.5 40 V

CSN

3.1.7 Voltage at logic input VDMS -0.5 13 V

DMS

3.1.8 Voltage at logic V -0.5 VDMS V

output SDO +0.5

3.1.9 Voltage at VsCP VCP VS - VS + V -

0.5 0.5

3.1.10 ESD voltage human VESD 4kV all pins

3.1.11 body model (MIL VESD-- 8kV only pins 6, 7, 14 and 15

STD 883D / ANSI (outputs)

OUT

EOS\ESD S5.1)

Note: Maximum ratings are absolute ratings; exceeding any one of these values may

cause irreversible damage to the integrated circuit.

Final Datasheet 19 V1.2, 2004-jul-01

TLE 7209-2R

Electrical Characteristics

3.2 Operating Range

Pos. Parameter Sym- Limit Values Unit Remark

bol min. max.

3.2.1 Supply Voltage VS 5 28 V

3.2.2 DMS Supply Voltage VDMS 3.5 5.5 V Device in SPI-mode

3.2.3 PWM frequency f 30 kHz May be limited to lower values

in the application due to

switching losses or duty cycle

requirements

3.2.4 Junction Temperature TJ -40 150 C

Note: In the operating range, the circuit functionality as described in the circuit

description is fulfilled.

3.3 Thermal Resistance

3.3.1 Junction-case RthJC 1.5 K/W specified by design

3.3.2 Junction-ambient RthJA 50 K/W minimal footprint

3.4 Electrical Characteristics

5V < VS < 28V; 40 C < Tj < 150 C; unless otherwise specified

Pos. Parameter Symbol Limit Values Unit Test Conditions

min. typ. max.

Power Supply

3.4.1 Under voltage at VS VUV OFF 3.4 4.2 5 V Switch off threshold

VUV ON 3.6 4.4 5.2 Switch on threshold

VUV HY 100 1000 mV Hysteresis

3.4.2 Supply current IUB 30 mA f = 20 kHz, IOUT = 0 A

20 mA f = 0 Hz, IOUT = 0 A

Final Datasheet 20 V1.2, 2004-jul-01

TLE 7209-2R

Electrical Characteristics

3.4 Electrical Characteristics (contd)

5V < VS < 28V; 40 C < Tj < 150 C; unless otherwise specified

Pos. Parameter Symbol Limit Values Unit Test Conditions

min. typ. max.

Logic Inputs IN1, IN2, DIS, EN

3.4.3 Input high VIH 2 V

3.4.4 Input low VIL 1 V

3.4.5 Input hysteresis VIHY 0.1 0.6 V

3.4.6 pull-up current IIL -200 -125 A U1V

IN1, IN2, DIS

3.4.7 pull-down current EN IIH 100 A U2V

Power Outputs OUT1, OUT2

3.4.8 Switch on resistance 300 m ROUT-UB, ROUT-GND

VS > 5 V, IOUT = 3 A

3.4.9 Switch-off current |IL| 5.5 6.6 7.7 A -40 C < Tj < TILR

1.4 2.5 3.6 A Tj = TSD; specified by

design

3.4.10 Switch-off time ta 8 16 26 s Vs=13.2 V, L=2.2 mH,

R=0.23

3.4.11 Blanking time tb 8 13 19 s Vs=13.2 V, L=2.2 mH,

R=0.23

3.4.12 Switch-off Tracking ta/tb 1.0 Vs=13.2 V, L=2.2 mH,

R=0.23

3.4.13 Short circuit detection |IOUK| 8 18 A

current

3.4.14 Current Tracking |IOUK|- 2 3.5 A specified by design

|IL|

3.4.15 Reactivation time after t 200 s Over-current- or over-

internal shut-down temperature shut-

down to reactivation

of the output stage

Note: Reactivation time is not subject to production test; specified by design

Final Datasheet 21 V1.2, 2004-jul-01

TLE 7209-2R

Electrical Characteristics

3.4 Electrical Characteristics (contd)

5V < VS < 28V; 40 C < Tj < 150 C; unless otherwise specified

Pos. Parameter Symbol Limit Values Unit Test Conditions

min. typ. max.

3.4.16 Leakage current 200 A Output stage

switched off

3.4.17 Free-wheel diode UD 2 V IOUT = 3 A

forward voltage

3.4.18 Free-wheel diode trr 100 ns Reverse recovery

reverse recovery time time is not subject to

production test;

specified by design

Output Status-flag, Open Drain Output DMS < 0.8 V

3.4.19 Output high ISF 20 A VSF = 5 V

(SF not set)

3.4.20 Output low ISF 300 A VSF = 1 V

(SF set) 100 A VSF = 0.5 V

Timing

3.4.21 Output ON-delay tdon 6 s IN1 --> OUT1 resp.

IN2 --> OUT2, IOUT =

3A

3.4.22 Output OFF-delay tdoff 6 s IN1 --> OUT1 resp.

IN2 --> OUT2, IOUT =

3A

3.4.23 Output switching time tr, tf 5 s OUT1H --> OUT1L,

OUT2H --> OUT2L,

IOUT = 3 A

OUT1L --> OUT1H,

OUT2L --> OUT2H

3.4.24 Disable delay time tddis 2 s DIS --> OUTn,

EN --> OUTn

3.4.25 Power on delay time 1 ms VS = on --> output

stage active; no load

3.4.26 Delay time for fault tdf 1.0 2 s specified by design

detection

3.4.27 Minimum pulse width tden 1.6 2.2 s EN/DIS-->Reset

DIA_REG

Final Datasheet 22 V1.2, 2004-jul-01

TLE 7209-2R

Electrical Characteristics

3.4 Electrical Characteristics (contd)

5V < VS < 28V; 40 C < Tj < 150 C; unless otherwise specified

Pos. Parameter Symbol Limit Values Unit Test Conditions

min. typ. max.

Input SCK, SPI Clock Input

3.4.28 Low Level USCKL 1 V

3.4.29 High Level USCKH 2 V

3.4.30 Hysteresis USCK 0.1 0.4 V

3.4.31 Input Capacity CSCK 10 pF

3.4.32 Input Current -ISCK 20 50 A Pull-up current source

connected to VCC

Input CSN, Chip Select Signal

3.4.33 Low Level UCSNL 1 V TLE 7209-2R is

selected

3.4.34 High Level UCSNH 2 V

3.4.35 Hysteresis UCSN 0.1 0.4 V

3.4.36 Input Capacity CCSN 10 pF

3.4.37 Input Current -ICSN 20 50 A Pull up current source

connected to VCC

Input SDI, SPI Data Input

3.4.38 Low Level USDIL 1 V

3.4.39 High Level USDIH 2 V

3.4.40 Hysteresis USDI 0.1 0.4 V

3.4.41 Input Capacity CSDI 10 pF

3.4.42 Input Current -ISDI 20 50 A Pull up current source

connected to VCC

Final Datasheet 23 V1.2, 2004-jul-01

TLE 7209-2R

Electrical Characteristics

3.4 Electrical Characteristics (contd)

5V < VS < 28V; 40 C < Tj < 150 C; unless otherwise specified

Pos. Parameter Symbol Limit Values Unit Test Conditions

min. typ. max.

Output SDO

Tristate Output of the TLE 7209-2R (SPI output);

3.4.43 Low Level VSDOL 0.4 V ISDO = 2 mA

3.4.44 High Level VSDOH VDMS V ISDO = -2 mA

- 0.75

3.4.45 Capacity CSDO 10 pF Capacity of the pin in

tristate

3.4.46 Leakage Current ISDO -10 10 A In tristate

Note: All in- and output pin capacities are not subject to production test; specified by design

Input DMS

Supply-Input for the SPI-Interface and Selection Pin for SPI- or SF-Mode

3.4.47 Input Voltage VDMS 3.5 V SPI-Mode

VDMS 0.8 V Status-Flag-Mode

3.4.48 Input Current IDMS 10 mA SPI-Mode

Open-Load Diagnosis

3.4.49 Diagnostic Threshold VOUT1 0.8 2.0 V DMS > 4.5 V, EN <

VOUT2 0.8 2.0 V 0.8 V or DIS > 4.5 V;

no load

3.4.50 Pull-up Current -IOUT1 1000 1500 2000 A VOUT1=0 V,

DMS > 4.5 V, EN <

0.8 V or DIS > 4.5 V;

no load

3.4.51 Pull-down Current IOUT2 700 1000 1400 A VOUT2=5 V,

DMS > 4.5 V, EN <

0.8 V or DIS > 4.5 V;

no load

3.4.52 Tracking Diag. C 1.2 1.5 1.7 IOUT1/IOUT2

3.4.53 Delay Time tD 30 100 ms

Note: Open Load is detected if VOUT1 > 2 V AND VOUT2 < 0.8 V (refer to fig. 9).

Final Datasheet 24 V1.2, 2004-jul-01

TLE 7209-2R

Electrical Characteristics

3.4 Electrical Characteristics (contd)

5V < VS < 28V; 40 C < Tj < 150 C; unless otherwise specified

Pos. Parameter Symbol Limit Values Unit Test Conditions

min. typ. max.

SPI Timing (see Figure 13)

3.4.54 Cycle-Time (1) tcyc (1) 200 ns referred to master

3.4.55 Enable Lead Time tlead (2) 100 ns referred to master

3.4.56 Enable Lag Time tlag (3) 150 ns referred to master

3.4.57 Data Valid tv (4) 40 ns CL = 40 pF

150 ns CL = 200 pF

referred to TLE 7209-

2R

3.4.58 Data Setup Time tsu (5) 50 ns referred to master

3.4.59 Data Hold Time th (6) 20 ns referred to master

3.4.60 Disable Time tdis (7) 100 ns referred to TLE 7209-

2R; specified by

design

3.4.61 Transfer Delay tdt (8) 150 ns referred to master

3.4.62 Select time tCSN (9) 50 ns referred to master

3.4.63 Access time tacc (10) 8.35 s referred to master

3.4.64 Clock inactive before (11) 200 ns

chip select becomes

valid

3.4.65 Clock inactive after (12) 200 ns

chip select becomes

invalid

Temperature Thresholds

3.4.66 Start of current limit TILR 150 165 C

reduction

3.4.67 Thermal Shut-down TSD 175 C

Note: Temperature thresholds are not subject to production test; specified by design

Final Datasheet 25 V1.2, 2004-jul-01

TLE 7209-2R

Timing Diagrams

4 Timing Diagrams

5

INx

50% 50%

80%

OUTx

20%

tdon tdoff

Figure 10 Output Delay Time--Depicted for Low-Side FETs

5

DIS / EN

50%

OUTx

20%

Z

tddis

Figure 11 Disable Delay Time

Final Datasheet 26 V1.2, 2004-jul-01

TLE 7209-2R

Timing Diagrams

tRISE tFALL

80% 80%

OUTx

20% 20%

Figure 12 Output Switching Time

10 9

CSN

11 2 1 3 8

SCK 12

4 7

SDO tristate

Bit (n-3) Bit (n-4)...1 Bit 0; LSB

5 6

SDI MSB IN Bit (n-2) Bit (n-3) Bit (n-4)...1 LSB IN

n = 16

Figure 13 SPI-timing

Final Datasheet 27 V1.2, 2004-jul-01

TLE 7209-2R

Application

5 Application

VSCP VS

DMS

V-Reg

Vcc

IN1

IN2

DIS

C CSN OUT 1

M

SDI

SDO

OUT 2

SCK/SF

from Watchdog or EN

fail-safe Controller

GND

Figure 14 Application Example with SPI-Interface

VSCP VS

DMS

V-Reg

Vcc

IN1

IN2

DIS

C CSN OUT 1

47k M

SDI

SDO

OUT 2

SCK/SF

from Watchdog or EN

fail-safe Controller

GND

Figure 15 Application Example with Status-Flag

Final Datasheet 28 V1.2, 2004-jul-01

TLE 7209-2R

Application

Reverse polarity protection via main relay

VS TLE 7209-2R

main

Vs < 40V

100F 100nF

relay

ignition

switch

battery

Figure 16 Application Examples for Over-Voltage- and Reverse-Voltage

Protection

Final Datasheet 29 V1.2, 2004-jul-01

TLE 7209-2R

Package Outlines

6 Package Outlines

P-DSO-20-12

(Plastic Dual Small Outline Package)

11 0.15 1)

3.5 MAX.

B

3.25 0.1

0.25 +0.07

1.2 -0.3 2.8

0.02

0 +0.1

5 3

1.3

15.74 0.1

6.3

1.27 (Heatslug) 0.1 Heatslug

(Mold)

0.95 0.15

0.4 +0.13

0.25 M A 20x 14.2 0.3

0.25 B

5.9 0.1

(Metal)

3.2 0.1

(Metal)

20 11 11 20

Index Marking

1 10 10 1 Heatslug

1 x 45 13.7 -0.2

15.9 0.15 1) (Metal)

A

(Mold)

GPS05791

1)

Does not include plastic or metal protrusion of 0.15 max. per side

Sorts of Packing

Package outlines for tubes, trays etc. are contained in our

Data Book Package Information

SMD = Surface Mounted Device Dimensions in mm

Final Datasheet 30 V1.2, 2004-jul-01

TLE 7209-2R

Revision History

7 Revision History

TLE 7209-2R 2004-jul-01 V1.2

Previous Version: Final Datasheet V1.1, 2004-may-25

Section Subjects (major changes since last revision)

3.4.25 Added no load to Test Conditions

3.4.26 Added 1.0 sec minimum

3.4.49 Clarified Open Load diagnostic threshold

4 Figure 10 is depicted for low-side FETs

Final Datasheet 31 V1.2, 2004-jul-01

Edition 2004-jul-01

Published by Infineon Technologies AG,

St.-Martin-Strasse 53,

D-81541 Mnchen, Germany

Infineon Technologies AG 2004.

All Rights Reserved.

Attention please!

The information herein is given to describe certain components and shall not be considered as warranted

characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding

circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

Information

For further information on technology, delivery terms and conditions and prices please contact your nearest

Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide.

Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in

question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written

approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure

of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support

devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain

and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may

be endangered.

S-ar putea să vă placă și

- 7 A H-Bridge For DC-Motor Applications 30348: Preliminary DatasheetDocument4 pagini7 A H-Bridge For DC-Motor Applications 30348: Preliminary DatasheetallisonÎncă nu există evaluări

- TLE7209 R InfineonDocument16 paginiTLE7209 R Infineonmobil benerÎncă nu există evaluări

- 7 A H-Bridge For DC-Motor Applications TLE 6209 R: 1 1.1 FeaturesDocument29 pagini7 A H-Bridge For DC-Motor Applications TLE 6209 R: 1 1.1 Featureswtn2013Încă nu există evaluări

- Tle5205 2Document23 paginiTle5205 2Richard MachadoÎncă nu există evaluări

- Infineon TLE6209R DS v03 02 enDocument30 paginiInfineon TLE6209R DS v03 02 enRoger SegoÎncă nu există evaluări

- DatasheetDocument16 paginiDatasheetAndres GuerreroÎncă nu există evaluări

- 1 Tle5206 2 - 1Document23 pagini1 Tle5206 2 - 1Fran CastanoÎncă nu există evaluări

- Smart Octal Low-Side Switch: LogicDocument17 paginiSmart Octal Low-Side Switch: Logicjuan echeverryÎncă nu există evaluări

- Trilithic Data Sheet Bts 781 GP: 1 1.1 FeaturesDocument17 paginiTrilithic Data Sheet Bts 781 GP: 1 1.1 FeaturesВиктор СабовÎncă nu există evaluări

- Data SheetDocument16 paginiData Sheetcarrei JohnÎncă nu există evaluări

- TLE4470Document24 paginiTLE4470ricahard61Încă nu există evaluări

- 2-Phase Stepper-Motor Driver TLE 4728 G: Bipolar-IC FeaturesDocument26 pagini2-Phase Stepper-Motor Driver TLE 4728 G: Bipolar-IC FeaturesMohammad RanjbarÎncă nu există evaluări

- Tle 7263eDocument62 paginiTle 7263eCarlos PenagosÎncă nu există evaluări

- Specification Nta92cDocument6 paginiSpecification Nta92cRajeshÎncă nu există evaluări

- 2-Phase Stepper-Motor Driver Bipolar-IC TLE4729G: FeaturesDocument29 pagini2-Phase Stepper-Motor Driver Bipolar-IC TLE4729G: FeaturesNgoc AnÎncă nu există evaluări

- Acrosser Technology AR B1673 DatasheetDocument5 paginiAcrosser Technology AR B1673 DatasheetWaleed MareeÎncă nu există evaluări

- Smart Octal Low-Side Switch: Features Product SummaryDocument16 paginiSmart Octal Low-Side Switch: Features Product SummaryAriel MercochaÎncă nu există evaluări

- An5092 Ais328dq Highperformance Ultralowpower 3axis Digital Output Accelerometer For Automotive Nonsafety Applications StmicroelectronicsDocument30 paginiAn5092 Ais328dq Highperformance Ultralowpower 3axis Digital Output Accelerometer For Automotive Nonsafety Applications Stmicroelectronicstomislav_darlicÎncă nu există evaluări

- Infineon Tle7230r Ds v03 04 enDocument15 paginiInfineon Tle7230r Ds v03 04 enياسين الطنفوريÎncă nu există evaluări

- TPS5125Document21 paginiTPS5125Shaun Dwyer Van HeerdenÎncă nu există evaluări

- Control de Garganta TACDocument15 paginiControl de Garganta TACmario rosasÎncă nu există evaluări

- NJU72341 NewJapanRadioDocument14 paginiNJU72341 NewJapanRadioPedro Carlos da SilvaÎncă nu există evaluări

- TLE6225GPDocument10 paginiTLE6225GPNoelÎncă nu există evaluări

- LED Step-Up Converter Data SheetDocument17 paginiLED Step-Up Converter Data SheetAbel GaunaÎncă nu există evaluări

- Wiring DiagramDocument4 paginiWiring DiagramDjalma MoreiraÎncă nu există evaluări

- Rp130X Series: Low Noise 150ma Ldo RegulatorDocument33 paginiRp130X Series: Low Noise 150ma Ldo RegulatorСергей БрегедаÎncă nu există evaluări

- Datasheet Diodo ZenerDocument22 paginiDatasheet Diodo ZenerAntonio Carlos CardosoÎncă nu există evaluări

- l438 Dual RegulatorDocument13 paginil438 Dual Regulatorjulio797Încă nu există evaluări

- Tle 62326 Low Side SwitchDocument19 paginiTle 62326 Low Side SwitchDiego CaceresÎncă nu există evaluări

- System Basis Chip T L E 6 2 6 6 G: Integrated LS CAN, LDO and LS - HS SwitchesDocument50 paginiSystem Basis Chip T L E 6 2 6 6 G: Integrated LS CAN, LDO and LS - HS Switchescork_ieÎncă nu există evaluări

- Tle 4726 IacDocument23 paginiTle 4726 Iacfreddys merchanÎncă nu există evaluări

- CD00081251Document15 paginiCD00081251Vladimir ParoleÎncă nu există evaluări

- NE/SA/SE5521 LVDT Signal Conditioner: Description Pin ConfigurationsDocument5 paginiNE/SA/SE5521 LVDT Signal Conditioner: Description Pin ConfigurationsAriel SanusiÎncă nu există evaluări

- IDBS07 and IDBM07 Wiring Manual: February 2008Document16 paginiIDBS07 and IDBM07 Wiring Manual: February 2008phankhoa83-1Încă nu există evaluări

- DC Motor Driver IC Controls Up to 1ADocument13 paginiDC Motor Driver IC Controls Up to 1Atigras6010Încă nu există evaluări

- Dual Power Operational Amplifier: Features DescriptionDocument10 paginiDual Power Operational Amplifier: Features DescriptionlyndondrÎncă nu există evaluări

- AP1509Document12 paginiAP1509Андрей ОлененкоÎncă nu există evaluări

- L6234 3 Fazlı Motor SürücüDocument10 paginiL6234 3 Fazlı Motor SürücüEngin UzunÎncă nu există evaluări

- MC2101 TM1628 PDFDocument22 paginiMC2101 TM1628 PDFPol ErnÎncă nu există evaluări

- Ne5521 Sa5521 2Document11 paginiNe5521 Sa5521 2José AdelinoÎncă nu există evaluări

- TLE6225GDocument9 paginiTLE6225GNoelÎncă nu există evaluări

- DatasheetDocument14 paginiDatasheetsamaya egÎncă nu există evaluări

- HTC Korea TAEJIN Tech CD4093BD - C510571Document9 paginiHTC Korea TAEJIN Tech CD4093BD - C510571SABBIR HOSSAINÎncă nu există evaluări

- AR-701B-X Fit 35mm DIN Rail or Mount Directly: CN1 CN2 CN3Document6 paginiAR-701B-X Fit 35mm DIN Rail or Mount Directly: CN1 CN2 CN3trisatriabÎncă nu există evaluări

- Trilithic Data Sheet Bts 7740 G: 1 1.1 FeaturesDocument17 paginiTrilithic Data Sheet Bts 7740 G: 1 1.1 FeaturesKrocodileÎncă nu există evaluări

- TPS7101Q PDFDocument40 paginiTPS7101Q PDFlittledropÎncă nu există evaluări

- ZXCDocument9 paginiZXCArda AkberkÎncă nu există evaluări

- TLE4279 SiemensSemiconductorGroupDocument19 paginiTLE4279 SiemensSemiconductorGroupLuis MezaÎncă nu există evaluări

- Tle5203 Motor Driver PDFDocument18 paginiTle5203 Motor Driver PDFJavier CuraÎncă nu există evaluări

- 3-A DC Motor Driver TLE 5203: SPT IcDocument18 pagini3-A DC Motor Driver TLE 5203: SPT IcJavier CuraÎncă nu există evaluări

- LP3211 LowpowersemiDocument6 paginiLP3211 LowpowersemiRafael BrunoÎncă nu există evaluări

- Aeg-Dvd4535 Service ManualDocument25 paginiAeg-Dvd4535 Service ManualSerp19720% (1)

- Sherwood RX-4105bDocument23 paginiSherwood RX-4105bGilberto0% (1)

- Digital Sound Processor IC with 64K SRAMDocument12 paginiDigital Sound Processor IC with 64K SRAMJaPan LifeÎncă nu există evaluări

- Infineon Bts3408g Ds v01 05 enDocument14 paginiInfineon Bts3408g Ds v01 05 enblessingj19it018Încă nu există evaluări

- Dmos Dual Full Bridge Driver: Multipower BCD TechnologyDocument11 paginiDmos Dual Full Bridge Driver: Multipower BCD TechnologyChristian BiancoÎncă nu există evaluări

- Tle 7259G PTM VWDocument28 paginiTle 7259G PTM VWSCANNER LABORAUTOÎncă nu există evaluări

- PCB DiagramDocument6 paginiPCB Diagramfreitastsp9166Încă nu există evaluări

- Apostila VolvoDocument72 paginiApostila VolvoMecaSoftwareÎncă nu există evaluări

- Acura MXD Acura MXD: Dashboard Photo: Dashboard Photo: Required Cable (S) : Required Cable (S)Document2 paginiAcura MXD Acura MXD: Dashboard Photo: Dashboard Photo: Required Cable (S) : Required Cable (S)MecaSoftwareÎncă nu există evaluări

- Aixam: Dashboard Photo: Dashboard Photo: Required Cable (S) : Required Cable (S)Document2 paginiAixam: Dashboard Photo: Dashboard Photo: Required Cable (S) : Required Cable (S)MecaSoftwareÎncă nu există evaluări

- Ariel Papercraft Printable 0210 - FDCOM PDFDocument2 paginiAriel Papercraft Printable 0210 - FDCOM PDFJocylinechrisÎncă nu există evaluări

- Belle Papercraft Printable 0210 FDCOMDocument2 paginiBelle Papercraft Printable 0210 FDCOMDennisSalvatoreÎncă nu există evaluări

- Acura MXD Acura MXD: Dashboard Photo: Dashboard Photo: Required Cable (S) : Required Cable (S)Document2 paginiAcura MXD Acura MXD: Dashboard Photo: Dashboard Photo: Required Cable (S) : Required Cable (S)MecaSoftwareÎncă nu există evaluări

- BU941 Bobina G7Document9 paginiBU941 Bobina G7MecaSoftwareÎncă nu există evaluări

- Mc68hc11a1 PDFDocument45 paginiMc68hc11a1 PDFRómulo Simón Lizarraga LeónÎncă nu există evaluări

- Datasheet 1354Document70 paginiDatasheet 1354Liliana SiscaÎncă nu există evaluări

- TIP41 NPN Transistor PDFDocument4 paginiTIP41 NPN Transistor PDFDiana GarciaÎncă nu există evaluări

- TLE4216G - Digifant 1.74Document15 paginiTLE4216G - Digifant 1.74MecaSoftwareÎncă nu există evaluări

- VB025 4SFDocument8 paginiVB025 4SFMecaSoftwareÎncă nu există evaluări

- Datasheet 1354Document70 paginiDatasheet 1354Liliana SiscaÎncă nu există evaluări

- 7 A H-Bridge for DC-Motor ApplicationsDocument29 pagini7 A H-Bridge for DC-Motor ApplicationsJoão JoséÎncă nu există evaluări

- 7 A H-Bridge For DC-Motor Applications TLE 7209-2R: Final DatasheetDocument32 pagini7 A H-Bridge For DC-Motor Applications TLE 7209-2R: Final DatasheetMecaSoftwareÎncă nu există evaluări

- TLE4216G - Digifant 1.74Document15 paginiTLE4216G - Digifant 1.74MecaSoftwareÎncă nu există evaluări

- VB026Document8 paginiVB026MecaSoftwareÎncă nu există evaluări

- 27C010 PDFDocument16 pagini27C010 PDFMecaSoftwareÎncă nu există evaluări

- O o o C o C: I Palio I Siena I StradaDocument1 paginăO o o C o C: I Palio I Siena I StradaMecaSoftwareÎncă nu există evaluări

- VND 7 N 04Document30 paginiVND 7 N 04Juan Guillermo MansillaÎncă nu există evaluări

- 24C02-8 EepromDocument16 pagini24C02-8 EepromJesus Almanzar SantosÎncă nu există evaluări

- RESUMEUPDATEDDocument2 paginiRESUMEUPDATEDsteven bianesÎncă nu există evaluări

- 3 N 71 BDocument4 pagini3 N 71 Bc.alfaro.sÎncă nu există evaluări

- 777 Design ArticleDocument16 pagini777 Design Articlesureshams100% (1)

- Instructions For Stow and Securing Steel CoilsDocument8 paginiInstructions For Stow and Securing Steel CoilsKhoai Sai GonÎncă nu există evaluări

- Cyprus National Annex en 1997-1Document16 paginiCyprus National Annex en 1997-1josifÎncă nu există evaluări

- ACA Fiber Optic AccessoriesDocument48 paginiACA Fiber Optic AccessoriesChiddarthan DhavidanÎncă nu există evaluări

- Pneumatic Control SystemsDocument4 paginiPneumatic Control SystemsRiyah_Rae100% (1)

- Apostila Desenho Mecanico 1 III ParteDocument12 paginiApostila Desenho Mecanico 1 III ParteVitor Rigueira de GodoyÎncă nu există evaluări

- ABB Project ExecutionDocument4 paginiABB Project ExecutionpamlidÎncă nu există evaluări

- O&M Manual For Tubular BatteriesDocument11 paginiO&M Manual For Tubular BatteriesAVIJIT MITRAÎncă nu există evaluări

- Siemens DP Profibus Connector 1Document2 paginiSiemens DP Profibus Connector 1kathreen mae fabianaÎncă nu există evaluări

- Project Specifications SummaryDocument3 paginiProject Specifications SummaryAe PocotÎncă nu există evaluări

- Auto Body BuildingDocument10 paginiAuto Body BuildingChirag SabhayaÎncă nu există evaluări

- Femto DevDocument1 paginăFemto DevKhalid AbnodeÎncă nu există evaluări

- Control units for irrigation motor pumpsDocument20 paginiControl units for irrigation motor pumpsMario StrašniÎncă nu există evaluări

- 06may2014 11Document44 pagini06may2014 11Raneesh MohamedÎncă nu există evaluări

- Engine 1 SpecificationsDocument5 paginiEngine 1 SpecificationsNeven SandicÎncă nu există evaluări

- List SSOP Rig 2 - Bridging DocumentDocument11 paginiList SSOP Rig 2 - Bridging DocumentRizki YanuarÎncă nu există evaluări

- Sample Dew Point CalculationDocument3 paginiSample Dew Point Calculationapi-3709413100% (1)

- Catter Pilatre SL Lant AsDocument31 paginiCatter Pilatre SL Lant Asjose33% (3)

- p072 Sysmac Catalogue enDocument418 paginip072 Sysmac Catalogue enKocsor AttilaÎncă nu există evaluări

- IGBC Green Cities RatingDocument86 paginiIGBC Green Cities RatingSampath NÎncă nu există evaluări

- PoloDocument45 paginiPolostripy101Încă nu există evaluări

- Mpofana Municipality General Valuation Roll - 31 March 2019Document144 paginiMpofana Municipality General Valuation Roll - 31 March 2019Sherebanu KajeeÎncă nu există evaluări

- Vitaulic Style 44 - 2 PDFDocument7 paginiVitaulic Style 44 - 2 PDFjoseÎncă nu există evaluări

- Understanding NPSHR to Prevent Cavitation DamageDocument2 paginiUnderstanding NPSHR to Prevent Cavitation Damageanwerosama0% (1)

- Mityvac Silverline MV8500 (Bomba de Vacío)Document2 paginiMityvac Silverline MV8500 (Bomba de Vacío)Anonymous 7W8uHgY3hÎncă nu există evaluări

- Apltcl040 SGD L-01Document136 paginiApltcl040 SGD L-01Waleed King100% (4)

- Breaker Rating (In) Correction Factors: Voltage Drop Calculation (Mcc23 Final Circuits)Document1 paginăBreaker Rating (In) Correction Factors: Voltage Drop Calculation (Mcc23 Final Circuits)shrikanth5singhÎncă nu există evaluări