Documente Academic

Documente Profesional

Documente Cultură

Black Fin Features

Încărcat de

vibhutepmDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Black Fin Features

Încărcat de

vibhutepmDrepturi de autor:

Formate disponibile

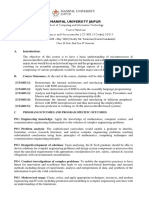

Embedded Microprocessors

Blackfin Processor Architecture Overview

Blackfin Processors are a new breed of 16-32-bit embedded microprocessor designed specifically to meet the

computational demands and power constraints of today's embedded audio, video and communications applications.

Based on the Micro Signal Architecture (MSA) jointly developed with Intel Corporation, Blackfin Processors combine

a 32-bit RISC-like instruction set and dual 16-bit multiply accumulate (MAC) signal processing functionality with the

ease-of-use attributes found in general-purpose microcontrollers. This combination of processing attributes enables

Blackfin Processors to perform equally well in both signal processing and control processing applications-in many

cases deleting the requirement for separate heterogeneous processors. This capability greatly simplifies both the

hardware and software design implementation tasks.

The Blackfin Processor family also offers industry leading power consumption performance down to 0.8V. This

combination of high performance and low power is essential in meeting the needs of today's and future signal

processing applications including broadband wireless, audio/video capable Internet appliances, and mobile

communications.

All Blackfin Processors offer fundamental benefits to the system designer which include:

High-performance signal processing and efficient control processing capability enabling a variety of new

markets and applications.

Dynamic Power Management (DPM) enabling the system designer to specifically tailor the device power

consumption profile to the end system requirements.

Easy to use mixed 16-/32-bit Instruction Set Architecture and development tool suite ensuring that product

development time is minimized.

High Performance Processor Core

The Blackfin Processor architecture is based upon a 10-stage RISC MCU/DSP pipeline with a mixed 16-/32-bit

Instruction Set Architecture designed for optimal code density. Blackfin processors architecture is also fully SIMD

compliant and includes instructions for accelerated video and image processing. The architecture is well suited for full

signal processing / analytical capabilities while also offering efficient RISC MCU control tasking capabilities - on either

a single or dual core device. With the optimal code density and the possibility of little to no code optimization, quicker

time to market can be achieved without running into performance headroom barriers seen on other traditional

processor.

High Bandwidth DMA Capability

All Blackfin Processors have multiple, independent DMA controllers that support automated data transfers with

minimal overhead from the processor core. DMA transfers can occur between the internal memories and any of the

many DMA-capable peripherals. Transfers can also occur between the peripherals and external devices connected to

the external memory interfaces, including the SDRAM controller and the asynchronous memory controller.

Video Instructions

In addition to native support for 8-bit data, the word size common to many pixel processing algorithms, the Blackfin

Processor architecture includes instructions specifically defined to enhance performance in video processing

applications. For example, Discrete Cosine Transform (DCT) is supported with an IEEE 1180 rounding operation,

while the "SUM ABSOLUTE DIFFERENCE" instruction supports motion estimation algorithms used in video

compression algorithms such as MPEG2, MPEG4, and JPEG.

Implementing video compression algorithms in software allows OEMs to adapt to evolving standards and new

functional requirements without hardware changes. The enhanced instructions allow Blackfin Processors to be

considered in applications previously addressed primarily by ASICs, VLIW media processors or hardwired chipsets.

Ultimately, Blackfin Processors will help lower overall system cost while improving the time to market for the end

application.

Efficient Control Processing

The Blackfin Processor architecture also offers a variety of benefits most often seen in RISC control processors.

These features include a powerful and flexible hierarchical memory architecture, superior code density, and a variety

of microcontroller-style peripherals including items such as 10/100 Ethernet MAC, UARTS, SPI, CAN controller,

Timers with PWM support, Watchdog Timer, Real-Time Clock, and a glueless synchronous and asynchronous

memory controller. All of these features provide the system designer with a great deal of design flexibility while

minimizing end system costs.

Hierarchical Memory

The Blackfin Processor memory architecture provides for both Level 1 (L1) and Level 2 (L2) memory blocks in device

implementations. The L1 memory is connected directly to the processor core, runs at full system clock speed, and

offers maximum system performance for time critical algorithm segments. The L2 memory is a larger, bulk memory

storage block that offers slightly reduced performance, but still faster than off-chip memory.

The L1 memory structure has been implemented to provide the performance needed for signal processing while

offering the programming ease found in general purpose microcontrollers. This is accomplished by allowing the L1

memory to be configured as SRAM, cache, or a combination of both. By supporting both SRAM and cache

programming models, system designers can allocate critical real time signal processing data sets that require high

bandwidth and low latency into SRAM, while storing more 'soft' real time control / OS tasks in the cache memory.

The Memory Management Unit provides for a memory protection format that, when coupled with the core's User and

Supervisor modes, can support a full Real Time Operating System. The RTOS runs in Supervisor mode and

partitions blocks of memory and other system resources for the actual application software to run in User mode.

Thus, the MMU offers an isolated and secure environment for robust systems and applications.

Superior Code Density

The Blackfin Processor architecture supports multi-length instruction encoding. Very frequently used control-type

instructions are encoded as compact 16-bit words, with more mathematically intensive signal processing instructions

encoded as 32-bit values. The processor will intermix and link 16-bit control instructions with 32-bit signal processing

instructions into 64-bit groups to maximize memory packing. When caching and fetching instructions, the core

automatically fully packs the length of the bus because it does not have alignment constraints. When combined,

these two features enable Blackfin Processors to deliver code density benchmarks comparable to industry-leading

RISC processors.

Dynamic Power Management

All Blackfin Processors employ multiple power saving techniques. Blackfin Processors are based on a gated clock

core design that selectively powers down functional units on an instruction-by-instruction basis. Blackfin Processors

also support multiple power-down modes for periods where little or no CPU activity is required. Lastly, and probably

most importantly, these embedded microprocessors support a self contained dynamic power management scheme

whereby the operating frequency AND voltage can be independently manipulated to meet the performance

requirements of the algorithm currently being executed. These transitions may occur continually under the control of

an RTOS or user firmware. Most Blackfin processors offer on-chip core voltage regulation circuitry as well as

operation to as low as 0.8V and are particularly well suited for portable applications requiring extended battery life.

Easy to Use

A single Blackfin Processor can be utilized in many applications previously requiring both a high performance signal

processor and a separate efficient control processor. This benefit greatly reduces development time and costs,

ultimately enabling end products to get to market sooner. Additionally, a single set of development tools can be used,

which decreases the system designer's initial expenses and learning curve.

S-ar putea să vă placă și

- EmbeddedDocument1 paginăEmbeddedvibhutepmÎncă nu există evaluări

- Wa0005 PDFDocument2 paginiWa0005 PDFsrinivasanÎncă nu există evaluări

- WritingDocument1 paginăWritingvibhutepmÎncă nu există evaluări

- MATLAB FundamentalsDocument4 paginiMATLAB FundamentalsvibhutepmÎncă nu există evaluări

- Ieee Accident Identification System Via Sms NotificationDocument3 paginiIeee Accident Identification System Via Sms NotificationvibhutepmÎncă nu există evaluări

- Arduino Comic v0004Document15 paginiArduino Comic v0004serf007Încă nu există evaluări

- Arduino : Is The Go-To Gear For Artists, Hobbyists, Students, and Anyone With A Gadgetry DreamDocument84 paginiArduino : Is The Go-To Gear For Artists, Hobbyists, Students, and Anyone With A Gadgetry DreamvibhutepmÎncă nu există evaluări

- To DoDocument1 paginăTo DovibhutepmÎncă nu există evaluări

- Engineers Mini NotebookDocument80 paginiEngineers Mini NotebookvibhutepmÎncă nu există evaluări

- Mnproject Abstract FormatDocument1 paginăMnproject Abstract FormatvibhutepmÎncă nu există evaluări

- Arduino Notebook v1-1Document25 paginiArduino Notebook v1-1vibhutepmÎncă nu există evaluări

- Virtual Lab User's ManualDocument24 paginiVirtual Lab User's ManualSourav KarthickÎncă nu există evaluări

- Raspberry Pie An Introduction 2Document20 paginiRaspberry Pie An Introduction 2vibhutepmÎncă nu există evaluări

- Mini Project Record For Group - LatestDocument2 paginiMini Project Record For Group - LatestvibhutepmÎncă nu există evaluări

- Mini Project Record For Group - LatestDocument2 paginiMini Project Record For Group - LatestvibhutepmÎncă nu există evaluări

- All SCI PublicationDocument342 paginiAll SCI PublicationvibhutepmÎncă nu există evaluări

- Me - Electronics Digital System PDFDocument23 paginiMe - Electronics Digital System PDFSanjay KanadeÎncă nu există evaluări

- Readme EnglishDocument1 paginăReadme EnglishvibhutepmÎncă nu există evaluări

- Embedded Training Cover ManualDocument1 paginăEmbedded Training Cover ManualvibhutepmÎncă nu există evaluări

- Message From ApjDocument4 paginiMessage From ApjvibhutepmÎncă nu există evaluări

- M.E. (E & TC) Course Structure for Signal ProcessingDocument59 paginiM.E. (E & TC) Course Structure for Signal ProcessingvibhutepmÎncă nu există evaluări

- DAQDocument8 paginiDAQvibhutepmÎncă nu există evaluări

- Network Statistical AnalysisDocument19 paginiNetwork Statistical AnalysisvibhutepmÎncă nu există evaluări

- Message From ApjDocument4 paginiMessage From ApjvibhutepmÎncă nu există evaluări

- Message From ApjDocument4 paginiMessage From ApjvibhutepmÎncă nu există evaluări

- Enhanced Method For Identification of Objects Class and Qualities in Real Images-PaperDocument9 paginiEnhanced Method For Identification of Objects Class and Qualities in Real Images-PapervibhutepmÎncă nu există evaluări

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (587)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (399)

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (73)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5794)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2219)

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (344)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (265)

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (119)

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)

- SXCheck Version 1.02Document6 paginiSXCheck Version 1.02Joyce ShiÎncă nu există evaluări

- Unit VI 80386DX Signals, Bus Cycles, 80387 CoprocessorDocument26 paginiUnit VI 80386DX Signals, Bus Cycles, 80387 CoprocessorShanti GuruÎncă nu există evaluări

- Old Paper - 202201 - A6-R5 - COMPUTER ORGANIZATION AND OPERATING SYSTEMDocument8 paginiOld Paper - 202201 - A6-R5 - COMPUTER ORGANIZATION AND OPERATING SYSTEMJacks LibrearyÎncă nu există evaluări

- Chapter 08 Processor DesignDocument71 paginiChapter 08 Processor DesignJohn De ShelbyÎncă nu există evaluări

- Instruction TablesDocument469 paginiInstruction Tablesreklamyspam02Încă nu există evaluări

- Assembly LanguageDocument199 paginiAssembly LanguagejharidasÎncă nu există evaluări

- Commodore 64 Programmer's Reference GuideDocument409 paginiCommodore 64 Programmer's Reference GuideMoe B. Us100% (7)

- 5th To 8trh Sem ECE SyllabusDocument45 pagini5th To 8trh Sem ECE Syllabusapi-3856240100% (2)

- The Digital Computer Accepts - Data As InputDocument43 paginiThe Digital Computer Accepts - Data As InputPradip Kumar PanditÎncă nu există evaluări

- Indirect Addressing S5 S7Document35 paginiIndirect Addressing S5 S7xl_hamo0% (1)

- Microprocessor-Based Agri Instrumentation: Krishna KantDocument11 paginiMicroprocessor-Based Agri Instrumentation: Krishna Kantmarikumar289Încă nu există evaluări

- Organization of The IBM PC Assembly LanguageDocument13 paginiOrganization of The IBM PC Assembly LanguageAsadullah KhanÎncă nu există evaluări

- A Secured Approach For Authentication System Using Fingerprint and IrisDocument6 paginiA Secured Approach For Authentication System Using Fingerprint and IrisKotteshwari KottiÎncă nu există evaluări

- MIPS Based On AESDocument5 paginiMIPS Based On AESSehar ChÎncă nu există evaluări

- Assignment 1 2020coaDocument5 paginiAssignment 1 2020coaAmit ChinaraÎncă nu există evaluări

- Computer - Britannica Online Encyclopedia PDFDocument79 paginiComputer - Britannica Online Encyclopedia PDFRodrigo Muñoz AcevedoÎncă nu există evaluări

- XXXXX: Important Instructions To ExaminersDocument21 paginiXXXXX: Important Instructions To ExaminersYogesh DumaneÎncă nu există evaluări

- 21 Network Programmability and AutomationDocument19 pagini21 Network Programmability and AutomationOsama DsokyÎncă nu există evaluări

- Microprocessors (Bcst601)Document61 paginiMicroprocessors (Bcst601)surbhiÎncă nu există evaluări

- William Stallings Computer Organization and Architecture 10 EditionDocument10 paginiWilliam Stallings Computer Organization and Architecture 10 EditionAhmed AyazÎncă nu există evaluări

- 8086 Microprocessor ProjectDocument11 pagini8086 Microprocessor ProjectJanhavi DongreÎncă nu există evaluări

- ACA Assignment 4Document16 paginiACA Assignment 4shresth choudharyÎncă nu există evaluări

- MPMC Theory Handout CS1403Document7 paginiMPMC Theory Handout CS1403John CameronÎncă nu există evaluări

- Expand What's Possible With PlandPAx 5.0Document34 paginiExpand What's Possible With PlandPAx 5.0Tim DuncanÎncă nu există evaluări

- Carnegie Mellon Machine Level Programming BasicsDocument55 paginiCarnegie Mellon Machine Level Programming BasicsGrace Bautista UrsuaÎncă nu există evaluări

- R30X Series Fingerprint Identification Module User ManualDocument26 paginiR30X Series Fingerprint Identification Module User ManualR. RagulÎncă nu există evaluări

- 4 CH Counter Input Module (4634)Document32 pagini4 CH Counter Input Module (4634)Ganesh TokeÎncă nu există evaluări

- MBSD - EE6008 - Answer Key - University ExamDocument17 paginiMBSD - EE6008 - Answer Key - University ExampraveenaÎncă nu există evaluări

- The JCC Instructions: Computer Organization and Assembly LanguageDocument19 paginiThe JCC Instructions: Computer Organization and Assembly LanguageammerÎncă nu există evaluări

- SDRDocument44 paginiSDRRameez AhamedÎncă nu există evaluări