Documente Academic

Documente Profesional

Documente Cultură

MOSFET Gate Driver

Încărcat de

Electrical-Engineer100%(1)100% au considerat acest document util (1 vot)

1K vizualizări2 paginiLearn why Gate Drivers are needed to drive MOSFET's.

Drepturi de autor

© Attribution Non-Commercial (BY-NC)

Formate disponibile

PDF, TXT sau citiți online pe Scribd

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentLearn why Gate Drivers are needed to drive MOSFET's.

Drepturi de autor:

Attribution Non-Commercial (BY-NC)

Formate disponibile

Descărcați ca PDF, TXT sau citiți online pe Scribd

100%(1)100% au considerat acest document util (1 vot)

1K vizualizări2 paginiMOSFET Gate Driver

Încărcat de

Electrical-EngineerLearn why Gate Drivers are needed to drive MOSFET's.

Drepturi de autor:

Attribution Non-Commercial (BY-NC)

Formate disponibile

Descărcați ca PDF, TXT sau citiți online pe Scribd

Sunteți pe pagina 1din 2

P O W E R to achieve full turn-on.

It is usually

specified in nanocoulombs (nC).

How does the gate driver affect

MOSFET switching speed?

The Miller effect produced by

MOSFET CGD is what predomi-

nantly limits switching speed. A

MOSFET responds instantaneously

to changes in gate voltage and begins

to conduct when the gate reaches the

Frequently Asked Questions: threshold voltage (VGS). To address

a wide range of applications, suppli-

ers offer a variety of power

MOSFETs that transition

POWER-MOSFET GATE DRIVERS at different gate thresholds,

such as logic-level

MOSFETs with

Sam Davis, Contributing Editor lower threshold

Drain

1. Simplified voltage. Gate

What is a power-MOSFET model of non-invert-

Power MOSFET

waveforms indi-

gate driver? ing gate-driver IC LD

cate a plateau at

It is a power amplifier that and power MOSFET a gate voltage

accepts a low-power input from a above the

controller IC and produces the CGD threshold volt-

CDS

appropriate high-current gate R

age. The time

Controller Gate Gate G

drive for a power MOSFET. A input

required to drive

driver

gate driver is used when a pulse- the gate through

width-modulation (PWM) con- CGS this plateau

troller cannot provide the output region depends

current required to drive the gate LS on the amount

capacitance of the associated MOSFET. Gate drivers of drive current

may be implemented as dedicated ICs, discrete transis- available, which

Source

tors, or transformers. They can also be integrated within determines the

a controller IC. Partitioning the gate-drive function off MOSFET’s

the PWM controller allows the controller to run cooler and be more stable drain-voltage rise and fall times.

by eliminating the high peak currents and heat dissipation needed to drive a

power MOSFET at very high frequencies. What about discrete drivers?

Discrete gate drivers constructed

What’s the circuit model for a gate driver and power MOSFET? with bipolar npn and pnp emitter-

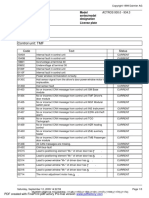

Figure 1 shows the simplified model, including the parasitic components followers can achieve reasonable

that influence high-speed switching, gate-to-source capacitance (CGS), the drive capability, but they’re not as

gate-to-drain capacitance (CGD), and drain-to-source capacitance (CDS). space-efficient as gate-driver ICs.

Values of the source inductance (LS) and drain inductance (LD) depend on Implementing delay and other

the MOSFET’s package. The other parasitic housekeeping

component is RG, the resistance associated functions need-

with the gate signal distribution within the ed for safe oper-

MOSFET that affects switching times. ation is cumber-

some and costly

What are the primary gate-driver with a discrete

VGS, gate-to-source voltage (V)

design considerations? circuit. The

An important attribute for the gate driver is gate-driver IC

its ability to provide sufficient drive current to overcomes these

quickly pass through the Miller Plateau limitations.

Region of the power-MOSFET’s switching

transition. This interval occurs when the tran- What about

sistor is being driven on or off, and the volt- IC drivers?

age across its gate-to-drain parasitic capacitor Gate-driver ICs

(CGD) is being charged or discharged by the include a logic

gate driver. Figure 2 plots total gate charge as input buffer that

QG, total gate charge (nC)

a function of the gate-drive voltage of a power drives sufficient

MOSFET. Total gate charge (QG) is how current-gain

much must be supplied to the MOSFET gate 2. Power MOSFET gate-drive characteristics stages to pro-

Sponsored by National Semiconductor Corp.

ADVERTISEMENT

duce a high-current output. In addi-

tion, the dedicated gate-driver IC can

include the housekeeping functions

needed for safe operation. Also, it can

be easily placed closer to the power

MOSFET, thereby reducing noise

interference and voltage-distribution

drops across the pc-board trace.

Single versus dual channels? NATIONAL’S HIGH-VOLTAGE GATE DRIVER FAMILY

There are single gate-driver ICs

whose output is either inverting or LM5100/01 Gate Drivers

non-inverting with respect to the The LM5100/LM5101 are high-voltage gate drivers for the high-side

controller input. Some single-chan- and low-side n-channel MOSFETs in a synchronous buck or bridge con-

nel gate drivers provide both invert- figuration. The floating high-side driver can operate with supplies up to

ing and non-inverting inputs. In 100 V. Outputs are independently controlled with CMOS input thresh-

addition, there are dual gate-driver olds (LM5100) or TTL-input thresholds (LM5101). Both the low-side

ICs with either two inverting, two and the high-side power rails include undervoltage lockout. Turn-off

non-inverting, or one inverting and propagation delay is 25 ns (typical), and the ICs can drive 1000-pF loads

one non-inverting channel. with 15-ns rise and fall times.

What influences gate-driver-IC LM5102 With Programmable Delay

lifetime and performance? The LM5102 is similar to the LM5100 with the addition of a program-

Load power requirements, thermal mable delay for adjusting driver dead time. The LM5102 offers the flexi-

characteristics of the semiconductor bility of an independent programmable delay of the rising edge for both

package and its cooling method high- and low-side driver outputs. Delays are set with external resistors

determine the lifetime and perform- and can be adjusted from 100 ns to 600 ns. The wide delay program-

ance of a gate-driver IC. The device’s ming range provides the flexibility to optimize drive signal timing for a

junction temperature must be kept broad range of MOSFETs and applications. In addition, the timer can be

within the rated limit at all times. terminated midway through a sequence.

What about designing for syn- LM5104 With Adaptive Delay

chronous rectification? The LM5104 is similar to the LM5100 with the addition of an adaptive

Shoot-through current is a poten- delay to prevent shoot-through. The high-side and low-side gate drivers

tial problem for MOSFETs used in are controlled from a single input. Each change in state is controlled in

synchronous rectification. Because an adaptive manner to turn off one MOSFET before the other is turned

the gate driver must turn on and off on. Besides the adaptive transition timing, an additional delay time can

not only the power switch but also be added, inversely proportional to an external setting resistor. The adap-

the rectifier switch, a low impedance tive control and additional delay of the timer prevent lower and upper

may be presented to the input volt- MOSFETs from conducting simultaneously.

age source during switching transi-

tions. This low transition impedance LM5110 Dual-Gate Driver

can allow a shoot-through current The LM5110 replaces industry-standard

to be conducted through both the gate drivers with improved peak output

power-switching MOSFET and the current and efficiency. Each "compound"

synchronous-rectifier MOSFETs. output driver stage includes MOS and

High shoot-through currents result bipolar transistors operating in parallel

in greater electromagnetic interfer- that together sink more than 5-A peak

ence, more noise on the input volt- from capacitive loads. Combining the

age source, lower efficiency, and unique characteristics of MOS and bipo-

reduced reliability. lar devices reduces drive current variation

Some gate-driver ICs include a with voltage and temperature. Separate input and output ground pins

non-overlap circuit that prevents provide negative drive capability, allowing the user to drive MOSFET

shoot-through current. Other ICs gates with positive and negative VGS. The gate driver control inputs are

specify a minimum amount of non- referenced to a dedicated input ground.

overlap, or dead-time. That is, a

minimum time at the switching tran-

sitions (two per operating cycle) For free online design tools, samples,

where both MOSFETs are turned off.

Maintaining the dead-time prevents evaluation boards, datasheets and more,

the problem of shoot-through current BE SURE TO VISIT:

but reduces circuit efficiency from its

optimum value. ED Online 8415 power.national.com

S-ar putea să vă placă și

- Driving Transistors and ThyristorsDocument11 paginiDriving Transistors and ThyristorsEugenio NanniÎncă nu există evaluări

- AN805 - PWM Optimized Power MOSFETsDocument7 paginiAN805 - PWM Optimized Power MOSFETsDanny AlonsoÎncă nu există evaluări

- Slva 714 DDocument24 paginiSlva 714 DMarcio WjbÎncă nu există evaluări

- MOSFET Gate Drive Circuit Design Considerations For Integrated High Switching Frequency Buck ConverterDocument7 paginiMOSFET Gate Drive Circuit Design Considerations For Integrated High Switching Frequency Buck ConvertermikeÎncă nu există evaluări

- Design Considerations For A Fast Stacked-MOSFET SwitchDocument7 paginiDesign Considerations For A Fast Stacked-MOSFET SwitchBruna RibeiroÎncă nu există evaluări

- Unit 01Document21 paginiUnit 01mathanstar77Încă nu există evaluări

- How To Drive Mosfets and Igbts Into The 21St Century: IXAN0009Document28 paginiHow To Drive Mosfets and Igbts Into The 21St Century: IXAN0009mmÎncă nu există evaluări

- Mosfet SDocument42 paginiMosfet Sricardo martinezÎncă nu există evaluări

- Chapter 7 - Driving Thytistors and TransistorsDocument11 paginiChapter 7 - Driving Thytistors and Transistorsmitros100% (2)

- Fairchild AN-6069 PDFDocument14 paginiFairchild AN-6069 PDFtiohbengchuanÎncă nu există evaluări

- Is Now Part ofDocument14 paginiIs Now Part ofchatty85Încă nu există evaluări

- Isolated Mosfet Gate Driver PaperDocument6 paginiIsolated Mosfet Gate Driver PapergenwittsÎncă nu există evaluări

- Gate Driver NotesDocument2 paginiGate Driver NotesBeng FoongÎncă nu există evaluări

- Power MOSFET Basics: by Vrej Barkhordarian, International Rectifier, El Segundo, CaDocument2 paginiPower MOSFET Basics: by Vrej Barkhordarian, International Rectifier, El Segundo, Cadfg dfgÎncă nu există evaluări

- University of California at Berkeley College of Engineering Department of Electrical Engineering and Computer SciencesDocument3 paginiUniversity of California at Berkeley College of Engineering Department of Electrical Engineering and Computer Sciencesvp agutamÎncă nu există evaluări

- Linear Power MOSFETs 2007Document4 paginiLinear Power MOSFETs 2007Robert DenchÎncă nu există evaluări

- Slup 097Document15 paginiSlup 097Can IlicaÎncă nu există evaluări

- Amplicadores DiseñoDocument3 paginiAmplicadores DiseñoEmer nelsonÎncă nu există evaluări

- Design - and - Fabrication - of - Regulated - DC - Electronic - Load - For - Testing - Power - Supplies - and - Batteries (3) UM POUCO MAIS SIMPLESDocument6 paginiDesign - and - Fabrication - of - Regulated - DC - Electronic - Load - For - Testing - Power - Supplies - and - Batteries (3) UM POUCO MAIS SIMPLESLuis KolbaÎncă nu există evaluări

- Application Note Anp20Document15 paginiApplication Note Anp20Raka Satria PradanaÎncă nu există evaluări

- How Did You Drive The MOSFETS?: Bargunan PonnusamyDocument2 paginiHow Did You Drive The MOSFETS?: Bargunan PonnusamyvineetÎncă nu există evaluări

- L-6 (DK) (Pe) ( (Ee) Nptel) 8Document3 paginiL-6 (DK) (Pe) ( (Ee) Nptel) 8GagneÎncă nu există evaluări

- gm07652r PDFDocument21 paginigm07652r PDFjose luisÎncă nu există evaluări

- Lectura 3 M PDFDocument12 paginiLectura 3 M PDFFlakita S MelcOchitaÎncă nu există evaluări

- DM0565RDocument20 paginiDM0565RSURESH CHANDRA ROUTÎncă nu există evaluări

- Power - MOSFET - and - IGBTDocument23 paginiPower - MOSFET - and - IGBTnkaÎncă nu există evaluări

- B.E.-vi Semester-Power Electronics LabDocument68 paginiB.E.-vi Semester-Power Electronics LabNanda Kishore PNÎncă nu există evaluări

- Design For A Gate-Driver CircuitDocument27 paginiDesign For A Gate-Driver Circuitdhruv100% (1)

- Exp7 Mosfet ConfigurationDocument14 paginiExp7 Mosfet ConfigurationAyeshaÎncă nu există evaluări

- Estimating Maximum Mosfet Switching FrequencyDocument5 paginiEstimating Maximum Mosfet Switching FrequencyFlavio AlmeidaÎncă nu există evaluări

- LDO FastsettlingDocument5 paginiLDO FastsettlingKini FamilyÎncă nu există evaluări

- ECE131 Unit4 Part 2Document79 paginiECE131 Unit4 Part 2Vana PraveenÎncă nu există evaluări

- Datasheet DMO565RDocument21 paginiDatasheet DMO565RSteve Bravo83% (6)

- Integrated Multi-Channel DC-DC Converter For TFT-LCD Panels: Global Mixed-Mode Technology IncDocument2 paginiIntegrated Multi-Channel DC-DC Converter For TFT-LCD Panels: Global Mixed-Mode Technology IncBuddhika Gihan WijerathneÎncă nu există evaluări

- Mosfet (J.B Gupta)Document13 paginiMosfet (J.B Gupta)rik banerjeeÎncă nu există evaluări

- Controlling Switch-Node Ringing in Synchronous Buck ConvertersDocument5 paginiControlling Switch-Node Ringing in Synchronous Buck ConvertersDmytro RakÎncă nu există evaluări

- Small Signal AnalysisDocument62 paginiSmall Signal AnalysissathviksolletiÎncă nu există evaluări

- Mosoft Circuit ApplicationDocument16 paginiMosoft Circuit Applicationkaran007_mÎncă nu există evaluări

- Power MOSFET Electrical CharacteristicsDocument11 paginiPower MOSFET Electrical CharacteristicsMarco FajardoÎncă nu există evaluări

- Desing NandDocument4 paginiDesing NandDavid Villamarin RiveraÎncă nu există evaluări

- AR313 Application Note MRF141GDocument6 paginiAR313 Application Note MRF141GerdemsecenÎncă nu există evaluări

- Design of Cmos Multistage High Gain Differential Amplifier Using CadenceDocument4 paginiDesign of Cmos Multistage High Gain Differential Amplifier Using CadenceAbdulrahman behiryÎncă nu există evaluări

- Final Paper 2007Document7 paginiFinal Paper 2007durrani shaheerÎncă nu există evaluări

- An 944Document5 paginiAn 944John CareyÎncă nu există evaluări

- MCTDocument9 paginiMCTChristine GomezÎncă nu există evaluări

- HEXFETs Power MOSFETsDocument22 paginiHEXFETs Power MOSFETsMiguel PenarandaÎncă nu există evaluări

- An 6003Document6 paginiAn 6003jesse_w_petersÎncă nu există evaluări

- 2marks Unit1Document4 pagini2marks Unit1Sinan SinanÎncă nu există evaluări

- 60 GHZ OOK Transmitter in 32 NM DG FinFET TechnologyDocument4 pagini60 GHZ OOK Transmitter in 32 NM DG FinFET TechnologyHARSHITHA R Ece-2019-23Încă nu există evaluări

- Controlling Inrush Current in High Demanding ApplicationsDocument10 paginiControlling Inrush Current in High Demanding ApplicationsFelipe MederosÎncă nu există evaluări

- Vlsi Mosfet 8-4-2021Document11 paginiVlsi Mosfet 8-4-2021GaneshÎncă nu există evaluări

- Isolated Gate Driver For SiC MOSFETs With Constant Negative Off VoltageDocument4 paginiIsolated Gate Driver For SiC MOSFETs With Constant Negative Off VoltageHainan DingÎncă nu există evaluări

- Dual Full-Bridge MOSFET Driver With Microstepping TranslatorDocument18 paginiDual Full-Bridge MOSFET Driver With Microstepping TranslatorОлег ПрохоренкоÎncă nu există evaluări

- Infineon-Application Note Applications For Depletion MOSFETs-AN-v01 00-ENDocument10 paginiInfineon-Application Note Applications For Depletion MOSFETs-AN-v01 00-ENvictorhugoseÎncă nu există evaluări

- An 4102 PDFDocument16 paginiAn 4102 PDFOmprakash DagarÎncă nu există evaluări

- Unit 4Document45 paginiUnit 4321910402038 gitamÎncă nu există evaluări

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2De la EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Încă nu există evaluări

- SPANNING TREE PROTOCOL: Most important topic in switchingDe la EverandSPANNING TREE PROTOCOL: Most important topic in switchingÎncă nu există evaluări

- Protection Guide enDocument74 paginiProtection Guide enEmad100% (28)

- Computer NetworkDocument63 paginiComputer NetworkElectrical-EngineerÎncă nu există evaluări

- Safety Considerations of Wireless Charger For EVDocument11 paginiSafety Considerations of Wireless Charger For EVElectrical-EngineerÎncă nu există evaluări

- Castes in PunjabDocument363 paginiCastes in PunjabElectrical-Engineer100% (2)

- 01 - Electric Powertrain Structures BaseDocument4 pagini01 - Electric Powertrain Structures BaseElectrical-EngineerÎncă nu există evaluări

- Constitution of Pakistan 1973 in Urdu VerDocument256 paginiConstitution of Pakistan 1973 in Urdu Vermuradlaghari82% (159)

- Carbon and Hydrogen StorageDocument12 paginiCarbon and Hydrogen StorageElectrical-Engineer100% (1)

- Micro Controller Based UPSDocument82 paginiMicro Controller Based UPSElectrical-Engineer100% (4)

- LT Capacitor Intervention at MEPCODocument3 paginiLT Capacitor Intervention at MEPCOElectrical-EngineerÎncă nu există evaluări

- Standalone Circuit Converts Square Waves To Sine WavesDocument2 paginiStandalone Circuit Converts Square Waves To Sine WavesCristian LiviuÎncă nu există evaluări

- Pulse Width ModulationDocument6 paginiPulse Width ModulationElectrical-EngineerÎncă nu există evaluări

- ThyristorDocument13 paginiThyristorElectrical-Engineer100% (1)

- PWM InvertersDocument17 paginiPWM InvertersElectrical-Engineer100% (1)

- Electrical SafetyDocument7 paginiElectrical SafetyElectrical-Engineer71% (7)

- Hino 700 Exhaust Brake-Engine Retarder WireingDocument2 paginiHino 700 Exhaust Brake-Engine Retarder Wireingg.shien5150100% (1)

- Breaker Failure Protection RAICADocument8 paginiBreaker Failure Protection RAICAGeorge AsuncionÎncă nu există evaluări

- Annexure To Start-Up & Commissioning of Fire Water PumpsDocument5 paginiAnnexure To Start-Up & Commissioning of Fire Water PumpsMina KhalilÎncă nu există evaluări

- RR RD5700SDocument1 paginăRR RD5700ShugoamendozaÎncă nu există evaluări

- Design For Low PowerDocument19 paginiDesign For Low PowerStudent0% (1)

- 8997 6956 00 Diagrams and DrawingsDocument74 pagini8997 6956 00 Diagrams and DrawingseduamaÎncă nu există evaluări

- Buck ConverterDocument31 paginiBuck Converterbalak144Încă nu există evaluări

- VSTPP Transformer Failures at VindhyachalDocument96 paginiVSTPP Transformer Failures at VindhyachalSam100% (1)

- Aa88e-Ibs 181227 (En+cn)Document52 paginiAa88e-Ibs 181227 (En+cn)aviantaraÎncă nu există evaluări

- Catalogo Productos Merten Schneider KNX ISC02052EN - 2010Document95 paginiCatalogo Productos Merten Schneider KNX ISC02052EN - 2010jjjjÎncă nu există evaluări

- Firefly LED LightingDocument6 paginiFirefly LED Lightingkhraieric16Încă nu există evaluări

- Flyback Transformer Leakage Inductance, Part 1: by Dennis L FeuchtDocument0 paginiFlyback Transformer Leakage Inductance, Part 1: by Dennis L FeuchtfuzakaÎncă nu există evaluări

- 1132 E EST 6 Project Work Conveyor Belt ControlDocument14 pagini1132 E EST 6 Project Work Conveyor Belt ControlSai RayapatiÎncă nu există evaluări

- Mechatronics Case StudyDocument7 paginiMechatronics Case Studyyogeesh_sharmaÎncă nu există evaluări

- Stormwater: (Interlocking Joint) - SANS 677Document1 paginăStormwater: (Interlocking Joint) - SANS 677Ephraim BarezÎncă nu există evaluări

- Set Rec Pic 827Document2 paginiSet Rec Pic 827Peter SalimÎncă nu există evaluări

- 2008-2009 GM Magna Transfer Case Detailed Info, Bulletin # 1226Document10 pagini2008-2009 GM Magna Transfer Case Detailed Info, Bulletin # 1226davidÎncă nu există evaluări

- CPSG 110 60hz en Cummins 6r5.9lDocument2 paginiCPSG 110 60hz en Cummins 6r5.9lErick Domínguez CansecoÎncă nu există evaluări

- 051790c0.sch-1 - Tue May 21 09:07:19 2002Document19 pagini051790c0.sch-1 - Tue May 21 09:07:19 2002Italo BocattuÎncă nu există evaluări

- SmartLine020-4 CoP 0051-CPR-1413 20181121 EN PDFDocument2 paginiSmartLine020-4 CoP 0051-CPR-1413 20181121 EN PDFDiego GodinesÎncă nu există evaluări

- T2500Document2 paginiT2500kylegazeÎncă nu există evaluări

- MkIV Failure CodesDocument12 paginiMkIV Failure Codesjaypc1050% (2)

- Types of MemoryDocument3 paginiTypes of MemoryVenkatareddy Mula0% (1)

- 27.classroom Objects BDocument21 pagini27.classroom Objects BAleksandra VuÎncă nu există evaluări

- Configuration Diagrams: Group 80ADocument20 paginiConfiguration Diagrams: Group 80ALuis Guillermo Ledezma CastroÎncă nu există evaluări

- Current Fault Codes: Code Text StatusDocument3 paginiCurrent Fault Codes: Code Text StatusnaftaliÎncă nu există evaluări

- LIT 11626 22 71 - Zuma125 - 1663 PDFDocument88 paginiLIT 11626 22 71 - Zuma125 - 1663 PDFMatius Ger CharrysÎncă nu există evaluări

- PIC Base A9Document28 paginiPIC Base A9Alfonso NiñoÎncă nu există evaluări

- VNHD7008AY: H-Bridge Motor Driver For Automotive DC Motor DrivingDocument44 paginiVNHD7008AY: H-Bridge Motor Driver For Automotive DC Motor DrivingFırat Dede (Robotus)Încă nu există evaluări

- User Manual All JET-TECH ModelsDocument32 paginiUser Manual All JET-TECH ModelsAllen ZhangÎncă nu există evaluări