Documente Academic

Documente Profesional

Documente Cultură

Informe Final de Laboratorio

Încărcat de

Ruben SandroDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Informe Final de Laboratorio

Încărcat de

Ruben SandroDrepturi de autor:

Formate disponibile

CONTADOR DIGITAL

CIRCUITOS DIGITALES II

PROYECTO FINAL

I. INTRODUCCION

Partiendo de la premisa de conocer la utilidad y manejo de los circuitos

secuenciales en nuestro entorno convencional y dada la importancia de

conocer su relevancia e imprescindible papel en el desarrollo de

nuevas tecnologas se realiza este proyecto siguiendo lo solicitado el

diseo e implementacin de un sistema de control de ingreso de

visitantes a un piso de una clnica, con un lmite de cupos establecidos.

En este informe se presenta paso a paso el desarrollo aplicando lo

aprendido en las temticas de la unidad 1 y 2 que presenta el mdulo

de sistemas digitales secuenciales, donde se profundiza en temas como

cerrojos, sistemas combinacionales y secuencialess, flip flop, diseo de

mquinas de estado, registros de desplazamiento y memorias.

DOCENTE: Dr. UTRILLA SALAZAR DARO | FIEE 2016-II

CONTADOR DIGITAL

CIRCUITOS DIGITALES II

PROYECTO FINAL

II. OBJETIVOS

Disear e implementar un sistema de control de acceso de

visitantes familiares a pacientes hospitalizados en una clnica,

esto teniendo como base lo estudiado, analizado y aplicado en los

temas realizados en el curso.

Sustentar el sistema de control de entrada y salida de visitantes

de acuerdo a las variables establecidas

III. MARCO TEORICO

Circuito integrado 555

El temporizador IC 555 es un circuito integrado (chip) que se utiliza en

una variedad de aplicaciones y se aplica en la generacin de pulsos y de

oscilaciones. El 555 puede ser utilizado para proporcionar retardos de

tiempo, como un oscilador, y como un circuito integrado flip-flop. Sus

derivados proporcionan hasta cuatro circuitos de sincronizacin en un

solo paquete. Introducido en 1971 por Signetics, el 555 sigue siendo de

uso generalizado debido a su facilidad de uso, precio bajo y la

estabilidad. Lo fabrican muchas empresas en bipolares y tambin

en CMOS de baja potencia. A partir de 2003, se estimaba que mil

millones de unidades se fabricaban cada ao.

DOCENTE: Dr. UTRILLA SALAZAR DARO | FIEE 2016-II

CONTADOR DIGITAL

CIRCUITOS DIGITALES II

PROYECTO FINAL

Descripcin de las patillas del temporizador 555

GND (normalmente la 1): es el polo negativo de la alimentacin,

generalmente tierra (masa).

Disparo (normalmente la 2): Es donde se establece el inicio del

tiempo de retardo si el 555 es configurado como monoestable. Este

proceso de disparo ocurre cuando esta patilla tiene menos de 1/3

del voltaje de alimentacin. Este pulso debe ser de corta duracin,

pues si se mantiene bajo por mucho tiempo la salida se quedar en

alto hasta que la entrada de disparo pase a alto otra vez.

Salida (normalmente la 3): Aqu veremos el resultado de la

operacin del temporizador, ya sea que est conectado como

monoestable, astable u otro. Cuando la salida es alta, el voltaje ser

el voltaje de alimentacin (Vcc) menos 1.7 V. Esta salida se puede

obligar a estar en casi 0 voltios con la ayuda de la patilla de reinicio

(normalmente la 4).

Reinicio (normalmente la 4): Si se pone a un nivel por debajo de

0.7 Voltios, pone la patilla de salida a nivel bajo. Si por algn motivo

esta patilla no se utiliza hay que conectarla a alimentacin para

evitar que el temporizador se reinicie.

Control de voltaje (normalmente la 5): Cuando el temporizador se

utiliza en el modo de controlador de voltaje, el voltaje en esta patilla

puede variar casi desde Vcc (en la prctica como Vcc -1.7 V) hasta

casi 0 V (aprox. 2 V menos). As es posible modificar los tiempos.

Puede tambin configurarse para, por ejemplo, generar pulsos en

rampa.

Umbral (normalmente la 6): Es una entrada a un comparador

interno que se utiliza para poner la salida a nivel bajo. 3

Descarga (normalmente la 7): Utilizado para descargar con

efectividad el condensador externo utilizado por el temporizador

para su funcionamiento.

DOCENTE: Dr. UTRILLA SALAZAR DARO | FIEE 2016-II

CONTADOR DIGITAL

CIRCUITOS DIGITALES II

PROYECTO FINAL

Voltaje de alimentacin (VCC) (normalmente la 8): es la patilla

donde se conecta el voltaje de alimentacin que va de 4.5 V hasta 16

V.

Multivibrador Astable

Este tipo de funcionamiento se caracteriza por una salida con forma de

onda cuadrada (o rectangular) continua de ancho predefinido por el

diseador del circuito. El esquema de conexin es el que se muestra. La

seal de salida tiene un nivel alto por un tiempo t1 y un nivel bajo por

un tiempo t2. La duracin de estos tiempos dependen de los valores de

R1, R2 y C, segn las frmulas siguientes:

[segundos]

[segundos]

La frecuencia con que la seal de salida oscila est dada por la frmula:

el perodo es simplemente:

Tambin decir que si lo que queremos es un generador con frecuencia

variable, debemos variar la capacidad del condensador, ya que si el

cambio lo hacemos mediante los resistores R1 y/o R2, tambin cambia

el ciclo de trabajo o ancho de pulso (D) de la seal de salida segn la 4

siguiente expresin:

DOCENTE: Dr. UTRILLA SALAZAR DARO | FIEE 2016-II

CONTADOR DIGITAL

CIRCUITOS DIGITALES II

PROYECTO FINAL

Hay que recordar que el perodo es el tiempo que dura la seal hasta

que sta se vuelve a repetir (Tb - Ta).

Multivibrador monoestable

En este caso el circuito entrega un solo pulso de un ancho establecido

por el diseador.

El esquema de conexin es el que se muestra. La frmula para calcular

el tiempo de duracin (tiempo en el que la salida est en nivel alto) es:

[s]

[segundos]

Ntese que es necesario que la seal de disparo sea de nivel bajo y de

muy corta duracin para iniciar la seal de salida.

DOCENTE: Dr. UTRILLA SALAZAR DARO | FIEE 2016-II

CONTADOR DIGITAL

CIRCUITOS DIGITALES II

PROYECTO FINAL

FLIP FLOP

Registro Bsico construido con compuertas NAND

Este es el circuito ms sencillo y bsico de un FF, Puede ser construido

a partir de dos compuertas NAND o dos compuertas NOR con dos

entradas, a continuacin se ilustra con compuertas NAND, y es

denominado "Registro Bsico NAND".La forma de conectarlas es la

siguiente: Se deja libre una de las entradas de cada compuerta, las

sobrantes son conectadas independientemente de manera cruzada

hacia la salida de la compuerta contraria.Quedando la conexin de la

siguiente manera:

La siguiente tabla muestra el estado inicial del Registro Bsico NAND,

cuando sus entradas se encuentran en ALTO (Estado de reposo del FF).

Para comenzar la accin de "Flip Flop" ser necesario enviar a BAJO

alguna de las entradas, con su correspondiente cambio de estado a la

salida.

La siguiente tabla nos muestra los diferentes cambios de las salidas,

segn cada seleccin de entradas (La "X" significa que no importa el

estado en el que se encuentren en ese momento):

DOCENTE: Dr. UTRILLA SALAZAR DARO | FIEE 2016-II

CONTADOR DIGITAL

CIRCUITOS DIGITALES II

PROYECTO FINAL

Siguiendo los datos de la tabla podemos resumir que:

Si SET y RESET estn en ALTO, el FF mantiene sus salidas en el

estado actual.

Si RESET recibe un pulso BAJO, las salidas son forzadas a Q = 0 y

/Q = 1

Si SET recibe un pulso BAJO, las salidas son forzadas a Q = 1 y /Q

=0

Si las dos entradas reciben pulsos BAJOS, las salidas son forzadas

a Q = 1 y /Q = 1

Este ltimo cambio normalmente se considera como no deseado,

ya que el principio bsico es que las salidas siempre estn

invertidas (Aunque en ciertos casos especiales, nosotros

podramos utilizar este efecto).Entonces, la tabla de verdad del

Registro Bsico NAND es la siguiente:

Registro Bsico con compuertas NOR

La conexin del Registro Bsico NOR es exactamente igual al del

Registro NAND, pero los cambios en sus salidas son completamente

diferentes, A continuacin se ilustran las dos tablas de verdad para

hacer el comparativo entre una y otra.Tabla de verdad del Registro

Bsico NOR

7

DOCENTE: Dr. UTRILLA SALAZAR DARO | FIEE 2016-II

CONTADOR DIGITAL

CIRCUITOS DIGITALES II

PROYECTO FINAL

Tabla de verdad del Registro Bsico NAND

Agregando pulsadores u otras compuertas en las entradas, los usos

ms comunes para el Registro Bsico NAND o NOR son:

Eliminadores de ruido para pulsadores mecnicos.

Sistemas de Encendido (ON)/Apagado (OFF) con dos pulsadores para

diversos circuitos digitales y/o anlogos.

Sensores de movimiento mecnico, (Fin o Inicio de carrera de

una puerta por ejemplo).

Control Digital de otros circuitos.

Y otras 373929273736 Aplicaciones dependiendo de tu IMAGINACIN.

Seales de Reloj (CLOCK) y FF controlados por Reloj

Hasta ahora hemos visto que un Registro Bsico tiene

dos variables de entrada y responde de manera predecible a ellas, pero

Qu podamos hacer si necesitramos otra variable de control? Cmo

podramos hacer que el registro acte cuando sea conveniente para

nosotros, y no al momento de cambiar sus entradas?Todos los sistemas

digitales tienen bsicamente dos formas de operacin:

Operacin en modo ASNCRONO.En este modo, las salidas cambian de

manera automtica siguiendo las rdenes de las entradas.

Operacin en modo SNCRONO.En este modo, las salidas cambian

siguiendo las ordenes de las entradas, pero slo cuando una seal de

control, llamada RELOJ (CLOCK, CLK, CP) es aplicada al registro.

Los circuitos digitales ASNCRONOS son muy complicados en lo que 8

a diseo y reparacin se refiere, ya que, al encontrarnos con una falla

en un circuito de 10 registros interconectados, el rastreo de los

cambios en todas las compuertas nos provocara un severo dolor de

DOCENTE: Dr. UTRILLA SALAZAR DARO | FIEE 2016-II

CONTADOR DIGITAL

CIRCUITOS DIGITALES II

PROYECTO FINAL

cabeza.Los circuitos digitales SNCRONOS son ms fciles de disear y

reparar, debido a que los cambios de las salidas

son eventos "esperados" (ya que fcilmente podemos saber el estado

de cada una de las entradas o salidas sin que estas cambien

repentinamente), y los cambios dependen del control de una sola seal

aplicada a todos los registros, la seal de RELOJ.La seal de reloj es una

onda cuadrada o rectangular, los registros que funcionan con esta

seal, slo pueden cambiar cuando la seal de reloj hace una

transicin, Tambin llamados "flancos", por lo tanto, la seal de reloj

slo puede hacer 2 transiciones (o Flancos):

La Transicin con pendiente positiva (TPP) o Flanco positivo (FP).Es

cuando la seal de reloj cambia del estado BAJO al estado ALTO.

La Transicin con pendiente negativa (TPN) o Flanco Negativo (FN).Es

cuando la seal de reloj cambia del estado ALTO al estado BAJO.

Principales caractersticas de los FF sincronizados por Reloj.

Todos los FF cuentan con una entrada con el rtulo (RELOJ, CLOCK,

CLK, CP) y un distintivo crculo para saber como debe ser la seal

activa. Los que no tienen crculo, son sincronizados por una TPP, los

que cuentan con un crculo son sincronizados por una TPN.

Todos los FF cuentan con entradas de control, que determinan el

cambio que van a tener las salidas, al igual que en los Registros bsicos,

pero estas entradas no pueden modificar las salidas arbitrariamente,

slo podrn hacerlo cuando el FF reciba su transicin activa.

Resumiendo, Las entradas de control del FF nos permiten saber cmo

van a cambiar las salidas, pero slo la seal de Reloj podr hacer

efectivo este cambio.

Constantes de tiempo de Establecimiento y de Retencin

La siguiente figura nos indica cmo estn compuestos los dos

detectores de Transiciones.

Detector de Transiciones Positivas (TPP)

DOCENTE: Dr. UTRILLA SALAZAR DARO | FIEE 2016-II

CONTADOR DIGITAL

CIRCUITOS DIGITALES II

PROYECTO FINAL

Circuito Detector de Transiciones Negativas

Las figuras nos muestran del lado izquierdo de la lnea verde el pin de

entrada de Reloj del FF, el lado derecho nos muestra el circuito interno

del FF.La diferencia entre CK y CK se debe al retraso en la propagacin

que cualquier compuerta tiene, desde que se aplica una seal en la

entrada, hasta que esta se refleja en al salida. Esta diferencia en tiempo,

nos permite obtener un pulso de salida solamente cuando ocurre la

transicin para la que estn diseados, y por lo tanto accionar el FF.

Registro Bsico NAND tipo Sncrono

Dejaremos de lado la conexin interna de los FF, ya que para nuestra

comodidad, todos podemos encontrarlos en forma de circuitos

integrados, as que nos ocuparemos solamente de su

funcionamiento.La siguiente figura nos muestra un Registro Bsico

Sincronizado por una seal de reloj. Es la forma ms bsica de un FF

controlado por la seal de reloj. (La falta del crculo en la entrada de

CLK significa que slo ser activa en los TPP) (Slo se muestra la salida

Normal (Q), ya que como dijimos, la salida negada siempre es inversa)

Flip Flop tipo "J-K"

Este FF es uno de los ms usados en los circuitos digitales, y de hecho

es parte fundamental de muchos circuitos avanzados como contadores

10

y registros de corrimiento, que ya vienen integrados en un chip.Este FF

cuenta con dos entradas de datos J y K, su funcin es en principio la

misma que el Registro bsico NAND o NOR, pero con la diferencia que

DOCENTE: Dr. UTRILLA SALAZAR DARO | FIEE 2016-II

CONTADOR DIGITAL

CIRCUITOS DIGITALES II

PROYECTO FINAL

la condicin en las entradas J = 1, K = 1, a diferencia del Registro NAND,

que generara una salida errnea o no deseada, en un FF J-K, obliga a

las salidas a conmutar su estado al opuesto (Toggle) a cada pulso del

reloj. Esto lo convierte en un tipo de FF muy verstil.Tabla de verdad

de un FF tipo J-K sncrono.

Observando la tabla de verdad observamos los cambios que provoca

en sus salidas este FF:

Si J y K = 0, no hay cambios en las salidas.

Si J = 1, y K = 0, se forzan las salidas a Q = 1, /Q = 0

Si J = 0, y K = 1, se forzan las salidas a Q = 0, /Q = 1

Si J = 1, y K = 1, las salidas conmutan su estado hacia el siguiente a cada

pulso del reloj (Toggle)

Flip Flop tipo "D" (Datos, Data)

A diferencia de los FF tipo J-K, el FF tipo "D" (Datos, Data) slo cuneta

con una entrada para hacer el cambio de las salidas. A cada pulso del

reloj (dependiendo si el FF utiliza una TPP o una TPN) el estado

presente en la entrada "D" ser transferido a la salida Q y /Q.Tabla de

verdad de un FF tipo "D"

Una de las aplicaciones de mayor uso para este tipo de FF es al de la

transferencia de datos de forma paralela, conectando varios FF tipo "D"

a X nmero de bits, podemos hacer que la informacin de todos los bits

pase inmediatamente a la salida de cada FF con slo un pulso de reloj.

Entradas asncronas en los FF 11

Como ya hemos visto, cada FF tiene entradas que pueden cambiar el

estado de las salidas de manera sincronizada con el pulso de reloj, pero

DOCENTE: Dr. UTRILLA SALAZAR DARO | FIEE 2016-II

CONTADOR DIGITAL

CIRCUITOS DIGITALES II

PROYECTO FINAL

Dnde quedaron nuestras entradas asncronas? Es posible seguir

usando estas entradas en FF sncronos?La respuesta est en los FF

sncronos de cualquier tipo que poseen entradas asncronas, esto

aade dos pines ms de control a nuestros FF, los conocidos SET y

RESET (Los cules pueden ser activos en el estado ALTO o BAJO).

Entonces tenemos FF sncronos (Tipo "J - K", o tipo "D" ) con un par de

entradas que no dependen en ningn momento del pulso de Reloj.

Haciendo una combinacin perfecta de entradas que controlan las

salidas de manera automtica (Asncronas) o controladas por un pulso

de reloj (Sncronas).La siguiente figura nos muestra los smbolos de los

FF Tipo "J - K" y "D" con sus entradas asncronas.

Tabla de verdad del FF Tipo "J - K" con entradas Asncronas

(Las "X" significan que no importa el estado actual de esa entrada).(El

FF tiene una entrada de Reloj que funciona con TPP)(Las entradas

asncronas con activas ALTAS)

El funcionamiento bsico sigue siendo el mismo, pero las salidas sern

forzadas a ALTO o BAJO, si se activan las entradas Asncronas

correspondientes (SET, RESET) sin importar el estado de las entradas

"J - K" o CLK.

12

DOCENTE: Dr. UTRILLA SALAZAR DARO | FIEE 2016-II

CONTADOR DIGITAL

CIRCUITOS DIGITALES II

PROYECTO FINAL

Tabla de verdad del FF Tipo "D" con entradas Asncronas

(Las "X" significan que no importa el estado actual de esa entrada).(El

FF tiene una entrada de Reloj que funciona con TPP)(Las entradas

asncronas con activas ALTAS)

El funcionamiento bsico sigue siendo el mismo, pero las salidas sern

forzadas a ALTO o BAJO, si se activan las entradas Asncronas

correspondientes (SET, RESET) sin importar el estado de la entrada

"D" o CLK.

Con esto termina este pequeo tutorial de Flip-Flops, espero que las

dudas hayan encontrado una respuesta satisfactoria, y que la

informacin aqu contenida sea de gran utilidad para el lector.

EL CONTADOR DIGITAL

En electrnica es bastante frecuente verse necesitado de contabilizar

eventos y por tanto se requiere utilizar un contador, en nuestro caso se

tratar de un contador electrnico digital. Un contador electrnico

bsicamente consta de una entrada de impulsos que se encarga de

conformar (escuadrar), de manera que el conteo de los mismos no sea

alterado por seales no deseadas, las cuales pueden falsear el

resultado final. Estos impulsos son acumulados en un contador

propiamente dicho cuyo resultado, se presenta mediante un visor que

puede estar constituido por una serie de sencillos dgitos de siete

segmentos o en su caso mediante una sofisticada pantalla de plasma.

Empezaremos por considerar un circuito de entrada que nos permita

tomar la seal motivo del conteo, para lo cual hemos de pensar en la

forma de tomar la seal a medir. Para que el mencionado circuito sea

lo ms universal posible:

Entrada de alta impedancia (Z). El circuito no debera absorber

13

demasiada seal para no inducir errores.

Dicha seal, la deberemos escuadrar de forma segura.

DOCENTE: Dr. UTRILLA SALAZAR DARO | FIEE 2016-II

CONTADOR DIGITAL

CIRCUITOS DIGITALES II

PROYECTO FINAL

El circuito constar de un separador de corriente continua mediante

un condensador ceramico de baja capacidad (47nf/400V), para

detectar las seales de alta frecuencia si es el caso, la salida se

conectar a un diferenciador constituido por una puerta lgica, para

una mayor seguridad dicha puerta ser un disparador Schmitt (trigger

Schmitt). Si utilizamos un transistor, ste debe ser de alta velocidad.

Fig. 1

El circuito de la figura 2, representa la entrada descrita, en la figura 3,

ms elaborada, se aprecia el circuito de entrada completo que puede

servirnos en la mayora de los casos, en la figura 4, se presenta un

nuevo circuito con mejores prestaciones al que se le a aadido el

mencionado disparador Schmitt formado por la puerta de alta

velocidad 74HCT14 (6 inversores Schmitt). En el cual resaltamos el

punto (A) ya que en l los impulsos detectados an no estan

totalmente escuadrados.

Fig. 2

14

DOCENTE: Dr. UTRILLA SALAZAR DARO | FIEE 2016-II

CONTADOR DIGITAL

CIRCUITOS DIGITALES II

PROYECTO FINAL

Fig. 3

Fig. 4

En la figura 2, se pueden apreciar dos componentes, el condensador

separa la tensin continua y la resistencia eleva la impedancia lo

suficiente para nuestro cometido. En la figura 3, se propone un circuito

que utiliza un transistor como seguidor de emisor con un limitador de

tensin a 6V mediante el diodo zener, al que le sigue un nuevo

transistor separador que mejora la salida, permitiendo as, una

alimentacin con un margen bastante amplio.

En la figura 4, los limitadores de tensin son los dos diodos D1 y D2, su

punto comn como se aprecia es conectado a la base de un transistor

mediante un divisor de tensin, y la salida del seguidor de emisor, nos 15

da la seal que utilizaremos para el contador, no obstante, se ha

intercalado un inversor o puerta trigger para escuadrar al mximo

dicha seal.

DOCENTE: Dr. UTRILLA SALAZAR DARO | FIEE 2016-II

CONTADOR DIGITAL

CIRCUITOS DIGITALES II

PROYECTO FINAL

Anteriormente vimos cmo detectar y escuadrar los impulsos que

posteriormente se han de contar. Ahora, trataremos el que es el

corazn del contador propiamente dicho, es decir, la parte del circuito

que se encarga de contar, almacenar y acumular cada pulso al siguiente

de la cuenta anterior y si es el caso cambiar de decada.

El circuito bsico que se use, depender de la tecnologa disponible,

esto lo podemos apreciar mejor en la tabla siguiente:

FAMILIA TIPO Relacin V/C

TTL 74LS192 + velocidad + consumo

CMOS CD4510B - velocidad - consumo

HCTLS 74HCTLS192 + velocidad - consumo

Atendiendo a que la velocidad es muy importante y en cualquier

momento se puede requerir esta capacidad, nos centraremos en la

opcin de la serie 74HCTLS192 o en su defecto por la 74LS192 ya que

se trata del mismo dispositivo, lo nico que cambia es el consumo, la

tensin de trabajo y poco ms.

El dispositivo 74HCTLS192, constituye un contador asncrono

reversible con entrada paralela, preparado para efectuar el conteo

decimal en cdigo binario BCD.

Para cargar las salidas a un determinado estado, se aplican los datos a

las entradas Da, Db, Dc y Dd y se aplica el nivel bajo L a la patilla 11

' load', esta operacin de carga es independiente del reloj y del estado

del contador.

En la figura 1, se muestra la disposicin de las patillas como se puede

ver.

16

Fig. 1

DOCENTE: Dr. UTRILLA SALAZAR DARO | FIEE 2016-II

CONTADOR DIGITAL

CIRCUITOS DIGITALES II

PROYECTO FINAL

El circuito se completar aadiendo 3 puertas NAND correspondientes

a un 74HCTLS00, una de ellas conectada como inversor y unos pocos

elementos como 1 pulsador 4 preselectores, 1 conmutador y unas

resistencias de 1k5 y W. Tambin se puede hacer que el contador se

ponga a una determinada cuenta de forma automtica

Fig. 2 Esquema del contador para 1 dgito.

Como se desprende del circuito para incrementar el nmero de dgitos,

tan solo habr que aadir tantos contadores como dgitos se deseen y

conectarlos en serie, prescindiendo de las subsiguientes puertas de los

nuevos contadores y conectando todas las patillas de carga al mismo

pulsador de igual forma que las patillas de PAC.

Por otra parte se encuentran los convertidores de BCD a 7 segmentos,

compuesto por un dispositivo de la serie CMOS por ser el ms tipico al

igual que por ser compatible con los HCT

IV. DESARROLLO DEL PROYECTO

4.1. DESCRIPCION DE LA NECESIDAD

Disear e implementar un sistema de control de entrada y

salida de visitantes a familiares hospitalizados en una clnica,

durante el horario de visitas, las reas de visitas para los

familiares para este caso el nmero mximo de visitantes es de

10 personas. Tener las siguientes consideraciones para la

implementacin: 17

DOCENTE: Dr. UTRILLA SALAZAR DARO | FIEE 2016-II

CONTADOR DIGITAL

CIRCUITOS DIGITALES II

PROYECTO FINAL

En la entrada se debe evidenciar el nmero de visitantes que

ha ingresado a travs de display siete segmentos indicando si

se puede permitir el acceso de mas visitantes o no.

Al momento de la llegada del visitante, si hay disponibilidad se

autoriza la entrada y automticamente se incrementara el

nmero de visitantes en el piso.

Cuando un visitante de cualquier piso salga debe evidenciar en

el display, su disponibilidad para un nuevo visitante.

En la entrada de la clnica se debe evidenciar en led de color

verde; si no hay disponibilidad, se debe evidenciar a travs de

un led de coloro rojo.

Recuerde que si no hay disponibilidad para el acceso de

visitantes en el piso, no se debe permitir su acceso.

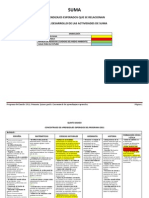

4.2. DIAGRAMA DE BLOQUES

18

DOCENTE: Dr. UTRILLA SALAZAR DARO | FIEE 2016-II

CONTADOR DIGITAL

CIRCUITOS DIGITALES II

PROYECTO FINAL

ENTRADA VISITANTE

CADA INGRESO EL

CONTADOR CRECE

PERMANECE ENCENDIDO EL

DISPLAY EN A=10 NO

LED VERDE

SI

PISO CON CUPOS PARA

INGRESO

ENCIENDE LED ROJO

PISO SIN CUPOS PARA

INGRESO

SALIDA CONTADOR DECRECE

4.3. MATERIALES

Transistor 2N3904

2 Display siete segmentos

Integrado 74LS08 (AND)

Integrado 74LS192

Timer 555

Integrado 7447

Switch

2 LED

Resistencia 1M, 100K, 10K, 330

Capacitor 0.22uF 19

DOCENTE: Dr. UTRILLA SALAZAR DARO | FIEE 2016-II

U7(VCC) U7(VCC)

V.

R2 U6 U6 U2 U2

R2 15 3 7 13

10k 15 3 D0 7 Q0 13 A QA

10k D0 Q0 1 A 2 QA 1 12

1 2 D1 1 Q1 12 B QB

D1 Q1 10 B 6 QB 2 11

U7 10 6 D2 2 Q2 11 C QC

D2 Q2 9 C 7 QC 6 10

8

U7 9 7 D3 6 Q3 10 D QD

8

D3 Q3 D QD 4 9 (COM)

4 9 BI/RBO QE (COM)

4 3 5 BI/RBO 12 QE 5 15

4 3 R Q 5 12 UP 5 TCU 15 RBI QF

R Q UP TCU 4 RBI 13 QF 3 14

VCC

4 13 DN 3 TCD 14 LT QG

VCC

7 DN TCD 11 LT QG

7 DC 11 PL

DC R1 R6 PL 14 7447

R1 R6 14 MR 7447

100K 5 1M MR

5 CV

100K CV 1M 74LS192

74LS192 (COM)

(COM)

2 6

TR TH

GND

2 6

TR TH

GND

1

U3 U5

1

U3 15

U5 3 7 13

ENTRADA 15 3 D0 7 Q0 13 A QA

D0 Q0 1 A 2 QA 1 12

ENTRADA 1 2 D1 1 Q1 12 B QB

10 6 2 11

IMPLEMENTACION

D1 Q1 D2 B QB C QC

10 6 9 2 Q2 7 11 6 10

C1 D2 Q2 D3 C

Q3 QC D QD

C1 9 7 6 10 4 9

0.22uf D3 Q3 D QD BI/RBO QE

0.22uf 5 4 12 9 5 15

UP BI/RBO QE RBI QF

5 12 4 5 TCU 15 3 14

UP TCU DN RBI 13 QF LT QG

4 13 11 3 TCD 14

DN TCD PL LT QG

11 14 7447

PL MR

14 7447

MR

R3 74192

R3 74192

10k

10k

U8 R9(1)

8

U8 R9(1)

8

4 3

4 3 R Q

VCC

R Q

7

VCC

7 DC

DC R4 R5 R9

R4 100K R55 1M

U1:A R9 330

5 CV U1:A

100K CV 1M 2 330

2 3

3 1

5

4

5

4

2 6

TR TH

GND

2 6 74LS08 U1:B

TR TH

GND

74LS08 U1:B 74LS08 D1

1

555 74LS08 D1 DISPONIBLE

1

555 DISPONIBLE

SALIDA

SALIDA C2

C2 0.22uF

6

0.22uF

Q1

6

Q1

R7 R8

R7 R8 330

10k 330

10k

2N3904

2N3904 D2

D2 LLENO

LLENO

CONTADOR DIGITAL

PROYECTO FINAL

CIRCUITOS DIGITALES II

DOCENTE: Dr. UTRILLA SALAZAR DARO | FIEE 2016-II

20

U7(VCC)

R2 U6 U2

10k 15 3 7 13

D0 Q0 A QA

1 2 1 12

D1 Q1 B QB

10 6 2 11

U7 D2 Q2 C QC

9 7 6 10

8

D3 Q3 D QD

4 9 (COM)

BI/RBO QE

4 3 5 12 5 15

R Q UP TCU RBI QF

4 13 3 14

VCC

DN TCD LT QG

7 11

DC PL

R1 R6 14 7447

MR

100K 5 1M

CV

74LS192

(COM)

2 6

TR TH

GND

1

U3 U5

15 3 7 13

ENTRADA D0 Q0 A QA

1 2 1 12

D1 Q1 B QB

10 6 2 11

D2 Q2 C QC

C1 9 7 6 10

D3 Q3 D QD

0.22uf 4 9

BI/RBO QE

5 12 5 15

UP TCU RBI QF

4 13 3 14

DN TCD LT QG

11

PL

14 7447

MR

R3 74192

10k

U8 R9(1)

8

4 3

R Q

VCC

7

DC

R4 R5 U1:A R9

100K 5 1M 330

CV

2

3

1

5

4

2 6

TR TH

GND

74LS08 U1:B

74LS08 D1

1

555 DISPONIBLE

SALIDA

C2

0.22uF

6

Q1

R7 R8

330

10k

2N3904

D2

LLENO

CONTADOR DIGITAL

PROYECTO FINAL

CIRCUITOS DIGITALES II

DOCENTE: Dr. UTRILLA SALAZAR DARO | FIEE 2016-II

21

S-ar putea să vă placă și

- Que Es El CoronavirusDocument2 paginiQue Es El CoronavirusRuben SandroÎncă nu există evaluări

- Laboratrorio 1 en Ing de Control - ArduinoDocument2 paginiLaboratrorio 1 en Ing de Control - ArduinoMirko RamirezÎncă nu există evaluări

- Muestreo de Señales de Banda BaseDocument15 paginiMuestreo de Señales de Banda BaseRuben SandroÎncă nu există evaluări

- Maquina DC MonografíaDocument32 paginiMaquina DC MonografíaRuben SandroÎncă nu există evaluări

- Tiristores (Electronica de Potencia)Document35 paginiTiristores (Electronica de Potencia)william.123100% (1)

- RvoltimetrolDocument2 paginiRvoltimetrolAlejandro GarcíaÎncă nu există evaluări

- Final 5Document4 paginiFinal 5Ruben SandroÎncă nu există evaluări

- Informe Previo 01 C. Electronicos 2Document11 paginiInforme Previo 01 C. Electronicos 2Ruben Sandro100% (3)

- Configuracion Cascada P1Document5 paginiConfiguracion Cascada P1Daniel SalazarÎncă nu există evaluări

- PoemaDocument1 paginăPoemaRuben SandroÎncă nu există evaluări

- FINAL 2 DARLINGTONG Circcuitos Electrónicos IIDocument10 paginiFINAL 2 DARLINGTONG Circcuitos Electrónicos IIRuben SandroÎncă nu există evaluări

- Cuaderno Teoria Maquina ElectricasDocument18 paginiCuaderno Teoria Maquina ElectricasRuben SandroÎncă nu există evaluări

- Tipos de ReproducciónDocument4 paginiTipos de ReproducciónRuben SandroÎncă nu există evaluări

- Ckto Sumador Restador BCDDocument2 paginiCkto Sumador Restador BCDRuben SandroÎncă nu există evaluări

- MONOGRAFÍA Compresion de VideoDocument25 paginiMONOGRAFÍA Compresion de VideoRuben SandroÎncă nu există evaluări

- Balotario Del Examen Parcial de Funciones AnaliticasDocument37 paginiBalotario Del Examen Parcial de Funciones AnaliticasCarlosAndresReyesRomeroÎncă nu există evaluări

- Informe Final Ce1-04Document5 paginiInforme Final Ce1-04Ruben SandroÎncă nu există evaluări

- Segundo Trabajo LPDocument7 paginiSegundo Trabajo LPRuben SandroÎncă nu există evaluări

- Tarea 01 (MEVF)Document5 paginiTarea 01 (MEVF)Ruben SandroÎncă nu există evaluări

- Informe Final 2Document8 paginiInforme Final 2Ruben SandroÎncă nu există evaluări

- f4 Diap 02 Optica Geometrica ReflexionDocument36 paginif4 Diap 02 Optica Geometrica ReflexionRuben SandroÎncă nu există evaluări

- Previo 3Document7 paginiPrevio 3Ruben SandroÎncă nu există evaluări

- Ciudad Universitaria 30 de Agostor de 2015: Curso: Lenguaje de Programación Profesor: Cesar Angulo Alumno: CódigoDocument19 paginiCiudad Universitaria 30 de Agostor de 2015: Curso: Lenguaje de Programación Profesor: Cesar Angulo Alumno: CódigoRuben SandroÎncă nu există evaluări

- E5 - Proyecto IntegradorDocument1 paginăE5 - Proyecto IntegradorRuben SandroÎncă nu există evaluări

- Interferencia y DifraccionDocument50 paginiInterferencia y DifraccionRuben SandroÎncă nu există evaluări

- Informe Previo 2 Labo de CircuitosDocument3 paginiInforme Previo 2 Labo de CircuitosRuben SandroÎncă nu există evaluări

- Practica Grupal Calficada de Fan-Unmsm-FieeDocument6 paginiPractica Grupal Calficada de Fan-Unmsm-FieeJohann Caceres FloresÎncă nu există evaluări

- Tecsup - Simbología y Esquemas Eléctricos PDFDocument57 paginiTecsup - Simbología y Esquemas Eléctricos PDFJuan Luis Merlo89% (19)

- Arequipa La Ciudad BlancaDocument1 paginăArequipa La Ciudad BlancaRuben SandroÎncă nu există evaluări

- Sintesis de Caminos de ReacciónDocument7 paginiSintesis de Caminos de ReacciónAndrés Camilo Regino RamirezÎncă nu există evaluări

- Formato de Informe Lab Física Itsa 2019Document7 paginiFormato de Informe Lab Física Itsa 2019Omar Guerrero CpdjÎncă nu există evaluări

- Informe de Suelos - TablestacasDocument11 paginiInforme de Suelos - TablestacasJennyfer SerranoÎncă nu există evaluări

- Derivada de Una Funcion RealDocument3 paginiDerivada de Una Funcion RealMiguel OverThe LimitÎncă nu există evaluări

- ADITIVOS PresentacionDocument29 paginiADITIVOS PresentacionPako Polo RojasÎncă nu există evaluări

- Bobina de Rotor o Bobina de Campo, EstatorDocument2 paginiBobina de Rotor o Bobina de Campo, EstatorDemian VasquezÎncă nu există evaluări

- Respuestas Hidrodinámicas de La Instalación de Acuicultura LONGLINE Con Redes de Linterna en Olas (Cañari Quispe, D. - Henriquez Alfaro, E.)Document22 paginiRespuestas Hidrodinámicas de La Instalación de Acuicultura LONGLINE Con Redes de Linterna en Olas (Cañari Quispe, D. - Henriquez Alfaro, E.)Diego CañariÎncă nu există evaluări

- Control 7 ErgonomiaDocument5 paginiControl 7 Ergonomiacamila100% (1)

- Celdas de FlotaciónDocument19 paginiCeldas de FlotaciónOscar MauricioÎncă nu există evaluări

- Mediciones y ErroresDocument8 paginiMediciones y ErroresOscar Hbk Vargas TercerosÎncă nu există evaluări

- Guia #1 Fisica Grado Noveno-2021Document5 paginiGuia #1 Fisica Grado Noveno-2021katherinÎncă nu există evaluări

- Trepanos Triconos PDFDocument7 paginiTrepanos Triconos PDFAnonymous ZvPZcetr5Încă nu există evaluări

- Taller Refracción Olga Morales y Angie LandinezDocument2 paginiTaller Refracción Olga Morales y Angie LandinezOlga moralesÎncă nu există evaluări

- Mecanoreceptor CaracolDocument6 paginiMecanoreceptor CaracolMartaSoledadRamosGuillenÎncă nu există evaluări

- Concentrado - Aprendizajes Esperados - Grado 5° - V2.0Document7 paginiConcentrado - Aprendizajes Esperados - Grado 5° - V2.0Yessi LopezÎncă nu există evaluări

- Propiedades de La LuzDocument5 paginiPropiedades de La LuzRené ZavalaÎncă nu există evaluări

- La Danza ModernaDocument354 paginiLa Danza ModernaMercedes Piñeiro95% (21)

- Mate2B2 ExamenDocument9 paginiMate2B2 ExamenBerenice Acosta CotaÎncă nu există evaluări

- Ejercicios ResueltosDocument201 paginiEjercicios ResueltosJaviera RiveraÎncă nu există evaluări

- TesisI Marcio FinalgbfdgDocument28 paginiTesisI Marcio FinalgbfdgMarci AlexisÎncă nu există evaluări

- No - Ccom .06. Uso e Instalacion de Retenidas Ver01Document15 paginiNo - Ccom .06. Uso e Instalacion de Retenidas Ver01ALBERTO SANCHEZÎncă nu există evaluări

- Trabajo CaolinDocument34 paginiTrabajo CaolinOmar MendozaÎncă nu există evaluări

- LABORATORIO #3 CapilaridadDocument9 paginiLABORATORIO #3 CapilaridadEdder Andrés Potosí VillacísÎncă nu există evaluări

- TAREA 2 BM David M - Himmelblau SEXTA EDIC PDFDocument8 paginiTAREA 2 BM David M - Himmelblau SEXTA EDIC PDFJuan Manuel Uceda Pérez50% (2)

- Aligantes Teoria AnaDocument14 paginiAligantes Teoria AnaOOnly AnythaÎncă nu există evaluări

- Medición y Conversión de UnidadesDocument5 paginiMedición y Conversión de Unidadesgregoriofernandez100% (1)

- Fisica General Dinamica y Energia, Grupo 100413 - 187Document30 paginiFisica General Dinamica y Energia, Grupo 100413 - 187juanÎncă nu există evaluări

- Stephen ChapmanDocument90 paginiStephen ChapmanClaudia Leticia50% (6)

- Suunto Ambit 3 Peak Manual Usuario Del Reloj Gps Altímetro Barómetro.Document131 paginiSuunto Ambit 3 Peak Manual Usuario Del Reloj Gps Altímetro Barómetro.Mayayo: Carrerasdemontana.com100% (1)

- Manuel - Acevedo - Reevaluacion Del Diseño Aislada ResidencialDocument8 paginiManuel - Acevedo - Reevaluacion Del Diseño Aislada ResidencialManuel Acevedo RamirezÎncă nu există evaluări