Documente Academic

Documente Profesional

Documente Cultură

EC6304 EC1 Questionbank Rejinpaul

Încărcat de

Ajay GanesanDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

EC6304 EC1 Questionbank Rejinpaul

Încărcat de

Ajay GanesanDrepturi de autor:

Formate disponibile

www.rejinpaul.

com

SRI VIDYA COLLEGE OF ENGINEERING & TECHNOLOGY EC-I QUESTION BANK

UNIT I

PART A

1. Define - Stability Factor

2. Compare bias stabilization and compensation techniques

3. What is the condition for thermal stability?

4. What are the different methods of biasing JFET?

5. What are the types of transistor biasing?

6. Draw the single stage self biased circuit using pnp transistor.

7. List the advantages of self bias.

8. Draw the fixed bias and the self bias circuits.

9. What is the need for biasing in transistor amplifier?

10. What is reverse saturation current?

11. Why is capacitive coupling used to connect a signal source to an amplifier?

12. Calculate the value of feedback resistor (Rs) required to self bias an N-channel JFET with

IDSS=40mA, VP = -10V and VGSQ = -5V.

13. What is DC load line? How is Q point plotted on the DC load line?

PART B

1. Explain fixed biasing in BJT and FET. Explain the procedure for locating operating point

on the characteristic curves.(16)

2. Explain the fixed bias method and derive an expression for the stability factor.(8)

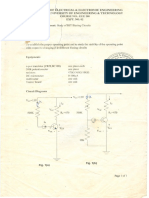

3. The following circuit has VCC = 20V, RC = 2K , = 50, VBE = 0.2V, R1 = 100K, RE =

100. Calculate IB, VCE, IC and the Stability Factor S. (16)

Vcc

R1 =R

C

R2

RE

.

4. Draw a voltage divider bias BJT network. Derive expressions for I CQ and VCEQ and

describe the method of drawing the dc load line on the output characteristics of transistor.

(16)

5. Explain the voltage divider bias method and derive an expression for the stability factor.

(8)

6. For the following circuit find the Q-point if VCC = 15V and = 100; VBE = 0.7V. (10)

EC6304 ELECTRONIC CIRCUITS - I Page 1

Get useful study materials from www.rejinpaul.com

www.rejinpaul.com

SRI VIDYA COLLEGE OF ENGINEERING & TECHNOLOGY EC-I QUESTION BANK

Vcc

100 k 4.3 k

100 k

6.8 k

7. A silicon transistor with = 49 is used in self bias arrangement with VCC = 5V, RE =

1Kohms and IE = 1mA. Find the values of R1 and R2 such that the stability factor does

not exceed 5. (10)

8. In an N-channel JFET, biased by potential divider method, the operating point has to be

at IDSS = 12mA. If VDD = 12V, R1 = 20K and R2 = 10K , RD =1.2K and VP= -4V.

Find the values of ID, VGS, VG, VDS and VS. (16)

9. Calculate the operating point for the following circuit.(6)

Vcc=15V

1 k ohm

200 ohm

=50

100 ohm

10. For the following circuit calculate VCE and IC, where = 100 for the silicon transistor.

11. Derive the expression of stability factor for collector feedback amplifier.

(10)

12. Explain the circuit that uses a diode to compensate the changes in VBE and in ICO.(12)

13. Explain the operation of thermistor compensation. (4)

14. Explain the various techniques of stabilization of Q-point in a transistor.

(16)

EC6304 ELECTRONIC CIRCUITS - I Page 2

Get useful study materials from www.rejinpaul.com

www.rejinpaul.com

SRI VIDYA COLLEGE OF ENGINEERING & TECHNOLOGY EC-I QUESTION BANK

15. Explain the factors on which an amplifier needs to be stabilized.(6)

16. With the help of neat diagram, explain the methods used in biasing the FET and

MOSFET. (16)

(i) Define - Stability Factor. (2)

(ii) The pnp transistor in the following circuit has = 50. Find the values of R C to obtain

Vc = 5V. What happens if the transistor is replaced with another transistor = 100? (14)

EC6304 ELECTRONIC CIRCUITS - I Page 3

Get useful study materials from www.rejinpaul.com

S-ar putea să vă placă și

- VSC-FACTS-HVDC: Analysis, Modelling and Simulation in Power GridsDe la EverandVSC-FACTS-HVDC: Analysis, Modelling and Simulation in Power GridsÎncă nu există evaluări

- Ec-I - Question Bank: Unit I Part - ADocument3 paginiEc-I - Question Bank: Unit I Part - ASuguna Priya0% (1)

- Electromagnetic Compatibility (EMC) Design and Test Case AnalysisDe la EverandElectromagnetic Compatibility (EMC) Design and Test Case AnalysisÎncă nu există evaluări

- Edc - Assignment Questions - NbaDocument5 paginiEdc - Assignment Questions - Nbagunda manasaÎncă nu există evaluări

- Analog Electronic Circuits Assignment QuestionsDocument6 paginiAnalog Electronic Circuits Assignment QuestionschaitanyaÎncă nu există evaluări

- Edlc Dec2007Document1 paginăEdlc Dec2007SwapnilDashputeÎncă nu există evaluări

- EDC - Question BankDocument7 paginiEDC - Question BankSwaum KisÎncă nu există evaluări

- Ee B 122-Beee QBDocument9 paginiEe B 122-Beee QBdavid josephÎncă nu există evaluări

- 16 131101 Basic ElectronicsDocument2 pagini16 131101 Basic Electronicsdhvani5988Încă nu există evaluări

- Study BJT biasing circuitsDocument3 paginiStudy BJT biasing circuitsMeowÎncă nu există evaluări

- Sem 3 Module 3Document5 paginiSem 3 Module 3Joshua HernandezÎncă nu există evaluări

- Question Bank - Principles of ElectronicsDocument13 paginiQuestion Bank - Principles of ElectronicsADDELYN CYNTHIA ANAK TONYÎncă nu există evaluări

- Basic Electronics (BBEE103/BBEE203) - Question Bank - VTUDocument11 paginiBasic Electronics (BBEE103/BBEE203) - Question Bank - VTUShrishail Bhat100% (1)

- Electronic Devices Exam QuestionsDocument1 paginăElectronic Devices Exam QuestionsManjot KaurÎncă nu există evaluări

- AE 1 EQ by Faiz SirDocument16 paginiAE 1 EQ by Faiz SirFaiz RangariÎncă nu există evaluări

- SDC- Important Questions for Semiconductor Diodes and CircuitsDocument5 paginiSDC- Important Questions for Semiconductor Diodes and CircuitsInstagramÎncă nu există evaluări

- Power ElectronicsDocument190 paginiPower ElectronicsBabul PratapÎncă nu există evaluări

- Question Paper Code:: Reg. No.Document3 paginiQuestion Paper Code:: Reg. No.Samraj JebasinghÎncă nu există evaluări

- AVS COLLEGE OF TECHNOLOGY EC8351 ELECTRONIC CIRCUITS-1 NOTESDocument26 paginiAVS COLLEGE OF TECHNOLOGY EC8351 ELECTRONIC CIRCUITS-1 NOTESPrabakaran RajanÎncă nu există evaluări

- Anna University - Chennai B.E./B.Tech - Degree-Examination-December 2009 Third Semester-Electronics &communications Engg. Electronic Circuits-IDocument1 paginăAnna University - Chennai B.E./B.Tech - Degree-Examination-December 2009 Third Semester-Electronics &communications Engg. Electronic Circuits-Iselvaece2010Încă nu există evaluări

- Edc PracticalsDocument7 paginiEdc PracticalsKarthik SrinivaasanÎncă nu există evaluări

- EC6304 Electronic Circuits I Question BankDocument10 paginiEC6304 Electronic Circuits I Question BankAnonymous kQZgP8Încă nu există evaluări

- Question Paper Code:: Reg. No.Document5 paginiQuestion Paper Code:: Reg. No.Samraj JebasinghÎncă nu există evaluări

- EE Important QuestionsDocument6 paginiEE Important QuestionsLE-1 BhargaviÎncă nu există evaluări

- G.H.RAISONI COLLEGE ELECTRONIC DEVICES & CIRCUITS NOTESDocument4 paginiG.H.RAISONI COLLEGE ELECTRONIC DEVICES & CIRCUITS NOTESbijileeÎncă nu există evaluări

- Module1 BEEE Important QuestionsDocument1 paginăModule1 BEEE Important QuestionsswathiÎncă nu există evaluări

- Electronic Devices & Circuits SyllabusDocument4 paginiElectronic Devices & Circuits SyllabusShareef KhanÎncă nu există evaluări

- AsdaDocument1 paginăAsdarrkeerthanaÎncă nu există evaluări

- Basic Electronics Assignments Chapter GuideDocument7 paginiBasic Electronics Assignments Chapter GuideSoumyaranjan PandaÎncă nu există evaluări

- Sample 3Document3 paginiSample 3Sujeev GyawaliÎncă nu există evaluări

- Electronic Devices Model Question PapersDocument2 paginiElectronic Devices Model Question Papersk_kunarajÎncă nu există evaluări

- BEE Important QuestionsDocument6 paginiBEE Important QuestionsBilal Ahmed100% (2)

- Module-Wise Eln QBDocument5 paginiModule-Wise Eln QBRashmi SamantÎncă nu există evaluări

- Ec (Ee) 301Document1 paginăEc (Ee) 301main2510Încă nu există evaluări

- AEC BankDocument9 paginiAEC BankprakashkerurÎncă nu există evaluări

- 1A Lect1 3 JJ Intro Diodes Set1Document1 pagină1A Lect1 3 JJ Intro Diodes Set1666jklmao666Încă nu există evaluări

- Ae 1 Eq PDFDocument16 paginiAe 1 Eq PDFFaiz RangariÎncă nu există evaluări

- Power Electronics Question Paper AnalysisDocument3 paginiPower Electronics Question Paper AnalysisSujesh ChittarikkalÎncă nu există evaluări

- Eee 2202 AssignmentDocument2 paginiEee 2202 AssignmentEnock OmariÎncă nu există evaluări

- Basic Electronics Question Bank-2023-DecDocument10 paginiBasic Electronics Question Bank-2023-Decpratiksharma2828Încă nu există evaluări

- E-Note 12425 Content Document 20231105014816AMDocument6 paginiE-Note 12425 Content Document 20231105014816AMkartik.doye2005Încă nu există evaluări

- V Semester B.E. (E&E) Degree Examination, January 2013 (2K6 Scheme) Ee 504: Power ElectronicsDocument3 paginiV Semester B.E. (E&E) Degree Examination, January 2013 (2K6 Scheme) Ee 504: Power ElectronicsSumant ReddyÎncă nu există evaluări

- QP Model EcedDocument3 paginiQP Model EcedShree Ram Senthil SubramaniamÎncă nu există evaluări

- Important Questions For ExaminationDocument4 paginiImportant Questions For ExaminationSaurabh SinghÎncă nu există evaluări

- KTU EC205 ELECTRONIC CIRCUITS (AE, EC) - MAin - Jan - 2017 - Ktu Qbank-MergedDocument16 paginiKTU EC205 ELECTRONIC CIRCUITS (AE, EC) - MAin - Jan - 2017 - Ktu Qbank-MergedsunÎncă nu există evaluări

- EDC Key Concepts: Feedback Amplifiers, OscillatorsDocument5 paginiEDC Key Concepts: Feedback Amplifiers, OscillatorsK.Swetha PriyadharshiniÎncă nu există evaluări

- EC6202 Electronic Devices and Circuits Question Paper May 2016Document16 paginiEC6202 Electronic Devices and Circuits Question Paper May 2016Senthil IlangovanÎncă nu există evaluări

- Unit V Transistor Biasing and Thermal StabilizationDocument65 paginiUnit V Transistor Biasing and Thermal Stabilizationgunasekaran kÎncă nu există evaluări

- Chapter 1-QB-Semicond Diodes& ApplicsDocument3 paginiChapter 1-QB-Semicond Diodes& ApplicsRamyaÎncă nu există evaluări

- Institute of Aeronautical Engineering: Model Question PaperDocument5 paginiInstitute of Aeronautical Engineering: Model Question PaperVigneshÎncă nu există evaluări

- S4 EC1 LabDocument87 paginiS4 EC1 LabM N GeethasreeÎncă nu există evaluări

- Semiconductor QBDocument9 paginiSemiconductor QBdheeraj rajÎncă nu există evaluări

- Electronic Devices Model Question PapersDocument2 paginiElectronic Devices Model Question Papersk_kunarajÎncă nu există evaluări

- Assignment - 6 SolutionsDocument7 paginiAssignment - 6 SolutionsGopal Iswarpur Ghosh100% (1)

- SDSSFDocument16 paginiSDSSFSamuel PakianathanÎncă nu există evaluări

- Introduction To Electronics and Communication (BESCK104C/BESCK204C) - Question Bank - VTUDocument14 paginiIntroduction To Electronics and Communication (BESCK104C/BESCK204C) - Question Bank - VTUShrishail Bhat100% (1)

- Edec Question Paper-IDocument8 paginiEdec Question Paper-IarunfriendsÎncă nu există evaluări

- Basic Question BankDocument4 paginiBasic Question Bankmanju.dsatmÎncă nu există evaluări

- Important Question Bank for Basic Electrical EngineeringDocument4 paginiImportant Question Bank for Basic Electrical EngineeringSAURAV CHAUDHARYÎncă nu există evaluări

- Question Bank: E1153 - Basic Electrical & Electronics EngineeringDocument18 paginiQuestion Bank: E1153 - Basic Electrical & Electronics EngineeringAnanthilakaÎncă nu există evaluări

- CLOCK DIVIDER MINI PROJECTDocument6 paginiCLOCK DIVIDER MINI PROJECTAjay GanesanÎncă nu există evaluări

- CN Unit12 Question Bank1Document17 paginiCN Unit12 Question Bank1Ajay GanesanÎncă nu există evaluări

- Assignment 1 AnswersDocument4 paginiAssignment 1 AnswersAjay GanesanÎncă nu există evaluări

- 2013 RegulationDocument39 pagini2013 RegulationAjay GanesanÎncă nu există evaluări

- Ec6502-Principles of Digital Signal Processing: Assignment - 1Document1 paginăEc6502-Principles of Digital Signal Processing: Assignment - 1Ajay GanesanÎncă nu există evaluări

- Static Electric Field ProblemsDocument74 paginiStatic Electric Field ProblemsAjay GanesanÎncă nu există evaluări

- EC6504 Microprocessor and Microcontroller Course MaterialDocument164 paginiEC6504 Microprocessor and Microcontroller Course MaterialprabhakaranÎncă nu există evaluări

- Assignment 4 AnswersDocument4 paginiAssignment 4 AnswersAjay GanesanÎncă nu există evaluări

- Ee6461 Eecs Lab Manual (1) - 1Document113 paginiEe6461 Eecs Lab Manual (1) - 1Ajay GanesanÎncă nu există evaluări

- Unit 1Document45 paginiUnit 1VISHAVÎncă nu există evaluări

- MA6351 TPDE May June 2017 Imp Qns PDFDocument4 paginiMA6351 TPDE May June 2017 Imp Qns PDFAjay GanesanÎncă nu există evaluări

- DC Machines and Transformers GuideDocument12 paginiDC Machines and Transformers GuidemaheshboobalanÎncă nu există evaluări

- MA6351 TPDE May June 2017 Imp Qns PDFDocument4 paginiMA6351 TPDE May June 2017 Imp Qns PDFAjay GanesanÎncă nu există evaluări

- MA6351 Maths 3 Notes R2013Document203 paginiMA6351 Maths 3 Notes R2013avinash100% (1)

- Question Bank: Ec6302 Digital ElectronicsDocument14 paginiQuestion Bank: Ec6302 Digital ElectronicsBarry SmithÎncă nu există evaluări

- Binary Search TreeDocument6 paginiBinary Search TreeAjay GanesanÎncă nu există evaluări

- UNIT IVDocument23 paginiUNIT IVAjay GanesanÎncă nu există evaluări

- Question Bank For EC6301 - Object Oriented Programming and Data StructuresDocument23 paginiQuestion Bank For EC6301 - Object Oriented Programming and Data StructuresAjay GanesanÎncă nu există evaluări

- Ece Oopsds Unit-4Document27 paginiEce Oopsds Unit-4Ajay GanesanÎncă nu există evaluări

- Mshengeli Issa H.150 323481421Document20 paginiMshengeli Issa H.150 323481421roger damianÎncă nu există evaluări

- Basics of Remote Sensing and Gis: Group MembersDocument36 paginiBasics of Remote Sensing and Gis: Group MembersKrunal RanaÎncă nu există evaluări

- 2SC2216,2SC2717: TV Final Picture IF Amplifier ApplicationsDocument5 pagini2SC2216,2SC2717: TV Final Picture IF Amplifier ApplicationsAshly RoblesÎncă nu există evaluări

- Tut 1Document4 paginiTut 1Abhijit PalÎncă nu există evaluări

- Line Parameters Program: Frequency-Dependent ElectromagneticDocument10 paginiLine Parameters Program: Frequency-Dependent ElectromagneticAnderson JustoÎncă nu există evaluări

- CC-LINK Interface: SR83 Digital ControllerDocument24 paginiCC-LINK Interface: SR83 Digital ControllerChristianÎncă nu există evaluări

- 83 Revision Questions SolutionsDocument5 pagini83 Revision Questions Solutionsmb1234Încă nu există evaluări

- 9mm!ূຌዡገ๕ۉ࿋ഗ Rotary Potentiometers With Metal Shaft Series: WH9011A-1-18TDocument26 pagini9mm!ূຌዡገ๕ۉ࿋ഗ Rotary Potentiometers With Metal Shaft Series: WH9011A-1-18TpeterfunÎncă nu există evaluări

- C1000D5 4 PDFDocument4 paginiC1000D5 4 PDFjavier.oyarzo.pÎncă nu există evaluări

- Technology and Livelihood Education: Electrical Installation and MaintenanceDocument11 paginiTechnology and Livelihood Education: Electrical Installation and MaintenanceAV Montes100% (1)

- Communication Engineering Asst. Prof. Dr. Ashwaq Q. Hameed Al Faisal UOT-Electrical Engineering Dept. Electronic Engineering BranchDocument6 paginiCommunication Engineering Asst. Prof. Dr. Ashwaq Q. Hameed Al Faisal UOT-Electrical Engineering Dept. Electronic Engineering BranchAzza24 Azize24Încă nu există evaluări

- Recent Trend in Electrochemical Science and TechnologyDocument316 paginiRecent Trend in Electrochemical Science and TechnologyCherry HamsteadÎncă nu există evaluări

- EVTV Pierburg CWA-50 Coolant Pump Specs and TestingDocument3 paginiEVTV Pierburg CWA-50 Coolant Pump Specs and TestingHarold TheHelicopter100% (4)

- Intro to Arduino: Zero to Prototyping in a FlashDocument93 paginiIntro to Arduino: Zero to Prototyping in a FlashEmmanuel Insieme Lo Facciamo MeglioÎncă nu există evaluări

- PMMCDocument16 paginiPMMCRavi Shankar 31Încă nu există evaluări

- SPM33 Data Sheet V2Document2 paginiSPM33 Data Sheet V2Vu SonÎncă nu există evaluări

- Technical Data: DescriptionDocument4 paginiTechnical Data: DescriptionMiltongrimi GrimilÎncă nu există evaluări

- IEC - Panel RegulationDocument20 paginiIEC - Panel RegulationAsith SavindaÎncă nu există evaluări

- Practical Electronics 1966 02 PDFDocument84 paginiPractical Electronics 1966 02 PDFCarlos Soares100% (1)

- Super UWBMIMOAntennaWithDualBand Notched - SajjadDocument9 paginiSuper UWBMIMOAntennaWithDualBand Notched - SajjadAbdullah MadniÎncă nu există evaluări

- PUTDocument15 paginiPUTDaisuke NiwaÎncă nu există evaluări

- Commissioning Manual - FinalDocument161 paginiCommissioning Manual - FinalRagab Tolba100% (1)

- SQ416V-SQ420V-SQ420W-SQ625W-SQ416Q-SQ420Q - Wiring Manual PDFDocument153 paginiSQ416V-SQ420V-SQ420W-SQ625W-SQ416Q-SQ420Q - Wiring Manual PDFDaniel BarrientosÎncă nu există evaluări

- Q2, WEEK 8 S10FE IIh 52Document8 paginiQ2, WEEK 8 S10FE IIh 52CRISTINE MAE AREVALO100% (1)

- Penyelesaian Tutorial Problem 40.3 Ebook BL. Theraja NO 1 Dan 2Document13 paginiPenyelesaian Tutorial Problem 40.3 Ebook BL. Theraja NO 1 Dan 2Restu RivalniÎncă nu există evaluări

- MAX803/MAX809/ MAX810 3-Pin Microprocessor Reset Circuits: General Description Benefits and FeaturesDocument8 paginiMAX803/MAX809/ MAX810 3-Pin Microprocessor Reset Circuits: General Description Benefits and FeaturesMaria TzagarakiÎncă nu există evaluări

- Equipment Wire Data SheetDocument3 paginiEquipment Wire Data Sheetamro emadÎncă nu există evaluări

- PB3 1Document5 paginiPB3 1womini1025Încă nu există evaluări

- Toshiba 57H81Document96 paginiToshiba 57H81tractorbobÎncă nu există evaluări

- 6.boq Ges P-1Document6 pagini6.boq Ges P-1RoshanÎncă nu există evaluări