Documente Academic

Documente Profesional

Documente Cultură

UC3842B/3843B: Unisonic Technologies Co., LTD

Încărcat de

vannadioDescriere originală:

Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

UC3842B/3843B: Unisonic Technologies Co., LTD

Încărcat de

vannadioDrepturi de autor:

Formate disponibile

UNISONIC TECHNOLOGIES CO.

, LTD

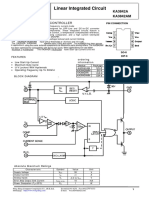

UC3842B/3843B LINEAR INTEGRATED CIRCUIT

HIGH PERFORMANCE

CURRENT MODE

CONTROLLERS

DESCRIPTION

The UTC UC3842B/3843B are specifically designed for off-line

and dc-to-dc converter applications offering the designer a

cost-effective solution with minimal external components.

The UC3842B has UVLO thresholds 16V (on) and 10V(off),

ideally suited for off-line converters. The UC3843B is tailored for

lower voltage applications having UVLO thresholds of 8.4V(on)

and 7.6V(off).

FEATURES Lead-free: UC3842BL

* Trimmed oscillator for precise frequency control UC3843BL

* Oscillator frequency guaranteed at 250kHz Halogen-free: UC3842BP

* Current mode operation to 500kHz UC3843BP

* Automatic feed forward compensation

* Latching PWM for cycle-by-cycle current limiting

* Internally trimmed reference with undervoltage lockout

* High current totem pole output

* Undervoltage lockout with hysteresis

* Low startup and operating current

ORDERING INFORMATION

Ordering Number

Package Packing

Normal Lead Free Halogen Free

UC3842B-D08-T UC3842BL-D08-T UC3842BP-D08-T DIP-8 Tube

UC3842B-S08-R UC3842BL-S08-R UC3842BP-S08-R SOP-8 Tape Reel

UC3843B-D08-T UC3843BL-D08-T UC3843BP-D08-T DIP-8 Tube

UC3843B-S08-R UC3843BL-S08-R UC3843BP-S08-R SOP-8 Tape Reel

www.unisonic.com.tw 1 of 11

Copyright © 2008 Unisonic Technologies Co., Ltd QW-R103-012.D

UC3842B/3843B LINEAR INTEGRATED CIRCUIT

PIN CONFIGURATION

COMP 1 8 VREF

VFB 2 7 VCC

CS 3 6 OUTPUT

RTCT 4 5 GND

PIN DESCRIPTIONS

PIN NO. PIN NAME I/O DESCRIPTION

1 COMP O Error amp output to provide loop compensation maintaing VFB at 2.5V

Error amp inverting input, The non-inverting input of error amp is 2.5V band

2 VFB I

gap reference

3 CS I Current sense input to PWM control gate drive of output

4 RTCT I To set oscillator frequency and maximum output duty cycle

5 GND Power ground

6 OUTPUT O To direct drive power MOSFET

7 VCC Power supply

8 VREF O 5V regulated output provides charging current for CT through RT

UNISONIC TECHNOLOGIES CO., LTD 2 of 11

www.unisonic.com.tw QW-R103-012.D

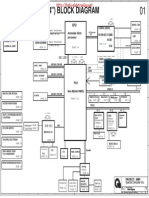

UC3842B/3843B LINEAR INTEGRATED CIRCUIT

BLOCK DIAGRAM

UNISONIC TECHNOLOGIES CO., LTD 3 of 11

www.unisonic.com.tw QW-R103-012.D

UC3842B/3843B LINEAR INTEGRATED CIRCUIT

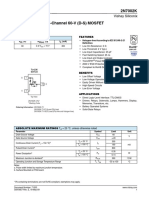

ABSOLUTE MAXIMUM RATINGS(Ta=25°C)

PARAMETER SYMBOL RATINGS UNIT

Total Power Supply and Zener Current (ICC + Iz) 30 mA

Output Current, Source or Sink (note1) Io 1.0 A

Output Energy (capacitive load per cycle) W 5.0 μJ

Current Sense and Voltage Feedback Inputs VIN -0.3 ~ +5.5 V

Error Amp. Output Sink Current IO(SINK) 10 mA

DIP-8 1250 mW

Power Dissipation PD

SOP-8 702 mW

Operating Junction Temperature TJ +150 °C

Operating Temperature TOPR 0 ~ +70 °C

Storage Temperature Range TSTG -65 ~ +150 °C

Note Absolute maximum ratings are those values beyond which the device could be permanently damaged.

Absolute maximum ratings are stress ratings only and functional device operation is not implied.

THERMAL DATA

PARAMETER SYMBOL RATINGS UNIT

DIP-8 100 °C/W

Thermal Resistance Junction to Ambient θJA

SOP-8 178 °C/W

ELECTRICAL CHARACTERISTICS

(0°C ≤TA≤70°C, VCC=15V [note 2], RT=10k, CT=3.3nF, unless otherwise specified)

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNIT

REFERENCE SECTION

Output Voltage VREF Io=1.0mA, TJ =25°C 4.9 5.0 5.1 V

Line Regulation ΔVLINE VCC=12V ~ 25V 2.0 20 mV

Load Regulation ΔVLOAD Io=1.0mA ~ 20mA 3.0 25 mV

Temperature Stability TS 0.2 mV/°C

Total Output Variation VREF Line, Load, Temperature 4.82 5.18 V

Output Noise Voltage eN F=10kHz ~ 10Hz, TJ =25°C 50 uV

Long Term Stability S TA=125°C,1000Hrs 5 mV

Output Short Circuit Current ISC -30 -85 -180 mA

OSCILLATOR SECTION

TJ =25°C 49 52 55

Frequency F Ta=0°C ~ 70°C 48 56 kHz

TJ =25°C (RT=6.2k,CT=1.0nF) 225 250 275

Frequency Change with Voltage ΔfOSC/ΔV 12 ≤ VCC ≤25V 0.2 1.0 %

Frequency Change with

ΔfOSC/ΔT 0°C ≤TA ≤70°C 0.5 %

Temperature

Oscillator Voltage Swing(Peak to

VOSC 1.6 V

Peak)

TJ =25°C 7.8 8.8

Discharge Current Idischg 8.3 mA

0°C ≤TA ≤70°C 7.6 8.8

ERROR AMPLIFIER SECTION

Voltage Feedback Input VFB Vo=2.5V 2.42 2.50 2.58 V

Input Bias Current II(BIAS) VFB=5.0V -0.1 -2.0 μA

Open Loop Voltage Gain GVO 2 ≤Vo≤4V 65 90 dB

Unity Gain Bandwidth GBW TJ =25°C 0.7 1.0 MHz

Power Supply Rejection Ratio PSRR I2V≤Vcc≤25V 60 70 dB

Output Sink Current ISINK Vo=1.1V,VFB =2.7V 2.0 12 mA

Output Source Current ISOURCE Vo=5.0V,VFB=2.3V -0.5 -1.0 mA

Output Voltage Swing High State VOH VFB=2.3V, RL=15k to GND 5.0 6.2 V

UNISONIC TECHNOLOGIES CO., LTD 4 of 11

www.unisonic.com.tw QW-R103-012.D

UC3842B/3843B LINEAR INTEGRATED CIRCUIT

ELECTRICAL CHARACTERISTICS (Cont.)

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNIT

Output Voltage Swing Low State VOL VFB=2.7V, RL=15k to VREF 0.8 1.1 V

CURRENT SENSE SECTION

Current Sense Input Voltage Gain GV (Note 3,4) 2.85 3.0 3.15 V/V

Maximum Current Sense Input

VI(THR) (Note 3) 0.9 1.0 1.1 V

Threshold

Power Supply Rejection Ratio PSRR 12≤Vcc≤25V (Note 3) 70 dB

Input Bias Current II(BIAS) -2 -10 μA

Propagation Delay tD(IN/OUT) Current Sense Input to Output 150 300 ns

OUTPUT SECTION

ISINK=20mA 0.1 0.4 V

Output Low Voltage VOL

ISINK=200mA 1.6 2.2 V

ISOURCE=20mA 13 13.5 V

Output High Voltage VOH

ISOURCE=200mA 12 13.4 V

Output Voltage with UVLO

VOL (UVLO) VCC=6.0V,ISINK=1.0mA 0.1 1.1 V

Activated

Output Voltage Rise Time tR TJ =25°C,CL=1nF 50 150 ns

Output Voltage Fall Time tF TJ =25°C,CL=1nF 50 150 ns

UNDER-VOLTAGE LOCKOUT SECTION

UTC UC3842B 14.5 16 17.5 V

Startup Threshold VTHR

UTC UC3843B 7.8 8.4 9 V

Min. Operating Voltage After UTC UC3842B 8.5 10 11.5 V

VCC(MIN)

Turn-on(Vcc) UTC UC3843B 7.0 7.6 8.2 V

PWM SECTION

MAX 94 96 %

Duty Cycle DC

MIN 0 %

Total DEVICE

VCC=6.5V for UC3843B

Power Startup Supply Current ICC+IC 0.3 0.5 mA

VCC=14V for UC3842B

Power Operating Supply Current ICC+IC Note2 12 17 mA

Power Supply Zener Voltage VZ ICC=25mA 30 36 V

Note: 1. Maximum Package power dissipation limits must be observed.

2. Adject VCC above the Startup threshold before setting to 15V.

3. This parameter is measured at the latch trip point with VFB=0V.

ΔV Output Compensation

4. Comparator gain is defined as : GV

ΔV Current Sense Input

UNISONIC TECHNOLOGIES CO., LTD 5 of 11

www.unisonic.com.tw QW-R103-012.D

UC3842B/3843B LINEAR INTEGRATED CIRCUIT

TYPICAL APPLICATION CIRCUIT

Open Loop Test Circuit

All of the parameters are not all tested in production, although been guaranteed. The timing and bypass capacitors

must be connected to pin 5 in a single point ground very closely. To sample the oscillator waveform, the transistor

and 5kΩ potentiometer are used, and also can apply an adjustable ramp to ISENSE pin.

VREF

2N UTC

2222 RT UC3842B/3843B

1 COMP VREF 8

100K

2 VFB VC 7 A V1

4.7K

3 ISENSE OUTPUT 6 OUTPUT

E/A 1K

0.1

ADJUST

ISENSE 5K 4 RT/CT GND 5

ADJUST

4.7K CT 0.1

1K/1W

Under Voltage Lockout

Under-Voltage Lock-Out: the output driver is biased to a high impedance state. To prevent activating the power

switch with output leakage current, pin 6 should be shunted to ground with a bleeder resistor.

Error Amp Configuration

UNISONIC TECHNOLOGIES CO., LTD 6 of 11

www.unisonic.com.tw QW-R103-012.D

UC3842B/3843B LINEAR INTEGRATED CIRCUIT

APPLICATION INFORMATION(Cont.)

Current Sense Circuit

Peak current (IS) is equaled:

IS(MAX)=1.0V/RS

There should be a small RC filter to suppress switch transients.

Oscillator Waveforms and Maximum Duty Cycle

LARGE RT

SMALL CT V4

VREF 8

RT

RT/RC 4 INTERINAL CLOCK

CT SMALL CT

LARGE RT

V4

GND 5

INTERINAL CLOCK

CT (Oscillator timing capacitor) can be charged by VREF through RT and discharged by an internal current source. At

discharge time, the internal clock signal blanks the output to the low. Both oscillator frequency and maximum duty

cycle can be determined by Selection of RT and CT. All charge and discharge times can be calculated by the next

formulas:

tC=0.55 RT CT

⎛ 0.0063R T − 2.7 ⎞

tD=RTCTIn ⎜⎜ ⎟

⎟

⎝ 0.0063R T − 4 ⎠

UNISONIC TECHNOLOGIES CO., LTD 7 of 11

www.unisonic.com.tw QW-R103-012.D

UC3842B/3843B LINEAR INTEGRATED CIRCUIT

APPLICATION INFORMATION(Cont.)

Shutdown Techniques

The UTC UC3842B’s shutdown can be accomplished by two ways: raise pin 3 above 1V; or pull pin 1 below a

voltage two diode drops above ground. Either method can cause the PWM comparator’s output to be high. Because

the PWM latch is reset dominant, the output will remain low until the next clock cycle after the shutdown condition at

pins 1 and/or 3 is removed.

Slope Compensation

UNISONIC TECHNOLOGIES CO., LTD 8 of 11

www.unisonic.com.tw QW-R103-012.D

UC3842B/3843B LINEAR INTEGRATED CIRCUIT

TYPICAL CHARACTERISTICS

Percent Output Deadtime, %DT.

Timing Resistor, RT (KΩ)

CT

=2

0

0p

F

CT

=5

.0

nF

CT

=1

0n

F

CT

=1

.0

nF

Maximum Output Duty Cycle, Dmax (%)

Discharge Current, Idischg (mA)

20mV/DIV

UNISONIC TECHNOLOGIES CO., LTD 9 of 11

www.unisonic.com.tw QW-R103-012.D

UC3842B/3843B LINEAR INTEGRATED CIRCUIT

TYPICAL CHARACTERISTICS(Cont.)

UNISONIC TECHNOLOGIES CO., LTD 10 of 11

www.unisonic.com.tw QW-R103-012.D

UC3842B/3843B LINEAR INTEGRATED CIRCUIT

TYPICAL CHARACTERISTICS(Cont.)

Output Saturation Voltage, Vsat (V)

Output Voltage, Vo

Supply Current, Icc (mA)

20V/DIV

Supply Current, Icc

UC3843B

UC3842B

100mA/DIV

UTC assumes no responsibility for equipment failures that result from using products at values that

exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or

other parameters) listed in products specifications of any and all UTC products described or contained

herein. UTC products are not designed for use in life support appliances, devices or systems where

malfunction of these products can be reasonably expected to result in personal injury. Reproduction in

whole or in part is prohibited without the prior written consent of the copyright owner. The information

presented in this document does not form part of any quotation or contract, is believed to be accurate

and reliable and may be changed without notice.

UNISONIC TECHNOLOGIES CO., LTD 11 of 11

www.unisonic.com.tw QW-R103-012.D

S-ar putea să vă placă și

- Unisonic Technologies Co., LTD: High Performance Current Mode PWM ControllersDocument7 paginiUnisonic Technologies Co., LTD: High Performance Current Mode PWM ControllersCesra HMÎncă nu există evaluări

- Current Mode PWMDocument9 paginiCurrent Mode PWMluis albertoÎncă nu există evaluări

- Unisonic Technologies Co., LTD: Voltage Mode PWM Control CircuitDocument8 paginiUnisonic Technologies Co., LTD: Voltage Mode PWM Control CircuitallendohorizontÎncă nu există evaluări

- Uc3842b 3843BDocument10 paginiUc3842b 3843Bbob75Încă nu există evaluări

- Unisonic Technologies Co., LTD: Switching Regulator Controller (Low Voltage)Document7 paginiUnisonic Technologies Co., LTD: Switching Regulator Controller (Low Voltage)Tahir HussainÎncă nu există evaluări

- Unisonic Technologies Co., LTD: DC To DC Converter ControllerDocument10 paginiUnisonic Technologies Co., LTD: DC To DC Converter ControllerAbel RodriguezÎncă nu există evaluări

- UC3848Document12 paginiUC3848isaiasvaÎncă nu există evaluări

- DD Microtech Corp.: AMC3842B/43BDocument10 paginiDD Microtech Corp.: AMC3842B/43BDahlanÎncă nu există evaluări

- RP108J Series: Low Input Voltage 3A LDO Regulator OutlineDocument29 paginiRP108J Series: Low Input Voltage 3A LDO Regulator OutlineArie DinataÎncă nu există evaluări

- Soldadora UTC3843DDocument9 paginiSoldadora UTC3843DChristian ormeñoÎncă nu există evaluări

- Bay Linear: Current Mode PWM ControllerDocument11 paginiBay Linear: Current Mode PWM ControllerShashikant PatilÎncă nu există evaluări

- DatasheetDocument9 paginiDatasheetjim campbellÎncă nu există evaluări

- UC3842/UC3843/UC3844/UC3845: SMPS ControllerDocument12 paginiUC3842/UC3843/UC3844/UC3845: SMPS ControllerMohamed HaddadÎncă nu există evaluări

- Unisonic Technologies Co., LTD: 4 Pin Dip Phototransistor PhotocouplerDocument7 paginiUnisonic Technologies Co., LTD: 4 Pin Dip Phototransistor PhotocouplerAbdul Rauf MughalÎncă nu există evaluări

- 3842a DatasheetDocument8 pagini3842a DatasheetVịnh DemoÎncă nu există evaluări

- 3842 Ic DatasheetDocument13 pagini3842 Ic DatasheetEngr Khalid IqbalÎncă nu există evaluări

- Unisonic Technologies Co., LTD: Telephone Tone RingerDocument5 paginiUnisonic Technologies Co., LTD: Telephone Tone Ringerzero cloudÎncă nu există evaluări

- BL0940 APPNote TSSOP14 V1.04 ENDocument6 paginiBL0940 APPNote TSSOP14 V1.04 ENGeorgi IlievÎncă nu există evaluări

- Operacional de Alto GanhoDocument11 paginiOperacional de Alto Ganhorogerio pessanha dos santosÎncă nu există evaluări

- ULN2804Document5 paginiULN2804vka_princeÎncă nu există evaluări

- TL1451Document14 paginiTL1451Teyfik koyuncuÎncă nu există evaluări

- Unisonic Technologies Co., LTD: PWM Control 3A Step-Down ConverterDocument8 paginiUnisonic Technologies Co., LTD: PWM Control 3A Step-Down ConverterLyw LywÎncă nu există evaluări

- IP4002CR DatasheetDocument7 paginiIP4002CR DatasheetJose BenavidesÎncă nu există evaluări

- 3842Document12 pagini3842luisÎncă nu există evaluări

- UTC TL1451 Linear Integrated Circuit: Dual Pulse-Width-Modulation Control CircuitsDocument5 paginiUTC TL1451 Linear Integrated Circuit: Dual Pulse-Width-Modulation Control CircuitsMarcos Gomes MisselÎncă nu există evaluări

- Ec48324 FV PDFDocument11 paginiEc48324 FV PDFАлександрÎncă nu există evaluări

- Unisonic Technologies Co., LTD: Eight High Voltage, High Current Darlington ArraysDocument5 paginiUnisonic Technologies Co., LTD: Eight High Voltage, High Current Darlington ArraysTojo BasheerÎncă nu există evaluări

- UC2842B/3B/4B/5B UC3842B/3B/4B/5B: High Performance Current Mode PWM ControllerDocument15 paginiUC2842B/3B/4B/5B UC3842B/3B/4B/5B: High Performance Current Mode PWM ControllertoajuiceÎncă nu există evaluări

- SMPS Controller: Features DescriptionDocument11 paginiSMPS Controller: Features DescriptionAdah BumboneÎncă nu există evaluări

- UC3846Document10 paginiUC3846Polo Soldas Polo SoldasÎncă nu există evaluări

- DP8600C YwDocument9 paginiDP8600C YwSURESH CHANDRA ROUTÎncă nu există evaluări

- Uc3863 Utc U863 PDFDocument9 paginiUc3863 Utc U863 PDFShailesh VajaÎncă nu există evaluări

- SE8117TADocument7 paginiSE8117TAdavid.gjeorgevskiÎncă nu există evaluări

- PD Derated at 8.5mW/ For Temperature Above Ta 25 (When Mounted On A PCB 70.0mm×70.0mm×1.6mm)Document5 paginiPD Derated at 8.5mW/ For Temperature Above Ta 25 (When Mounted On A PCB 70.0mm×70.0mm×1.6mm)Osama YaseenÎncă nu există evaluări

- Telefono l3240b Twotone RingerDocument6 paginiTelefono l3240b Twotone Ringerblackbeast79Încă nu există evaluări

- Dual Operational Amplifier: Features DescriptionDocument6 paginiDual Operational Amplifier: Features DescriptionAmin MahfudiÎncă nu există evaluări

- Low Power Dual Operational Amplifiers Az358/358CDocument13 paginiLow Power Dual Operational Amplifiers Az358/358CMarissa ValdezÎncă nu există evaluări

- At2596 IatDocument13 paginiAt2596 Iatlaboratorio eletronicoÎncă nu există evaluări

- 8205Document16 pagini8205sonytinÎncă nu există evaluări

- Unisonic Technologies Co., LTD: Vertical Deflection Output CircuitDocument5 paginiUnisonic Technologies Co., LTD: Vertical Deflection Output CircuitNerza ElectronicsÎncă nu există evaluări

- CR 6848 TDocument14 paginiCR 6848 Tndc20002003Încă nu există evaluări

- Novel Low Cost Green-Power PWM Controller: FeaturesDocument15 paginiNovel Low Cost Green-Power PWM Controller: FeaturesmehmoodÎncă nu există evaluări

- MC34063AB - MC34063AC MC34063EB - MC34063EC: DC/DC Converter Control CircuitsDocument23 paginiMC34063AB - MC34063AC MC34063EB - MC34063EC: DC/DC Converter Control CircuitsBoglárka TurcsánÎncă nu există evaluări

- SK6406 PDFDocument6 paginiSK6406 PDFjddgÎncă nu există evaluări

- 5-Channel Driver (BTL:4ch, H-Bridge:1ch) : For CD and DVD PlayersDocument8 pagini5-Channel Driver (BTL:4ch, H-Bridge:1ch) : For CD and DVD PlayersSony KusumoÎncă nu există evaluări

- APW7159ADocument23 paginiAPW7159AVoicu AdrianÎncă nu există evaluări

- Precision Waveform Generator/Voltage Controlled Oscillator FeaturesDocument12 paginiPrecision Waveform Generator/Voltage Controlled Oscillator FeaturesCharles Tineo0% (1)

- CT5503SDocument12 paginiCT5503SSubhash Digambar VisalÎncă nu există evaluări

- KA3842A IC Datasheet PDFDocument5 paginiKA3842A IC Datasheet PDFagarcosÎncă nu există evaluări

- Linear Integrated Circuit: Current Mode PWM ControllerDocument6 paginiLinear Integrated Circuit: Current Mode PWM ControllernermeenelnaggarÎncă nu există evaluări

- FP5139 Ic Dao Dong Bost NguonDocument14 paginiFP5139 Ic Dao Dong Bost Nguondinh vinh nguyenÎncă nu există evaluări

- UC3843 ChipsWinnerDocument11 paginiUC3843 ChipsWinnerPareÎncă nu există evaluări

- LA4145Document7 paginiLA4145NalsonÎncă nu există evaluări

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsDe la EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsÎncă nu există evaluări

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2De la EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Încă nu există evaluări

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1De la EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Evaluare: 4.5 din 5 stele4.5/5 (3)

- 2n7002k Sot-23 VishayDocument9 pagini2n7002k Sot-23 VishayKST5Încă nu există evaluări

- 2n7002k Sot-23 VishayDocument9 pagini2n7002k Sot-23 VishayKST5Încă nu există evaluări

- Tps 51225Document31 paginiTps 51225AEÎncă nu există evaluări

- A04d1 SW9Document41 paginiA04d1 SW9iskenderbeyÎncă nu există evaluări

- SM3317NSQA: Features Pin DescriptionDocument13 paginiSM3317NSQA: Features Pin DescriptionvannadioÎncă nu există evaluări

- APM4305KDocument10 paginiAPM4305KvannadioÎncă nu există evaluări

- Datasheet DIODOSDocument6 paginiDatasheet DIODOSvannadioÎncă nu există evaluări

- Features General Description: 5A Low Dropout Fast Response Positive Adjustable Regulator and Fixed 3.3VDocument13 paginiFeatures General Description: 5A Low Dropout Fast Response Positive Adjustable Regulator and Fixed 3.3VchoppersureÎncă nu există evaluări

- PCF 817Document12 paginiPCF 817claudiocbamtÎncă nu există evaluări

- UC3842B/3843B: Unisonic Technologies Co., LTDDocument11 paginiUC3842B/3843B: Unisonic Technologies Co., LTDvannadioÎncă nu există evaluări

- Reference Essay Computer)Document4 paginiReference Essay Computer)Trane SamÎncă nu există evaluări

- Ac To AcDocument32 paginiAc To AcAbenezer ZenebeÎncă nu există evaluări

- Roland/BOSS Products AC Adaptor InformationDocument4 paginiRoland/BOSS Products AC Adaptor InformationCristian Daniel ChelariuÎncă nu există evaluări

- Century Corporation User's Manual: KD25/35PRODocument24 paginiCentury Corporation User's Manual: KD25/35PROCS TanÎncă nu există evaluări

- Asus P4S800Document66 paginiAsus P4S800Infonova RuteÎncă nu există evaluări

- SOC Architecture DesignDocument24 paginiSOC Architecture DesignShravaniKashyapÎncă nu există evaluări

- Rhomberg Brasler Slimline Sc-320 - Especificaciones GeneralesDocument4 paginiRhomberg Brasler Slimline Sc-320 - Especificaciones Generalesbiotech666Încă nu există evaluări

- Mircostrip Patch Antenna With E Shaped Structure For S-Band ApplicationsDocument5 paginiMircostrip Patch Antenna With E Shaped Structure For S-Band ApplicationsijsretÎncă nu există evaluări

- 03-KERYS - Navigation (Operator Access) ENGDocument66 pagini03-KERYS - Navigation (Operator Access) ENGWashington VásquezÎncă nu există evaluări

- 4N29, 4N30, 4N31, 4N32, 4N33 General Purpose 6-Pin Photodarlington OptocouplerDocument14 pagini4N29, 4N30, 4N31, 4N32, 4N33 General Purpose 6-Pin Photodarlington OptocouplerGonzalo RojasÎncă nu există evaluări

- CSC326 Relay TestingDocument47 paginiCSC326 Relay TestingAssistant executive engineer100% (1)

- R4875G1 DatasheetDocument4 paginiR4875G1 DatasheetThịnh NguyễnÎncă nu există evaluări

- Star X Decoder-ManualDocument26 paginiStar X Decoder-ManualKaty WhiteÎncă nu există evaluări

- Afe Builtin System Catdat Da6510 76Document18 paginiAfe Builtin System Catdat Da6510 76rmsserviceÎncă nu există evaluări

- Acer P1283Document2 paginiAcer P1283Oscar Alexander Ojeda AriasÎncă nu există evaluări

- TV Plasma Panasonic TH 37 pwd7bx Ex pwd7 BK Ek Uy 42pw7ex BX pwd7bk Ek Es Uy Chassis GP 7dDocument160 paginiTV Plasma Panasonic TH 37 pwd7bx Ex pwd7 BK Ek Uy 42pw7ex BX pwd7bk Ek Es Uy Chassis GP 7dvideosonÎncă nu există evaluări

- Elements of An Optical Fiber Transmission LinkDocument2 paginiElements of An Optical Fiber Transmission LinkranjithÎncă nu există evaluări

- Mod 5Document82 paginiMod 5Siraj Bendre100% (1)

- Electrical Circuit Alexander & Sadiku (4th Edition)Document6 paginiElectrical Circuit Alexander & Sadiku (4th Edition)জাহিদ হাসানÎncă nu există evaluări

- P3 (192x192) IndoorDocument4 paginiP3 (192x192) IndoorCasio AutomaÎncă nu există evaluări

- Catálogo KLIP XTREME y FORZA Enero 2014Document126 paginiCatálogo KLIP XTREME y FORZA Enero 2014Alfonso Alfaro CortezÎncă nu există evaluări

- Design and Simulation of 2:1 Mux Using Multiple Logic GatesDocument58 paginiDesign and Simulation of 2:1 Mux Using Multiple Logic Gatesdurga manisha100% (1)

- 325 Final Design Lab ReportDocument11 pagini325 Final Design Lab Reportapi-241454978Încă nu există evaluări

- Wai-H Technology 49Document1 paginăWai-H Technology 49Arthur SeahÎncă nu există evaluări

- Assignment No 5 Subject Code: ECC/EIC 15103 Student Name .. Class Roll NoDocument6 paginiAssignment No 5 Subject Code: ECC/EIC 15103 Student Name .. Class Roll NoNagendra UdupaÎncă nu există evaluări

- NCR 7779 Tablet DatasheetDocument2 paginiNCR 7779 Tablet DatasheetprashantpsplÎncă nu există evaluări

- Clarification Points On GTS and CTSDocument1 paginăClarification Points On GTS and CTSkoushik42000Încă nu există evaluări

- Prospectus PDFDocument28 paginiProspectus PDFAjay DubeyÎncă nu există evaluări

- Danfoss VLT 2800Document120 paginiDanfoss VLT 2800daovanthanh_bk2007100% (1)