Documente Academic

Documente Profesional

Documente Cultură

CH 8

Încărcat de

TàiLươngTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

CH 8

Încărcat de

TàiLươngDrepturi de autor:

Formate disponibile

Chapter 8, Sec. 8.

5 : Error Checking

Error detection Error correction

Parity approaches

Hamming Codes

Cyclic Redundancy Checking

Comp Sys Design & Arch 2nd Ed 2004 Prentice Hall

Error Detection and Correction

Bit Error Rate (statistical property)

BER = prob {on reading, a given bit will be in error}

Important where noise and signal integrity cannot be

so easily controlled:

I/O and communications

Magnetic Storage

DRAM

BER inside processor ~ 10-18

BER outside processor ~ 10-8 - 10-12

Comp Sys Design & Arch 2nd Ed 2004 Prentice Hall

Parity Checking: Error Detection

Add a Parity Bit to the word.

Even Parity: Make the parity bit 1 bit if needed to

make number 1 of bits even, else make it 0.

Odd Parity: Make the parity bit a 1 bit if needed to

make number of 1 bits odd, else make it 0.

Example: for word 10011010, to add odd parity bit:

100110101

What sort of errors can be detected ?

Comp Sys Design & Arch 2nd Ed 2004 Prentice Hall

Hamming Codes

Hamming codes are a class of codes that use combinations of

parity checks to both detect and correct errors.

They add a group of parity check bits to the data bits.

For ease of visualization, intersperse the parity bits within the

data bits;

Reserve bit locations (numbered 1 r) whose bit numbers are

powers of 2 for the parity bits.

A given parity bit is computed from data bits whose bit numbers

contain a 1 at the parity bit number.

Comp Sys Design & Arch 2nd Ed 2004 Prentice Hall

Multiple Parity Checks Making up a Hamming Code

Check 2

Check 1

Check 0

Bit position 1 2 3 4 5 6 7

P1 P2 D3 P4 D5 D6 D7 Parity or data bit

20 21 22

001 010 011 100 101 110 111

P1 = D3 + D5 + D7

P2 = D3 + D6 + D7

P4 = D5 + D6 + D7

Thus each bit takes part in a different combination of parity checks.

When the word is checked, if only one bit is in error, all the parity bits that use it in

their computation will be incorrect.

Comp Sys Design & Arch 2nd Ed 2004 Prentice Hall

Exp: Venn Diagram showing Error Detection &

Correction using the Hamming Code

a. insert data

a. Sender: computes

& inserts even

parity bits

a. Receiver:

recomputes parity

bits, detects and

corrects error.

P1+P2 = 011

location

of the bit in

error

Comp Sys Design & Arch 2nd Ed 2004 Prentice Hall

Encode 1011 Using the Hamming Code &

Odd Parity

D3 D5 D6 D7

Insert the data bits: P1 P2 1 P4 0 1 1

P1 is computed from P1 D3 D5 D7 = 1, so P1 = 1.

P2 is computed from P2 D3 D6 D7 = 1, so P2 = 0.

P4 is computed from P4 D5 D6 D7 = 1, so P4 = 1.

The final encoded number is 1 0 1 1 0 1 1.

Note that the Hamming encoding scheme assumes that

at most one bit is in error.

Comp Sys Design & Arch 2nd Ed 2004 Prentice Hall

SECDED (Single Error Correct, Double Error Detect)

Add another parity bit at position 0 (computed to over all bits;

data & parity).

Let ci, ,the check bit I, be 1 if check i fails, otherwise 0.

In the case of a 1-bit error:

The string ck-1, . . ., c1, c0 will be the binary index of the

erroneous bit (as before).

The overall parity will be wrong.

In the case of a 2-bit error:

One or more Hamming checks will fail,

The overall parity will be correct.

Assumption: The probability of 3 bits being in error is

negligible.

Comp Sys Design & Arch 2nd Ed 2004 Prentice Hall

Compute the odd parity SECDED encoding of 01101011

The 8 data bits 01101011 would have 5 parity bits added to them to

make the 13-bit value:

P0 P1 P2 0 P4 1 1 0 P8 1 0 1 1

D1 D2 D3 D4 D5 D6 D7 D8

-------------------------------------------------------------------------------------------------------------------------

P1 = D1 D2 D4 D5 D7

0 = 0 1 0 1 1

-------------------------------------------------------------------------------------------------------------------------

P2= D1 D3 D4 D6 D7

P4= D2 D3 D4 D8

P8= D5 D6 D7 D8

--------------------------------------------------------------------------------------

Now P1 = 0, P2 = 1, P4 = 0, & P8 = 0, and we can compute that P0,

overall parity, = 1, giving the encoded value:

1010011001011

Comp Sys Design & Arch 2nd Ed 2004 Prentice Hall

Extract the Correct Data Value from the SECDED-

Encoded String 0110101101101, Assuming odd Parity

The string shows even parity, so there must be a

single bit in error.

Checks c2 and c4 fail, giving the binary index of the

erroneous bits as 0110 = 6, so D6 is in error.

It should be 0 instead of 1

Comp Sys Design & Arch 2nd Ed 2004 Prentice Hall

SECDED (Single Error Correct, Double Error Detect)

SEC SECDED

DATA CHK % CHK %

BITS BITS iNCREASE BITS iNCREASE

8 4 50 5 62.5

16 5 31.25 6 37.5

32 6 18.75 7 21.88

64 7 10.94 8 12.5

128 8 6.25 9 7.03

256 9 3.52 10 3.91

Comp Sys Design & Arch 2nd Ed 2004 Prentice Hall

Cyclic Redundancy Check, CRC

When data is transmitted serially over communications lines, the

pattern of errors usually results in several or many bits in error,

due to the nature of line noise (e.g., "crackling" noise on

telephone lines) is this kind of noise.

Parity checks are not as useful in these cases.

Instead CRC checks are used.

The CRC can be generated serially.

It usually consists of XOR gates.

Comp Sys Design & Arch 2nd Ed 2004 Prentice Hall

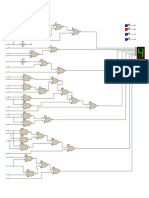

CRC Generator Based on the Polynomial

x16 + x12 + x5 + 1.

Data b0 b1 b2 b3 b4 b5 b6 b7 b8 b9 b10 b11 b12 b13 b14 b15

The number & position of XOR gates is determined by the

polynomial.

CRC does not support error correction but the CRC bits

generated can be used to detect multi-bit errors.

The CRC results in extra CRC bits, which are appended to the

data word & sent along.

The receiving entity can check for errors by recomputing the

CRC and comparing it with the one that was transmitted.

Comp Sys Design & Arch 2nd Ed 2004 Prentice Hall

Serial Data Transmission with Appended

CRC Code

Word 1

Word 2

CRC Generator

Word 3

Word 4

.

.

CRC Word N . . . Word 3 Word 2 Word 1

. Sending

Word N a Packet time

Transmission

Line

Output

Buffer

Comp Sys Design & Arch 2nd Ed 2004 Prentice Hall

Receiving Serial Data with Appended CRC

Input

Buffer

Received Word 1

Packet Word 2

Correct: Word 3

CRC Generator Send ACK Word 4

YES .

Received Received .

=

CRC NO Packet .

Incorrect: Word N

Send NACK

Transmission Word N . . . Word 3 Word 2 Word 1

Line Input

time

Comp Sys Design & Arch 2nd Ed 2004 Prentice Hall

S-ar putea să vă placă și

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (895)

- Board Information & Wiring Diagram Power Supply: Com Bat Com V VDocument1 paginăBoard Information & Wiring Diagram Power Supply: Com Bat Com V VTàiLươngÎncă nu există evaluări

- ISS Casino EngDocument25 paginiISS Casino EngTàiLươngÎncă nu există evaluări

- AEX ProductionsDocument40 paginiAEX ProductionsTàiLươngÎncă nu există evaluări

- CP Plus TechnicalDocument103 paginiCP Plus TechnicalTàiLươngÎncă nu există evaluări

- BoonTouch Software V1 - 9 - 35 Install Instructions and Release Notes (+speedlane Compact)Document2 paginiBoonTouch Software V1 - 9 - 35 Install Instructions and Release Notes (+speedlane Compact)TàiLươngÎncă nu există evaluări

- 4Document1 pagină4TàiLươngÎncă nu există evaluări

- AexDocument28 paginiAexTàiLươngÎncă nu există evaluări

- Simplified MIPS ProcessorDocument21 paginiSimplified MIPS ProcessorTàiLươngÎncă nu există evaluări

- 10 1 1 403 6994 PDFDocument6 pagini10 1 1 403 6994 PDFpoojaÎncă nu există evaluări

- Design and Implementation of 32-Bit RISC Processor Using Xilinx PDFDocument7 paginiDesign and Implementation of 32-Bit RISC Processor Using Xilinx PDFTàiLươngÎncă nu există evaluări

- 'HVLJQRI%LW0,365,6&3URFHVVRU%DVHG Rq6RfDocument5 pagini'HVLJQRI%LW0,365,6&3URFHVVRU%DVHG Rq6RfTàiLươngÎncă nu există evaluări

- DE2 UserManual 1.5Document73 paginiDE2 UserManual 1.5Rohan RepaleÎncă nu există evaluări

- 0Document1 pagină0TàiLươngÎncă nu există evaluări

- Design & Simulation of A 32-Bit Risc Based Mips Processor Using VerilogDocument7 paginiDesign & Simulation of A 32-Bit Risc Based Mips Processor Using VerilogTàiLươngÎncă nu există evaluări

- Design and Implementation of 32-Bit RISC Processor Using Xilinx PDFDocument7 paginiDesign and Implementation of 32-Bit RISC Processor Using Xilinx PDFTàiLươngÎncă nu există evaluări

- Writing To SRAM: Using Control PanelDocument8 paginiWriting To SRAM: Using Control PanelTàiLươngÎncă nu există evaluări

- Design of 32 Bit RISC Processor1 PDFDocument6 paginiDesign of 32 Bit RISC Processor1 PDFpalakÎncă nu există evaluări

- Ijert: 32-Bit Risc Processor For Computer ArchitectureDocument6 paginiIjert: 32-Bit Risc Processor For Computer ArchitectureTàiLươngÎncă nu există evaluări

- Table of Fourier Transform PairsDocument7 paginiTable of Fourier Transform Pairsfink18Încă nu există evaluări

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (400)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (266)

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (588)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2259)

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (73)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (121)

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)

- An Introduction To Coding Theory: Adrish BanerjeeDocument28 paginiAn Introduction To Coding Theory: Adrish BanerjeeShuubham OjhaÎncă nu există evaluări

- Ai File HMDocument19 paginiAi File HMnikunjÎncă nu există evaluări

- Minimum and Maximum Value of A FNXDocument23 paginiMinimum and Maximum Value of A FNXNik LagahitÎncă nu există evaluări

- Nwerc 2017 SlidesDocument91 paginiNwerc 2017 Slidesakash patilÎncă nu există evaluări

- Project Program Question 4Document7 paginiProject Program Question 4Beast Boy Squad GamingÎncă nu există evaluări

- Lecture23 24Document15 paginiLecture23 24numan jafarÎncă nu există evaluări

- Cscc24 Midterm NotesDocument5 paginiCscc24 Midterm NotesDeveloperAtWorkÎncă nu există evaluări

- Mathematical Programming Models and Methods For Production Planning and SchedulingDocument73 paginiMathematical Programming Models and Methods For Production Planning and SchedulingUyên PhạmÎncă nu există evaluări

- Assignment # 2 (Clo2) Submission Date: 18-11-19 Compiler Construction BCS-7C By: Yasir Awan Q. 1Document2 paginiAssignment # 2 (Clo2) Submission Date: 18-11-19 Compiler Construction BCS-7C By: Yasir Awan Q. 1Yasir AwanÎncă nu există evaluări

- Analysis of Function-LhopitalDocument13 paginiAnalysis of Function-LhopitalParvez ForaziÎncă nu există evaluări

- Stack, Queue, Linked ListDocument33 paginiStack, Queue, Linked ListMvr Sai KishoreÎncă nu există evaluări

- Chapter 3-Graph Algorithms: 2021 Prepared By: Beimnet GDocument42 paginiChapter 3-Graph Algorithms: 2021 Prepared By: Beimnet GBetty KebedeÎncă nu există evaluări

- 15-381 Spring 2007 Final Exam SOLUTIONSDocument18 pagini15-381 Spring 2007 Final Exam SOLUTIONStiggerÎncă nu există evaluări

- Cse 5-3Document4 paginiCse 5-3Riya PatilÎncă nu există evaluări

- Cheat Sheets For AI, Neural Networks, ML, DL & Big Data. - 1547405333 PDFDocument21 paginiCheat Sheets For AI, Neural Networks, ML, DL & Big Data. - 1547405333 PDFAvinash Thawani100% (1)

- Lecture-11 Impulse Response & Convolution Integral in CT LTI SystemDocument25 paginiLecture-11 Impulse Response & Convolution Integral in CT LTI SystemThe LifeÎncă nu există evaluări

- Tags RB2 WinCC Elipse (Salvo Automaticamente)Document628 paginiTags RB2 WinCC Elipse (Salvo Automaticamente)Mariana SanchezÎncă nu există evaluări

- Study Material: Vivekananda College, ThakurpukurDocument13 paginiStudy Material: Vivekananda College, ThakurpukurSubhasish BaruiÎncă nu există evaluări

- 1901005-Problem Solving and Python ProgrammingDocument10 pagini1901005-Problem Solving and Python ProgrammingKrishÎncă nu există evaluări

- MCQDocument3 paginiMCQmythili swaminathanÎncă nu există evaluări

- Assignment 2 Solutions PDFDocument13 paginiAssignment 2 Solutions PDFRudi OosthuizenÎncă nu există evaluări

- Wipro Coding Questions - Set 1Document7 paginiWipro Coding Questions - Set 1krishnÎncă nu există evaluări

- SAP CDs MSEG VIEWDocument5 paginiSAP CDs MSEG VIEWPawÎncă nu există evaluări

- 9 Pumping Lemma ExamplesDocument2 pagini9 Pumping Lemma ExamplesRonildo OliveiraÎncă nu există evaluări

- Adjacency GraphsDocument5 paginiAdjacency GraphsAriel LancasterÎncă nu există evaluări

- ASIC Design - Physical DesignDocument39 paginiASIC Design - Physical DesignPrabhavathi ParameshwarappaÎncă nu există evaluări

- Numerical Methods and Programming P. B. Sunil Kumar Department of Physics Indian Institute of Technology, Madras Lecture - 1 Programming - BasicsDocument26 paginiNumerical Methods and Programming P. B. Sunil Kumar Department of Physics Indian Institute of Technology, Madras Lecture - 1 Programming - BasicsPhạm Ngọc HòaÎncă nu există evaluări

- Holiday HomeworkDocument2 paginiHoliday Homeworkapi-245176244Încă nu există evaluări

- Java Practice Problems Activity 2Document6 paginiJava Practice Problems Activity 2Ian TaregaÎncă nu există evaluări

- Sample SCJP QuestionsDocument23 paginiSample SCJP QuestionsManuel GalganaÎncă nu există evaluări