Documente Academic

Documente Profesional

Documente Cultură

FASTRAC IC Design Company - 2018

Încărcat de

fukscribdTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

FASTRAC IC Design Company - 2018

Încărcat de

fukscribdDrepturi de autor:

Formate disponibile

Rony Parvej’s EEE Question Bank FASTRAC ANONTEX LTD.

Recruitment Test Question of FASTRAC ANONTEX LTD. ( an I.C. design company )

Compiled by: Rony Parvej (IUT, EEE’07)

Post: Assistant Engineer (Electrical)

Time: 90 minutes Full Marks: 100

Exam Date: February’2012 Venue: head office

1. Write the elaboration: VLSI, ASIC, CMOS, RTL, FPGA and DFT. 3

2. Write Linux command for the following operations: 5

(a) Change directory to /etc

(b) List all the files in current directory

(c) Rename ‘myfile’ to ‘yourfile’

(d) Count the number of lines in ‘myfile’

(e) Concatenate ‘file2’ at the end of ‘file1’

3. Draw the schematic of a CMOS inverter and it’s layout. Also draw the transfer characteristics curve

( input-vs-output voltage) of the inverter and indicate the point where current is maximum.

4. Which one is faster between NAND and NOR gate? Why?

5. What happens to the delay when you (a) decrease the load capacitance (b) include a resistance at the

output. And why?

6. Write the difference between Moore and Mealy type state machine.

7. Please briefly describe the following:

(a) setup time

(b) race time

(c) hold condition

8. Draw a gate level schematic implementation of a D flip-flop.

9. Make a JK flip-flop using a D flip-flop and 4-to-1 multiplexer.

10. Write the difference between the latch and flip-flop. Write the HDL code for both Latch and flip-

flop.

11. Write the usage of buffer in the digital circuits.

12. Can you implement a XOR using 2-to-1 multiplexer(s)? If yes, then implement it.

13. Design a four input NAND gate using two input NAND gates.

14. Implement a comparator that compares two 2-bit numbers A and B.

The comparator should have 3 outputs: A>B, A<B, A=B.

Do it in two ways: (a) Using combinational logic (b) Using multiplexers.

Write HDL code for your schematic at RTL.

15. Draw a circuit which can divide a frequency by two.

Rony Parvej’s EEE Question Bank FASTRAC ANONTEX LTD.

16. How do you convert a XOR gate into a

(a) buffer

(b) inverter

Use only one XOR gate for each.

17. Define FPGA and ASIC. What is look up table (LUT) in an FPGA? How is ASIC different from

FPGA?

18. Write the difference between a RAM and FIFO. Where is the FIFO used? Is the RAM volatile or

non-volatile?

S-ar putea să vă placă și

- Software Testing Interview Questions AnswersDocument29 paginiSoftware Testing Interview Questions AnswersAyan Baral100% (1)

- PizzaDocument164 paginiPizzaGyu Bot100% (3)

- MAPS Diet FoodsDocument1 paginăMAPS Diet FoodsMartin HaynesÎncă nu există evaluări

- NVIDIA QuestionsDocument5 paginiNVIDIA QuestionsJibin P John0% (1)

- C CheatsheetDocument74 paginiC CheatsheetRoberto Solano100% (6)

- (PDF Download) Design Electrical Comput Engineers Full Online by J. Eric SaltDocument1 pagină(PDF Download) Design Electrical Comput Engineers Full Online by J. Eric SaltfukscribdÎncă nu există evaluări

- (PDF Download) Design Electrical Comput Engineers Full Online by J. Eric SaltDocument1 pagină(PDF Download) Design Electrical Comput Engineers Full Online by J. Eric SaltfukscribdÎncă nu există evaluări

- RXCamView-Mobile APP User ManualDocument7 paginiRXCamView-Mobile APP User ManualNigromante_0125% (4)

- IntelDocument5 paginiIntelrAM50% (2)

- Termis 6 0Document952 paginiTermis 6 0Adrian MarinÎncă nu există evaluări

- Hasbunallahu Wa Nimal Wakeel Nimal Maula Wa Niman Naseer1 PDFDocument12 paginiHasbunallahu Wa Nimal Wakeel Nimal Maula Wa Niman Naseer1 PDFfukscribd100% (2)

- Hasbunallahu Wa Nimal Wakeel Nimal Maula Wa Niman Naseer1 PDFDocument12 paginiHasbunallahu Wa Nimal Wakeel Nimal Maula Wa Niman Naseer1 PDFfukscribd100% (2)

- 7 Intel Paper - AlDocument11 pagini7 Intel Paper - Alks25021995Încă nu există evaluări

- University Question Papers - VLSIDocument26 paginiUniversity Question Papers - VLSIVijayÎncă nu există evaluări

- Questions 4 1Document95 paginiQuestions 4 1Anik PaulÎncă nu există evaluări

- S, R Are All STD - LogicDocument7 paginiS, R Are All STD - LogicMuhammad Moin100% (1)

- Scheme - I Sample Question Paper: I. Instruction Set Ii. Applications Iii. Memory Organization. I/O CompatibilityDocument5 paginiScheme - I Sample Question Paper: I. Instruction Set Ii. Applications Iii. Memory Organization. I/O CompatibilityC052 Diksha PawarÎncă nu există evaluări

- B.C.S. - Computer Organization & Assembly - January - April - 2016Document6 paginiB.C.S. - Computer Organization & Assembly - January - April - 2016Raj GamiÎncă nu există evaluări

- Vlsi QP 21,22Document11 paginiVlsi QP 21,22Arunitha ArulnathanÎncă nu există evaluări

- Term End Examination November 2012Document4 paginiTerm End Examination November 2012Akash SharmaÎncă nu există evaluări

- Question Paper Code:: (10 2 20 Marks)Document2 paginiQuestion Paper Code:: (10 2 20 Marks)AbdulAzizÎncă nu există evaluări

- UCS510Document2 paginiUCS510Subhav GoyalÎncă nu există evaluări

- OS set 3Document2 paginiOS set 3sriranganathan120Încă nu există evaluări

- March 2016: Subject: Computer Science IIDocument2 paginiMarch 2016: Subject: Computer Science IIAyushÎncă nu există evaluări

- Question Paper Code: X10348: Reg. NoDocument2 paginiQuestion Paper Code: X10348: Reg. NoJaikumar RajendranÎncă nu există evaluări

- Model QP Os Set 3 UpdatedDocument3 paginiModel QP Os Set 3 Updatednarenmadhavan5Încă nu există evaluări

- Wa0011Document2 paginiWa0011Ayushi BoliaÎncă nu există evaluări

- Scheme E - Digital Techniques and Microprocessor Sample Question PaperDocument3 paginiScheme E - Digital Techniques and Microprocessor Sample Question PaperHarshal DevadeÎncă nu există evaluări

- Practice Final SolnDocument17 paginiPractice Final SolnJimmie J MshumbusiÎncă nu există evaluări

- Future of Computer ArchitectureDocument46 paginiFuture of Computer ArchitecturemeerashekarÎncă nu există evaluări

- Digital Nov 07Document6 paginiDigital Nov 07skssushÎncă nu există evaluări

- 07A80305 COMPUTERORGANIZATIONANDARCHITECTUREfr 7607Document8 pagini07A80305 COMPUTERORGANIZATIONANDARCHITECTUREfr 7607Pulihora Kat RajaÎncă nu există evaluări

- Jntua University Previous Question Papers: Dept., of E.C.E, RCEWDocument4 paginiJntua University Previous Question Papers: Dept., of E.C.E, RCEWHarshini AÎncă nu există evaluări

- Model Answer: Maharashtra State Boarad of Technical Educatiod (Autonomous) (ISO/IEC-27001-2005 Certified)Document13 paginiModel Answer: Maharashtra State Boarad of Technical Educatiod (Autonomous) (ISO/IEC-27001-2005 Certified)Shreyas KingeÎncă nu există evaluări

- 2019DECDocument8 pagini2019DECAnupam GyawaliÎncă nu există evaluări

- Electronic engineer interview questions and answers for top tech companiesDocument4 paginiElectronic engineer interview questions and answers for top tech companiesAbhilashPadmanabhanÎncă nu există evaluări

- Embedded Systems 9168 - Sample Paper of MSBTE For Sixth Semester Final Year Computer Engineering Diploma (80 Marks)Document2 paginiEmbedded Systems 9168 - Sample Paper of MSBTE For Sixth Semester Final Year Computer Engineering Diploma (80 Marks)Sanjay DudaniÎncă nu există evaluări

- Microprocessors and Interfacing November Am Rr311903Document8 paginiMicroprocessors and Interfacing November Am Rr311903Nizam Institute of Engineering and Technology LibraryÎncă nu există evaluări

- DigitalLogic_ComputerOrganization_L26_RevisionDocument13 paginiDigitalLogic_ComputerOrganization_L26_RevisionPhan Tuấn KhôiÎncă nu există evaluări

- CMSC411 Midterm 1 SolutionsDocument6 paginiCMSC411 Midterm 1 SolutionsbsudheertecÎncă nu există evaluări

- CS 201Document3 paginiCS 201Jgapreet SinghÎncă nu există evaluări

- MP Lab CbcsDocument41 paginiMP Lab Cbcsanand_gudnavarÎncă nu există evaluări

- ME PAPER (SEM-1) For E.C. GTUDocument59 paginiME PAPER (SEM-1) For E.C. GTUGaurang RathodÎncă nu există evaluări

- R5310404 Digital IC Applications12Document1 paginăR5310404 Digital IC Applications12subbuÎncă nu există evaluări

- 172 CSE313 FinalDocument3 pagini172 CSE313 FinalSabbir HossainÎncă nu există evaluări

- Digital Interview QuestionsDocument5 paginiDigital Interview QuestionsAnindra NallapatiÎncă nu există evaluări

- Campusexpress - Co.in: Set No. 1Document8 paginiCampusexpress - Co.in: Set No. 1skssushÎncă nu există evaluări

- Microprocessor and Architecture Solution PDFDocument23 paginiMicroprocessor and Architecture Solution PDFKarmaveer Bhaurao Patil CollegeÎncă nu există evaluări

- SP ESE QuestionPaper Sem1 2019Document9 paginiSP ESE QuestionPaper Sem1 2019SK Relaxing MusicÎncă nu există evaluări

- Advanced Digital Logic DesignDocument2 paginiAdvanced Digital Logic DesignSougata GhoshÎncă nu există evaluări

- CSC319 - 356 - 141 - CSC319Document5 paginiCSC319 - 356 - 141 - CSC319Aniket AmbekarÎncă nu există evaluări

- Time: 3 Hours Total Marks: 70: Printed Pages: 2 Sub Code: REC-405 Paper Id: Roll NoDocument2 paginiTime: 3 Hours Total Marks: 70: Printed Pages: 2 Sub Code: REC-405 Paper Id: Roll NoATUL KUMAR YADAVÎncă nu există evaluări

- CS401-Computer Architecture and Assembly Language Programming Finalterm Examination Fall 2012Document33 paginiCS401-Computer Architecture and Assembly Language Programming Finalterm Examination Fall 2012lubnaÎncă nu există evaluări

- MCS 012Document118 paginiMCS 012SongYak YamÎncă nu există evaluări

- EEE-347 / CNG-336 Homework 1Document3 paginiEEE-347 / CNG-336 Homework 1rusdiÎncă nu există evaluări

- Antennas and Wave Propagation Fourth EditionDocument37 paginiAntennas and Wave Propagation Fourth EditionAsha JÎncă nu există evaluări

- RR320202-MICROPROCESSORS-AND-INTERFACING May2008Document7 paginiRR320202-MICROPROCESSORS-AND-INTERFACING May2008Hari PrasadÎncă nu există evaluări

- Digital System Design: Provided by Humayra JahanDocument5 paginiDigital System Design: Provided by Humayra JahanZabirÎncă nu există evaluări

- CSE 331 - Final - Assignment - v2Document5 paginiCSE 331 - Final - Assignment - v2S.M. Imam Jahed Hossain 1511500642Încă nu există evaluări

- CC 12 2021Document3 paginiCC 12 2021abishek singhÎncă nu există evaluări

- NB:-Write The Answers in Your Own Way and Do Not Copy From OtherDocument2 paginiNB:-Write The Answers in Your Own Way and Do Not Copy From OtherSayanMaitiÎncă nu există evaluări

- 2150707Document2 pagini2150707Virang PatelÎncă nu există evaluări

- Cisco: Section 1 - Basic Digital SectionDocument3 paginiCisco: Section 1 - Basic Digital SectionboiroyÎncă nu există evaluări

- CSE2006Document9 paginiCSE2006saugatÎncă nu există evaluări

- MCS 012june2020Document8 paginiMCS 012june2020kk2760057Încă nu există evaluări

- MP SoluDocument21 paginiMP SoluAhmad MukaddasÎncă nu există evaluări

- M.E Adsd Question PaperDocument2 paginiM.E Adsd Question PapershankarÎncă nu există evaluări

- Electronic Engineer Interview Questions GuideDocument7 paginiElectronic Engineer Interview Questions Guidepred87Încă nu există evaluări

- Transformer Math FormulaDocument4 paginiTransformer Math FormulafukscribdÎncă nu există evaluări

- Adapted Gaps Intro DietDocument2 paginiAdapted Gaps Intro DietfukscribdÎncă nu există evaluări

- Finally, An Easy, Affordable Breath Test For Small Intestine Bacterial Overgrowth (SIBO) !Document1 paginăFinally, An Easy, Affordable Breath Test For Small Intestine Bacterial Overgrowth (SIBO) !fukscribdÎncă nu există evaluări

- High and Low Fod Map FoodsDocument1 paginăHigh and Low Fod Map FoodsfukscribdÎncă nu există evaluări

- Irritable Bowel Syndrome Mechanisms and Dietary ManagementDocument42 paginiIrritable Bowel Syndrome Mechanisms and Dietary ManagementfukscribdÎncă nu există evaluări

- Adapted Gaps Intro DietDocument2 paginiAdapted Gaps Intro DietfukscribdÎncă nu există evaluări

- Idioms New PDFDocument61 paginiIdioms New PDFshothapp100% (2)

- (Arcexam - In) MCQs On Computer by Dr. Alok KumarDocument149 pagini(Arcexam - In) MCQs On Computer by Dr. Alok KumarBalajiÎncă nu există evaluări

- Idioms New PDFDocument61 paginiIdioms New PDFshothapp100% (2)

- (Arcexam - In) MCQs On Computer by Dr. Alok KumarDocument149 pagini(Arcexam - In) MCQs On Computer by Dr. Alok KumarBalajiÎncă nu există evaluări

- Active Passive+sol 4Document121 paginiActive Passive+sol 4aayushcooolzÎncă nu există evaluări

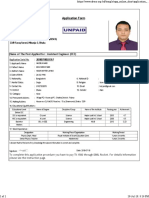

- Application - DESCO Form 2018Document1 paginăApplication - DESCO Form 2018fukscribdÎncă nu există evaluări

- Level I 2016 2017 Program ChangesDocument2 paginiLevel I 2016 2017 Program ChangesIam JaiÎncă nu există evaluări

- Application - DESCO Form 2018Document1 paginăApplication - DESCO Form 2018fukscribdÎncă nu există evaluări

- Active Passive+sol 4Document121 paginiActive Passive+sol 4aayushcooolzÎncă nu există evaluări

- Austen Jane Pride PrejudiceDocument201 paginiAusten Jane Pride PrejudicefukscribdÎncă nu există evaluări

- Wel Cfa b2b Cfa Level1 Graphic FinalDocument1 paginăWel Cfa b2b Cfa Level1 Graphic FinalDhruv JoshiÎncă nu există evaluări

- Application - DESCO Form 2018Document1 paginăApplication - DESCO Form 2018fukscribdÎncă nu există evaluări

- 9 10 16 - Civicscitizenship Bangla PDFDocument150 pagini9 10 16 - Civicscitizenship Bangla PDFSharmeen HelalÎncă nu există evaluări

- 42TH BMA SPL COURSE recruitment questionsDocument2 pagini42TH BMA SPL COURSE recruitment questionsLone SparrowÎncă nu există evaluări

- Level I 2016 2017 Program ChangesDocument2 paginiLevel I 2016 2017 Program ChangesIam JaiÎncă nu există evaluări

- Shushanta Paul English NoteDocument29 paginiShushanta Paul English NotefukscribdÎncă nu există evaluări

- Kotlin Coroutines Cheat Sheet PDFDocument1 paginăKotlin Coroutines Cheat Sheet PDFgeiledeutscheÎncă nu există evaluări

- Electrical Engineering Technology Department Ms. Jen AndadorDocument13 paginiElectrical Engineering Technology Department Ms. Jen Andadorpeter vanderÎncă nu există evaluări

- John 1990, Price: $59.95.: Graphical Models in Applied Multivariate StatisticsDocument1 paginăJohn 1990, Price: $59.95.: Graphical Models in Applied Multivariate StatisticsAqibAnsariÎncă nu există evaluări

- Sysview UserGuide ENUDocument205 paginiSysview UserGuide ENUborisg3Încă nu există evaluări

- DCDocument1 paginăDCBSAScitiÎncă nu există evaluări

- The Graphics Class: Maging, System - Drawing2D and System - Design NamespacesDocument12 paginiThe Graphics Class: Maging, System - Drawing2D and System - Design NamespacesnehaÎncă nu există evaluări

- Ivent101 Operator'S ManualDocument184 paginiIvent101 Operator'S ManualTrang PhạmÎncă nu există evaluări

- Resonant Inverter OrCADDocument13 paginiResonant Inverter OrCADCh ChristianÎncă nu există evaluări

- Resistivity and Geophysical Investigations Into The Subsurface Geology at Houghall Grange, Durham, Northern EnglandDocument9 paginiResistivity and Geophysical Investigations Into The Subsurface Geology at Houghall Grange, Durham, Northern EnglandCharlie KenzieÎncă nu există evaluări

- Facilities and Floor PlanDocument7 paginiFacilities and Floor Planapi-312955079Încă nu există evaluări

- Module 3Document60 paginiModule 3MydÎncă nu există evaluări

- Timothy Mo: Sour SweetDocument3 paginiTimothy Mo: Sour SweetSimion FloryÎncă nu există evaluări

- Digital Tools For Managing DiabetesDocument1 paginăDigital Tools For Managing DiabetesTaufiqurrokhman RofiiÎncă nu există evaluări

- ZAAA x32 Ironman SK (ZAA) & Captain SK (ZAAA) MB 6L E Version PDFDocument48 paginiZAAA x32 Ironman SK (ZAA) & Captain SK (ZAAA) MB 6L E Version PDFSebastian StanacheÎncă nu există evaluări

- Technical Specifications SSDDocument2 paginiTechnical Specifications SSDFelisha FebryÎncă nu există evaluări

- TASM 5 Intel 8086 Turbo AssemblerDocument3 paginiTASM 5 Intel 8086 Turbo AssemblerKeating Lopez100% (1)

- Image-Line Software RegistrationsDocument2 paginiImage-Line Software RegistrationsNahuel Perez0% (1)

- Simulation Summary ReportDocument3 paginiSimulation Summary ReportDivanshu ChaturvediÎncă nu există evaluări

- Army Aviation Digest - Apr 1985Document48 paginiArmy Aviation Digest - Apr 1985Aviation/Space History LibraryÎncă nu există evaluări

- Fiber Optic ManufacturingDocument4 paginiFiber Optic ManufacturingEarlÎncă nu există evaluări

- CTI Summit compressor control overviewDocument3 paginiCTI Summit compressor control overviewsalehÎncă nu există evaluări

- Daniel Reidy ResumeDocument1 paginăDaniel Reidy Resumeapi-395805597Încă nu există evaluări

- HuhuhuDocument3 paginiHuhuhuApril Yanda Hadi SatriaÎncă nu există evaluări

- AgilescrummethodologyDocument29 paginiAgilescrummethodologyNasir NaseemÎncă nu există evaluări

- Getting Started with Limelight VisionDocument83 paginiGetting Started with Limelight VisionHuma TajÎncă nu există evaluări

- Module4 ExceptionHandlingDocument3 paginiModule4 ExceptionHandlingSOHAM GANGURDEÎncă nu există evaluări

- SS901 DSD 95 DriveDocument4 paginiSS901 DSD 95 DriveSantosh InchalÎncă nu există evaluări