Documente Academic

Documente Profesional

Documente Cultură

Introduction To VLSI Design EC 361 2 Jan 2018: 1/2/2018 Usha Gogineni 1

Încărcat de

raja viriyala0 evaluări0% au considerat acest document util (0 voturi)

32 vizualizări17 paginivlsi intro

Titlu original

VLSI Design Lecture 1

Drepturi de autor

© © All Rights Reserved

Formate disponibile

PDF, TXT sau citiți online pe Scribd

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentvlsi intro

Drepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca PDF, TXT sau citiți online pe Scribd

0 evaluări0% au considerat acest document util (0 voturi)

32 vizualizări17 paginiIntroduction To VLSI Design EC 361 2 Jan 2018: 1/2/2018 Usha Gogineni 1

Încărcat de

raja viriyalavlsi intro

Drepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca PDF, TXT sau citiți online pe Scribd

Sunteți pe pagina 1din 17

Introduction to VLSI Design

EC 361

Lecture 1

2nd Jan 2018

1/2/2018 Usha Gogineni 1

Introduction to VLSI Design

(Circuit) Design:

Analog Circuits: Operate on Continuously Varying Signals

Eg: Operational Amplifiers

Digital Circuits: Operate on signals with one of two discrete values

Eg: Microprocessors

Mixed Signal Design: Contain both analog and digital circuits on a

single die.

Eg: Data Converters (A/D, D/A), Digital Radio

1/2/2018 Usha Gogineni 2

VLSI

Very Large Scale Integration > 10,000 transistors

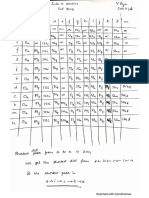

Processor Date of Clock Speed Transistor Count

introduction

Intel 4004 1971 108 kHz 2300

Intel 8086 1978 10 – 4.77 MHz 29,000

Intel 80486 1989 50 – 25 MHz 1,180,235

Intel Pentium 1993 66 – 60 MHz 3,100,000

Intel Pentium 4 2000 2 – 1.3 GHz 42,000,000

Intel Core 2 Duo 2006 2.4 - 1.8 GHz 291,000,000

Intel Core i7 Broadwell E 2016 3.5 GHz 3,200,000,000

10 core

AMD Ryzen 8 core 2017 3.6 GHz 4,800,000,000

1/2/2018 Usha Gogineni 3

Moore’s Law

Transistor Count doubles

every 2 years

1/2/2018 Usha Gogineni 4

MOSFET Scaling

CMOS Scaling has enabled VLSI

Processor Date of Clock Speed Transistor Count Process Chip Area

intro (mm2)

Intel 4004 1971 108 kHz 2300 10 mm 12 mm2

Intel 8086 1978 10 – 4.77 MHz 29,000 3 mm 33 mm2

Intel 80486 1989 50 – 25 MHz 1,180,235 1 mm 173 mm2

Pentium 1993 66 – 60 MHz 3,100,000 0.8 mm 294 mm2

Pentium 4 2000 2 – 1.3 GHz 42,000,000 0.18 mm 217 mm2

Core 2 Duo 2006 2.4 - 1.8 GHz 291,000,000 65 nm 143 mm2

Intel Core i7 Broadwell 2016 3.5 GHz 3,200,000,000 14 nm 246 mm2

E 10 core

AMD Ryzen 8 core 2017 3.6 GHz 4,800,000,000 14 nm 192 mm2

1/2/2018 Usha Gogineni 5

Minimum Feature Size

1/2/2018 Usha Gogineni 6

Clock Speed

1/2/2018 Usha Gogineni 7

1/2/2018 Usha Gogineni 8

Design Abstraction

Microprocessor

Adder

NAND, NOR

Implement gates

using transistors

MOSFET

1/2/2018 Usha Gogineni 9

MOSFET as a switch

1/2/2018 Usha Gogineni 10

Inverter

Symbol Circuit Schematic

Pull Up

Truth Table Pull Down

1/2/2018 Usha Gogineni 11

CMOS Logic

Pull Down Network

1/2/2018 Usha Gogineni 12

CMOS Logic

Pull Up Network

1/2/2018 Usha Gogineni 13

NAND Gate

Truth Table

Symbol 2-input NAND 3-input NAND

1/2/2018 Usha Gogineni 14

Compound Gates

Pull Down Network

Pull Up Network

1/2/2018 Usha Gogineni 15

Next Lecture

• CMOS Manufacturing

1/2/2018 Usha Gogineni 16

References

• Neil Weste and David Harris, “CMOS VLSI Design – A Circuits

and Systems Perspective”, 4th Edition

• Jan Rabaey, “Digital Integrated Circuits – A Design

Perspective”, 2nd Edition

• Other Sources …

1/2/2018 Usha Gogineni 17

S-ar putea să vă placă și

- Mt7621 DatasheetDocument43 paginiMt7621 DatasheetSimas ŽalaÎncă nu există evaluări

- ComparchDocument10 paginiComparchsnehal shindeÎncă nu există evaluări

- Introduction of MicroprocessorDocument53 paginiIntroduction of MicroprocessorMRAÎncă nu există evaluări

- What Is A MicroprocessorDocument10 paginiWhat Is A MicroprocessorSukanti PalÎncă nu există evaluări

- Module 4 - CODocument10 paginiModule 4 - COAnnabelleÎncă nu există evaluări

- Unit IDocument126 paginiUnit Iuradekaruna1972Încă nu există evaluări

- MICprocessor Unit 1Document46 paginiMICprocessor Unit 1Anjali MataleÎncă nu există evaluări

- What Is A Microprocessor?: Block Diagram of A MicrocomputerDocument5 paginiWhat Is A Microprocessor?: Block Diagram of A MicrocomputerSENTHIL RÎncă nu există evaluări

- Amf Ind T3538Document30 paginiAmf Ind T3538JamesÎncă nu există evaluări

- Pc-Ee 602Document19 paginiPc-Ee 602Koustav SahaÎncă nu există evaluări

- Poriyaan 1saxvBL6xpqZak6jOwx mFCPlMixrGDZmDocument37 paginiPoriyaan 1saxvBL6xpqZak6jOwx mFCPlMixrGDZmS. GobikaÎncă nu există evaluări

- 06 Advanced MOSFET PDFDocument153 pagini06 Advanced MOSFET PDFmayurÎncă nu există evaluări

- New Microsoft Word DocumenDocument19 paginiNew Microsoft Word Documenmelkamu mollaÎncă nu există evaluări

- Part 1Document66 paginiPart 1souleymanefomba57Încă nu există evaluări

- List of Intel Core 2 MicroprocessorsDocument38 paginiList of Intel Core 2 MicroprocessorsKaisar Ahmed KhanÎncă nu există evaluări

- Aphcore SimonKnowles v04Document25 paginiAphcore SimonKnowles v04ddscribeÎncă nu există evaluări

- MPMC Unit I 2021Document17 paginiMPMC Unit I 2021Venkatasamy EEEÎncă nu există evaluări

- 8085 MicroprocessorDocument37 pagini8085 MicroprocessorTilottama Deore100% (1)

- CpuDocument41 paginiCpukitty8200Încă nu există evaluări

- Microprocessor and Interfacing Unit 1Document10 paginiMicroprocessor and Interfacing Unit 1Shubham SoniÎncă nu există evaluări

- Module 5 MergedDocument98 paginiModule 5 MergedNithish Kumar A NÎncă nu există evaluări

- 1 Introduction To 8086Document18 pagini1 Introduction To 8086PREETI SAI THANDAVAN 20BCE1740Încă nu există evaluări

- 1 Introduction To 8086Document18 pagini1 Introduction To 8086Sudeeksha GanguliÎncă nu există evaluări

- UNIT-1: 1. Introduction To Microprocessors 2. Internal Architecture of 8086 3. Addressing Modes of 8086Document91 paginiUNIT-1: 1. Introduction To Microprocessors 2. Internal Architecture of 8086 3. Addressing Modes of 8086Sri ChandanaÎncă nu există evaluări

- Lecture Week2 Embedded SystemsDocument55 paginiLecture Week2 Embedded SystemsDerek WangÎncă nu există evaluări

- ProcessorsDocument3 paginiProcessorsFaisal HaroonÎncă nu există evaluări

- Microprocessor: Prepared by Engr. Rynefel ElopreDocument16 paginiMicroprocessor: Prepared by Engr. Rynefel ElopreRynefel ElopreÎncă nu există evaluări

- 8085 Introduction - OptDocument36 pagini8085 Introduction - OptVenkatasamy EEEÎncă nu există evaluări

- 8086 Architecture and Pin DiscriptionDocument20 pagini8086 Architecture and Pin DiscriptionDr Sreenivasa Rao IjjadaÎncă nu există evaluări

- Any Device, Any Time, Any Where: Introduction To VLSI Design and Design ChallengesDocument40 paginiAny Device, Any Time, Any Where: Introduction To VLSI Design and Design ChallengesYash BhattÎncă nu există evaluări

- Encapsulation and Tunneling: Encapsulation Describes The Process of Placing An IP Datagram Inside ADocument36 paginiEncapsulation and Tunneling: Encapsulation Describes The Process of Placing An IP Datagram Inside ANoman AliÎncă nu există evaluări

- Comparison of Intel® MicroprocessorsDocument5 paginiComparison of Intel® MicroprocessorsChetan GuptaÎncă nu există evaluări

- Timeline - Intel ProcessorDocument18 paginiTimeline - Intel ProcessorRemarCaballeroÎncă nu există evaluări

- ch01 IntroductionDocument29 paginich01 IntroductionHASHIR KHANÎncă nu există evaluări

- Bluetooth Based Home Appliances ControllerDocument77 paginiBluetooth Based Home Appliances ControllerCrispÎncă nu există evaluări

- MM Module1 CseDocument137 paginiMM Module1 CseAnonymous ivcUHwjChEÎncă nu există evaluări

- ECE391 - Ch1 - Basics of Computer SystemsDocument21 paginiECE391 - Ch1 - Basics of Computer SystemsAnh Hào NguyễnÎncă nu există evaluări

- CO Notes Mod 4Document10 paginiCO Notes Mod 4Amal MonichanÎncă nu există evaluări

- Microprocessors & Interfacing For GITAM University ECEDocument118 paginiMicroprocessors & Interfacing For GITAM University ECEDr Sreenivasa Rao Ijjada100% (1)

- Plextor M8PeG en 0516Document2 paginiPlextor M8PeG en 0516Roxana PetrescuÎncă nu există evaluări

- 7 Series FPGAs OverviewDocument16 pagini7 Series FPGAs Overviewreza_azadÎncă nu există evaluări

- Basic Micro ProcessorsDocument21 paginiBasic Micro ProcessorsishapptÎncă nu există evaluări

- Rsa Netwitness Logs and Packets: Server, Dac and San HW SpecificationsDocument10 paginiRsa Netwitness Logs and Packets: Server, Dac and San HW SpecificationsfunyiroemberÎncă nu există evaluări

- Microprocessors & their Operating Systems: A Comprehensive Guide to 8, 16 & 32 Bit Hardware, Assembly Language & Computer ArchitectureDe la EverandMicroprocessors & their Operating Systems: A Comprehensive Guide to 8, 16 & 32 Bit Hardware, Assembly Language & Computer ArchitectureEvaluare: 1 din 5 stele1/5 (1)

- ECSMcp73T M3Document5 paginiECSMcp73T M3registers0% (1)

- GIGABYTE HD 6670 2 GB Specs - TechPowerUp GPU DatabaseDocument3 paginiGIGABYTE HD 6670 2 GB Specs - TechPowerUp GPU DatabaseMarcusÎncă nu există evaluări

- Camera Features FeasibilityDocument6 paginiCamera Features FeasibilityAbdullah KhalidÎncă nu există evaluări

- MP QabankDocument81 paginiMP QabankPreethamkumarms PreethamÎncă nu există evaluări

- Session - I Microprocessors-The Solution in Search of ProblemsDocument75 paginiSession - I Microprocessors-The Solution in Search of ProblemsPratik PetkarÎncă nu există evaluări

- AN4397-Common Hardware DesignDocument20 paginiAN4397-Common Hardware Designpaviliondv6Încă nu există evaluări

- 25.2. SCADA TRANSMISI FLORES - REVIEW Rev1Document39 pagini25.2. SCADA TRANSMISI FLORES - REVIEW Rev1MegsÎncă nu există evaluări

- EE310: Introduction To VLSI DesignDocument73 paginiEE310: Introduction To VLSI DesignPuneeth VenkataÎncă nu există evaluări

- Product OverviewDocument17 paginiProduct Overviewjsouza souzaÎncă nu există evaluări

- Prepaid Card Petrol BankDocument67 paginiPrepaid Card Petrol Bankimran kadriÎncă nu există evaluări

- University Institute of EnggDocument51 paginiUniversity Institute of EnggMeghna ChatterjeeÎncă nu există evaluări

- Introduction of MicroprocessorDocument13 paginiIntroduction of MicroprocessorHaafizee FizÎncă nu există evaluări

- Advanced ProcessorsDocument31 paginiAdvanced ProcessorsPraveen GovindÎncă nu există evaluări

- ,, ,,, Enhanced Intel Technology (EIST),, XD Bit (An Implementation)Document5 pagini,, ,,, Enhanced Intel Technology (EIST),, XD Bit (An Implementation)mahesa34Încă nu există evaluări

- Inside Intel Inside WorksheetDocument14 paginiInside Intel Inside WorksheetSaurav suroliaÎncă nu există evaluări

- Dev Board Mini Datasheet: FeaturesDocument14 paginiDev Board Mini Datasheet: Featuresjaime salamancaÎncă nu există evaluări

- Satellite Communications Final-30Document1 paginăSatellite Communications Final-30raja viriyalaÎncă nu există evaluări

- Satellite Communications Final-24Document1 paginăSatellite Communications Final-24raja viriyalaÎncă nu există evaluări

- Satellite Communications Final-29Document1 paginăSatellite Communications Final-29raja viriyalaÎncă nu există evaluări

- Satellite Communications Final-27Document1 paginăSatellite Communications Final-27raja viriyalaÎncă nu există evaluări

- Figure 1.15: Launching Stages of A GEO (Example: Rocket LaunchDocument1 paginăFigure 1.15: Launching Stages of A GEO (Example: Rocket Launchraja viriyalaÎncă nu există evaluări

- Satellite Communications Final-23Document1 paginăSatellite Communications Final-23raja viriyalaÎncă nu există evaluări

- Satellite Communications Final-28Document1 paginăSatellite Communications Final-28raja viriyalaÎncă nu există evaluări

- Satellite Communications Final-25Document1 paginăSatellite Communications Final-25raja viriyalaÎncă nu există evaluări

- Satellite Communications Final-22Document1 paginăSatellite Communications Final-22raja viriyalaÎncă nu există evaluări

- Satellite Communications Final-21Document1 paginăSatellite Communications Final-21raja viriyalaÎncă nu există evaluări

- Satellite Communications Final-20Document1 paginăSatellite Communications Final-20raja viriyalaÎncă nu există evaluări

- Satellite Communications Final-19Document1 paginăSatellite Communications Final-19raja viriyalaÎncă nu există evaluări

- Satellite Communications Final-18Document1 paginăSatellite Communications Final-18raja viriyalaÎncă nu există evaluări

- Satellite Communications Final-16Document1 paginăSatellite Communications Final-16raja viriyalaÎncă nu există evaluări

- Satellite Communications Final-12Document1 paginăSatellite Communications Final-12raja viriyalaÎncă nu există evaluări

- Satellite Communications Final-10Document1 paginăSatellite Communications Final-10raja viriyalaÎncă nu există evaluări

- Satellite Communications Final-15Document1 paginăSatellite Communications Final-15raja viriyalaÎncă nu există evaluări

- Satellite Communications Final-17Document1 paginăSatellite Communications Final-17raja viriyalaÎncă nu există evaluări

- Satellite Communications Final-14Document1 paginăSatellite Communications Final-14raja viriyalaÎncă nu există evaluări

- Satellite Communications Final-13Document1 paginăSatellite Communications Final-13raja viriyalaÎncă nu există evaluări

- Untitled 4Document1 paginăUntitled 4raja viriyalaÎncă nu există evaluări

- Satellite Communications Final-9Document1 paginăSatellite Communications Final-9raja viriyalaÎncă nu există evaluări

- Satellite Communications Final-11Document1 paginăSatellite Communications Final-11raja viriyalaÎncă nu există evaluări

- Course Objectives and OutcomesDocument1 paginăCourse Objectives and Outcomesraja viriyalaÎncă nu există evaluări

- End-Sem QuizDocument1 paginăEnd-Sem Quizraja viriyalaÎncă nu există evaluări

- Course Objectives and OutcomesDocument1 paginăCourse Objectives and Outcomesraja viriyalaÎncă nu există evaluări

- Satellite Communications FinalDocument146 paginiSatellite Communications Finalraja viriyalaÎncă nu există evaluări

- Satellite Communication: SyllabusDocument1 paginăSatellite Communication: Syllabusraja viriyalaÎncă nu există evaluări

- ItrDocument10 paginiItrraja viriyalaÎncă nu există evaluări

- Scanned With CamscannerDocument14 paginiScanned With Camscannerraja viriyalaÎncă nu există evaluări

- Behavior of Structure Under Blast LoadingDocument32 paginiBehavior of Structure Under Blast Loadingramyashri inalaÎncă nu există evaluări

- Data Sheet - enDocument2 paginiData Sheet - enrodriggoguedesÎncă nu există evaluări

- Friction Clutches PDFDocument14 paginiFriction Clutches PDFamanmittal0850% (2)

- HCL McQs SET-3Document8 paginiHCL McQs SET-3ThorÎncă nu există evaluări

- Bafbana Module 5Document12 paginiBafbana Module 5VILLANUEVA, RAQUEL NONAÎncă nu există evaluări

- Pro ESEDocument2 paginiPro ESEquadhirababilÎncă nu există evaluări

- Hydraulic Structure - 16 - 30 - FianalDocument26 paginiHydraulic Structure - 16 - 30 - FianalMahmood YounsÎncă nu există evaluări

- Electroculture by Briggs, Lyman J & Others 1926Document38 paginiElectroculture by Briggs, Lyman J & Others 1926Mashae McewenÎncă nu există evaluări

- Force Vectors: Scalars and Vectors 2D and 3D Force SystemsDocument20 paginiForce Vectors: Scalars and Vectors 2D and 3D Force Systemsdanaluca2753Încă nu există evaluări

- ME361 - Manufacturing Science Technology: Measurements and MetrologyDocument20 paginiME361 - Manufacturing Science Technology: Measurements and MetrologyKartikeyaÎncă nu există evaluări

- Gantry Crane DesignDocument2 paginiGantry Crane DesignSophia PoBari-Soter (MenaXrux)Încă nu există evaluări

- 07a80809 OperationsresearchDocument11 pagini07a80809 OperationsresearchSharanya ThirichinapalliÎncă nu există evaluări

- Vinco Lesson Plan CO2 2022 EditedDocument8 paginiVinco Lesson Plan CO2 2022 EditedAdrianalover RescofanaticsÎncă nu există evaluări

- SO100K Installation InstructionDocument32 paginiSO100K Installation InstructionAlwin Anno SastraÎncă nu există evaluări

- Opposite Corners CourseworkDocument8 paginiOpposite Corners Courseworkpqltufajd100% (2)

- MT-LXX Parallel Manual PDFDocument120 paginiMT-LXX Parallel Manual PDFJunior Alexander Rodriguez Rodriguez0% (1)

- Soil Bearing Capacity CalculationDocument29 paginiSoil Bearing Capacity CalculationJohn Jerome TerciñoÎncă nu există evaluări

- 125 Tractor: (Specifications and Design Subject To Change Without Notice)Document5 pagini125 Tractor: (Specifications and Design Subject To Change Without Notice)Gary LarsonÎncă nu există evaluări

- Bearing Reliability Improvement-SKFDocument55 paginiBearing Reliability Improvement-SKFAbdulrahman AlkhowaiterÎncă nu există evaluări

- 4 A Short History of Islamic Science From Genesis To Decline ShortversionDocument24 pagini4 A Short History of Islamic Science From Genesis To Decline ShortversionKateryna KuslyvaÎncă nu există evaluări

- The ParagraphDocument4 paginiThe Paragraphapi-238710927Încă nu există evaluări

- Sesam and Bladed - Efficient Coupled Analyses - Webinar Presentation - tcm8-102589 PDFDocument31 paginiSesam and Bladed - Efficient Coupled Analyses - Webinar Presentation - tcm8-102589 PDFsamiransmitaÎncă nu există evaluări

- Pages À Partir de Hyundai-Terracan-2001-2007-factory-service-manualDocument10 paginiPages À Partir de Hyundai-Terracan-2001-2007-factory-service-manualcointoinÎncă nu există evaluări

- Chapter 4 Statistial Process Control (SPC)Document22 paginiChapter 4 Statistial Process Control (SPC)Yousab CreatorÎncă nu există evaluări

- Ratio Worksheet AKDocument12 paginiRatio Worksheet AKChika AuliaÎncă nu există evaluări

- Jet Powered BoatDocument22 paginiJet Powered BoatMagesh OfficialÎncă nu există evaluări

- Yuzuru Hanyu - ThesisDocument6 paginiYuzuru Hanyu - ThesisFatima Esperanza Ortiz Ortiz100% (4)

- Google F1 DatabaseDocument12 paginiGoogle F1 DatabasenulloneÎncă nu există evaluări

- Tutorial 1 PDFDocument2 paginiTutorial 1 PDFSYAFIQAH ISMAIL100% (1)

- Activity 2 Resultant Vector by Graphical MethodDocument2 paginiActivity 2 Resultant Vector by Graphical MethodRick Ignacio0% (1)