Documente Academic

Documente Profesional

Documente Cultură

Z80 Linguagem Assembly 2

Încărcat de

Carlos Enrique BortolotoDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Z80 Linguagem Assembly 2

Încărcat de

Carlos Enrique BortolotoDrepturi de autor:

Formate disponibile

LINGUAGEM ASSEMBLY

1. GENERALIDADES

1.1 – Histórico do início dos microprocessadores

Em 1971, a INTEL lançou o primeiro microprocessador no mercado, o 4004.

Com repertório de 46 instruções, era adequado para aplicações de controle de

processos que necessitavam de tomadas de decisões e operações aritméticas

simples. O microprocessador 4004 tinha um “DATA BUS” de 4 bits e tinha

capacidade de realizar até 100.000 operações de adições por segundo, em 2

operandos de 4 bits de extensão.

A geração seguinte de microprocessadores, caracterizou-se principalmente,

por um “DATA BUS” de 8 bits.

Em 1972, a INTEL lançou o 8008, encabeçando os microprocessadores desta

geração. Tal microprocessador apresentava um repertório de 48 instruções,

podendo endereçar até 16K de memória, e podendo realizar aproximadamente

80.000 operações de adição por segundo, em 2 operandos de 8 bits de

extensão.

Após o seu lançamento, o microprocessador 8008 foi largamente difundido

através da indústria eletrônica num curto espaço de tempo, principalmente

porque não havia mais nada do gênero de outros fabricantes.

Ainda dentro da linha de microprocessadores de 8 bits, em 1973 a INTEL

lançou o 8080, que se tornou um dos microprocessadores mais usados,

assumindo uma posição privilegiada em relação aos numerosos concorrentes,

posteriormente disseminados no mercado mundial.

O repertório de instruções do 8080, incluía o conjunto de instruções do

microprocessador 8008 e 30 instruções adicionais. Desta forma, o usuário do

8008 poderia evoluir para o 8080 aproveitando todo o software já desenvolvido

para o 8008.

Do ponto de vista de velocidade de processamento, o 8080 podia executar até

500.000 instruções de soma por segundo, com 2 operandos de 8 bits. A

capacidade máxima de endereçamento do 8080 era de 64k de memória.

Em 1976, a INTEL desenvolveu uma série de melhorias no 8080, lançando o

microprocessador 8085. Esse microprocessador atingiu um índice maior de

integração, incorporando algumas simplificações de hardware. No entanto,

manteve o repertório de instruções semelhante ao 8080, adicionando apenas

duas instruções (RIM e SIM).

O microprocessador Z-80, lançado pela ZILOG, logo após ao 8085, veio trazer

novos aperfeiçoamentos. O repertório de instruções do Z-80, inclui o conjunto

de instruções do microprocessador 8080 e 80 instruções adicionais. Desta

forma, o software do Z-80 é compatível com a linha 8008 e 8080, permitindo o

aproveitamento de todos os programas já desenvolvidos. Além da

compatibilidade de software as seguintes melhorias foram implementadas:

Apostila de propriedade do Prof. Cruz 1

- Duplicação do número de registros de uso geral.

- A incorporação de novas técnicas para otimizar o endereçamento de

memória.

- O acréscimo no microprocessador de um hardware que, no 8080 e 8085,

tinha que ser realizado externamente.

Igualmente aos microprocessadores fabricados pela INTEL (8080 e 8085) o Z-

80 utiliza tecnologia NMOS e necessita apenas uma alimentação de 5V,

apresenta saídas e entradas compatíveis com a lógica TTL.

1.2 – Características dos microprocessadores

Os principais componentes dos microprocessadores estão apresentados na

Figura 1.1.

ULA = Unidade Lógica Aritmética

R E/S = Registro de Entrada / Saída

RDM = Registro de Dado da Memória

REM = Registro de Endereço da Memória

CI = Contador de Instrução

RI = Registro de Instrução

R

D

M

ULA

REM

CI

AC

RI

UNIDADE DE

CONTROLE

R E/S

SAÍDAS ENTRADAS

Figura 1.1 – Componentes dos microprocessadores

Apostila de propriedade do Prof. Cruz 2

a) Unidade Lógica e Aritmética (ULA)

A ULA contém o acumulador, o registro de flags e alguns registros

temporários que são inacessíveis ao programador. Operações

aritméticas, lógicas e de rotação são executadas pela ULA. O resultado

destas operações podem ser depositadas no acumulador ou podem ser

transferidas para a Via de Dados interna para serem usadas em outros

registros.

b) Acumulador (AC)

É o registro de maior versatibilidade sendo referenciado explicitamente ou

implicitamente por um grande número de instruções, as quais incluem

instruções lógicas, aritméticas, carregar, armazenar, deslocamentos,

rotações e transferências de E/S.

c) Unidade de Controle (UC)

Usualmente esta unidade, utilizando sinais de clocks externos, mantém

uma sequência própria de eventos necessários à realização de uma dada

tarefa. Normalmente esta unidade é capaz de responder à sinais

externos, tais como: pedido de interrupção do processamento de uma

tarefa, pedido de espera de um dispositivo lento, etc.

d) Registro de Instrução (RI)

Sob o controle da UC o código de operação é trazido da memória para o

microprocessador durante o ciclo de busca (fetch) sendo armazenado no

RI.

e) Contador de Instrução (CI)

É o registro que mantém o endereço da próxima instrução a ser

executada.

f) Registro de Endereço da Memória (REM)

Mantém o endereço presente na Via de Endereços durante leitura/escrita

em memória.

O número de bits do REM determina o espaço de endereçamento do

microprocessador.

g) Registro de Dado da Memória (RDM)

Funciona como buffer de interface entre a Via de Dados interna do

microprocessador e a via externa.

O número de bits do RDM caracteriza a largura da Via de Dados do

microprocessador.

Apostila de propriedade do Prof. Cruz 3

h) Registro de Entrada/Saída (R E/S)

Utilizado nas transferências de dados entre o microprocessador e

periféricos.

1.3 – Conceitos Básicos de Programação

As informações manipuladas pelos microcomputadores são de dois tipos:

Instruções e Dados.

As instruções são comandos que governam a transferência de informação

dentro da máquina e especificam a operação lógica ou aritmética a ser

realizada, bem como onde buscar o operando. Especificam também a

transferência de informações, entre a máquina e o meio exterior. Um grupo de

instruções logicamente relacionadas para realizar uma dada tarefa é

denominado Programa.

O microprocessador tem o seu comportamento governado por instruções as

quais encontram-se armazenadas na memória. O microprocessador é o

responsável em buscar a instrução, decodificá-la e realizar as operações

exigidas pela mesma. Estas operações são realizadas sequencialmente, sendo

que as micro-operações realizadas em cada passo, são determinadas pela

Unidade de Controle do microprocessador.

A tarefa de buscar (fetch) e executar uma única instrução é denominada Ciclo

de Instrução.

Na Figura 1.2 é apresentado um fluxograma caracterizando o modo de

operação do microprocessador.

As instruções que formam um programa são armazenadas na memória, sendo

utilizadas pelo microprocessador para determinar as ações específicas deste.

Assim sendo, este precisa conhecer a localização da próxima instrução a ser

executada, e para isto, o microprocessador possui um registro que mantém o

endereço da próxima instrução a ser executada, registro este denominado

Contador de Instrução.

Cada operação que o microprocessador pode realizar é identificada por uma

palavra binária conhecida como código de operação. O mecanismo pelo qual o

microprocessador converte o código de operação em atividades específicas de

processamento é realizado pela Unidade de Controle (UC).

Sob o controle da UC o código de operação é trazido da memória para o

microprocessador durante o ciclo de busca sendo armazenado no registro de

instrução. O decodificador de instrução e circuitos de controle, utilizando a

palavra binária disponível no RI, mantém durante o ciclo de execução uma

sequencia própria de eventos necessários a tarefa de processamento da

instrução corrente.

A sequencialização dos eventos tem por base o sinal de relógio fornecido ao

microprocessador.

Apostila de propriedade do Prof. Cruz 4

INÍCIO

CICLO DE BUSCA

N

FETCH

START

ATIVADO?

CICLO DE INSTRUÇÃO

S

BUSCAR A

INSTRUÇÃO

EXECUTAR A

INSTRUÇÃO

CICLO DE EXECUÇÃO

HÁ

N INTERRUPÇÕES

AGUARDANDO O

ATENDIMENTO?

TRANSFERIR CONTROLE

P/ PROGRAMA QUE

ATENDE INTERRUPÇÕES

Figura 1.2 – Modo de Operação do Microprocessador

Apostila de propriedade do Prof. Cruz 5

1.4 – Mapa de Registros do Microprocessador Z-80

1.4.1 – Introdução

Os registros que o Z-80 possui estão apresentados na Figura 1.3.

8 bits 8 bits

Registro de Condição (F) Registro de Condição Ativo

Acumulador (A)

Registro B (B) Registro C (C)

Registros Ativos de Uso Geral

Registro D (D) Registro E (E)

Registro H (H) Registro L (L)

Registro de Condição (F’) Registro de Condição Passivo

Acumulador’ (A’)

Registro B’ (B’) Registro C’ (C’)

Registros Passivos de Uso Geral

Registro D’ (D’) Registro E’ (E’)

Registro H’ (H’) Registro L’ (L’)

Contador de Programa (PC)

Ponteiro de Pilha (SP)

Registro de Índice X (IX)

Registros de Uso Específico

Registro de Índice Y (IY)

Registro I

Registro R

Figura 1.3 – Mapa de Registros do Z-80

1.4.2 – Registros de Uso Geral

O Z-80 possui 14 registros de uso geral, de 8 bits cada um, e estão divididos

em 2 grupos de 7 registros cada.

ATIVOS PASSIVOS

A A’

B B’

C C’

D D’

E E’

H H’

L L’

Figura 1.4 – Registros de Uso Geral do Z-80

Apostila de propriedade do Prof. Cruz 6

Os registros de uso geral e os registros F e F’, são também classificados,

durante a execução de um programa em ativos e passivos. Em qualquer

instante tem-se 8 registros ativos e 8 registros passivos. Os registros passivos

só podem ser alterados quando tornarem-se ativos.

Uma vantagem de se ter 2 blocos de registros de uso geral é a maior

disponibilidade de registros no interior do Z-80, o que permite o acesso mais

rápido às informações do que as mesmas estivessem armazenadas na

memória. Outra vantagem é que o programador pode trocar rapidamente de

um bloco de registro para outro. Isto é usado, principalmente, na troca de

contexto durante o atendimento de interrupções.

1.4.3 – Registros de Flags

O Z-80 possui 2 registros de flags (F e F’) sendo que, um deles é ativo e outro

passivo.

Cada registro de flags tem 8 bits, dos quais somente 6 são usados.

O registro de flags ativo funciona associado ao acumulador e à ULA, e cada

um de seus bits indica uma situação definida, resultante basicamente de

operações lógicas e aritméticas.

A figura 1.5 apresenta o registro de flags.

D7 D0

S Z H P/V N C

Figura 1.5 – Registro de Flags

Descrição dos bits do registro de flags:

a) Bit C (Carry bit)

Indica a ocorrência de “VAI UM” ou “TRANSBORDO”, no 8º bit, após a

realização de uma soma, ou de empréstimo (BORROW) quando se efetua

uma subtração, assumindo o valor “1” se houver tal ocorrência, ou o valor

“0”, se não houver.

b) Bit N (Subtract bit)

De uma maneira geral, assume o valor “0” após as instruções de soma, e o

valor “1” após as instruções de subtração.

Apostila de propriedade do Prof. Cruz 7

c) Bit P/V (Parity/Overflow bit)

Representa paridade ou transbordo, dependendo da instrução executada.

No caso de representar paridade temos:

- P/V = 1 indica paridade par

No caso de representar transbordo temos:

- P/V = 1 indica que houve transbordo (normalmente usada depois de

uma operação aritmética).

d) Bit H (Half-carry bit)

Indica a ocorrência de “VAI UM”, ou “EMPRÉSTIMO” do quarto para o

quinto bit do resultado, na realização de uma soma ou uma subtração.

Assume valor “1” se houver tal ocorrência.

e) Bit Z (Zero bit)

Normalmente usado após uma operação lógica ou aritmética e indica o

seguinte:

- Z = 1 quando o resultado é nulo.

f) Bit S (Sinal bit)

Representa o sinal de um resultado (em complemento de 2) e indica o

seguinte:

- S = 1 significa que o resultado é um número negativo.

1.4.4 – Registros de Uso Específico

O Z-80 possui 4 registros de 16 bits e 2 de 8 bits, que operam com finalidades

específicas.

Os registros de 16 bits são:

- Contador de programa (PC)

- Ponteiro da pilha (SP)

- Registros de índice (IX e IY)

Os registros de 8 bits são:

- Registro de interrupção (I)

- Registro de refrescamento (R)

Apostila de propriedade do Prof. Cruz 8

1.4.4.1 – Descrição dos 4 registros de 16 bits

a) Contador de Programa (PC)

O PC é atualizado ao término de cada instrução, de modo a conter o

endereço da próxima instrução a ser executada.

As instruções do Z-80 podem ocupar de 1 a 4 bytes consecutivos da

memória. Desta forma, a Unidade de Controle incrementa automaticamente

o conteúdo do PC de 1,2,3 ou 4, dependendo do número de bytes da

instrução que está em execução.

Esta atualização seqüencial do PC é quebrada quando o Z-80 executa

instruções que alteram o curso normal do programa. Estas instruções, por

exemplo: JP, CALL, RET e RST, carregam o PC com um novo valor.

b) Ponteiro da Pilha (SP)

O SP endereça o último dado inserido ou o seguinte ao que foi retirado, isto

é, o topo da pilha.

Nos microcomputadores, uma das utilizações da pilha é o armazenamento

temporário de registros, de uma maneira sistemática e organizada

(estrutura LIFO – último a entrar e o primeiro a sair).

Outra aplicação da pilha é o armazenamento do endereço de retorno em

chamadas de subrotinas e no tratamento de pedidos de interrupções.

c) Registros de Índice (IX e IY)

São registros que permitem ao Z-80 calcular endereços de operandos de

instruções que utilizam a técnica de endereçamento indexado. Estes

registros armazenam um valor de 16 bits que é o endereço base para uma

região da memória, onde um dado será gravado ou lido.

Um byte adicional , incluso numa instrução indexativa, é usado para

especificar o deslocamento do endereço, em relação a base fixa.

As instruções com endereçamento indexado são usadas principalmente em

aplicações com listas e tabelas.

1.4.4.2 – Descrição dos 2 registros de 8 bits

a) Registro de Interrupção (I)

O registro I é usado no atendimento de interrupção. O seu conteúdo é

previamente carregado pelo programador e representa os 8 bits mais

significativos do endereço do vetor de interrupção. A parte menos

Apostila de propriedade do Prof. Cruz 9

significativa deste endereço é gerada pelo dispositivo de E/S que requisitou

o pedido de interrupção.

O vetor de interrupção é o endereço da primeira instrução da rotina de

tratamento de interrupção. Associado a uma instrução de desvio leva o Z-

80 a executar esta rotina.

b) Registro de Refrescamento (R)

O registro R tem como função controlar o refrescamento automático de

memórias dinâmicas, é incrementado, automaticamente, a cada ciclo de

busca de instruções.

O dado contido no registro R é enviado para a memória, através dos 7 bits

menos significativos da via de endereços (A0 a A6), durante o sinal de

controle de refrescamento. Isto ocorre em paralelo com o processamento

interno da instrução, justamente nos intervalos de tempo em que a

execução da instrução não requer o uso das vias.

Este modo de refrescamento é totalmente transparente ao programador e

não diminui o tempo de processamento.

Apostila de propriedade do Prof. Cruz 10

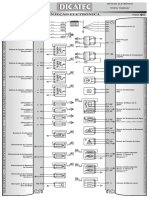

2. CONJUNTO DE INSTRUÇÕES

2.1 – Generalidades

-n indica valor Constante de 8 bits (00H a FFH)

- nn indica valor Constante de 16 bits (0000H a FFFFH)

- o valor do flag depende do resultado da operação

- • o valor do flag não é alterado pela operação

-0 o valor do flag é resetado (colocado em “0”) pela operação

-1 o valor do flag é setado (colocado em “1”) pela operação

-X o valor do flag é “don’t care”

-r um dos registros: A, B, C, D, E, H, L

-s conteúdo de 8 bits (A, B, C, D, E, H, L, (HL), (IX+d), (IY+d), constante

de 8 bits)

- ss um dos pares de registros: BC, DE, HL ou SP

- ii um dos registros de índice: IX ou IY

-R registro R

-m conteúdo de 8 bits (A, B, C, D, E, H, L, (HL), (IX+d), (IY+d) )

- IFF flip-flop de interrupção

- dd um dos pares de registros: BC, DE, HL ou SP

- qq um dos pares de registros: BC, DE, HL, AF

-d uma constante de 8 bits em complemento de 2

- pp um dos pares de registros: BC, DE ou IX ou SP

- rr um dos pares de registros: BC, DE ou IY ou SP

2.2 – Instruções do Z-80

Apostila de propriedade do Prof. Cruz 11

COND. DE FLAGS Nº DE

MNEMÔNICO DESCRIÇÃO OPERAÇÃO

C Z P/V S N H EST.

LD r,r Carrega o registro r com o registro r r←r • • • • • • 4

LD r,n Carrega o registro r com a constante n r←n • • • • • • 7

LD r, (HL) Carrega o registro r com o conteúdo da posição de r←(HL) • • • • • • 7

memória endereçada pelo par HL

LD r,(IX+d) Carrega o registro r com o conteúdo da posição de r ← (IX + d) • • • • • • 19

memória endereçada por IX + d

LD r, (IY+d) Carrega o registro r com o conteúdo da posição de r ← (IY+d) • • • • • • 19

memória endereçada por IY + d

LD (HL),r Carrega o conteúdo da posição de memória endereçada (HL) ← r • • • • • • 7

pelo par HL com o registro r

LD (IX + d),r Carrega o conteúdo da posição de memória endereçada (IX+d) ← r • • • • • • 19

por IX + d com o registro r

LD (HL),n Carrega o conteúdo da posição de memória endereçada (HL) ← n • • • • • • 10

pelo par HL com a constante n

LD (IX + d),n Carrega o conteúdo da posição de memória endereçada (IX + d) ← n • • • • • • 19

por IX + d com a constante n

LD (IY + d),n Carrega o conteúdo da posição de memória IY + d, com a (IY + d) ← n • • • • • • 19

constante n

LD A, (BC) Carrega o Acumulador com o conteúdo da posição de A ← (BC) • • • • • • 7

memória endereçada pelo par BC

LD A, (DE) Carrega o Acumulador com o conteúdo da posição de A ← (DE) • • • • • • 7

memória endereçada pelo par DE

LD A, (nn) Carrega o Acumulador com o conteúdo da posição de A ← (nn) • • • • • • 13

memória nn

LD (BC), A Carrega o conteúdo da posição de memória endereçada (BC) ← A • • • • • • 7

pelo par BC com o Acumulador

LD (DE), A Carrega o conteúdo da posição de memória endereçada (DE) ← A • • • • • • 7

pelo par DE com o Acumulador

LD (nn), A Carrega o conteúdo da posição de memória nn com o (nn) ← A • • • • • • 13

Acumulador

↔ ↔

↔ ↔

LD A,I Carrega o Acumulador com o registro I A←I • IFF • • 9

LD A, R Carrega o Acumulador com o registro R A←R • IFF • • 9

LD I,A Carrega o registro I com o Acumulador I←A • • • • • • 9

LD R,A Carrega o registro R com o Acumulador R←A • • • • • • 9

LD dd,nn Carrega o par de registros dd com a constante nn dd ← nn • • • • • • 10

LD IX,nn Carrega o registro IX com a constante nn IX ← nn • • • • • • 14

LD IY,nn Carrega o registro IY com a constante nn IY ← nn • • • • • • 14

LD HL,(nn) Carrega o registro L com o conteúdo da posição de H ← (nn+1) • • • • • • 16

memória nn e carrega o registro H com o conteúdo da

L ← (nn)

posição de memória nn+1

LD dd,(nn) Carrega o registro ddL com o conteúdo da posição de ddH ← (nn+1) • • • • • • 20

memória nn e carrega o registro ddH com o conteúdo da

ddL ← (nn)

posição de memória nn+1

Apostila de propriedade do Prof. Cruz 12

COND. DE FLAGS Nº DE

MNEMÔNICO DESCRIÇÃO OPERAÇÃO

C Z P/V S N H EST.

LD IX,(nn) Carrega IXL com o conteúdo da posição de memória nn e IXH ← (nn+1) • • • • • • 20

carrega IXH com o conteúdo da posição de memória nn+1

IXL ← (nn)

LD IY,(nn) Carrega IYL com o conteúdo da posição de memória nn e IYH ← (nn+1) • • • • • • 20

carrega IYH com o conteúdo da posição de memória nn+1

IYL ← (nn)

LD (nn), HL Carrega o conteúdo da posição de memória nn com o (nn+1) ← H • • • • • • 16

registro L e carrega o conteúdo da posição de memória

(nn) ← L

nn+1 com o registro H

LD (nn), dd Carrega o conteúdo da posição de memória nn+1 com o (nn+1) ← ddH • • • • • • 20

registro ddH e carrega o conteúdo da posição de memória

(nn) ← ddL

nn com o registro ddL.

LD (nn), IX Carrega o conteúdo da posição de memória nn+1 com (nn+1) ← IXH • • • • • • 20

IXH e carrega o conteúdo da posição de memória nn com

(nn) ← IXL

IXL.

LD (nn), IY Carrega o conteúdo da posição de memória nn+1 com (nn+1) ← IYH • • • • • • 20

IYH e carrega o conteúdo da posição de memória nn com

(nn) ← IYL

IYL.

LD SP, HL Carrega o registro SP com o registro HL. SP ← HL • • • • • • 6

LD SP, IX Carrega o registro SP com o registro IX. SP ← IX • • • • • • 10

LD SP, IY Carrega o registro SP com o registro IY. SP ← IY • • • • • • 10

PUSH qq Carrega o conteúdo da posição de memória SP-1 com o (SP-2) ← qqL • • • • • • 11

registro qqH e carrega o conteúdo da posição de memória

(SP-1) ← qqH

SP-2 com o registro qqL.

PUSH IX Carrega o conteúdo da posição de memória SP-1 com (SP-2) ← IXL • • • • • • 15

IXH e carrega o conteúdo da posição de memória SP-2

(SP-1) ← IXH

com IXL.

PUSH IY Carrega o conteúdo da posição de memória SP-1 com (SP-2) ← IYL • • • • • • 15

IYH e carrega o conteúdo da posição de memória SP-2

(SP-1) ← IYH

com IYL.

POP qq Carrega o registro qqL com o conteúdo da posição de qqH ← (SP+1) • • • • • • 10

memória SP e carrega o registro qqH com o conteúdo da

qqL ← (SP)

posição de memória SP+1.

POP IX Carrega IXL com o conteúdo da posição de memória SP e IXH←(SP+1) • • • • • • 14

carrega IXH com o conteúdo da posição de memória

IXL ← (SP)

SP+1.

POP IY Carrega IYL com o conteúdo da posição de memória SP e IYH ← (SP+1) • • • • • • 14

carrega IYH com o conteúdo da posição de memória

IYL ← (SP)

SP+1.

EX DE, HL Troca simultânea dos conteúdos dos pares de registros DE DE ↔ HL • • • • • • 4

e HL.

EX AF, AF Troca simultânea dos conteúdos dos pares de registros AF AF ↔ AF’ • • • • • • 4

e AF’.

EXX Troca simultânea dos conteúdos dos pares de registros: BC ↔ BC’ • • • • • • 4

BC com BC’, DE com DE’ e HL com HL’

DE ↔ DE’

HL ↔ HL’

Apostila de propriedade do Prof. Cruz 13

COND. DE FLAGS Nº DE

MNEMÔNICO DESCRIÇÃO OPERAÇÃO

C Z P/V S N H EST.

EX (SP), HL Troca simultânea do conteúdo da posição de memória SP H ↔ (SP+1) • • • • • • 19

com L e do conteúdo da posição de memória SP+1 com

L ↔ (SP)

H.

EX (SP), IX Troca simultânea do conteúdo da posição de memória SP IXH ↔ (SP+1) • • • • • • 23

com IXL e do conteúdo da posição de memória SP+1 com

IXL ↔ (SP)

IXH.

EX (SP), IY Troca simultânea do conteúdo da posição de memória SP IYH ↔ (SP+1) • • • • • • 23

com IHL e do conteúdo da posição de memória SP+1 com

IYL ↔ (SP)

IYH.

↔

LDI Carrega o conteúdo da posição de memória endereçada (DE) ← (HL) • • • 0 0 16

por DE com o conteúdo da posição endereçada por HL.

DE ← DE + 1

Incrementa DE e HL. Decrementa BC.

HL ← HL + 1

BC ← BC - 1

LDIR Carrega o conteúdo da posição de memória endereçada (DE) ← (HL) • • 0 • 0 0 21

por DE com o conteúdo da posição endereçada por HL.

DE ←DE + 1 16

Incrementa DE e HL. Decrementa BC.

HL ← HL + 1

Repete estas operações até BC = 0000H.

BC ← BC-1

repete até

BC = 0

↔

LDD Carrega o conteúdo da posição de memória endereçada (DE) ← (HL) • • • 0 0 16

por DE com o conteúdo da posição endereçada por HL.

DE ← DE – 1

Decrementa DE, HL e BC.

HL ← HL –1

BC ← BC-1

LDDR Carrega o conteúdo da posição de memória endereçada (DE) ←(HL) • • 0 • 0 0 21

por DE com o conteúdo da posição endereçada por HL.

DE ← DE-1

Decrementa DE, HL e BC.

HL ← HL-1

Repete estas operações até BC = 0000H.

BC ← BC-1

repete até

BC=0

•

↔

↔

↔

↔

CPI Compara o Acumulador com o conteúdo da posição de A : (HL) ↑ 16

memória endereçada pelo par de registros HL. HL ← HL+1

Incrementa HL e decrementa BC.

BC ← BC-1

•

↔

↔

↔

CPIR Compara o Acumulador com o conteúdo da posição de A : (HL) ↑ 21

memória endereçada pelo par de registros HL. HL ← HL+1 16

Incrementa HL e decrementa BC.

BC ← BC-1

Repete estas operações até A = (HL) ou BC = 0000H.

repete até

A = (HL) ou

BC = 0

•

↔

↔

↔

CPD Compara o Acumulador com o conteúdo da posição de A : (HL) ↑ 16

memória endereçada pelo par de registro HL. HL ← HL –1

Decrementa HL e BC.

BC ← BC-1

Apostila de propriedade do Prof. Cruz 14

COND. DE FLAGS Nº DE

MNEMÔNICO DESCRIÇÃO OPERAÇÃO

C Z P/V S N H EST.

•

↔

↔

↔

↔

CPDR Compara o Acumulador com o conteúdo da posição de A : (HL) 1 21

memória endereçada pelo par de registros HL. HL ← HL – 1 16

Decrementa HL e BC.

BC ← BC – 1

Repete estas operações até A = (HL) ou BC = 0000H.

repete até

A = (HL) ou

BC = 0

A←A+r

↔

↔

↔

ADD A, r Soma o Acumulador com o registro r. O resultado é V 0 4

↔

armazenado no Acumulador.

A←A+n

↔

↔

↔

ADD A, n Soma o Acumulador com a constante n. O resultado é V 0 7

↔

armazenado no Acumulador.

A ← A + (HL)

↔

↔

↔

ADD A, (HL) Soma o Acumulador com o conteúdo da posição de V 0 7

↔

memória endereçada pelo par de registros HL. O resultado

é armazenado no Acumulador.

A ← A+(IX+d)

↔

↔

↔

ADD A,(IX+d) Soma o Acumulador com o conteúdo da posição de V 0 19

↔

memória endereçada por IX+d. O resultado é armazenado

no Acumulador.

A ← A+(IY+d)

↔

↔

↔

ADD A,(IY+d) Soma o Acumulador com o conteúdo da posição de 0 19

↔

V

memória endereçada por IY+d. O resultado é armazenado

no Acumulador.

A ← A+s+CY

↔

↔

↔

ADC A,s Soma o Acumulador com um conteúdo de 8 bits e com o 0

↔

V

flag CY. O resultado é armazenado no Acumulador.

A ← A-s ↔

↔

↔

SUB s Subtrai do Acumulador um conteúdo de 8 bits. O

↔

V 1

resultado é armazenado no Acumulador.

A ← A-s-CY

↔

↔

↔

SBC A,s Subtrai do Acumulador um conteúdo de 8 bits e o flag

↔

V 1

CY. O resultado é armazenado no Acumulador.

A←A∧s

↔

↔

AND s Operação “E” entre o Acumulador e um conteúdo de 8 0 P 0 1

bits. O resultado é armazenado no Acumulador.

A←A∨s

↔

OR s Operação “OU” entre o Acumulador e um conteúdo de 8 0 P 0 0

bits. O resultado é armazenado no Acumulador.

A←A⊗s

↔

XOR s Operação “OU EXCLUSIVO” entre o Acumulador e um 0 P 0 0

conteúdo de 8 bits. O resultado é armazenado no

Acumulador.

CP s Compara o Acumulador com um conteúdo de 8 bits. A:s

↔

↔

V 1

Altera os flags. Não altera o Acumulador, nem o conteúdo

de 8 bits.

INC r Soma 1 ao registro r. r←r+1 4

↔

↔

V 0

INC (HL) Soma 1 ao conteúdo da posição de memória endereçada (HL) ← (HL)+1 11

↔

↔

V 0

pelo par de registros HL.

INC (IX+d) Soma 1 ao conteúdo da posição de memória endereçada (IX+d)←(IX+d)+1 23

↔

↔

V 0

por IX + d

INC (IY+d) Soma 1 ao conteúdo da posição de memória endereçada (IY+d)←(IY+d)+1 • 23

↔

V 0

por IY + d

DEC m Subtrai 1 do conteúdo de 8 bits. m←m–1 •

↔

V 0

Apostila de propriedade do Prof. Cruz 15

COND. DE FLAGS Nº DE

MNEMÔNICO DESCRIÇÃO OPERAÇÃO

C Z P/V S N H EST.

ADD HL, ss Soma o par de registros HL com ss. O resultado é HL ← HL + ss • • • 0 X 11

↔

armazenado em HL.

ADC HL, ss Soma o par de registros HL com ss e com o flag CY. O HL←HL+ss+CY V 0 X 15

↔

↔

↔

resultado é armazenado em HL.

SBC HL, ss Subtrai do par de registros HL o valor de ss e do flag CY. HL→HL-ss-CY V 0 X 15

↔

↔

↔

O resultado é armazenado em HL.

ADD IX,pp Soma o registro IX com pp. O resultado é armazenado em IX ← IX+pp • • • 0 X 15

↔

IX.

ADD IY, rr Soma o registro IY com rr. O resultado é armazenado em IY ← IY+rr • • • 0 X 15

↔

IY.

INC ss Soma 1 a ss. ss ← ss + 1 • • • • • • 6

INC IX Soma 1 ao registro IX. IX ← IX + 1 • • • • • • 10

INC IY Soma 1 ao registro IY. IY ← IY + 1 • • • • • • 10

DEC ss Subtrai 1 de ss. ss ← ss – 1 • • • • • • 6

DEC IX Subtrai 1 do registro IX. IX ← IX – 1 • • • • • • 10

DEC IY Subtrai 1 do registro IY. IY ← IY – 1 • • • • • • 10

RLCA Rotação do Acumulador para esquerda sem o flag CY. An+1 ← An • • • 0 0 4

↔

CY ← A7

A0 ← A7

RLA Rotação do Acumulador para esquerda através do flag An+1 ← An • • • 0 0 4

↔

CY.

CY ← A7

A0 ← CY

RRCA Rotação do Acumulador para direita sem o flag CY. An ← An+1 • • • 0 0 4

↔

CY ← A7

A0 ← A7

RRA Rotação do Acumulador para direita através do flag CY. An ← An+1 • • • 0 0 4

↔

CY ← A0

A7 ← CY

RLC r Rotação do registro r para esquerda sem o flag CY. rn+1 ← rn p 0 0 8

↔

↔

CY ← r7

r0 ← r7

RLC (HL) Rotação do conteúdo da posição de memória endereçada (HL)n+1←(HL)n p 0 0 15

↔

↔

pelo par de registro HL sem o flag CY. CY←(HL)7

(HL)0 ← (HL)7

RLC (IX+d) Rotação do conteúdo da posição de memória endereçada (IX+d)n+1←(IX+d)n p 0 0 23

↔

↔

pelo IX+d sem o flag CY CY←(IX+d)7

(IX+d)0 ← (IX+d)7

RLC (IY+d) Rotação do conteúdo da posição de memória endereçada (IY+d)n+1←(IY+d)n p 0 0 23

↔

↔

pelo IY+d sem o flag CY CY←(IY+d)7

(IY+d)0 ← (IY+d)7

RL m Rotação de m para esquerda através do flag CY. mn+1←mn p 0 0

↔

↔

CY← m7

m0 ← CY

Apostila de propriedade do Prof. Cruz 16

COND. DE FLAGS Nº DE

MNEMÔNICO DESCRIÇÃO OPERAÇÃO

C Z P/V S N H EST.

RRC m Rotação de m para direita sem o flag CY mn←mn+1 p 0 0

↔

↔

↔

CY← m0

m7 ← m0

RR m Rotação de m para direita através do flag CY. mn←mn+1

↔

↔

↔

p 0 0

CY← m0

m7 ← CY

SLA m Deslocamento de m para esquerda. mn+1←mn

↔

↔

↔

p 0 0

m0 ← “0”

CY ← m7

SRA m Deslocamento de m para direita. mn←mn+1

↔

↔

↔

p 0 0

m7 ← m7

CY ← m0

SRL m Deslocamento de m para direita. mn←mn+1

↔

↔

↔

p 0 0

m7 ← “0”

CY ← m0

RLD Rotação para esquerda entre o Acumulador e o conteúdo (HL)7-4←(HL)3-0 • P 0 0 18

↔

da posição de memória endereçada pelo par HL A3-0←(HL)7-4

(HL)3-0←A3-0

RRD Rotação para direita entre o Acumulador e o conteúdo da (HL)7-4←A3-0 • P 0 0 18

↔

posição de memória endereçada pelo par HL. (HL)3-0←(HL)7-4

A3-0←(HL)3-0

DAA Ajusta o valor do Acumulador para decimal A10 ← Abin P • 4

↔

↔

↔

CPL Complemento de 1 do Acumulador A←A • • • • 1 1

4

NEG Complemento de 2 do Acumulador A ← A+1 8

↔

↔

↔

V 1

CCF Complementa o flag CY CY ← CY • • • 4

↔

0 X

SCF Seta o flag CY CY ← “1” • • • 4

↔

0 0

NOP Sem operação. - • • • • • • 4

HALT Parada do Z-80 Fim • • • • • • 4

DI Desabilita interrupções. IFF ← “0” • • • • • • 4

EI Habilita interrupções. IFF ← “1” • • • • • • 4

IM 0 Seta interrupção Modo 0 I ← M0 • • • • • • 8

IM 1 Seta interrupção Modo 1 I ← M1 • • • • • • 8

IM 2 Seta interrupção Modo 2 I ← M2 • • • • • • 8

BIT b, r Verifica bit b do registro r. Resultado fica no flag Z. Z ← rb • X X 8

↔

0 1

BIT b, (HL) Verifica bit b do conteúdo da posição de memória Z ← (HL)b • X X 12

↔

0 1

endereçada pelo par de registros HL. Resultado fica no

flag Z

BIT b, (IX+d) Verifica bit b do conteúdo da posição de memória Z ← (IX+d) • X X 20

↔

0 1

endereçada por IX+d. Resultado fica no flag Z

BIT b, (IY+d) Verifica bit b do conteúdo da posição de memória Z ← (IY+d) • X X 20

↔

0 1

endereçada por IY+d. Resultado fica no flag Z

Apostila de propriedade do Prof. Cruz 17

COND. DE FLAGS Nº DE

MNEMÔNICO DESCRIÇÃO OPERAÇÃO

C Z P/V S N H EST.

SET b, r Seta o bit b do registro r rb ← 1 • • • • • • 8

SET b, (HL) Seta o bit b do conteúdo da posição de memória (HL)b ←1 • • • • • • 15

endereçada pelo registro HL

SET b, (IX+d) Seta o bit b do conteúdo da posição de memória (IX+d)b ← 1 • • • • • • 23

endereçada pelo registro IX+d

SET b, (IY+d) Seta o bit b do conteúdo da posição de memória (IY+d)b ← 1 • • • • • • 23

endereçada pelo registro IY+d

RES b, m Resseta o bit do conteúdo m (m)b ← 0 • • • • • •

JP nn Desvia incondicionalmente para a posição de memória nn PC ← nn • • • • • • 10

JP cc, nn Desvia para a posição de memória nn se a condição cc for se cc = verd. • • • • • • 10

verdadeira, caso contrário vai para a posição de memória PC ← nn

seguinte

JR e Desvia incondicionalmente para a posição de memória PC ← PC+e • • • • • • 12

atual +e

JR C, e Desvia para a posição de memória atual +e, se o flag CY se CY = 1 • • • • • • 7

=1 PC ← PC + e 12

JR NC, e Desvia para a posição de memória atual +e, se o flag CY se CY = 0 • • • • • • 7

=0 PC ← PC+e 12

JR Z, e Desvia para a posição de memória atual +e, se o flag Z = se Z = 1 • • • • • • 7

1 PC ← PC+e 12

JR NZ, e Desvia para a posição de memória atual +e, se o flag Z = se Z = 0 • • • • • • 7

0 PC ← PC +e 12

JP (HL) Desvia incondicionalmente para a posição de memória PC ← HL • • • • • • 4

endereçada pelo par de registros HL

JP (IX) Desvia incondicionalmente para a posição de memória PC ← IX • • • • • • 8

endereçada pelo par de registros IX

JP (IY) Desvia incondicionalmente para a posição de memória PC ← IY • • • • • • 8

endereçada pelo par de registros IY

DJNZ e Decrementa o registro B. Se B ≠ 0, desvia para a posição B ← B-1 • • • • • • 8

de memória atual +e. Caso B = 0, vai para a posição de se B ≠0, PC←PC+e 13

memória seguinte se B =0, PC←PC+2

CALL nn Chama subrotina que começa na posição de memória nn. (SP-1) ← PCH • • • • • • 17

Guarda endereço de retorno na pilha (SP-2) ← PCL

PC ← nn

CALL cc, nn Chama subrotina que começa na posição de memória nn, Se cc=Verd. • • • • • • 10

se condição cc for verdadeira. Guarda endereço de retorno (SP-1) ←PCH 17

na pilha (SP-2) ← PCL

PC ← nn

RET Retorno incondicional de subrotina PCL ← (SP) • • • • • • 10

PCH ← (SP+1)

RET cc Retorno condicional de subrotina, se condição cc for se cc = Verd. • • • • • • 5

verdadeira, retorna ao programa principal PCL ← (SP) 11

PCH ← (SP+1)

RETI Retorno de subrotina de tratamento de interrupção PCL ← (SP) • • • • • • 14

mascarável PCH ← (SP+1)

RETN Retorno de subrotina de tratamento de interrupção não PCL ← (SP) • • • • • • 14

mascarável PCH ← (SP+1)

RST p Desvia para subrotina de endereço fixo. Guarda endereço (SP-1) ←PCH • • • • • • 11

de retorno na pilha (SP-2) ←PCL

PCH ← 00H

PCL ← p

IN A, (n) Carrega no Acumulador o conteúdo do dispositivo de A ← (n) • • • • • • 11

entrada de endereço n

Apostila de propriedade do Prof. Cruz 18

COND. DE FLAGS Nº DE

MNEMÔNICO DESCRIÇÃO OPERAÇÃO

C Z P/V S N H EST.

IN r, (C) Carrega no registro r o conteúdo do dispositivo de entrada r ← (C) • P 12

↔

0 0

cujo endereço é fornecido pelo registro C

INI Carrega o conteúdo da posição de memória endereçada (HL) ← (C) • X X 16

↔

1 X

pelo par de registros HL com o conteúdo do dispositivo B ← B-1

de entrada cujo endereço é fornecido pelo registro C. HL ← HL+1

Decrementa o registro B. Incrementa o par de registros

HL

INIR Carrega o conteúdo da posição de memória endereçada (HL) ← (C) • 1 X X 1 X

21

pelo par de registros HL com o conteúdo do dispositivo B ← B-1 16

de entrada cujo endereço é fornecido pelo registro C. HL ← HL+1

Decrementa o registro B. Incrementa o par de registros repete até B=00H

HL. Repete até B = 00H

IND Carrega o conteúdo da posição de memória endereçada (HL) ← (C) • X X 16

↔

1 X

pelo par de registros HL com o conteúdo do dispositivo B ← B-1

de entrada cujo endereço é fornecido pelo registro C. HL ← HL-1

Decrementa o registro B. Decrementa o par de registros

HL

INDR Carrega o conteúdo da posição de memória endereçada (HL) ← (C) • 1 X X 1 X

21

pelo par de registros HL com o conteúdo do dispositivo B ← B-1 16

de entrada cujo endereço é fornecido pelo registro C. HL ← HL-1

Decrementa o registro B. Incrementa o par de registros repete até B=00H

HL. Repete até B = 00H

OUT (n), A Carrega no dispositivo de saída de endereço n o conteúdo (N) ← A • • • • • • 11

do Acumulador

OUT (C), r Carrega no dispositivo de saída cujo endereço é fornecido (C) ← r • • • • • • 12

pelo registro C o conteúdo do registro r

OUTI Carrega no dispositivo de saída cujo endereço é fornecido (C) ← (HL) • X X 16

↔

1 X

pelo registro C o conteúdo da posição de memória B ← B-1

endereçada pelo par de registros HL. Decrementa o HL ← HL +1

registro B. Incrementa o par de registros HL

OTIR Carrega no dispositivo de saída cujo endereço é fornecido (C) ← (HL) • 1 X X 1 X

21

pelo registro C o conteúdo da posição de memória B ← B-1 16

endereçada pelo par de registros HL. Decrementa o HL ← HL +1

registro B. Incrementa o par de registros HL. Repete até B repete até B=00H

= 00H

OUTD Carrega no dispositivo de saída cujo endereço é fornecido (C) ← (HL) • X X 16

↔

1 X

pelo registro C o conteúdo da posição de memória B ← B-1

endereçada pelo par de registros HL. Decrementa o HL ← HL -1

registro B. Decrementa o par de registros HL

OTDR Carrega no dispositivo de saída cujo endereço é fornecido (C) ← (HL) • 1 X X 1 X

21

pelo registro C o conteúdo da posição de memória B ← B-1 16

endereçada pelo par de registros HL. Decrementa o HL ← HL –1

registro B. Decrementa o par de registros HL. Repete até Repete até

B = 00H B=00H

Apostila de propriedade do Prof. Cruz 19

8E ADC A, (HL) CB49 BIT 1, C CB7D BIT 7,L ED68 IN L, (C)

DD8E_ ADC A, (IX+d) CB4A BIT 1,D DC_ _ CALL C,nn 34 INC (HL)

FD8E_ ADC A, (IY+d) CB4B BIT 1,E FC_ _ CALL M,nn DD34_ INC (IX+d)

8F ADC A,A CB4C BIT 1,H D4_ _ CALL NC,nn FD34_ INC (IY+d)

88 ADC A,B CB4D BIT 1,L CD_ _ CALL nn 3C INC A

89 ADC A,C CB56 BIT 2, (HL) C4_ _ CALL NZ,nn 04 INC B

8A ADC A,D DDCB_56 BIT 2, (IX+d) F4_ _ CALL P,nn 03 INC BC

8B ADC A,E FDCB_56 BIT 2, (IY+d) EC_ _ CALL PE,nn 0C INC C

8C ADC A,H CB57 BIT 2,A E4_ _ CALL P0,nn 14 INC D

8D ADC A,L CB50 BIT 2,B CC_ _ CALL Z,nn 13 INC DE

CE_ ADC A,n CB51 BIT 2,C 3F CCF 1C INC E

ED4A ADC HL, BC CB52 BIT 2,D BE CP (HL) 24 INC H

ED5A ADC HL, DE CB53 BIT 2,E DDBE_ CP (IX+d) 23 INC HL

ED6A ADC HL,HL CB54 BIT 2,H FDBE_ CP (IY+d) DD23 INC IX

ED7A ADC HL, SP CB55 BIT 2,L BF CP A FD23 INC IY

86 ADD A, (HL) CB5E BIT 3, (HL) B8 CP B 2C INC L

DD86_ ADD A, (IX+d) DDCB_5E BIT 3, (IX+d) B9 CP C 33 INC SP

FD86_ ADD A, (IY+d) FDCB_5E BIT 3, (IY+d) BA CP D EDAA IND

87 ADD A,A CB5F BIT 3,A BB CP E EDBA INDR

80 ADD A,B CB58 BIT 3,B BC CP H EDA2 INI

81 ADD A,C CB59 BIT 3,C BD CP L EDB2 INIR

82 ADD A,D CB5A BIT 3,D FE_ CP n E9 JP (HL)

83 ADD A,E CB5B BIT 3,E EDA9 CPD DDE9 JP (IX)

84 ADD A,H CB5C BIT 3,H ED89 CPDR FDE9 JP (IY)

85 ADD A,L CB5D BIT 3,L EDA1 CPI DA_ _ JP C, nn

C6_ ADD A,n CB66 BIT 4, (HL) EDB1 CPIR FA_ _ JP M, nn

09 ADD HL, BC DDCB_66 BIT 4, (IX+d) 2F CPL D2_ _ JP NC, nn

19 ADD HL, DE FDCB_66 BIT 4, (IY+d) 27 DAA C3_ _ JP nn

29 ADD HL, HL CB67 BIT 4,A 35 DEC (HL) C2_ _ JP NZ, nn

39 ADD HL, SP CB60 BIT 4,B DD35_ DEC (IX+d) F2_ _ JP P, nn

DD09 ADD IX, BC CB61 BIT 4,C FD35_ DEC (IY+d) EA_ _ JP PE,nn

DD19 ADD IX, DE CB62 BIT 4,D 3D DEC A E2_ _ JP P0, nn

DD29 ADD IX, IX CB63 BIT 4,E 05 DEC B CA_ _ JP Z, nn

DD39 ADD IX, SP CB64 BIT 4,H 0B DEC BC 38_ JR C, e

FD09 ADD IY, BC CB65 BIT 4,L 0D DEC C 18_ JR e

FD19 ADD IY, DE CB6E BIT 5, (HL) 15 DEC D 30_ JR NC, e

FD29 ADD IY, IY DDCB_6E BIT 5, (IX+d) 1B DEC DE 20_ JR NZ, e

FD39 ADD IY, SP FDCB_6E BIT 5, (IY+d) 1D DEC E 28_ JR Z, e

A6 AND (HL) CB6F BIT 5,A 25 DEC H 02 LD (BC), A

DDA6_ AND (IX+d) CB68 BIT 5,B 2B DEC HL 12 LD (DE), A

FDA6_ AND (IY+d) CB69 BIT 5,C DD2B DEC IX 77 LD (HL), A

A7 AND A CB6A BIT 5,D FD2B DEC IY 70 LD (HL), B

A0 AND B CB6B BIT 5,E 2D DEC L 71 LD (HL), C

A1 AND C CB6C BIT 5,H 3B DEC SP 72 LD (HL), D

A2 AND D CB6D BIT 5,L F3 DI 73 LD (HL), E

A3 AND E CB76 BIT 6, (HL) 10_ DJNZ e 74 LD (HL), H

A4 AND H DDCB_76 BIT 6, (IX+d) FB EI 75 LD (HL), L

A5 AND L FDCB_76 BIT 6, (IY+d) E3 EX (SP), HL 36_ LD (HL), n

E6_ AND n CB77 BIT 6,A DDE3 EX (SP), IX DD77_ LD (IX+d), A

CB46 BIT 0,(HL) CB70 BIT 6,B FDE3 EX (SP), IY DD70_ LD (IX+d), B

DDCB_46 BIT 0,(IX+d) CB71 BIT 6,C 08 EX AF, AF’ DD71_ LD (IX+d), C

FDCB_46 BIT 0, (IY+d) CB72 BIT 6,D EB EX DE, HL DD72_ LD (IX+d), D

CB47 BIT 0,A CB73 BIT 6,E D9 EXX DD73_ LD (IX+d), E

CB40 BIT 0,B CB74 BIT 6,H 76 HALT DD74_ LD (IX+d), H

CB41 BIT 0,C CB75 BIT 6,L ED46 IM 0 DD75_ LD (IX+d), L

CB42 BIT 0,D CB7E BIT 7, (HL) ED56 IM 1 DD36_ LD (IX+d), n

CB43 BIT 0,E DDCB_7E BIT 7, (IX+d) ED5E IM 2 FD77_ LD (IY+d), A

CB44 BIT 0,H FDCB_7E BIT 7, (IY+d) ED78 IN A, (C) FD70_ LD (IY+d), B

CB45 BIT 0,L CB7F BIT 7,A DB_ IN A, (n) FD71_ LD (IY+d), C

CB4E BIT 1,(HL) CB78 BIT 7,B ED40 IN B, (C) FD72_ LD (IY+d), D

DDCB_4E BIT 1,(IX+d) CB79 BIT 7,C ED48 IN C, (C) FD73_ LD (IY+d), E

FDCB_4E BIT 1,(IY+d) CB7A BIT 7,D ED50 IN D, (C) FD74_ LD (IY+d), H

CB4F BIT 1,A CB7B BIT 7,E ED58 IN E, (C) FD75_ LD (IY+d), L

CB48 BIT 1,B CB7C BIT 7,H ED60 IN H, (C)

Apostila de propriedade do Prof. Cruz 20

FD36_ _ LD (IY+d),n 1E_ LD E,n F5 PUSH AF CBB0 RES 6,B

32_ _ LD (nn), A 66 LD H, (HL) C5 PUSH BC CBB1 RES 6,C

ED43_ _ LD (nn), BC DD66_ LD H, (IX+d) D5 PUSH DE CBB2 RES 6,D

ED53_ _ LD (nn), DE FD66_ LD H, (IY+d) E5 PUSH HL CBB3 RES 6,E

22_ _ LD (nn), HL 67 LD H,A DDE5 PUSH IX CBB4 RES 6,H

DD22_ _ LD (nn), IX 60 LD H,B FDE5 PUSH IY CBB5 RES 6,L

FD22_ _ LD (nn), IY 61 LD H,C CB86 RES 0, (HL) CBBE RES 7, (HL)

ED73_ _ LD (nn), SP 62 LD H,D D0CB_86 RES 0, (IX+d) DDCB_BE RES 7, (IX+d)

0A LD A, (BC) 63 LD H,E FDCB_86 RES 0, (IY+d) FDCB_BE RES 7, (IY+d)

1A LD A, (DE) 64 LD H,H CB87 RES 0,A CBBF RES 7,A

7E LD A, (HL) 65 LD H,L CB80 RES 0,B CBB8 RES 7,B

DD7E_ LD A, (IX+d) 26_ LD H,n CB81 RES 0,C CBB9 RES 7,C

FD7E_ LD A, (IY+d) 2A_ _ LD HL, (nn) CB82 RES 0,D CBBA RES 7,D

3A_ _ LD A, (nn) 21_ _ LD HL, nn CB83 RES 0,E CBBB RES 7,E

7F LD A,A ED47 LD I,A CB84 RES 0,H CBBC RES 7,H

78 LD, A,B DD2A_ _ LD IX, (nn) CB85 RES O,L CBBD RES 7,L

79 LD A,C DD21_ _ LD IX, nn CB8E RES 1, (HL) C9 RET

7A LD A,D FD2A_ _ LD IY, (nn) DDCB_8E RES 1, (IX+d) D8 RET C

7B LD A,E FD21_ _ LD IY, nn FDCB_8E RES 1, (IY+d) F8 RET M

7C LD A,H 6E LD L, (HL) CB8F RES 1,A D0 RET NC

ED57 LD A,I DD6E_ LD L, (IX+d) CB88 RES 1,B C0 RET NZ

7D LD A,L FD6E_ LD L, (IY+d) CB89 RES 1,C F0 RET P

3E_ LD A,n 6F LD L,A CB8A RES 1,D E8 RET PE

46 LD B, (HL) 66 LD L,B CB8B RES 1,E E0 RET PO

DD46_ LD B, (IX+d) 67 LD L,C CB8C RES 1,H C8 RET Z

FD46_ LD B, (IY+d) 6A LD L,D CB8D RES 1,L ED4D RETI

47 LD B,A 6B LD L,E CB96 RES 2, (HL) ED45 RETN

40 LD B,B 6C LD L,H D0CB_96 RES 2, (IX+d) CB16 RL (HL)

41 LD B,C 6D LD L,L FDCB_96 RES 2, (IY+d) DDCB_16 RL (IX+d)

42 LD B,D 2E_ LD L,n CB97 RES 2,A FDCB_16 RL (IY+d)

43 LD B,E ED78_ _ LD SP, (nn) CB90 RES 2,B CB17 RL A

44 LD B,H F9 LD SP, HL CB91 RES 2,C CB10 RL B

45 LD B,L DDF9 LD SP, IX CB92 RES 2,D CB11 RL C

06_ LD B,n FDF9 LD SP, IY CB93 RES 2,E CB12 RL D

ED48_ _ LD BC, (nn) 31_ _ LD SP, nn CB94 RES 2,H CB13 RL E

01_ _ LD BC, nn EDA8 LDD CB95 RES 2,L CB14 RL H

4E LD C, (HL) ED88 LDDR CB9E RES 3, (HL) CB15 RL L

DD4E_ LD C, (IX+d) EDA0 LDI DDCB_9E RES 3, (IX+d) 17 RLA

FD4E_ LD C, (IY+d) EDB0 LDIR FDCB_9E RES 3, (IY+d) CB06 RLC (HL)

4F LD C,A ED44 NEG CB9F RES 3,A DDCB_06 RLC (IX+d)

48 LD C,B 00 NOP CB98 RES 3,B FDCB_06 RLC (IY+d)

49 LD C,C B6 OR (HL) CB99 RES 3,C CB07 RLC A

4A LD C,D DDB6_ OR (IX+d) CB9A RES 3,D CB00 RLC B

4B LD C,E FDB6_ OR (IY+d) CB9B RES 3,E CB01 RLC C

4C LD C,H B7 OR A CB9C RES 3,H CB02 RLC D

4D LD C,L B0 OR B CB9D RES 3,L CB03 RLC E

0E_ LD C,n B1 OR C CBA6 RES 4, (HL) CB04 RLC H

56 LD D, (HL) B2 OR D DDCB_AB RES 4, (IX+d) CB05 RLC L

DD56_ LD D, (IX+d) B3 OR E FDCB_AB RES 4, (IY+d) 07 RLCA

FD56_ LD D, (IY+d) B4 OR H CBA7 RES 4,A ED6F RLD

57 LD D,A B5 OR L CBA0 RES 4,B CB1E RR (HL)

50 LD D,B F6_ OR n CBA1 RES 4,C DDCB_1E RR (IX+d)

51 LD D,C EDBB OTDR CBA2 RES 4,D FDCB_1E RR (IY+d)

52 LD D,D EDB3 OTIR CBA3 RES 4,E CB1F RR A

53 LD D,E ED79 OUT (C), A CBA4 RES 4,H CB18 RR B

54 LD D,H ED41 OUT (C), B CBA5 RES 4,L CB19 RR C

55 LD D,L ED49 OUT (C), C CBAE RES 5, (HL) CB1A RR D

10_ LD D,n ED51 OUT (C), D DDCB_AE RES 5, (IX+d) CB1B RR E

ED58_ _ LD DE, (nn) ED59 OUT (C), E FDCB_AE RES 5, (IY+d) CB1C RR H

11_ _ LD DE, nn ED61 OUT (C), H CBAF RES 5,A CB1D RR L

5E LD E, (HL) ED69 OUT (C), L CBA8 RES 5,B 1F RRA

DD5E_ LD E, (IX+d) D3_ OUT (n), A CBA9 RES 5,C CB0E RRC (HL)

FD5E_ LD E, (IY+d) EDAB OUTD CBAA RES 5,D DDCB_0E RRC (IY+d)

5F LD E,A EDA3 OUTI CBAB RES 5,E FDCB_0E RRC (IY+d)

58 LD E,B F1 POP AF CBAC RES 5,H CB0F RRC A

59 LD E,C C1 POP BC CBAD RES 5,L CB08 RRC B

5A LD E,D D1 POP DE CBB6 RES 6, (HL) CB09 RRC C

5B LD E,E E1 POP HL DDCB_B6 RES 6, (IX+d) CB0A RRC D

5C LD E,H DDE1 POP IX FDCB_B6 RES 6, (IY+d) CB0B RRC E

5D LD E,L FDE1 POP IY CBB7 RES 6,A CB0C RRC H

Apostila de propriedade do Prof. Cruz 21

CB0D RRC L CBCC SET 1,H CBF7 SET 6,A CB3C SRL H

0F RRCA CBCD SET 1,L CBF0 SET 6,B CB3D SRL L

ED67 RRD CBD6 SET 2, (HL) CBF1 SET 6,C 96 SUB (HL)

C7 RST 0 DDCB_06 SET 2, (IX+d) CBF2 SET 6,D DD96_ SUB (IX+d)

D7 RST 10H FDCB_D6 SET 2, (IY+d) CBF3 SET 6,E FD96_ SUB (IY+d)

DF RST 18H CBD7 SET 2,A CBF4 SET 6,H 97 SUB A

E7 RST 20H CBD0 SET 2,B CBF5 SET 6,L 90 SUB B

EF RST 28H CBD1 SET 2,C CBFE SET 7, (HL) 91 SUB C

F7 RST 30H CBD2 SET 2,D DDCB_FE SET 7, (IX+d) 92 SUB D

FF RST 38H CBD3 SET 2,E FDCB_FE SET 7, (IY+d) 93 SUB E

CF RST 8 CBD4 SET 2,H CBFF SET 7,A 94 SUB H

9E SBC A, (HL) CBD5 SET 2,L CBF8 SET 7,B 95 SUB L

DD9E_ SBC A, (IX+d) CBD8 SET 3,B CBF9 SET 7,C D6_ SUB n

FD9E_ SBC A, (IY+d) CBDE SET 3, (HL) CBFA SET 7,D AE XOR (HL)

9F SBC A,A DDCB_DE SET 3, (IX+d) CBFB SET 7,E DDAE_ XOR (IX+d)

98 SBC A,B FDCB_DE SET 3, (IY+d) CBFC SET 7,H FDAE_ XOR (IY+d)

99 SBC A,C CBDF SET 3,A CBFD SET 7,L AF XOR A

9A SBC A,D CBD9 SET 3,C CB26 SLA (HL) A8 XOR B

9B SBC A,E CBDA SET 3,D DDCB_26 SLA (IX+d) A9 XOR C

9C SBC A,H CBDB SET 3,E FDCB_26 SLA (IY+d) AA XOR D

9D SBC A,L CBDC SET 3,H CB27 SLA A AB XOR E

DE_ SBC A,n CBDD SET 3,L CB20 SLA B AC XOR H

ED42 SBC HL, BC CBE6 SET 4, (HL) CB21 SLA C AD XOR L

ED52 SBC HL, DE DDCB_E6 SET 4, (IX+d) CB22 SLA D EE_ XOR n

ED62 SBC HL, HL FDCB_E6 SET 4, (IY+d) CB23 SLA E

ED72 SBC HL, SP CBE7 SET 4,A CB24 SLA H

37 SCF CBE0 SET 4,B CB25 SLA L

CBC6 SET 0, (HL) CBE1 SET 4,C CB2E SRA (HL)

DDCB_C6 SET 0, (IX+d) CBE2 SET 4,D DDCB_2E SRA (IX+d)

FDCB_C6 SET 0, (IY+d) CBE3 SET 4,E FDCB_2E SRA (IY+d)

CBC7 SET 0,A CBE4 SET 4,H CB2F SRA A

CBC0 SET 0,B CBE5 SET 4,L CB28 SRA B

CBC1 SET 0,C CBEE SET 5, (HL) CB29 SRA C

CBC2 SET 0,D DDCB_EE SET 5, (IX+d) CB2A SRA D

CBC3 SET 0,E FDCB_EE SET 5, (IY+d) CB2B SRA E

CBC4 SET 0,H CBEF SET 5,A CB2C SRA H

CBC5 SET 0,L CBE8 SET 5,B CB2D SRA L

CBCE SET 1, (HL) CBE9 SET 5,C CB3E SRL (HL)

DDCB_CE SET 1, (IX+d) CBEA SET 5,D DDCB_3E SRL (IX+d)

FDCB_CE SET 1, (IY+d) CBEB SET 5,E FDCB_3E SRL (IY+d)

CBCF SET 1,A CBEC SET 5,H CB3F SRL A

CBC8 SET 1,B CBED SET 5,L CB38 SRL B

CBC9 SET 1,C CBF6 SET 6, (HL) CB39 SRL C

CBCA SET 1,D DDCB_F6 SET 6, (IX+d) CB3A SRL D

CBCB SET 1,E FDCB_F6 SET 6, (IY+d) CB3B SRL E

Apostila de propriedade do Prof. Cruz 22

3 - EXEMPLOS DE PROGRAMAÇÃO

1. Colocar 20H na posição de memória 1A00H.

2. Colocar o conteúdo da posição de memória 1950H nos registros B e D.

3. Colocar 00H na posição de memória 1E00H e 01H na posição de

memória 1E01H.

4. Colocar 19H nas posições de memória 1900H, 1901H, 1902H e 1903H.

5. Colocar o conteúdo da posição de memória 1B00H no registro E e o

conteúdo da posição de memória 1B01H no registro D.

6. Colocar 30H na posição de memória 1900H, 31H em 1901H, 32H em

1902H, 33H em 1903H, 34H em 1904H e 35H em 1905H.

7. Incrementar o conteúdo da posição de memória 1960H e decrementar o

conteúdo da posição de memória 1961H.

8. Somar o conteúdo da posição de memória 1C00H com o registro B e

guardar o resultado no registro C.

9. Somar o registro H com o registro L e guardar o resultado em 19A0H.

10. Somar o conteúdo da posição de memória 1905H com o conteúdo da

posição de memória 1906H e guardar o resultado em 1904H.

11. Somar 32H com o conteúdo da posição de memória 1930H e guardar o

resultado em 1950H.

12. Subtrair 05H do conteúdo da posição de memória 1900H e guardar o

resultado em 1905H.

13. Fazer a subtração de H com L (H-L) e guardar H em 1900H, L em 1901H

e o resultado em 1902H.

14. Decrementar o registro B e incrementar duas vezes o registro C, repetir

até o registro B assumir o valor 00H.

15. Deixar o acumulador igual a 00H.

16. Verificar o valor do bit B4 do conteúdo da posição de memória 1900H.

Se B4 = “0” colocar 00H em 1901H.

Se B4 = “1” colocar FFH em 1901H.

17. Deixar os bits B6 e B1 iguais a “1” e não modificar o valor dos outros bits

do conteúdo da posição de memória 1950H.

Apostila de propriedade do Prof. Cruz 23

18. Deixar os bits B4 e B0 iguais a “0” e não modificar o valor dos outros bits

do conteúdo da posição de memória 1920H.

19. Determinar quantos bits tem valor “1” no conteúdo da posição de

memória 1910H.

Colocar o resultado em 1911H.

20. Inverter o valor dos bits B0 a B3 do registro L e não alterar o valor dos

demais bits (B4 a B7).

Apostila de propriedade do Prof. Cruz 24

4 - LISTA DE EXERCÍCIOS DO Z-80

Para os exercícios a seguir fazer o fluxograma, linguagem assembly para o

Z-80 e linguagem de máquina.

Considerar que o programa começará na posição 1800H.

1. Colocar 00H na posição de memória 1900H.

2. Somar os conteúdos das posições 1900H e 1901H e colocar o

resultado em 1902H.

3. Colocar o maior dos conteúdos das posições 1900H e 1901H em 1902H.

4. Transferir uma tabela de 20 elementos que começa no endereço 1900H

para 1950H.

5. Testar o bit 4 (B3) do conteúdo da posição 1900H. Colocar 00H em

1901H se B3=0 ou 01H se B3=1

6. Colocar os 4 bits menos significativos da posição de memória 1900H nos

4 bits menos significativos da posição de memória 1901H. Limpar os

4 bits mais significativos de 1901H.

7. Somar o número de 16 bits localizado nas posições 1900H e 1901H

com o número de 16 bits localizado nas posições 1902H e 1903H.

Armazenar o resultado nas posições 1904H, 1905H e 1906H.

8. Determinar o maior elemento de uma tabela. O comprimento da

tabela está na posição 1900H e a tabela começa no endereço

1901H. Colocar o maior elemento logo após o último elemento da tabela.

9. Deslocar para esquerda o conteúdo da posição de memória 1900H até

que o bit mais significativo fique "1". Armazenar o número de

deslocamento para esquerda na posição 1901H. Se o conteúdo da

posição de memória 1900H é 00H, colocar 00H em 1901H.

10. Determinar o comprimento de um STRING de caracteres ASCII (caracter

ASCII com 7 bits e o 8º bit igual a "0"). O STRING começa no endereço

1900H e o fim é marcado pelo caracter CR (CARRIAGE RETURN).

Colocar o comprimento do STRING na posição 1A00H.

11. Calcular o CHECKSUM de uma memória EPROM 2716 que está

alocada a partir do endereço 2000H. Colocar o resultado na posição

1900H. O CHECKSUM pode ser feito pela SOMA ou OU-EXCLUSIVO

de todos os bytes de memória.

Apostila de propriedade do Prof. Cruz 25

12. Determinar o comprimento de uma mensagem ASCII. A mensagem

começa com um caracter STX e termina com ETX. Pesquisar a

mensagem a partir do endereço 1900H, colocar o endereço inicial da

mensagem em 1A00H e 1A01H, o endereço final em 1A02H e 1A03H e o

comprimento em 1A04H.

13. Dada uma tabela que começa em 1900H e tem 10 elementos.

Determinar quantos bits "1" existem nesta tabela. Guardar o resultado

em 1A00H.

14. Dada uma tabela com 20 elementos e com inicio em 1900H, pede-se:

- deixar os bits 0 e 4 de todos os elementos com valor "1";

- deixar os bits 6 e 7 dos elementos pares com valor "0".

15. Dada uma tabela com 10 elementos e com início em 1900H, pede-se:

- Determinar quantos elementos tem bits "0" e "3" igual a "zero" e bits

"1" e "5" iguais a "1".

Colocar o resultado em 1950H.

16. Fazer uma subrotina para determinar qual caracter da base hexadecimal

é maior:

- os 2 caracteres estão no acumulador

A7 A6 A5 A4 A3 A2 A1 A0

Y3 Y2 Y1 Y0 X3 X2 X1 X0

Y X

- se Y>X → fazer flag CY = "1" e retornar

- se Y<=X → fazer flag CY = "0" e retornar

17. Fazer um programa para executar o seguinte:

- determinar numa tabela quantos elementos são maiores que 64H e

guardar o resultado em 1A00H.

- guardar os endereços das posições que contém os elementos

maiores que 64H, a partir da posição 1B00H.

Considerar:

- a tabela começa em 1900H.

- a tabela tem 10 elementos

Apostila de propriedade do Prof. Cruz 26

18. Preencher uma tabela que começa em 1900H e tem (50)10 elementos

com elementos com valor 00H.

19. Preencher a memória do endereço 1900H até 19FFH com 00H, 01H,

02H, 03H,....., FFH.

20. Complementar o conteúdo da posição de memória 1950H e colocar o

resultado em 1951H.

Apostila de propriedade do Prof. Cruz 27

S-ar putea să vă placă și

- Z80 Eleição TurmaDocument16 paginiZ80 Eleição TurmaElias Eugenio Machava100% (2)

- Roteiro Aula Prática - Sensores em ArduinoDocument15 paginiRoteiro Aula Prática - Sensores em ArduinoDyogo Mondego MoraesÎncă nu există evaluări

- Z80 Chip e InstruçõesDocument108 paginiZ80 Chip e InstruçõesWallace Teixeira100% (1)

- Amplificador Operacional Exercícios ListaDocument7 paginiAmplificador Operacional Exercícios ListaGustavo TelesÎncă nu există evaluări

- Manual Software MMDB 01Document88 paginiManual Software MMDB 01ricardo_eletronicaÎncă nu există evaluări

- Relatorio RelogioDocument15 paginiRelatorio RelogioMario Gato Jr.Încă nu există evaluări

- ATmega328 40cDocument6 paginiATmega328 40ccelsovillelaÎncă nu există evaluări

- MF 47Document43 paginiMF 47Symon4949100% (1)

- Pic MicrocontroladorDocument112 paginiPic MicrocontroladorFernando SimõesÎncă nu există evaluări

- SPI-Flash Programmer ManualDocument4 paginiSPI-Flash Programmer ManualAlbert NewtonÎncă nu există evaluări

- Microprocessadores e microcontroladores: introduçãoDocument51 paginiMicroprocessadores e microcontroladores: introduçãopatriciarsilva17Încă nu există evaluări

- Manual Ace UsbDocument25 paginiManual Ace UsbRachel RowlandÎncă nu există evaluări

- Somador Completo e Meio SomadorDocument24 paginiSomador Completo e Meio SomadorKarinesaÎncă nu există evaluări

- FPGA: Aplicações em processamento digital de sinaisDocument23 paginiFPGA: Aplicações em processamento digital de sinaisBianca SantanaÎncă nu există evaluări

- Programação para ArduinoDocument19 paginiProgramação para ArduinoJorge BrandãoÎncă nu există evaluări

- Incb 019Document74 paginiIncb 019Gunter KieferÎncă nu există evaluări

- Microcontrolador PIC16F628A tutorialDocument43 paginiMicrocontrolador PIC16F628A tutorialJoão Paulo Lopes100% (1)

- CEFET-SC Apresenta Fontes Lineares e ChaveadasDocument18 paginiCEFET-SC Apresenta Fontes Lineares e ChaveadasnoahkrpgÎncă nu există evaluări

- Zanco - Microcontroladores Pic18Document7 paginiZanco - Microcontroladores Pic18jefersilvaÎncă nu există evaluări

- PIC16 F 628 ADocument0 paginiPIC16 F 628 ADaniel TaveiraÎncă nu există evaluări

- Engenharia da Computação e seus ComponentesDocument57 paginiEngenharia da Computação e seus ComponentesBeca AdamuzÎncă nu există evaluări

- Curso Eletrônica - SCR Parte IDocument4 paginiCurso Eletrônica - SCR Parte IFadir SalmenÎncă nu există evaluări

- Mecatrônica FácilDocument37 paginiMecatrônica FácilDiego CorteloÎncă nu există evaluări

- Conversor A/D com PIC - Termômetro e multímetro digitaisDocument8 paginiConversor A/D com PIC - Termômetro e multímetro digitaisalexandresjr7Încă nu există evaluări

- Circuitos CombinatóriosDocument2 paginiCircuitos CombinatóriosRicardoo OliveiraÎncă nu există evaluări

- Apostila Análise de Circuitos ElétricosDocument375 paginiApostila Análise de Circuitos Elétricosvinleal003Încă nu există evaluări

- Eletronica Analogica Senai SCDocument98 paginiEletronica Analogica Senai SClucianomadeiraÎncă nu există evaluări

- Teoria 19 EncodersDocument13 paginiTeoria 19 EncodersAmanda DiasÎncă nu există evaluări

- Wanderleycardoso-Aula 03 - Interrupções e TemporizadoresDocument43 paginiWanderleycardoso-Aula 03 - Interrupções e TemporizadoresRicardo AlbrechtÎncă nu există evaluări

- Por Tras Do Trade Aula 1Document35 paginiPor Tras Do Trade Aula 1crismoraes.fotos2022Încă nu există evaluări

- ChaveadoresDocument17 paginiChaveadoresJulhao HackerÎncă nu există evaluări

- Relógio e Calendário Digital Com RTC DS1307Document8 paginiRelógio e Calendário Digital Com RTC DS1307Allan FlavioÎncă nu există evaluări

- 1 - Transistor Bipolar PDFDocument53 pagini1 - Transistor Bipolar PDFAntonio PortelaÎncă nu există evaluări

- Testes de Fonte ATX Com PIC PDFDocument5 paginiTestes de Fonte ATX Com PIC PDFRobson Dorival CordeiroÎncă nu există evaluări

- Desenvolvendo Um Medidor De Vazão Modbus Rs485 No ArduinoDe la EverandDesenvolvendo Um Medidor De Vazão Modbus Rs485 No ArduinoÎncă nu există evaluări

- Apostila Assembly MIPS Christiane PDFDocument51 paginiApostila Assembly MIPS Christiane PDFmichael_dougras1325450% (2)

- Manual NXTDocument80 paginiManual NXTRapHael SanderÎncă nu există evaluări

- Eletronica DigitalDocument19 paginiEletronica DigitalAnonymous xqAXarvXtÎncă nu există evaluări

- Sensores e transdutores: módulo didático completoDocument12 paginiSensores e transdutores: módulo didático completoAlex SouzaÎncă nu există evaluări

- Eletrônica Básica 2 - Aposta sobre conceitos de fontes de alimentação e transistoresDocument38 paginiEletrônica Básica 2 - Aposta sobre conceitos de fontes de alimentação e transistoresVicente Dos Santos Filho100% (3)

- Controladores lógicos programáveis e suas aplicações na indústriaDocument31 paginiControladores lógicos programáveis e suas aplicações na indústriaFernando Angelim LeiteÎncă nu există evaluări

- Curso de Reparo em Impressora Epson LX 300Document6 paginiCurso de Reparo em Impressora Epson LX 300Ricarte BalbinoÎncă nu există evaluări

- Curso Pós-Graduação Controle Lógico ProgramávelDocument81 paginiCurso Pós-Graduação Controle Lógico ProgramávelpfalencarÎncă nu există evaluări

- 03 Microcontroladores Pic16f628aDocument76 pagini03 Microcontroladores Pic16f628aAlexcya LopesÎncă nu există evaluări

- Transistor Bipolar de JunçãoDocument75 paginiTransistor Bipolar de JunçãoGrazielle Amanda100% (2)

- Injetor sinais 555Document6 paginiInjetor sinais 555Gabriel RochaÎncă nu există evaluări

- Uso de Imagens No PostgreSQLDocument2 paginiUso de Imagens No PostgreSQLRoberson NavesÎncă nu există evaluări

- EncoderDocument17 paginiEncoderRoberto VerhagenÎncă nu există evaluări

- Introdução à linguagem Assembly 8086 usando o programa DEBUGDocument7 paginiIntrodução à linguagem Assembly 8086 usando o programa DEBUGjeanpsilvaÎncă nu există evaluări

- Aprenda Linguagem C Básico para Microcontroladores - v1Document63 paginiAprenda Linguagem C Básico para Microcontroladores - v1Cassio Jose FonsecaÎncă nu există evaluări

- Amplificadores OperacionaisDocument30 paginiAmplificadores OperacionaisHellen RodriguesÎncă nu există evaluări

- Circuitos Integrados COS/MOS e Percu-SomDocument64 paginiCircuitos Integrados COS/MOS e Percu-Somg30.mirandaÎncă nu există evaluări

- 10 Fontes de Alimentação (ART1083)Document23 pagini10 Fontes de Alimentação (ART1083)jgsm1Încă nu există evaluări

- PIC18F4520 C LinguagemDocument49 paginiPIC18F4520 C LinguagemEng. Edelson Martins100% (1)

- J Antares Rpi Dose Book FinalDocument106 paginiJ Antares Rpi Dose Book FinalCarlos Enrique BortolotoÎncă nu există evaluări

- Móvel com instruções de montagem detalhadasDocument7 paginiMóvel com instruções de montagem detalhadasCarlos Enrique BortolotoÎncă nu există evaluări

- Instruções de montagem móvel G25702PRDocument10 paginiInstruções de montagem móvel G25702PRCarlos Enrique BortolotoÎncă nu există evaluări

- Artigo COBENGE19Document8 paginiArtigo COBENGE19Carlos Enrique BortolotoÎncă nu există evaluări

- Slides Pré Aula MS Project 2016 PDFDocument46 paginiSlides Pré Aula MS Project 2016 PDFCarlos Enrique BortolotoÎncă nu există evaluări

- G25121PRDocument14 paginiG25121PRCarlos Enrique BortolotoÎncă nu există evaluări

- G24124SPDocument17 paginiG24124SPCarlos Enrique BortolotoÎncă nu există evaluări

- QG 100Document23 paginiQG 100Carlos Enrique BortolotoÎncă nu există evaluări

- Cap2 PDFDocument39 paginiCap2 PDFCarlos Enrique BortolotoÎncă nu există evaluări

- Zener Diode Operation and ApplicationsDocument6 paginiZener Diode Operation and ApplicationsFellipe Miranda MartinsÎncă nu există evaluări

- Comandos MSDOSDocument1 paginăComandos MSDOSCarlos Enrique BortolotoÎncă nu există evaluări

- Instalações de TelefoniaDocument40 paginiInstalações de TelefoniaCarlos Enrique BortolotoÎncă nu există evaluări

- Ipod 4th Gen ManualDocument78 paginiIpod 4th Gen ManualCarlos Enrique BortolotoÎncă nu există evaluări

- O Cortiço de Aluísio AzevedoDocument162 paginiO Cortiço de Aluísio AzevedoRamon Luiz Santos GonçalvesÎncă nu există evaluări

- Anexo A - Fire-Loop GameDocument4 paginiAnexo A - Fire-Loop GameCarlos Enrique BortolotoÎncă nu există evaluări

- Apresentaçao Ciencias Dos MateriaisDocument10 paginiApresentaçao Ciencias Dos MateriaisAndrielly CarolineÎncă nu există evaluări

- 7 ErrosDocument20 pagini7 Errosrenatamruiz100% (3)

- 1000 Exercicios 2wDocument114 pagini1000 Exercicios 2wLucianne Monnier Merlo100% (1)

- Livro Sistemas BiologicosDocument133 paginiLivro Sistemas BiologicosJESSICA FERNANDES REGUERA RUIZ100% (1)

- Rafael Luglio Guedes DEFINITIVO 3105Document68 paginiRafael Luglio Guedes DEFINITIVO 3105rafael guedesÎncă nu există evaluări

- Como conquistar a felicidade com a TRECDocument112 paginiComo conquistar a felicidade com a TRECRita De Cassia MathaisÎncă nu există evaluări

- As 7 soluções para falta de dinheiro e como fazer seu dinheiro render maisDocument5 paginiAs 7 soluções para falta de dinheiro e como fazer seu dinheiro render maisProatma Soluções DefinitivasÎncă nu există evaluări

- Cravo Da Índia - Seus Poderes Mágicos - Oficina PDFDocument4 paginiCravo Da Índia - Seus Poderes Mágicos - Oficina PDFElton Castorino100% (2)

- Document 46328 1Document444 paginiDocument 46328 1Chirley SilvaÎncă nu există evaluări

- Sistema Cardiovascular 1Document34 paginiSistema Cardiovascular 1Camila AmaralÎncă nu există evaluări

- CoRolla 1.8Document2 paginiCoRolla 1.8Jose Graciano SouzaÎncă nu există evaluări

- Segurança diária e meio ambiente em discussãoDocument14 paginiSegurança diária e meio ambiente em discussãoSinalize SetÎncă nu există evaluări

- Direito Romano: Introdução, Conceitos e DivisãoDocument34 paginiDireito Romano: Introdução, Conceitos e DivisãoMarthaOliveiraÎncă nu există evaluări

- Alimentos limpos e impuros segundo a BíbliaDocument10 paginiAlimentos limpos e impuros segundo a BíbliaWeldner CeccatoÎncă nu există evaluări

- Aula 10 - Prática 2016Document22 paginiAula 10 - Prática 2016tthaliaramosÎncă nu există evaluări

- Exercício Avaliativo I - EmpreendedorismoDocument2 paginiExercício Avaliativo I - EmpreendedorismoPaulo SérgioÎncă nu există evaluări

- SALDOS. Carteiras e Nécessaires de Mulher BIMBA Y LOLA InvernoDocument1 paginăSALDOS. Carteiras e Nécessaires de Mulher BIMBA Y LOLA InvernoMariana Simões DinizÎncă nu există evaluări

- Agentes BiológicosDocument43 paginiAgentes Biológicosluis_carlos_467009100% (2)

- Equinócios e PáscoasDocument78 paginiEquinócios e PáscoasMário Renato MarianoÎncă nu există evaluări

- Revista Cultura Do Automóvel - Ed. 35 - Maio22Document52 paginiRevista Cultura Do Automóvel - Ed. 35 - Maio22alemao7x1 DiehlÎncă nu există evaluări

- Direito Administrativo - Liçoes IntroduçaoDocument663 paginiDireito Administrativo - Liçoes IntroduçaoAnonymous O73A0EwmSCÎncă nu există evaluări

- Novas Práticas para o Ensino MédioDocument319 paginiNovas Práticas para o Ensino MédioLipeh FamaÎncă nu există evaluări

- Porquinho Da ÍndiaDocument6 paginiPorquinho Da ÍndiaÉVELYN SANTOS DE OLIVEIRAÎncă nu există evaluări

- Prova - Cfs 1 2021 - Cod - 33Document28 paginiProva - Cfs 1 2021 - Cod - 33Desqueronee XesqueroneeÎncă nu există evaluări

- 1 - Evolução Do Modelo AtómicoDocument11 pagini1 - Evolução Do Modelo AtómicoAnabela MachadoÎncă nu există evaluări

- Manual Dos Exames CardíacosDocument45 paginiManual Dos Exames CardíacosMatheus BaraldiÎncă nu există evaluări

- Comportamento Organizacional e Liderança EficazDocument22 paginiComportamento Organizacional e Liderança EficazJadson CunhaÎncă nu există evaluări

- Darwin, mente e significado: análise críticaDocument12 paginiDarwin, mente e significado: análise críticajose.costajunior100% (1)

- Pisa 2012Document23 paginiPisa 2012Denizete Mesquita MesquitaÎncă nu există evaluări

- Lista de Exercícios 02 – Aritmética BináriaDocument2 paginiLista de Exercícios 02 – Aritmética BináriaTeo JavaÎncă nu există evaluări