Documente Academic

Documente Profesional

Documente Cultură

MCP3204 MCP3208 PDF

Încărcat de

Carlos PosadaTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

MCP3204 MCP3208 PDF

Încărcat de

Carlos PosadaDrepturi de autor:

Formate disponibile

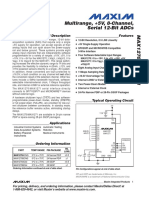

MCP3204/3208

2.7V 4-Channel/8-Channel 12-Bit A/D Converters

with SPI® Serial Interface

FEATURES PACKAGE TYPES

• 12-bit resolution PDIP, SOIC, TSSOP

• ± 1 LSB max DNL CH0 1 14 VDD

• ± 1 LSB max INL (MCP3204/3208-B) CH1 2 13 VREF

MCP3204

• ± 2 LSB max INL (MCP3204/3208-C) CH2 3 12 AGND

• 4 (MCP3204) or 8 (MCP3208) input channels CH3 4 11 CLK

• Analog inputs programmable as single-ended or NC 5 10 DOUT

pseudo differential pairs NC 6 9 DIN

DGND 7 8 CS/SHDN

• On-chip sample and hold

• SPI® serial interface (modes 0,0 and 1,1)

• Single supply operation: 2.7V - 5.5V

• 100ksps max. sampling rate at VDD = 5V PDIP, SOIC

• 50ksps max. sampling rate at VDD = 2.7V

• Low power CMOS technology CH0 1 16 VDD

- 500 nA typical standby current, 2µA max. CH1 2 15 VREF

MCP3208

CH2 3 14 AGND

- 400 µA max. active current at 5V

CH3 4 13 CLK

• Industrial temp range: -40°C to +85°C CH4 5 12 DOUT

• Available in PDIP, SOIC and TSSOP packages CH5 6 11 DIN

CH6 7 10 CS/SHDN

APPLICATIONS CH7 8 9 DGND

• Sensor Interface

• Process Control

• Data Acquisition FUNCTIONAL BLOCK DIAGRAM

• Battery Operated Systems

VDD VSS

DESCRIPTION VREF

The Microchip Technology Inc. MCP3204/3208 CH0

devices are successive approximation 12-bit Ana- CH1 Input

Channel DAC

log-to-Digital (A/D) Converters with on-board sample Mux

and hold circuitry. The MCP3204 is programmable to CH7*

provide two pseudo-differential input pairs or four sin- Comparator

gle-ended inputs. The MCP3208 is programmable to Sample 12-Bit SAR

provide four pseudo-differential input pairs or eight sin- and

Hold

gle-ended inputs. Differential Nonlinearity (DNL) is

specified at ±1 LSB, and Integral Nonlinearity (INL) is Shift

Control Logic

offered in ±1 LSB (MCP3204/3208-B) and ±2 LSB Register

(MCP3204/3208-C) versions. Communication with the

devices is done using a simple serial interface compat- CS/SHDN DIN CLK DOUT

ible with the SPI protocol. The devices are capable of

conversion rates of up to 100ksps. The MCP3204/3208 *Note: Channels 5-7 available on MCP3208 Only

devices operate over a broad voltage range (2.7V -

5.5V). Low current design permits operation with typi-

cal standby and active currents of only 500nA and

320µA, respectively. The MCP3204 is offered in 14-pin

PDIP, 150mil SOIC and TSSOP packages, and the

MCP3208 is offered in 16-pin PDIP and SOIC pack-

ages.

1999 Microchip Technology Inc. Preliminary DS21298B-page 1

MCP3204/3208

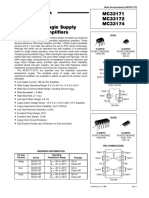

1.0 ELECTRICAL PIN FUNCTION TABLE

CHARACTERISTICS

NAME FUNCTION

1.1 Maximum Ratings* VDD +2.7V to 5.5V Power Supply

VDD.........................................................................7.0V DGND Digital Ground

All inputs and outputs w.r.t. VSS ...... -0.6V to VDD +0.6V AGND Analog Ground

Storage temperature ..........................-65°C to +150°C

CH0-CH7 Analog Inputs

Ambient temp. with power applied......-65°C to +125°C

Soldering temperature of leads (10 seconds) .. +300°C CLK Serial Clock

ESD protection on all pins ...................................> 4kV DIN Serial Data In

*Notice: Stresses above those listed under “Maximum Ratings” may DOUT Serial Data Out

cause permanent damage to the device. This is a stress rating only and

functional operation of the device at those or any other conditions CS/SHDN Chip Select/Shutdown Input

above those indicated in the operational listings of this specification is

not implied. Exposure to maximum rating conditions for extended peri- VREF Reference Voltage Input

ods may affect device reliability.

ELECTRICAL CHARACTERISTICS

All parameters apply at VDD = 5V, VSS = 0V, VREF = 5V, TAMB = -40°C to +85°C, fSAMPLE = 100ksps and

fCLK = 20*fSAMPLE, unless otherwise noted.

PARAMETER SYMBOL MIN. TYP. MAX. UNITS CONDITIONS

Conversion Rate

Conversion Time tCONV 12 clock

cycles

Analog Input Sample Time tSAMPLE 1.5 clock

cycles

Throughput Rate fSAMPLE 100 ksps VDD = VREF = 5V

50 ksps VDD = VREF = 2.7V

DC Accuracy

Resolution 12 bits

Integral Nonlinearity INL ±0.75 ±1 LSB MCP3204/3208-B

±1 ±2 MCP3204/3208-C

Differential Nonlinearity DNL ±0.5 ±1 LSB No missing codes over

temperature

Offset Error ±1.25 ±3 LSB

Gain Error ±1.25 ±5 LSB

Dynamic Performance

Total Harmonic Distortion -82 dB VIN = 0.1V to 4.9V@1kHz

Signal to Noise and Distortion 72 dB VIN = 0.1V to 4.9V@1kHz

(SINAD)

Spurious Free Dynamic 86 dB VIN = 0.1V to 4.9V@1kHz

Range

Reference Input

Voltage Range 0.25 VDD V Note 2

Current Drain 100 150 µA

0.001 3 µA CS = VDD = 5V

Analog Inputs

Input Voltage Range for VSS VREF V

CH0-CH7 in Single-Ended

Mode

Input Voltage Range for IN+ In IN- VREF+IN-

pseudo-differential Mode

Input Voltage Range for IN- In VSS-100 VSS+100 mV

pseudo-differential Mode

Leakage Current 0.001 ±1 µA

DS21298B-page 2 Preliminary 1999 Microchip Technology Inc.

MCP3204/3208

ELECTRICAL CHARACTERISTICS (CONTINUED)

All parameters apply at VDD = 5V, VSS = 0V, VREF = 5V, TAMB = -40°C to +85°C, fSAMPLE = 100ksps and

fCLK = 20*fSAMPLE, unless otherwise noted.

PARAMETER SYMBOL MIN. TYP. MAX. UNITS CONDITIONS

Analog Inputs (Continued)

Switch Resistance 1K Ω See Figure 4-1

Sample Capacitor 20 pF See Figure 4-1

Digital Input/Output

Data Coding Format Straight Binary

High Level Input Voltage VIH 0.7 VDD V

Low Level Input Voltage VIL 0.3 VDD V

High Level Output Voltage VOH 4.1 V IOH = -1mA, VDD = 4.5V

Low Level Output Voltage VOL 0.4 V IOL = 1mA, VDD = 4.5V

Input Leakage Current ILI -10 10 µA VIN = VSS or VDD

Output Leakage Current ILO -10 10 µA VOUT = VSS or VDD

Pin Capacitance CIN, COUT 10 pF VDD = 5.0V (Note 1)

(All Inputs/Outputs) TAMB = 25°C, f = 1 MHz

Timing Parameters

Clock Frequency fCLK 2.0 MHz VDD = 5V (Note 3)

1.0 MHz VDD = 2.7V (Note 3)

Clock High Time tHI 250 ns

Clock Low Time tLO 250 ns

CS Fall To First Rising CLK tSUCS 100 ns

Edge

Data Input Setup Time tSU 50 ns

Data Input Hold Time tHD 50 ns

CLK Fall To Output Data Valid tDO 200 ns See Test Circuits, Figure 1-2

CLK Fall To Output Enable tEN 200 ns See Test Circuits, Figure 1-2

CS Rise To Output Disable tDIS 100 ns See Test Circuits, Figure 1-2

CS Disable Time tCSH 500 ns

DOUT Rise Time tR 100 ns See Test Circuits, Figure 1-2

(Note 1)

DOUT Fall Time tF 100 ns See Test Circuits, Figure 1-2

(Note 1)

Power Requirements

Operating Voltage VDD 2.7 5.5 V

Operating Current IDD 320 400 µA VDD = VREF = 5V, DOUT unloaded

225 VDD = VREF = 2.7V, DOUT unloaded

Standby Current IDDS 0.5 2 µA CS = VDD = 5.0V

Note 1: This parameter is guaranteed by characterization and not 100% tested.

Note 2: See graphs that relate linearity performance to VREF levels.

Note 3: Because the sample cap will eventually lose charge, effective clock rates below 10kHz can affect linearity

performance, especially at elevated temperatures. See Section 6.2 for more information.

1999 Microchip Technology Inc. Preliminary DS21298B-page 3

MCP3204/3208

tCSH

CS

tSUCS

tHI tLO

CLK

tSU tHD

DIN MSB IN

tDO tR tF tDIS

tEN

DOUT NULL BIT MSB OUT LSB

FIGURE 1-1: Serial Interface Timing.

Load circuit for tR, tF, tDO Load circuit for tDIS and tEN

1.4V Test Point

VDD

tDIS Waveform 2

3K Test Point 3K VDD/2

DOUT DOUT tEN Waveform

CL = 100pF 100pF tDIS Waveform 1

VSS

Voltage Waveforms for tR, tF Voltage Waveforms for tEN

VOH CS

DOUT VOL

1 2 3 4

CLK

tR tF

DOUT B11

tEN

Voltage Waveforms for tDO Voltage Waveforms for tDIS

VIH

CS

CLK

DOUT

90%

tDO Waveform 1*

TDIS

DOUT

DOUT 10%

Waveform 2†

* Waveform 1 is for an output with internal condi-

tions such that the output is high, unless dis-

abled by the output control.

† Waveform 2 is for an output with internal condi-

tions such that the output is low, unless disabled

by the output control.

FIGURE 1-2: Test Circuits.

DS21298B-page 4 Preliminary 1999 Microchip Technology Inc.

MCP3204/3208

2.0 TYPICAL PERFORMANCE CHARACTERISTICS

Note: Unless otherwise indicated, VDD = VREF = 5V, VSS = 0V, fSAMPLE = 100ksps, fCLK = 20* fSAMPLE,TA = 25°C

1.0 2.0

VDD = VREF = 2.7V

0.8 Positive INL 1.5

0.6

1.0

0.4 Positive INL

INL (LSB)

INL (LSB)

0.5

0.2

0.0 0.0

-0.2 -0.5

Negative INL

-0.4 Negative INL -1.0

-0.6 -1.5

-0.8

-2.0

-1.0 0 10 20 30 40 50 60 70 80

0 25 50 75 100 125 150

Sample Rate (ksps) Sample Rate (ksps)

FIGURE 2-1: Integral Nonlinearity (INL) vs. Sample FIGURE 2-4: Integral Nonlinearity (INL) vs. Sample

Rate. Rate (VDD = 2.7V).

3.0 2.0

2.5

1.5

2.0

1.5 1.0 Positive INL

Positive INL

1.0

INL(LSB)

INL(LSB)

0.5

0.5

0.0 0.0

-0.5

Negative INL

-0.5

-1.0

-1.5 -1.0 Negative INL

-2.0

-1.5

-2.5

-3.0 -2.0

0 1 2 3 4 5 6 0.0 0.5 1.0 1.5 2.0 2.5 3.0

VREF (V) VREF (V)

FIGURE 2-2: Integral Nonlinearity (INL) vs. VREF. FIGURE 2-5: Integral Nonlinearity (INL) vs. VREF

(VDD = 2.7V).

1.0 1.0

0.8 0.8 VDD = VREF = 2.7V

FSAMPLE = 50ksps

0.6 0.6

0.4 0.4

INL (LSB)

INL (LSB)

0.2 0.2

0.0 0.0

-0.2 -0.2

-0.4 -0.4

-0.6 -0.6

-0.8 -0.8

-1.0 -1.0

0 512 1024 1536 2048 2560 3072 3584 4096 0 512 1024 1536 2048 2560 3072 3584 4096

Digital Code Digital Code

FIGURE 2-3: Integral Nonlinearity (INL) vs. Code FIGURE 2-6: Integral Nonlinearity (INL) vs. Code

(Representative Part). (Representative Part, VDD = 2.7V).

1999 Microchip Technology Inc. Preliminary DS21298B-page 5

MCP3204/3208

Note: Unless otherwise indicated, VDD = VREF = 5V, VSS = 0V, fSAMPLE = 100ksps, fCLK = 20* fSAMPLE,TA = 25°C

1.0 1.0

VDD = VREF = 2.7V

0.8 Positive INL 0.8

F SAMPLE = 50ksps

0.6 0.6

Positive INL

0.4 0.4

INL (LSB)

INL (LSB)

0.2 0.2

0.0 0.0

-0.2 Negative INL -0.2

-0.4 -0.4

-0.6 -0.6 Negative INL

-0.8 -0.8

-1.0 -1.0

-50 -25 0 25 50 75 100 -50 -25 0 25 50 75 100

Temperature (°C) Temperature (°C)

FIGURE 2-7: Integral Nonlinearity (INL) vs. FIGURE 2-10: Integral Nonlinearity (INL) vs.

Temperature. Temperature (VDD = 2.7V).

1.0 2.0

VDD = VREF = 2.7V

0.8 1.5

0.6 1.0

0.4 Positive DNL

DNL (LSB)

DNL (LSB)

Positive DNL

0.5

0.2

0.0 0.0

-0.2 -0.5 Negative DNL

-0.4

Negative DNL -1.0

-0.6

-0.8 -1.5

-1.0 -2.0

0 25 50 75 100 125 150 0 10 20 30 40 50 60 70

Sample Rate (ksps) Sample Rate (ksps)

FIGURE 2-8: Differential Nonlinearity (DNL) vs. FIGURE 2-11: Differential Nonlinearity (DNL) vs.

Sample Rate. Sample Rate (VDD = 2.7V).

3.0 3.0

VDD = VREF= 2.7V

2.0 2.0 FSAMPLE = 50ksps

Positive DNL

DNL (LSB)

1.0

DNL (LSB)

1.0 Positive DNL

0.0 0.0

Negative DNL Negative DNL

-1.0 -1.0

-2.0 -2.0

-3.0 -3.0

0 1 2 3 4 5 0.0 0.5 1.0 1.5 2.0 2.5 3.0

VREF (V) VREF(V)

FIGURE 2-9: Differential Nonlinearity (DNL) vs. FIGURE 2-12: Differential Nonlinearity (DNL) vs. VREF

VREF. (VDD = 2.7V).

DS21298B-page 6 Preliminary 1999 Microchip Technology Inc.

MCP3204/3208

Note: Unless otherwise indicated, VDD = VREF = 5V, VSS = 0V, fSAMPLE = 100ksps, fCLK = 20* fSAMPLE,TA = 25°C

1.0 1.0

0.8 0.8 VDD = VREF = 2.7V

FSAMPLE = 50ksps

0.6 0.6

0.4 0.4

DNL (LSB)

DNL (LSB)

0.2 0.2

0.0 0.0

-0.2 -0.2

-0.4 -0.4

-0.6 -0.6

-0.8 -0.8

-1.0 -1.0

0 512 1024 1536 2048 2560 3072 3584 4096 0 512 1024 1536 2048 2560 3072 3584 4096

Digital Code Digital Code

FIGURE 2-13: Differential Nonlinearity (DNL) vs. FIGURE 2-16: Differential Nonlinearity (DNL) vs.

Code (Representative Part). Code (Representative Part, VDD = 2.7V).

1.0 1.0

VDD = VREF = 2.7V

0.8 0.8

FSAMPLE = 50ksps

0.6 0.6

0.4 DNL (LSB) 0.4 Positive DNL

Positive DNL

DNL (LSB)

0.2 0.2

0.0 0.0

-0.2 -0.2

-0.4 -0.4 Negative DNL

Negative DNL

-0.6 -0.6

-0.8 -0.8

-1.0 -1.0

-50 -25 0 25 50 75 100 -50 -25 0 25 50 75 100

Temperature (°C) Temperature (°C)

FIGURE 2-14: Differential Nonlinearity (DNL) vs. FIGURE 2-17: Differential Nonlinearity (DNL) vs.

Temperature. Temperature (VDD = 2.7V).

4 20

18

3

VDD = 2.7V 16 VDD = 5V

Offset Error (LSB)

Gain Error (LSB)

2 F SAMPLE = 50ksps

14 F SAMPLE = 100ksps

1 12

10

0

8

-1 VDD = 2.7V

VDD = 5V 6

F SAMPLE = 50ksps

-2 FSAMPLE = 100ksps 4

-3 2

0

-4

0 1 2 3 4 5

0 1 2 3 4 5

VREF (V)

VREF(V)

FIGURE 2-15: Gain Error vs. VREF. FIGURE 2-18: Offset Error vs. VREF.

1999 Microchip Technology Inc. Preliminary DS21298B-page 7

MCP3204/3208

Note: Unless otherwise indicated, VDD = VREF = 5V, VSS = 0V, fSAMPLE = 100ksps, fCLK = 20* fSAMPLE,TA = 25°C

0.2 2.0

0.0 VDD = VREF = 2.7V 1.8

FSAMPLE = 50ksps VDD = VREF = 5V

1.6

Offset Error (LSB)

-0.2

Gain Error (LSB)

FSAMPLE = 100ksps

-0.4 1.4

-0.6 1.2

-0.8 1.0

VDD = VREF = 2.7V

-1.0 0.8

FSAMPLE = 50ksps

VDD = VREF = 5V

-1.2 0.6

FSAMPLE = 100ksps

-1.4 0.4

-1.6 0.2

-1.8 0.0

-50 -25 0 25 50 75 100 -50 -25 0 25 50 75 100

Temperature (°C) Temperature (°C)

FIGURE 2-19: Gain Error vs. Temperature. FIGURE 2-22: Offset Error vs. Temperature.

100 100.0

90 VDD = VREF = 5V VDD = VREF = 5V

90.0

FSAMPLE = 100ksps FSAMPLE = 100ksps

80 80.0

70

SINAD (dB)

70.0

SNR (dB)

60 60.0

50 50.0 VDD = VREF = 2.7V

40 VDD = VREF = 2.7V 40.0 F SAMPLE = 50ksps

30 FSAMPLE = 50ksps 30.0

20 20.0

10 10.0

0 0.0

1 10 100 1 10 100

Input Frequency (kHz) Input Frequency (kHz)

FIGURE 2-20: Signal to Noise (SNR) vs. Input FIGURE 2-23: Signal to Noise and Distortion

Frequency. (SINAD) vs. Input Frequency.

0 80

-10 VDD = VREF = 5V

70 FSAMPLE = 100ksps

-20

-30 60

VDD = VREF = 2.7V

THD (dB)

SINAD (dB)

-40 F SAMPLE = 50ksps 50

VDD = VREF = 2.7V

-50 40 FSAMPLE = 50ksps

-60

30

-70

20

-80 VDD = VREF = 5V

-90 FSAMPLE = 100ksps 10

-100 0

1 10 100 -40 -35 -30 -25 -20 -15 -10 -5 0

Input Frequency (kHz) Input Signal Level (dB)

FIGURE 2-21: Total Harmonic Distortion (THD) vs. FIGURE 2-24: Signal to Noise and Distortion

Input Frequency. (SINAD) vs. Input Signal Level.

DS21298B-page 8 Preliminary 1999 Microchip Technology Inc.

MCP3204/3208

Note: Unless otherwise indicated, VDD = VREF = 5V, VSS = 0V, fSAMPLE = 100ksps, fCLK = 20* fSAMPLE,TA = 25°C

12.0

12.00

11.75 11.5

11.50

11.0

ENOB (rms)

11.25

ENOB (rms)

11.00 VDD = VREF = 5V 10.5

10.75 VDD = VREF = 2.7V FSAMPLE =100ksps

10.50 10.0 VDD = VREF = 5V

FSAMPLE = 50ksps

10.25 F SAMPLE = 100ksps

9.5

10.00

9.75 9.0 VDD = VREF = 2.7V

9.50 F SAMPLE = 50ksps

9.25 8.5

9.00 8.0

0.0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0 1 10 100

VREF (V)

Input Frequency (kHz)

FIGURE 2-25: Effective Number of Bits (ENOB) vs. FIGURE 2-28: Effective Number of Bits (ENOB) vs.

VREF. Input Frequency.

100 0

VDD = VREF = 5V

Power Supply Rejection (dB)

90 -10

FSAMPLE = 100ksps

80

-20

70

SFDR (dB)

-30

60

50 VDD = VREF = 2.7V -40

40 FSAMPLE = 50ksps

-50

30

-60

20

-70

10

0 -80

1 10 100 1 10 100 1000 10000

Ripple Frequency (kHz)

Input Frequency (kHz)

FIGURE 2-26: Spurious Free Dynamic Range FIGURE 2-29: Power Supply Rejection (PSR) vs.

(SFDR) vs. Input Frequency. Ripple Frequency.

0

0

-10 VDD = VREF = 2.7V

-10 VDD = VREF = 5V

-20 FSAMPLE = 50ksps

-20 FSAMPLE = 100ksps -30 FINPUT = 998.76Hz

-30

Amplitude (dB)

FINPUT = 9.985kHz

Amplitude (dB)

-40 4096 points

-40 4096 points -50

-50

-60

-60

-70

-70

-80

-80

-90

-90

-100

-100

-110

-110

-120

-120

-130

-130

0 5000 10000 15000 20000 25000

0 10000 20000 30000 40000 50000

Frequency (Hz)

Frequency (Hz)

FIGURE 2-30: Frequency Spectrum of 1kHz input

FIGURE 2-27: Frequency Spectrum of 10kHz input

(Representative Part, VDD = 2.7V).

(Representative Part).

1999 Microchip Technology Inc. Preliminary DS21298B-page 9

MCP3204/3208

Note: Unless otherwise indicated, VDD = VREF = 5V, VSS = 0V, fSAMPLE = 100ksps, fCLK = 20* fSAMPLE,TA = 25°C

500 100

VREF = VDD VREF = VDD

450 90

All points at FCLK = 2MHz except All points at FCLK = 2MHz except

400 at VREF = VDD = 2.5V, F CLK = 1MHz 80

at VREF = VDD = 2.5V, F CLK = 1MHz

350 70

IREF (µA)

60

IDD (µA)

300

250 50

200 40

150 30

100 20

50 10

0 0

2.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5 6.0 2.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5 6.0

VDD (V) VDD (V)

FIGURE 2-31: IDD vs. VDD. FIGURE 2-34: IREF vs. VDD.

400 100

350 90 VDD = VREF = 5V

80

300

VDD = VREF = 5V 70

IREF (µA)

250 60

IDD (µA)

200 50

VDD = VREF = 2.7V

40

150

30 VDD = VREF = 2.7V

100 20

50 10

0 0

10 100 1000 10000 10 100 1000 10000

Clock Frequency (kHz) Clock Frequency (kHz)

FIGURE 2-32: IDD vs. Clock Frequency. FIGURE 2-35: IREF vs. Clock Frequency.

100

400 VDD = VREF = 5V

VDD = VREF = 5V 90 FCLK = 2MHz

350 FCLK = 2MHz

80

300

70

250

IDD (µA)

60

IREF (µA)

200 50

150 VDD = VREF = 2.7V 40

FCLK = 1MHz VDD = VREF = 2.7V

30

100 FCLK = 1MHz

20

50

10

0

0

-50 -25 0 25 50 75 100 -50 -25 0 25 50 75 100

Temperature (°C) Temperature (°C)

FIGURE 2-33: IDD vs. Temperature. FIGURE 2-36: IREF vs. Temperature.

DS21298B-page 10 Preliminary 1999 Microchip Technology Inc.

MCP3204/3208

Note: Unless otherwise indicated, VDD = VREF = 5V, VSS = 0V, fSAMPLE = 100ksps, fCLK = 20* fSAMPLE,TA = 25°C

80 2.0

Analog Input Leakage (nA)

VREF = CS = VDD

70 1.8

1.6

60

1.4

50

IDDS (pA)

1.2 VDD = VREF = 5V

40 1.0 FCLK = 2MHz

30 0.8

20

0.6

0.4

10

0.2

0 0.0

2.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5 6.0

-50 -25 0 25 50 75 100

VDD (V)

Temperature (°C)

FIGURE 2-37: IDDS vs. VDD. FIGURE 2-39: Analog Input Leakage Current vs.

Temperature.

100.00

VDD = VREF = CS = 5V

10.00

IDDS (nA)

1.00

0.10

0.01

-50 -25 0 25 50 75 100

Temperature (°C)

FIGURE 2-38: IDDS vs. Temperature.

1999 Microchip Technology Inc. Preliminary DS21298B-page 11

MCP3204/3208

3.0 PIN DESCRIPTIONS 4.1 Analog Inputs

3.1 CH0 - CH7 The MCP3204/3208 devices offer the choice of using

the analog input channels configured as single-ended

Analog inputs for channels 0 - 7 respectively for the inputs or pseudo-differential pairs. The MCP3204 can

multiplexed inputs. Each pair of channels can be pro- be configured to provide two pseudo-differential input

grammed to be used as two independent channels in pairs or four single-ended inputs. the MCP3208 can be

single ended-mode or as a single pseudo-differential configured to provide four pseudo-differential input

input where one channel is IN+ and one channel is IN-. pairs or eight single-ended inputs. Configuration is

See Section 4.1 and Section 5.0 for information on pro- done as part of the serial command before each con-

gramming the channel configuration. version begins. When used in the pseudo-differential

mode, each channel pair (i.e., CH0 and CH1, CH2 and

3.2 CS/SHDN(Chip Select/Shutdown) CH3 etc.) are programmed as the IN+ and IN- inputs as

part of the command string transmitted to the device.

The CS/SHDN pin is used to initiate communication

The IN+ input can range from IN- to (VREF + IN-). The

with the device when pulled low and will end a conver-

IN- input is limited to ±100mV from the VSS rail. The IN-

sion and put the device in low power standby when

input can be used to cancel small signal com-

pulled high. The CS/SHDN pin must be pulled high

mon-mode noise which is present on both the IN+ and

between conversions.

IN- inputs.

3.3 CLK (Serial Clock) When operating in the pseudo-differential mode, if the

voltage level of IN+ is equal to or less than IN-, the

The SPI clock pin is used to initiate a conversion and to resultant code will be 000h. If the voltage at IN+ is equal

clock out each bit of the conversion as it takes place. to or greater than {[VREF + (IN-)] - 1 LSB}, then the out-

See Section 6.2 for constraints on clock speed. put code will be FFFh. If the voltage level at IN- is more

than 1 LSB below VSS, then the voltage level at the IN+

3.4 DIN (Serial Data Input) input will have to go below VSS to see the 000h output

code. Conversely, if IN- is more than 1 LSB above VSS,

The SPI port serial data input pin is used to load chan-

then the FFFh code will not be seen unless the IN+

nel configuration data into the device.

input level goes above VREF level.

3.5 DOUT (Serial Data output) For the A/D Converter to meet specification, the charge

holding capacitor, (CSAMPLE) must be given enough time

The SPI serial data output pin is used to shift out the to acquire a 12-bit accurate voltage level during the 1.5

results of the A/D conversion. Data will always change clock cycle sampling period. The analog input model is

on the falling edge of each clock as the conversion shown in Figure 4-1.

takes place. In this diagram it is shown that the source impedance

(RS) adds to the internal sampling switch (RSS) imped-

3.6 AGND

ance, directly affecting the time that is required to

Analog ground connection to internal analog circuitry. charge the capacitor, CSAMPLE. Consequently, larger

source impedances increase the offset, gain, and inte-

3.7 DGND gral linearity errors of the conversion. See Figure 4-2.

Digital ground connection to internal digital circuitry. 4.2 Reference Input

For each device in the family, the reference input (VREF)

4.0 DEVICE OPERATION determines the analog input voltage range. As the ref-

The MCP3204/3208 A/D Converters employ a conven- erence input is reduced, the LSB size is reduced

tional SAR architecture. With this architecture, a sam- accordingly. The theoretical digital output code pro-

ple is acquired on an internal sample/hold capacitor for duced by the A/D Converter is a function of the analog

1.5 clock cycles starting on the fourth rising edge of the input signal and the reference input as shown below.

serial clock after the start bit has been received. Follow- Digital Output Code = 4096 * VIN

ing this sample time, the device uses the collected

VREF

charge on the internal sample and hold capacitor to

produce a serial 12-bit digital output code. Conversion where:

rates of 100ksps are possible on the MCP3204/3208. VIN = analog input voltage

See Section 6.2 for information on minimum clock VREF = reference voltage

rates. Communication with the device is done using a

4-wire SPI-compatible interface. When using an external voltage reference device, the

system designer should always refer to the manufac-

turer’s recommendations for circuit layout. Any instabil-

ity in the operation of the reference device will have a

direct effect on the operation of the A/D Converter.

DS21298B-page 12 Preliminary 1999 Microchip Technology Inc.

MCP3204/3208

VDD

Sampling

Switch

VT = 0.6V

RS CHx SS RSS = 1kΩ

CSAMPLE

CPIN

VA ILEAKAGE = DAC capacitance

7pF VT = 0.6V ± 1 nA = 20 pF

VSS

Legend

VA = Signal Source

RS = Source Impedance

CHx = Input Channel Pad

CPIN = Input Capacitance

VT = Threshold Voltage

ILEAKAGE = Leakage Current at the pin

due to various junctions

SS = Sampling Switch

RSS = Sampling Switch Resistor

CSAMPLE = Sample/Hold Capacitance

FIGURE 4-1: Analog Input Model

2.5

VDD = 5V

Clock Frequency (MHz)

2.0

1.5

1.0

VDD = 2.7V

0.5

0.0

100 1000 10000

Input Resistance (Ohms)

FIGURE 4-2: Maximum Clock Frequency vs. Input

resistance (RS) to maintain less than a 0.1LSB

deviation in INL from nominal conditions.

1999 Microchip Technology Inc. Preliminary DS21298B-page 13

MCP3204/3208

5.0 SERIAL COMMUNICATIONS CONTROL BIT

SELECTIONS

Communication with the MCP3204/3208 devices is INPUT CHANNEL

CONFIGURATION SELECTION

done using a standard SPI-compatible serial interface. SINGLE/ D2 D1 D0

Initiating communication with either device is done by DIFF

bringing the CS line low. See Figure 5-1. If the device 1 0 0 0 single ended CH0

was powered up with the CS pin low, it must be brought 1 0 0 1 single ended CH1

high and back low to initiate communication. The first

clock received with CS low and DIN high will constitute 1 0 1 0 single ended CH2

a start bit. The SGL/DIFF bit follows the start bit and will 1 0 1 1 single ended CH3

determine if the conversion will be done using single 1 1 0 0 single ended CH4

ended or differential input mode. The next three bits

1 1 0 1 single ended CH5

(D0, D1 and D2) are used to select the input channel

configuration. Table 5-1 and Table 5-2 show the config- 1 1 1 0 single ended CH6

uration bits for the MCP3204 and MCP3208, respec- 1 1 1 1 single ended CH7

tively. The device will begin to sample the analog input 0 0 0 0 differential CH0 = IN+

on the fourth rising edge of the clock after the start bit CH1 = IN-

has been received. The sample period will end on the 0 0 0 1 differential CH0 = IN-

falling edge of the fifth clock following the start bit. CH1 = IN+

After the D0 bit is input, one more clock is required to 0 0 1 0 differential CH2 = IN+

complete the sample and hold period (DIN is a don’t CH3 = IN-

care for this clock). On the falling edge of the next clock, 0 0 1 1 differential CH2 = IN-

the device will output a low null bit. The next 12 clocks CH3 = IN+

will output the result of the conversion with MSB first as 0 1 0 0 differential CH4 = IN+

shown in Figure 5-1. Data is always output from the CH5 = IN-

device on the falling edge of the clock. If all 12 data bits 0 1 0 1 differential CH4 = IN-

have been transmitted and the device continues to CH5 = IN+

receive clocks while the CS is held low, the device will

0 1 1 0 differential CH6 = IN+

output the conversion result LSB first as shown in CH7 = IN-

Figure 5-2. If more clocks are provided to the device

0 1 1 1 differential CH6 = IN-

while CS is still low (after the LSB first data has been CH7 = IN+

transmitted), the device will clock out zeros indefinitely.

TABLE 5-2: Configuration Bits for the MCP3208.

If necessary, it is possible to bring CS low and clock in

leading zeros on the DIN line before the start bit. This is

often done when dealing with microcontroller-based

SPI ports that must send 8 bits at a time. Refer to

Section 6.1 for more details on using the

MCP3204/3208 devices with hardware SPI ports.

CONTROL BIT

SELECTIONS

INPUT CHANNEL

CONFIGURATION SELECTION

SINGLE/ D2* D1 D0

DIFF

1 X 0 0 single ended CH0

1 X 0 1 single ended CH1

1 X 1 0 single ended CH2

1 X 1 1 single ended CH3

0 X 0 0 differential CH0 = IN+

CH1 = IN-

0 X 0 1 differential CH0 = IN-

CH1 = IN+

0 X 1 0 differential CH2 = IN+

CH3 = IN-

0 X 1 1 differential CH2 = IN-

CH3 = IN+

*D2 is don’t care for MCP3204

TABLE 5-1: Configuration Bits for the MCP3204.

DS21298B-page 14 Preliminary 1999 Microchip Technology Inc.

MCP3204/3208

tCYC tCYC

tCSH

CS

tSUCS

CLK

DIN Start SGL/ D2 D1 D0 Don’t Care Start SGL/ D2

DIFF DIFF

HI-Z Null HI-Z

DOUT Bit B11 B10 B9 B8 B7 B6 B5 B4 B3 B2 B1 B0 *

tCONV

tSAMPLE tDATA **

* After completing the data transfer, if further clocks are applied with CS low, the A/D Converter will output LSB

first data, then followed with zeros indefinitely. See Figure 5-2 below.

** tDATA: during this time, the bias current and the comparator power down while the reference input becomes

a high impedance node, leaving the CLK running to clock out the LSB-first data or zeros.

FIGURE 5-1: Communication with the MCP3204 or MCP3208.

tCYC

tCSH

CS

tSUCS

Power Down

CLK

Start

DIN D2 D1 D0 Don’t Care

SGL/

DIFF

HI-Z Null * HI-Z

B11 B10 B9 B8 B7 B6 B5 B4 B3 B2 B1 B0 B1 B2 B3 B4 B5 B6 B7 B8 B9 B10 B11

DOUT Bit

(MSB)

tCONV tDATA **

tSAMPLE

* After completing the data transfer, if further clocks are applied with CS low, the A/D Converter will output zeros

indefinitely.

** tDATA: During this time, the bias circuit and the comparator power down while the reference input becomes a

high impedance node, leaving the CLK running to clock out LSB first data or zeroes.

FIGURE 5-2: Communication with MCP3204 or MCP3208 in LSB First Format.

1999 Microchip Technology Inc. Preliminary DS21298B-page 15

MCP3204/3208

6.0 APPLICATIONS INFORMATION As shown in Figure 6-1, the first byte transmitted to the

A/D Converter contains five leading zeros before the

6.1 Using the MCP3204/3208 with start bit. Arranging the leading zeros this way produces

Microcontroller (MCU) SPI Ports the output 12 bits to fall in positions easily manipulated

by the MCU. The MSB is clocked out of the A/D Con-

With most microcontroller SPI ports, it is required to verter on the falling edge of clock number 12. After the

send groups of eight bits. It is also required that the second eight clocks have been sent to the device, the

microcontroller SPI port be configured to clock out data MCUs receive buffer will contain three unknown bits

on the falling edge of clock and latch data in on the rising (the output is at high impedance for the first two clocks),

edge. Because communication with the MCP3204/3208 the null bit and the highest order four bits of the conver-

devices may not need multiples of eight clocks, it will be sion. After the third byte has been sent to the device, the

necessary to provide more clocks than are required. receive register will contain the lowest order eight bits of

This is usually done by sending ‘leading zeros’ before the conversion results. Easier manipulation of the con-

the start bit. As an example, Figure 6-1 and Figure 6-2 verted data can be obtained by using this method.

shows how the MCP3204/3208 can be interfaced to a

Figure 6-2 shows the same thing in SPI Mode 1,1

MCU with a hardware SPI port. Figure 6-1 depicts the

which requires that the clock idles in the high state. As

operation shown in SPI Mode 0,0 which requires that the

with mode 0,0, the A/D Converter outputs data on the

SCLK from the MCU idles in the ‘low’ state, while

falling edge of the clock and the MCU latches data from

Figure 6-2 shows the similar case of SPI Mode 1,1

the A/D Converter in on the rising edge of the clock.

where the clock idles in the ‘high’ state.

CS

MCU latches data from A/D Converter

on rising edges of SCLK

SCLK 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24

Data is clocked out of

A/D Converter on falling edges

SGL/ D2 D1 DO

DIN Start Don’t Care

DIFF

HI-Z NULL

DOUT BIT B11 B10 B9 B8 B7 B6 B5 B4 B3 B2 B1 B0

Start

Bit

MCU Transmitted Data SGL/

(Aligned with falling 0 0 0 0 0 1 D2 D1 DO X X X X X X X X X X X X X X

DIFF

edge of clock)

MCU Received Data

(Aligned with rising ? ? ? ? ? ? ? ? ? ? ? 0 B11 B10 B9 B8 B7 B6 B5 B4 B3 B2 B1 B0

edge of clock) (Null)

Data stored into MCU receive register Data stored into MCU receive register Data stored into MCU receive register

after transmission of first 8 bits after transmission of second 8 bits after transmission of last 8 bits

X = Don’t Care Bits

FIGURE 6-1: SPI Communication using 8-bit segments (Mode 0,0: SCLK idles low).

CS MCU latches data from A/D Converter

on rising edges of SCLK

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24

SCLK

Data is clocked out of

A/D Converter on falling edges

SGL/ D2 D1 DO Don’t Care

DIN Start DIFF

HI-Z NULL

DOUT BIT B11 B10 B9 B8 B7 B6 B5 B4 B3 B2 B1 B0

Start

Bit

MCU Transmitted Data

(Aligned with falling 0 0 0 0 0 SGL/ D2

1 DIFF D1 DO X X X X X X X X X X X X X X

edge of clock)

MCU Received Data

(Aligned with rising ? ? ? ? ? ? ? ? ? ? ? 0 B11 B10 B9 B8 B7 B6 B5 B4 B3 B2 B1 B0

edge of clock) (Null)

Data stored into MCU receive register Data stored into MCU receive register Data stored into MCU receive register

after transmission of first 8 bits after transmission of second 8 bits after transmission of last 8 bits

X = Don’t Care Bits

FIGURE 6-2: SPI Communication using 8-bit segments (Mode 1,1: SCLK idles high).

DS21298B-page 16 Preliminary 1999 Microchip Technology Inc.

MCP3204/3208

6.2 Maintaining Minimum Clock Speed 6.4 Layout Considerations

When the MCP3204/3208 initiates the sample period, When laying out a printed circuit board for use with ana-

charge is stored on the sample capacitor. When the log components, care should be taken to reduce noise

sample period is complete, the device converts one bit wherever possible. A bypass capacitor should always

for each clock that is received. It is important for the be used with this device and should be placed as close

user to note that a slow clock rate will allow charge to as possible to the device pin. A bypass capacitor value

bleed off the sample capacitor while the conversion is of 1µF is recommended.

taking place. At 85°C (worst case condition), the part Digital and analog traces should be separated as much

will maintain proper charge on the sample capacitor for as possible on the board and no traces should run

at least 1.2ms after the sample period has ended. This underneath the device or the bypass capacitor. Extra

means that the time between the end of the sample precautions should be taken to keep traces with high

period and the time that all 12 data bits have been frequency signals (such as clock lines) as far as possi-

clocked out must not exceed 1.2ms (effective clock fre- ble from analog traces.

quency of 10kHz). Failure to meet this criterion may

induce linearity errors into the conversion outside the Use of an analog ground plane is recommended in

rated specifications. It should be noted that during the order to keep the ground potential the same for all

entire conversion cycle, the A/D Converter does not devices on the board. Providing VDD connections to

require a constant clock speed or duty cycle, as long as devices in a “star” configuration can also reduce noise

all timing specifications are met. by eliminating return current paths and associated

errors. See Figure 6-4. For more information on layout

6.3 Buffering/Filtering the Analog Inputs tips when using A/D Converters, refer to AN688 “Lay-

out Tips for 12-Bit A/D Converter Applications”.

If the signal source for the A/D Converter is not a low

impedance source, it will have to be buffered or inaccu-

rate conversion results may occur. See Figure 4-2. It is VDD

Connection

also recommended that a filter be used to eliminate any

signals that may be aliased back in to the conversion

results. This is illustrated in Figure 6-3 where an op

amp is used to drive the analog input of the

MCP3204/3208. This amplifier provides a low imped-

ance source for the converter input and a low pass fil- Device 4

ter, which eliminates unwanted high frequency noise.

Low pass (anti-aliasing) filters can be designed using Device 1

Microchip’s free interactive FilterLab™ software. Fil-

terLab will calculate capacitor and resistors values, as

well as determine the number of poles that are required Device 3

for the application. For more information on filtering sig-

Device 2

nals, see the application note AN699 “Anti-Aliasing

Analog Filters for Data Acquisition Systems.”

VDD

FIGURE 6-4: VDD traces arranged in a ‘Star’

10µF

4.096V configuration in order to reduce errors caused by

Reference

0.1µF 1µF

current return paths.

ADI Tant. 0.1µF

REF198

1µF

VREF

IN+

MCP3204

C1 MCP601 IN-

R1

+

R2

VIN -

C2

R4

R3

FIGURE 6-3: The MCP601 Operational Amplifier is

used to implement a 2nd order anti-aliasing filter for FilterLab is a trademark of Microchip Technology Inc. in

the signal being converted by the MCP3204. the U.S.A and other countries. All rights reserved.

1999 Microchip Technology Inc. Preliminary DS21298B-page 17

MCP3204/3208

6.5 Utilizing the Digital and Analog

Ground Pins

The MCP3204/3208 devices provide both digital and

analog ground connections to provide another means

of noise reduction. As shown in Figure 6-5, the analog

and digital circuitry is separated internal to the device.

This reduces noise from the digital portion of the device

being coupled into the analog portion of the device. The

two grounds are connected internally through the sub-

strate which has a resistance of 5 -10 Ω.

If no ground plane is utilized, then both grounds must

be connected to VSS on the board. If a ground plane is

available, both digital and analog ground pins should

be connected to the analog ground plane. If both an

analog and a digital ground plane are available, both

the digital and the analog ground pins should be con-

nected to the analog ground plane. Following these

steps will reduce the amount of digital noise from the

rest of the board being coupled into the A/D Converter.

VDD

Digital Side Analog Side

-SPI Interface -Sample Cap

-Shift Register -Capacitor Array

-Control Logic -Comparator

Substrate

5 - 10 Ω

Digital Analog

Ground Pin Ground Pin

FIGURE 6-5: Separation of Analog and Digital

Ground Pins.

DS21298B-page 18 Preliminary 1999 Microchip Technology Inc.

MCP3204/3208

MCP3204 PRODUCT IDENTIFICATION SYSTEMS

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

MCP3204 - G T /P

Package: P = PDIP (14 lead)

SL = SOIC (150 mil Body), 14 lead

ST = TSSOP, 14 lead (C Grade only)

Temperature I = –40°C to +85°C

Range:

Performance B = ±1 LSB INL (TSSOP not available in this grade)

Grade: C = ±2 LSB INL

Device: MCP3204 = 4-Channel 12-Bit Serial A/D Converter

MCP3204T = 4-Channel 12-Bit Serial A/D Converter on tape and reel

(SOIC and TSSOP packages only)

MCP3208 PRODUCT IDENTIFICATION SYSTEMS

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

MCP3208 - G T /P

Package: P = PDIP (16 lead)

SL = SOIC (150 mil Body), 16 lead

Temperature I = –40°C to +85°C

Range:

Performance B = ±1 LSB INL (TSSOP not available in this grade)

Grade: C = ±2 LSB INL

Device: MCP3208 = 8-Channel 12-Bit Serial A/D Converter

MCP3208T = 8-Channel 12-Bit Serial A/D Converter on tape and reel

(SOIC packages only)

Sales and Support

Data Sheets

Products supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recom-

mended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

1. Your local Microchip sales office

2. The Microchip Corporate Literature Center U.S. FAX: (602) 786-7277. After September 1, 1999, (480) 786-7277

3. The Microchip Worldwide Site (www.microchip.com)

Please specify which device, revision of silicon and Data Sheet (include Literature #) you are using.

New Customer Notification System

Register on our web site (www.microchip.com/cn) to receive the most current information on our products.

1999 Microchip Technology Inc. Preliminary DS21298B-page 19

WORLDWIDE SALES AND SERVICE

AMERICAS AMERICAS (continued) ASIA/PACIFIC (continued)

Corporate Office Toronto Singapore

Microchip Technology Inc. Microchip Technology Inc. Microchip Technology Singapore Pte Ltd.

2355 West Chandler Blvd. 5925 Airport Road, Suite 200 200 Middle Road

Chandler, AZ 85224-6199 Mississauga, Ontario L4V 1W1, Canada #07-02 Prime Centre

Tel: 480-786-7200 Fax: 480-786-7277 Tel: 905-405-6279 Fax: 905-405-6253 Singapore 188980

Technical Support: 480-786-7627 ASIA/PACIFIC Tel: 65-334-8870 Fax: 65-334-8850

Web Address: http://www.microchip.com Taiwan, R.O.C

Hong Kong Microchip Technology Taiwan

Atlanta Microchip Asia Pacific 10F-1C 207

Microchip Technology Inc. Unit 2101, Tower 2 Tung Hua North Road

500 Sugar Mill Road, Suite 200B Metroplaza Taipei, Taiwan, ROC

Atlanta, GA 30350 223 Hing Fong Road Tel: 886-2-2717-7175 Fax: 886-2-2545-0139

Tel: 770-640-0034 Fax: 770-640-0307 Kwai Fong, N.T., Hong Kong

Boston Tel: 852-2-401-1200 Fax: 852-2-401-3431 EUROPE

Microchip Technology Inc. Beijing United Kingdom

5 Mount Royal Avenue Microchip Technology, Beijing Arizona Microchip Technology Ltd.

Marlborough, MA 01752 Unit 915, 6 Chaoyangmen Bei Dajie 505 Eskdale Road

Tel: 508-480-9990 Fax: 508-480-8575 Dong Erhuan Road, Dongcheng District Winnersh Triangle

Chicago New China Hong Kong Manhattan Building Wokingham

Microchip Technology Inc. Beijing 100027 PRC Berkshire, England RG41 5TU

333 Pierce Road, Suite 180 Tel: 86-10-85282100 Fax: 86-10-85282104 Tel: 44 118 921 5858 Fax: 44-118 921-5835

Itasca, IL 60143 India Denmark

Tel: 630-285-0071 Fax: 630-285-0075 Microchip Technology Inc. Microchip Technology Denmark ApS

Dallas India Liaison Office Regus Business Centre

Microchip Technology Inc. No. 6, Legacy, Convent Road Lautrup hoj 1-3

4570 Westgrove Drive, Suite 160 Bangalore 560 025, India Ballerup DK-2750 Denmark

Addison, TX 75248 Tel: 91-80-229-0061 Fax: 91-80-229-0062 Tel: 45 4420 9895 Fax: 45 4420 9910

Tel: 972-818-7423 Fax: 972-818-2924 Japan France

Dayton Microchip Technology Intl. Inc. Arizona Microchip Technology SARL

Microchip Technology Inc. Benex S-1 6F Parc d’Activite du Moulin de Massy

Two Prestige Place, Suite 150 3-18-20, Shinyokohama 43 Rue du Saule Trapu

Miamisburg, OH 45342 Kohoku-Ku, Yokohama-shi Batiment A - ler Etage

Tel: 937-291-1654 Fax: 937-291-9175 Kanagawa 222-0033 Japan 91300 Massy, France

Detroit Tel: 81-45-471- 6166 Fax: 81-45-471-6122 Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Microchip Technology Inc. Korea Germany

Tri-Atria Office Building Microchip Technology Korea Arizona Microchip Technology GmbH

32255 Northwestern Highway, Suite 190 168-1, Youngbo Bldg. 3 Floor Gustav-Heinemann-Ring 125

Farmington Hills, MI 48334 Samsung-Dong, Kangnam-Ku D-81739 München, Germany

Tel: 248-538-2250 Fax: 248-538-2260 Seoul, Korea Tel: 49-89-627-144 0 Fax: 49-89-627-144-44

Los Angeles Tel: 82-2-554-7200 Fax: 82-2-558-5934 Italy

Microchip Technology Inc. Shanghai Arizona Microchip Technology SRL

18201 Von Karman, Suite 1090 Microchip Technology Centro Direzionale Colleoni

Irvine, CA 92612 RM 406 Shanghai Golden Bridge Bldg. Palazzo Taurus 1 V. Le Colleoni 1

Tel: 949-263-1888 Fax: 949-263-1338 2077 Yan’an Road West, Hong Qiao District 20041 Agrate Brianza

New York Shanghai, PRC 200335 Milan, Italy

Microchip Technology Inc. Tel: 86-21-6275-5700 Fax: 86 21-6275-5060 Tel: 39-039-65791-1 Fax: 39-039-6899883

150 Motor Parkway, Suite 202

11/15/99

Hauppauge, NY 11788

Tel: 631-273-5305 Fax: 631-273-5335

San Jose Microchip received QS-9000 quality system

Microchip Technology Inc. certification for its worldwide headquarters,

2107 North First Street, Suite 590 design and wafer fabrication facilities in

San Jose, CA 95131 Chandler and Tempe, Arizona in July 1999. The

Tel: 408-436-7950 Fax: 408-436-7955 Company’s quality system processes and

procedures are QS-9000 compliant for its

PICmicro® 8-bit MCUs, KEELOQ® code hopping

devices, Serial EEPROMs and microperipheral

products. In addition, Microchip’s quality

system for the design and manufacture of

development systems is ISO 9001 certified.

All rights reserved. © 1999 Microchip Technology Incorporated. Printed in the USA. 11/99 Printed on recycled paper.

Information contained in this publication regarding device applications and the like is intended for suggestion only and may be superseded by updates. No representation or warranty is given and no liability is assumed

by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip’s products

as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights. The Microchip

logo and name are registered trademarks of Microchip Technology Inc. in the U.S.A. and other countries. All rights reserved. All other trademarks mentioned herein are the property of their respective companies.

1999 Microchip Technology Inc.

S-ar putea să vă placă și

- Mcp320x 12-Bit AdcDocument34 paginiMcp320x 12-Bit AdcGeoFurrielÎncă nu există evaluări

- MCP 3008Document34 paginiMCP 3008Anita IonelaÎncă nu există evaluări

- 2.7V 4-Channel/8-Channel 12-Bit A/D Converters With SPI Serial InterfaceDocument41 pagini2.7V 4-Channel/8-Channel 12-Bit A/D Converters With SPI Serial InterfacecutoÎncă nu există evaluări

- MCP3202Document20 paginiMCP3202LuisÎncă nu există evaluări

- 2.7V 4-Channel/8-Channel 10-Bit A/D Converters With SPI Serial InterfaceDocument40 pagini2.7V 4-Channel/8-Channel 10-Bit A/D Converters With SPI Serial InterfacehelloÎncă nu există evaluări

- Mcp3208 - AdcDocument34 paginiMcp3208 - AdcNeneFIÎncă nu există evaluări

- DatasheetDocument48 paginiDatasheetGerardo Arcángel AlvarezÎncă nu există evaluări

- mcp3911 3.3v Two Channel Analog Front End ds20002286dDocument74 paginimcp3911 3.3v Two Channel Analog Front End ds20002286dJosueEspinozaÎncă nu există evaluări

- MAX1204 5V, 8-Channel, Serial, 10-Bit ADC With 3V Digital InterfaceDocument24 paginiMAX1204 5V, 8-Channel, Serial, 10-Bit ADC With 3V Digital InterfaceGeorge BintarchasÎncă nu există evaluări

- 2.7V Dual Channel 10-Bit A/D Converter With SPI Serial InterfaceDocument34 pagini2.7V Dual Channel 10-Bit A/D Converter With SPI Serial InterfaceVed Shekhar GowdaÎncă nu există evaluări

- 8/10/12-Bit Dual Voltage Output Digital-to-Analog Converter With Internal V and SPI InterfaceDocument50 pagini8/10/12-Bit Dual Voltage Output Digital-to-Analog Converter With Internal V and SPI InterfaceGustavo YbañezÎncă nu există evaluări

- Fm24c64a Ds EngDocument22 paginiFm24c64a Ds EngHamza Abbasi AbbasiÎncă nu există evaluări

- MCP413X/415X/423X/425X: 7/8-Bit Single/Dual SPI Digital POT With Volatile MemoryDocument82 paginiMCP413X/415X/423X/425X: 7/8-Bit Single/Dual SPI Digital POT With Volatile MemoryEyeVeeÎncă nu există evaluări

- Low-Power, 8-Channel, Serial 10-Bit ADC: - General DescriptionDocument25 paginiLow-Power, 8-Channel, Serial 10-Bit ADC: - General DescriptionAnkitÎncă nu există evaluări

- PCF85XXC-2 Fam 1 PDFDocument24 paginiPCF85XXC-2 Fam 1 PDFFlorin Bila-NicolaÎncă nu există evaluări

- +5V, Low-Power, 8-Bit Quad DAC With Rail-to-Rail Output BuffersDocument16 pagini+5V, Low-Power, 8-Bit Quad DAC With Rail-to-Rail Output BuffersMazhar IqbalÎncă nu există evaluări

- MCP4802Document46 paginiMCP4802KarbonÎncă nu există evaluări

- 3.3V Two-Channel Analog Front End: Features DescriptionDocument76 pagini3.3V Two-Channel Analog Front End: Features DescriptionSiete SieteÎncă nu există evaluări

- 21743BDocument28 pagini21743BRavinder Reddy AÎncă nu există evaluări

- MCP33131/21/11-XX: 1 Msps/500 KSPS 16/14/12-Bit Single-Ended Input SAR ADCDocument54 paginiMCP33131/21/11-XX: 1 Msps/500 KSPS 16/14/12-Bit Single-Ended Input SAR ADCtrival001Încă nu există evaluări

- ADocument84 paginiAVnuk MonikaÎncă nu există evaluări

- Advanced 250 V Three-Phase BLDC Controller With Embedded STM32 MCUDocument32 paginiAdvanced 250 V Three-Phase BLDC Controller With Embedded STM32 MCUOne SpringÎncă nu există evaluări

- 16-Bit, Serial Input Multiplying Digital-to-Analog ConverterDocument16 pagini16-Bit, Serial Input Multiplying Digital-to-Analog ConverternhbrÎncă nu există evaluări

- ADu M7703024586Document22 paginiADu M7703024586Sergio MuriloÎncă nu există evaluări

- CD4017 Datasheet PDFDocument8 paginiCD4017 Datasheet PDFRuben NinaÎncă nu există evaluări

- 2-Wire Serial EEPROM: FeaturesDocument19 pagini2-Wire Serial EEPROM: FeaturesAgustin AndrokaitesÎncă nu există evaluări

- V02 0409en - DS - HCPL 7860 - 2015 03 061 908727Document18 paginiV02 0409en - DS - HCPL 7860 - 2015 03 061 908727Shirley CastañedaÎncă nu există evaluări

- MCP2221 DatasheetDocument82 paginiMCP2221 Datasheetbs8j2cp5nnÎncă nu există evaluări

- Description Features: SBAS075Document15 paginiDescription Features: SBAS075Roozbeh BahmanyarÎncă nu există evaluări

- DS1302 DatasheetDocument15 paginiDS1302 DatasheetTripleXÎncă nu există evaluări

- Ad5308 5318 5328 PDFDocument28 paginiAd5308 5318 5328 PDFAndres Fernandez FernandezÎncă nu există evaluări

- CD4017BC - CD4022BC Decade Counter/Divider With 10 Decoded Outputs - Divide-By-8 Counter/Divider With 8 Decoded OutputsDocument8 paginiCD4017BC - CD4022BC Decade Counter/Divider With 10 Decoded Outputs - Divide-By-8 Counter/Divider With 8 Decoded Outputsfabian orozÎncă nu există evaluări

- Two-Wire Serial EEPROM 32K (4096 X 8) 64K (8192 X 8) AT24C32A AT24C64ADocument21 paginiTwo-Wire Serial EEPROM 32K (4096 X 8) 64K (8192 X 8) AT24C32A AT24C64Anordio2Încă nu există evaluări

- Dacmcp 4901Document51 paginiDacmcp 4901Ri Cha RdÎncă nu există evaluări

- 21290f PDFDocument40 pagini21290f PDFАндрій БілявськийÎncă nu există evaluări

- Ad7403 1517424Document25 paginiAd7403 1517424Mohammad AsadiÎncă nu există evaluări

- MCP2221A: USB 2.0 To I C/UART Protocol Converter With GPIODocument80 paginiMCP2221A: USB 2.0 To I C/UART Protocol Converter With GPIOSupernova SimulationsÎncă nu există evaluări

- 24c1024 Ic DatasheetDocument20 pagini24c1024 Ic DatasheetVikas AttardeÎncă nu există evaluări

- Three-Wire Serial Eeprom: FeaturesDocument21 paginiThree-Wire Serial Eeprom: FeaturesАлександр СаральповÎncă nu există evaluări

- MCP342X Datasheet PDFDocument58 paginiMCP342X Datasheet PDFFelipePerezÎncă nu există evaluări

- DatasheetDocument12 paginiDatasheetKlan ZangoÎncă nu există evaluări

- Two-Wire Serial Eeprom: FeaturesDocument19 paginiTwo-Wire Serial Eeprom: Featuresvladimir_p80Încă nu există evaluări

- Three-Wire Serial EEPROM: 1. FeaturesDocument17 paginiThree-Wire Serial EEPROM: 1. FeatureskppsadiÎncă nu există evaluări

- T6963CDocument28 paginiT6963Capi-19831863Încă nu există evaluări

- MCP413X 415X 423X 425X PDFDocument88 paginiMCP413X 415X 423X 425X PDFspotÎncă nu există evaluări

- MCP 4141Document88 paginiMCP 4141ikaro181083Încă nu există evaluări

- Two-Wire Serial EEPROM 32K (4096 X 8) 64K (8192 X 8) AT24C32A AT24C64ADocument22 paginiTwo-Wire Serial EEPROM 32K (4096 X 8) 64K (8192 X 8) AT24C32A AT24C64AmedÎncă nu există evaluări

- SN 65 HVD 33Document32 paginiSN 65 HVD 33craigslist_nÎncă nu există evaluări

- ADP3212DDocument35 paginiADP3212DDraghiNikoÎncă nu există evaluări

- 4.0x2.0x1.6mm 0.1W/0.2W Intelligent External Control Surface Mount SMD Side Light Emitting LED (MSL:5a)Document19 pagini4.0x2.0x1.6mm 0.1W/0.2W Intelligent External Control Surface Mount SMD Side Light Emitting LED (MSL:5a)jakalae5263Încă nu există evaluări

- Anil ProjectDocument8 paginiAnil Projectapi-3713690Încă nu există evaluări

- Tps 65218 D 0Document112 paginiTps 65218 D 0carlos huenupanÎncă nu există evaluări

- Adc 1283Document24 paginiAdc 1283Manuel MarquesÎncă nu există evaluări

- Precision Digital-to-Analog Converters: SEA DFAE Training Dec 2004Document38 paginiPrecision Digital-to-Analog Converters: SEA DFAE Training Dec 2004wildmonkey88Încă nu există evaluări

- 3-Wire Serial Eeproms: FeaturesDocument18 pagini3-Wire Serial Eeproms: FeaturesAriana ScheiderÎncă nu există evaluări

- Adc128s022 PDFDocument20 paginiAdc128s022 PDFThiagoÎncă nu există evaluări

- Multirange, +5V, 8-Channel, Serial 12-Bit Adcs: General Description FeaturesDocument21 paginiMultirange, +5V, 8-Channel, Serial 12-Bit Adcs: General Description FeaturesGeorge BintarchasÎncă nu există evaluări

- EEPROM 24C256 - Atmel PDFDocument20 paginiEEPROM 24C256 - Atmel PDFValdir DerlannÎncă nu există evaluări

- Max 1011Document12 paginiMax 1011Carlos PosadaÎncă nu există evaluări

- BB PCM 61pdatasheetDocument4 paginiBB PCM 61pdatasheetenergiculÎncă nu există evaluări

- P6ke6v8 (C) A - P6ke440 (C) ADocument3 paginiP6ke6v8 (C) A - P6ke440 (C) ACarlos PosadaÎncă nu există evaluări

- Max 1114Document12 paginiMax 1114Carlos PosadaÎncă nu există evaluări

- TDA1387 PhilipsDocument16 paginiTDA1387 PhilipsCarlos PosadaÎncă nu există evaluări

- Icl7135c - TLC7135CDocument11 paginiIcl7135c - TLC7135CCarlos PosadaÎncă nu există evaluări

- Multirange, +5V, 12-Bit DAS With 2-Wire Serial Interface: General Description FeaturesDocument16 paginiMultirange, +5V, 12-Bit DAS With 2-Wire Serial Interface: General Description FeaturesCarlos PosadaÎncă nu există evaluări

- Max 1003Document12 paginiMax 1003Carlos PosadaÎncă nu există evaluări

- Max 1002Document12 paginiMax 1002Carlos PosadaÎncă nu există evaluări

- CS4338 PDFDocument26 paginiCS4338 PDFCarlos PosadaÎncă nu există evaluări

- 250Msps, 8-Bit ADC With Track/Hold: Evaluation Kit AvailableDocument16 pagini250Msps, 8-Bit ADC With Track/Hold: Evaluation Kit AvailableCarlos PosadaÎncă nu există evaluări

- OP471 PDFDocument16 paginiOP471 PDFCarlos PosadaÎncă nu există evaluări

- Max114 Max118Document12 paginiMax114 Max118Carlos PosadaÎncă nu există evaluări

- Adc 081000Document29 paginiAdc 081000Carlos PosadaÎncă nu există evaluări

- CS4360 Cirrus LogicDocument37 paginiCS4360 Cirrus LogicCarlos PosadaÎncă nu există evaluări

- CS4360 Cirrus LogicDocument37 paginiCS4360 Cirrus LogicCarlos PosadaÎncă nu există evaluări

- OP777 - Analog DevicesDocument12 paginiOP777 - Analog DevicesCarlos PosadaÎncă nu există evaluări

- LM2900 - LM3900 PDFDocument9 paginiLM2900 - LM3900 PDFCarlos PosadaÎncă nu există evaluări

- NJM4565 JRCDocument5 paginiNJM4565 JRCCarlos PosadaÎncă nu există evaluări

- NE5532 ON Semiconductor PDFDocument10 paginiNE5532 ON Semiconductor PDFCarlos PosadaÎncă nu există evaluări

- TDA1311ADocument20 paginiTDA1311ACarlos PosadaÎncă nu există evaluări

- MC 33174Document12 paginiMC 33174Carlos PosadaÎncă nu există evaluări

- Ba10324 Rohm PDFDocument5 paginiBa10324 Rohm PDFCarlos PosadaÎncă nu există evaluări

- Tea 2025Document9 paginiTea 2025Duong HusterÎncă nu există evaluări

- Tda 8588 AjDocument54 paginiTda 8588 AjAngel Fig100% (1)

- TDA2030ADocument15 paginiTDA2030AAtsivatlaÎncă nu există evaluări

- Tda7294 PDFDocument16 paginiTda7294 PDFRoger NunesÎncă nu există evaluări

- TDA2009a DatasheetDocument12 paginiTDA2009a Datasheeticecore02100% (2)

- 22W Bridge / Stereo Audio Amplifier With Clipping Detector: ProtectionsDocument22 pagini22W Bridge / Stereo Audio Amplifier With Clipping Detector: ProtectionsManase RomeoÎncă nu există evaluări

- Arabsat 5CDocument5 paginiArabsat 5Chidrogen.h.786786Încă nu există evaluări

- 2.1 Basic Concept of NetworkDocument17 pagini2.1 Basic Concept of NetworkSyamier DanishÎncă nu există evaluări

- RRC Connection: Radio BearerDocument12 paginiRRC Connection: Radio BearerGEORGE MYLONASÎncă nu există evaluări

- DWR 978 Datasheet EU ENDocument2 paginiDWR 978 Datasheet EU ENvishalteslaÎncă nu există evaluări

- Uc Creg 097 2008Document399 paginiUc Creg 097 2008algotrÎncă nu există evaluări

- Assignment # 2Document1 paginăAssignment # 2Mod454Încă nu există evaluări

- 2019 Chrysler Dodge Jeep Ram SRT ManualDocument202 pagini2019 Chrysler Dodge Jeep Ram SRT ManualRadiocode24Încă nu există evaluări

- Capacity Controller EKC 331TDocument12 paginiCapacity Controller EKC 331Tabdur rafayÎncă nu există evaluări

- Communication Systems by B P Lathi PDFDocument2 paginiCommunication Systems by B P Lathi PDFAshley0% (3)

- BeSweet BelightDocument41 paginiBeSweet BelightMab AcÎncă nu există evaluări

- Alber Bds 256xl Installation Instructions - Combined Reading PDFDocument82 paginiAlber Bds 256xl Installation Instructions - Combined Reading PDFVinicius AlmeidaÎncă nu există evaluări

- IoT Based Raspberry Pi Smart Energy MonitorDocument17 paginiIoT Based Raspberry Pi Smart Energy MonitorKoushik Maity100% (1)

- Suntrio Plus 12-20K-Datasheet 201907Document1 paginăSuntrio Plus 12-20K-Datasheet 201907ali ahmadÎncă nu există evaluări

- Ultrasonic PCB Generator ManualDocument7 paginiUltrasonic PCB Generator ManualopetakyÎncă nu există evaluări

- Fault Passage IndicatorDocument5 paginiFault Passage Indicatorbibhas_samantaÎncă nu există evaluări

- Stepper Motor Controller Using 8051Document37 paginiStepper Motor Controller Using 8051gutzz0079197100% (2)

- BCU TR - 6MD85.rv1Document5 paginiBCU TR - 6MD85.rv1PằngPằngChiuChiuÎncă nu există evaluări

- Busbar and breaker failure protection overviewDocument20 paginiBusbar and breaker failure protection overviewarun singhÎncă nu există evaluări

- Siprotec 5 Configuration May 29, 2017 2:18 PM: Note On Function-Points ClassDocument6 paginiSiprotec 5 Configuration May 29, 2017 2:18 PM: Note On Function-Points ClassOae FlorinÎncă nu există evaluări

- Content Sheet: Micro-Star Int'L Co.,Ltd Micro-Star Int'L Co.,Ltd Micro-Star Int'L Co.,LtdDocument32 paginiContent Sheet: Micro-Star Int'L Co.,Ltd Micro-Star Int'L Co.,Ltd Micro-Star Int'L Co.,LtdkasimkaÎncă nu există evaluări

- RM100 Installation Manual Moore Industries1Document32 paginiRM100 Installation Manual Moore Industries1Ikhuosho AbodeÎncă nu există evaluări

- Eaget M880-User Manual v1.0.3Document44 paginiEaget M880-User Manual v1.0.3NewÎncă nu există evaluări

- Viettel PresentationDocument25 paginiViettel PresentationDuy NguyenÎncă nu există evaluări

- JE50-HR M/B SchematicsDocument61 paginiJE50-HR M/B SchematicsismaeltorresrojasÎncă nu există evaluări

- TECH VibrationDiagnosticGuideDocument2 paginiTECH VibrationDiagnosticGuidetiagofer84575Încă nu există evaluări

- Software Defined RadioDocument6 paginiSoftware Defined RadioUjjwal DhusiaÎncă nu există evaluări

- The Mumbai Suburban Railway Smart CardDocument17 paginiThe Mumbai Suburban Railway Smart Cardrsmbgss575Încă nu există evaluări

- Phantom Load ManualDocument52 paginiPhantom Load ManualVirna SilaoÎncă nu există evaluări

- HW Rest Part1Document5 paginiHW Rest Part1Anand SridharanÎncă nu există evaluări