Documente Academic

Documente Profesional

Documente Cultură

AD7811/AD7812: Parameter Y Version Units Test Conditions/Comments

Încărcat de

Antonio HerreraTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

AD7811/AD7812: Parameter Y Version Units Test Conditions/Comments

Încărcat de

Antonio HerreraDrepturi de autor:

Formate disponibile

AD7811/AD7812

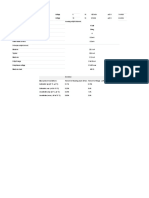

Parameter Y Version Units Test Conditions/Comments

POWER SUPPLY

VDD 2.7 V min For Specified Performance

5.5 V max

IDD Digital Inputs = 0 V or VDD

Normal Operation 3.5 mA max

Power-Down

Full Power-Down 1 µA max

Partial Power-Down (Internal Ref) 350 µA max See Power-Up Times Section

Power Dissipation VDD = 3 V

Normal Operation 10.5 mW max

Auto Full Power-Down See Power vs. Throughput Section

Throughput 1 kSPS 31.5 µW max

Throughput 10 kSPS 315 µW max

Throughput 100 kSPS 3.15 mW max

Partial Power-Down (Internal Ref) 1.05 mW max

Full Power-Down 3 µW max

NOTES

1

See Terminology.

2

Sample tested during initial release and after any redesign or process change that may affect this parameter.

Specifications subject to change without notice.

TIMING CHARACTERISTICS1, 2 (V DD = +2.7 V to +5.5 V, VREF = +VDD [EXT] unless otherwise noted)

Parameter Y Version Units Conditions/Comments

tPOWER-UP 1 µs (max) Power-Up Time of AD7811/AD7812 After Rising Edge of CONVST

t1 2.3 µs (max) Conversion Time

t2 20 ns (min) CONVST Pulsewidth

t3 25 ns (min) SCLK High Pulsewidth

t4 25 ns (min) SCLK Low Pulsewidth

t5 3 5 ns (min) RFS Rising Edge to SCLK Rising Edge Setup Time

t6 3 5 ns (min) TFS Falling Edge to SCLK Falling Edge Setup Time

t7 3 10 ns (max) SCLK Rising Edge to Data Out Valid

t8 10 ns (min) DIN Data Valid to SCLK Falling Edge Setup Time

t9 5 ns (min) DIN Data Valid after SCLK Falling Edge Hold Time

t103, 4 20 ns (max) SCLK Rising Edge to DOUT High Impedance

t11 100 ns (min) DOUT High Impedance to CONVST Falling Edge

NOTES

1

Sample tested to ensure compliance.

2

See Figures 16, 17 and 18.

3

These numbers are measured with the load circuit of Figure 1. They are defined as the time required for the o/p to cross 0.8 V or 2.4 V for V DD = 5 V ± 10% and

0.4 V or 2 V for V DD = 3 V ± 10%.

4

Derived from the measured time taken by the data outputs to change 0.5 V when loaded with the circuit of Figure 1. The measured number is then extrapolated back

to remove the effects of charging or discharging the 50 pF capacitor. This means that the time, t 11, quoted in the Timing Characteristics is the true bus relinquish

time of the part and as such is independent of external bus loading capacitances.

Specifications subject to change without notice.

200 A IOL

TO

OUTPUT +2.1V

PIN CL

50pF

200 A IOH

Figure 1. Load Circuit for Digital Output Timing Specifications

REV. A –3–

S-ar putea să vă placă și

- Testing, Adjusting, and Balancing - TabDocument19 paginiTesting, Adjusting, and Balancing - TabAmal Ka100% (1)

- Stability Analysis of Steel Storage Rack Structures PDFDocument7 paginiStability Analysis of Steel Storage Rack Structures PDFFabian Flemin BahamondeÎncă nu există evaluări

- ATR4518R2Document2 paginiATR4518R2estebanarca50% (4)

- Therapeutic EffectsofWhole-BodyDevices Applying Pulsed Electromagnetic Fields (PEMF)Document11 paginiTherapeutic EffectsofWhole-BodyDevices Applying Pulsed Electromagnetic Fields (PEMF)Jeroan MonteiroÎncă nu există evaluări

- Unit 07 Self-Test Chemistry Self TestDocument2 paginiUnit 07 Self-Test Chemistry Self TestOluwatusin Ayo OluwatobiÎncă nu există evaluări

- RespiratorypptDocument69 paginiRespiratorypptMichelle RotairoÎncă nu există evaluări

- Ce Const2 132kv CB Siemens 2012 PDFDocument12 paginiCe Const2 132kv CB Siemens 2012 PDFOctavio EspañaÎncă nu există evaluări

- AD7811/AD7812: Parameter Y Version Units Test Conditions/CommentsDocument1 paginăAD7811/AD7812: Parameter Y Version Units Test Conditions/CommentsAntonio HerreraÎncă nu există evaluări

- 1.25Gb 20klm SM 1550nm LC (Cisco Coded)Document7 pagini1.25Gb 20klm SM 1550nm LC (Cisco Coded)Sean SerinÎncă nu există evaluări

- Iris 4015Document6 paginiIris 4015vetchboyÎncă nu există evaluări

- 1.25Gb 20klm 1490T-1310R SM (Standard Code)Document6 pagini1.25Gb 20klm 1490T-1310R SM (Standard Code)Sean SerinÎncă nu există evaluări

- 1.25Gb 550mtr MM LC (Cisco Coded)Document6 pagini1.25Gb 550mtr MM LC (Cisco Coded)Sean SerinÎncă nu există evaluări

- TC75S67TU: Single Operational Amplifier (Ultra Low Noise Operational Amplifier)Document11 paginiTC75S67TU: Single Operational Amplifier (Ultra Low Noise Operational Amplifier)amaza_prodeoÎncă nu există evaluări

- PMCC VCO24-30G Datasheet Rev 2.3Document3 paginiPMCC VCO24-30G Datasheet Rev 2.3GbarbarÎncă nu există evaluări

- Texas Advanced Optoelectronic Solutions Inc.: DescriptionDocument6 paginiTexas Advanced Optoelectronic Solutions Inc.: DescriptionJohnny CGÎncă nu există evaluări

- Hoja de Datos 10n65kDocument6 paginiHoja de Datos 10n65kleamxi777Încă nu există evaluări

- 2N6ADocument4 pagini2N6Ajackson singhÎncă nu există evaluări

- 1NN70-ML Unisonic Dual 1A MOSFETDocument6 pagini1NN70-ML Unisonic Dual 1A MOSFETvanderlei1Încă nu există evaluări

- 3A L.D.O. VOLTAGE REGULATOR (Adjustable & Fixed) LM1085: FeaturesDocument8 pagini3A L.D.O. VOLTAGE REGULATOR (Adjustable & Fixed) LM1085: FeatureslghmshariÎncă nu există evaluări

- 3 N 80Document6 pagini3 N 80Mahmoued YasinÎncă nu există evaluări

- STD17NF03Document9 paginiSTD17NF03VeronicaÎncă nu există evaluări

- NDP2331Document9 paginiNDP2331Dedy GameÎncă nu există evaluări

- N-Channel 100 V, 0.0036 Typ., 110 A, Stripfet™ F7 Power Mosfet in A To-220 PackageDocument13 paginiN-Channel 100 V, 0.0036 Typ., 110 A, Stripfet™ F7 Power Mosfet in A To-220 PackageCarautotronica LaboratorioÎncă nu există evaluări

- Stp5Nc50 - Stp5Nc50Fp Stb5Nc50 - Stb5Nc50-1: N-Channel 500V - 1.3 - 5.5A To-220/Fp/D Pak/I Pak Powermesh Ii MosfetDocument12 paginiStp5Nc50 - Stp5Nc50Fp Stb5Nc50 - Stb5Nc50-1: N-Channel 500V - 1.3 - 5.5A To-220/Fp/D Pak/I Pak Powermesh Ii MosfetJavier55Încă nu există evaluări

- 7A 650V N-Channel Enhancement Mode Power MOSFET: 7N65/F7N65/I7N65/E7N65/B7N65/D7N65Document11 pagini7A 650V N-Channel Enhancement Mode Power MOSFET: 7N65/F7N65/I7N65/E7N65/B7N65/D7N65Sergio Daniel CaminoÎncă nu există evaluări

- 3N80Document6 pagini3N80hectorsevillaÎncă nu există evaluări

- Unisonic Technologies Co., LTD: 1.2A, 600V N-CHANNEL Power MosfetDocument7 paginiUnisonic Technologies Co., LTD: 1.2A, 600V N-CHANNEL Power MosfetRogerio E. SantoÎncă nu există evaluări

- 3001B-DIP8: SANYO Electric Co.,Ltd. Semiconductor Bussiness HeadquartersDocument4 pagini3001B-DIP8: SANYO Electric Co.,Ltd. Semiconductor Bussiness HeadquartersManuel MartinezÎncă nu există evaluări

- FCH067N65S3 FairchildSemiconductorDocument9 paginiFCH067N65S3 FairchildSemiconductorJoaquim FernandesÎncă nu există evaluări

- DatasheetDocument12 paginiDatasheetErwin Rolando EscobarÎncă nu există evaluări

- MMRF1016HDocument19 paginiMMRF1016HandreasmonÎncă nu există evaluări

- IRIS-G5653: FeaturesDocument8 paginiIRIS-G5653: FeaturesisaiasvaÎncă nu există evaluări

- STB12NK80Z STP12NK80Z - STW12NK80ZDocument16 paginiSTB12NK80Z STP12NK80Z - STW12NK80ZMAKERÎncă nu există evaluări

- General Description: Multi-Mode Primary Side Regulation (PSR) CV/CC ControllerDocument11 paginiGeneral Description: Multi-Mode Primary Side Regulation (PSR) CV/CC ControllertoolsÎncă nu există evaluări

- STP 5 NK 100 ZDocument15 paginiSTP 5 NK 100 ZJimmy LinaresÎncă nu există evaluări

- 2SK2978 RenesasDocument7 pagini2SK2978 RenesasJuan NunesÎncă nu există evaluări

- STD3N62K3, STF3N62K3, Stu3n62k3Document27 paginiSTD3N62K3, STF3N62K3, Stu3n62k3David Alberto Lotero AlvarezÎncă nu există evaluări

- Design Considerations When Using Radiation-Hardened Small Signal Logic Level MOSFETs International Rectifier An1067Document25 paginiDesign Considerations When Using Radiation-Hardened Small Signal Logic Level MOSFETs International Rectifier An1067abcdÎncă nu există evaluări

- STP11NK50ZDocument13 paginiSTP11NK50ZWilliam OliveiraÎncă nu există evaluări

- Tk10a60d5 Tk10a60d5 Tk10a60d5 Tk10a60d5Document9 paginiTk10a60d5 Tk10a60d5 Tk10a60d5 Tk10a60d5Yaneisi MariñoÎncă nu există evaluări

- Circuito en Fuente TV LCD Mustek N3856VGDocument13 paginiCircuito en Fuente TV LCD Mustek N3856VGAntonio ChavezÎncă nu există evaluări

- Exercise Sheet 1: Buck-Converter (Step-Down Converter)Document10 paginiExercise Sheet 1: Buck-Converter (Step-Down Converter)Fury NightÎncă nu există evaluări

- MLC 777442Document5 paginiMLC 777442GabrieleÎncă nu există evaluări

- IRF730Document12 paginiIRF730Aandk NovaÎncă nu există evaluări

- 9N80 UnisonicTechnologiesDocument6 pagini9N80 UnisonicTechnologiesJlavieraÎncă nu există evaluări

- Irf6775mpbf PDFDocument10 paginiIrf6775mpbf PDFMárcio FerreiraÎncă nu există evaluări

- PMCC VCO11G Datasheet Rev 2.4Document3 paginiPMCC VCO11G Datasheet Rev 2.4GbarbarÎncă nu există evaluări

- Unisonic Technologies Co., LTD: 15A, 600V N-CHANNEL Power MosfetDocument6 paginiUnisonic Technologies Co., LTD: 15A, 600V N-CHANNEL Power MosfetCode Main ProjectÎncă nu există evaluări

- 161 5 003187 FDD6685Document6 pagini161 5 003187 FDD6685Marcos Paulo FariaÎncă nu există evaluări

- AC-DC LED Driver MT7930Document8 paginiAC-DC LED Driver MT7930Daniel GonzálezÎncă nu există evaluări

- Unisonic Technologies Co., LTD: 10 Amps, 600/650 Volts N-Channel Power MosfetDocument9 paginiUnisonic Technologies Co., LTD: 10 Amps, 600/650 Volts N-Channel Power MosfetEmmanuel ZambranoÎncă nu există evaluări

- 40GBASE-ZR4 QSFP+ 1310nm 80km DDM SMF Transceiver P/N: QT-QSFP+-ZR4Document12 pagini40GBASE-ZR4 QSFP+ 1310nm 80km DDM SMF Transceiver P/N: QT-QSFP+-ZR4Utel TVÎncă nu există evaluări

- KA2S0680B: Fairchild Power Switch (SPS)Document12 paginiKA2S0680B: Fairchild Power Switch (SPS)henriquegonferÎncă nu există evaluări

- STW 34 NM 60 NDocument12 paginiSTW 34 NM 60 NSujit KumarÎncă nu există evaluări

- Data Sheet Irs 40n03Document4 paginiData Sheet Irs 40n03Omar GuzmanÎncă nu există evaluări

- Stp9Nk65Z Stp9Nk65Zfp: N-Channel 650 V, 1 Ω, 6.4 A, To-220, To-220Fp Zener-Protected Supermesh™ Power MosfetDocument16 paginiStp9Nk65Z Stp9Nk65Zfp: N-Channel 650 V, 1 Ω, 6.4 A, To-220, To-220Fp Zener-Protected Supermesh™ Power MosfetAndyMahataraÎncă nu există evaluări

- 6n60a PDFDocument8 pagini6n60a PDFRoy AnaÎncă nu există evaluări

- LinearPS DesignExamplesDocument6 paginiLinearPS DesignExamplesRagnar RagnarsonÎncă nu există evaluări

- Stn3Nf06L: N-Channel 60 V, 0.07 Ω Typ., 4 A Stripfet™ Ii Power Mosfet In A Sot-223 PackageDocument12 paginiStn3Nf06L: N-Channel 60 V, 0.07 Ω Typ., 4 A Stripfet™ Ii Power Mosfet In A Sot-223 Packageramesh sahukhalÎncă nu există evaluări

- FQD4P40 D 1809499Document9 paginiFQD4P40 D 1809499SaanounÎncă nu există evaluări

- P5NK90ZDocument12 paginiP5NK90ZsrikrishÎncă nu există evaluări

- Tda 1579Document13 paginiTda 1579nooneezÎncă nu există evaluări

- Unisonic Technologies Co., LTD: 10A, 650V N-CHANNEL Power MosfetDocument6 paginiUnisonic Technologies Co., LTD: 10A, 650V N-CHANNEL Power MosfetJhonson Shut DownÎncă nu există evaluări

- Stw20Nk50Z: N-Channel 500 V, 0.23 Ω, 20 A Supermesh™ Power Mosfet Zener-Protected In To-247 PackageDocument12 paginiStw20Nk50Z: N-Channel 500 V, 0.23 Ω, 20 A Supermesh™ Power Mosfet Zener-Protected In To-247 PackagemonikaÎncă nu există evaluări

- 374067a 05Document1 pagină374067a 05Antonio HerreraÎncă nu există evaluări

- Ups EatonDocument2 paginiUps EatonAntonio HerreraÎncă nu există evaluări

- NI cRIO-9066 - 376186a - 02Document8 paginiNI cRIO-9066 - 376186a - 02angeljchrÎncă nu există evaluări

- 374067a 05Document1 pagină374067a 05Antonio HerreraÎncă nu există evaluări

- Power RequirementsDocument1 paginăPower RequirementsAntonio HerreraÎncă nu există evaluări

- 374067a 05Document1 pagină374067a 05Antonio HerreraÎncă nu există evaluări

- +2.7 V To +5.5 V, 350 KSPS, 10-Bit 4-/8-Channel Sampling AdcsDocument1 pagină+2.7 V To +5.5 V, 350 KSPS, 10-Bit 4-/8-Channel Sampling AdcsAntonio HerreraÎncă nu există evaluări

- AD7812YNPAG2Document2 paginiAD7812YNPAG2Antonio HerreraÎncă nu există evaluări

- NI 9265 Specifications: Output CharacteristicsDocument1 paginăNI 9265 Specifications: Output CharacteristicsAntonio HerreraÎncă nu există evaluări

- Accuracy Measurement Conditions Percent of Reading (Gain Error) Percent of Range (Offset Error)Document2 paginiAccuracy Measurement Conditions Percent of Reading (Gain Error) Percent of Range (Offset Error)Antonio HerreraÎncă nu există evaluări

- Ni CRIO-9063 DatasheetDocument17 paginiNi CRIO-9063 DatasheetAntonio HerreraÎncă nu există evaluări

- Circuitry: Ni Labview Fpga ModuleDocument1 paginăCircuitry: Ni Labview Fpga ModuleAntonio HerreraÎncă nu există evaluări

- AD7812YNPAG2Document1 paginăAD7812YNPAG2Antonio HerreraÎncă nu există evaluări

- NI C Series Overview: DatasheetDocument11 paginiNI C Series Overview: DatasheetAntonio HerreraÎncă nu există evaluări

- Acti 9 Iem3000 - Metsect5cc008Document2 paginiActi 9 Iem3000 - Metsect5cc008Antonio HerreraÎncă nu există evaluări

- 1851 E Solar Module Simulation Model 3-Fold 23V 2ADocument1 pagină1851 E Solar Module Simulation Model 3-Fold 23V 2AAntonio HerreraÎncă nu există evaluări

- Ni Usb 6008 375295bDocument12 paginiNi Usb 6008 375295bAntonio HerreraÎncă nu există evaluări

- 5690 E EPH 2 3 Design of Photovoltaic Systems For Grid-Parallel Operation ShortDocument6 pagini5690 E EPH 2 3 Design of Photovoltaic Systems For Grid-Parallel Operation ShortAntonio HerreraÎncă nu există evaluări

- XBTZN999 DatasheetDocument1 paginăXBTZN999 DatasheetAntonio HerreraÎncă nu există evaluări

- Ni 9923 Conector 37pinDocument8 paginiNi 9923 Conector 37pinAntonio HerreraÎncă nu există evaluări

- Ni Crio User ManualDocument26 paginiNi Crio User ManualAntonio HerreraÎncă nu există evaluări

- Ni 9265 ds-220Document10 paginiNi 9265 ds-220Antonio HerreraÎncă nu există evaluări

- PowerLogic PM5000 Series - METSEPM5330Document3 paginiPowerLogic PM5000 Series - METSEPM5330Antonio HerreraÎncă nu există evaluări

- NI9265 DatasheetDocument14 paginiNI9265 DatasheetAntonio HerreraÎncă nu există evaluări

- NI cRIO-9066 - 376186a - 02Document8 paginiNI cRIO-9066 - 376186a - 02angeljchrÎncă nu există evaluări

- AI 374070a 02Document10 paginiAI 374070a 02Antonio HerreraÎncă nu există evaluări

- NI PS 15 372911bDocument49 paginiNI PS 15 372911bAntonio HerreraÎncă nu există evaluări

- NI cRIO-9066 - 376186a - 02Document8 paginiNI cRIO-9066 - 376186a - 02angeljchrÎncă nu există evaluări

- Decision-Making Under Risk and Uncertainty: OutcomesDocument21 paginiDecision-Making Under Risk and Uncertainty: OutcomesprabodhÎncă nu există evaluări

- 7625-300 Vitamin B12 AccuBind ELISA Rev 6Document2 pagini7625-300 Vitamin B12 AccuBind ELISA Rev 6carlosalfredorivasÎncă nu există evaluări

- PPF CalculatorDocument2 paginiPPF CalculatorshashanamouliÎncă nu există evaluări

- Finches Statistics Student-1Document7 paginiFinches Statistics Student-1api-319172404Încă nu există evaluări

- P 130881757895329843Document44 paginiP 130881757895329843Vijay MohanÎncă nu există evaluări

- Analysis and Design of Telecommunication Tower Using Different Truss System by ETab SoftwareDocument12 paginiAnalysis and Design of Telecommunication Tower Using Different Truss System by ETab SoftwareEditor IJTSRDÎncă nu există evaluări

- Highway Design ProjectDocument70 paginiHighway Design ProjectmuhammedÎncă nu există evaluări

- Week 1 Lesson 1 2nd QuarterDocument2 paginiWeek 1 Lesson 1 2nd QuarterKristine Jewel MacatiagÎncă nu există evaluări

- Solved - Which $1,000 Bond Has The Higher Yield To Maturity, A T...Document4 paginiSolved - Which $1,000 Bond Has The Higher Yield To Maturity, A T...Sanjna ChimnaniÎncă nu există evaluări

- Sentinel Visualizer 6 User GuideDocument227 paginiSentinel Visualizer 6 User GuideTaniaÎncă nu există evaluări

- V. Activities: A. Directions: Do The Activity Below. (20 PTS.) Note: Work On This OfflineDocument7 paginiV. Activities: A. Directions: Do The Activity Below. (20 PTS.) Note: Work On This OfflineKeith Neomi CruzÎncă nu există evaluări

- ElutriatorDocument9 paginiElutriatoratiyorockfan9017Încă nu există evaluări

- PDC NitDocument6 paginiPDC NitrpshvjuÎncă nu există evaluări

- VT300 User ManualDocument21 paginiVT300 User ManualLuvÎncă nu există evaluări

- Iot Lab RecordDocument33 paginiIot Lab RecordMadhavan Jayarama MohanÎncă nu există evaluări

- Packages in JavaDocument4 paginiPackages in JavaKummeta KeerthiÎncă nu există evaluări

- Solutionbank D1: Edexcel AS and A Level Modular MathematicsDocument30 paginiSolutionbank D1: Edexcel AS and A Level Modular MathematicsMaruf_007Încă nu există evaluări

- Atmel 2565 Using The Twi Module As I2c Slave - Applicationnote - Avr311Document14 paginiAtmel 2565 Using The Twi Module As I2c Slave - Applicationnote - Avr311m3y54mÎncă nu există evaluări

- Residual Alkalinity Nomograph by John Palmer PDFDocument1 paginăResidual Alkalinity Nomograph by John Palmer PDFcarlos pablo pableteÎncă nu există evaluări

- Fundamentals Writing Prompts: TechnicalDocument25 paginiFundamentals Writing Prompts: TechnicalFjvhjvgÎncă nu există evaluări

- Biztalk and Oracle IntegrationDocument2 paginiBiztalk and Oracle IntegrationkaushiksinÎncă nu există evaluări

- VFS1000 6000Document126 paginiVFS1000 6000krisornÎncă nu există evaluări

- Ss e (Bocr) ManualDocument2 paginiSs e (Bocr) ManualNaveen GuptaÎncă nu există evaluări

- X-Plane Mobile ManualDocument66 paginiX-Plane Mobile ManualRafael MunizÎncă nu există evaluări