Documente Academic

Documente Profesional

Documente Cultură

FFT Analysis & Physical Design of Multibit Adders using 3.0 μm SCMOS

Încărcat de

IJRT OnlineDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

FFT Analysis & Physical Design of Multibit Adders using 3.0 μm SCMOS

Încărcat de

IJRT OnlineDrepturi de autor:

Formate disponibile

INTERNATIONAL JOURNAL OF RESEARCH IN TECHNOLOGY (IJRT) ISSN No.

2394-9007

Vol. V, No. III, June 2018 www.ijrtonline.org

FFT Analysis & Physical Design of Multibit Adders

using 3.0 µm SCMOS

Farhan Siddiqui, Ayoush Johari

Abstract— A method illustrated in this is to design carry look II. FULL ADDER

ahead adders using SCMOS technology, also analyzed the effect

of various parameters on the characteristics of adders, using 50

A Full adder is a logical circuit that performs an addition

nm, spice model for SCMOS technology. The design was operation on three one bit binary numbers. The Full Adder

implemented for 16 bit and then extended for multibit bit also. produces a sum of the two inputs and carries value. It can be

Here parameters are computed and response curves are combined with other full adders or work on its own. Full

computed between all characteristics, DC and transient adders are one of the most fundamental building block for

characteristics. The design and simulations are carried out to circuit applications, remain a key focus domain of the

achieve these values approximately. Design will be carried out in researchers over the years. Different logic styles, each having

Electric CAD and LTSPICE. Simulation results are verified its own merits and bottlenecks, was investigated to implement

using LTSpice. The Design rule check DRC, LVS Layout vs

reliable, simpler with less power requirement but the on chip

Schematic and Network Consistency Checks, transient checks

are performed in the presented design of multibit adders. In

area requirement is usually larger compared with its dynamic

comparison with the existing full adder designs, the present counterpart. These designs exploit the features of different

implementation will offer significant improvement in terms of logic styles to improve the overall performance of the full

frequency and noise as verified by FFT analysis for the same. adder. There are two types of full adders in case of logic

Keywords: Full adder, SCMOS Circuit, 0.3 um C5 Process, Carry structure. One is static and the other is dynamic style. Static

look ahead adder circuits, Transient analysis, FFT Analysis. full adders are commonly more reliable, simpler and are lower

power consuming than dynamic ones. Dynamic is an

I. INTRODUCTION alternative logic style to design a logic function. It has some

An adder is a combinational digital circuit which performs advantages over the static mode such as faster switching

addition of number. In many computers and other processors speeds, no static power consumption, nonrated logic, full

adders are used in arithmetic logic units and other parts of swing voltage levels, and lesser number of transistors. An N

processors where they are used to calculate addresses, input logic function requires N+2 transistors versus 2N

increment and decrement operators, and table indices. They transistors in the standard CMOS logic.

can also be constructed for many numerical representations

such as binary coded decimal or excess-3, the most common

adders operate on binary numbers. In case where two’s

complement or one’s complement is being used to represent

negative number. Adders are the elemental units in various

electronic circuits especially in circuits used for performing

arithmetic operations. An optimized is needed to avoid any

degradation at the circuit level in the output voltage, less delay

in critical path, and consume less power.

Manuscript received on June, 2018.

Farhan Siddiqui, Research Scholar, Department of Electronics &

Communication Engineering, Lakshmi Narain College of Technology &

Science, Bhopal, M.P., India.

Prof. Ayoush Johari, Professor, Department of Electronics &

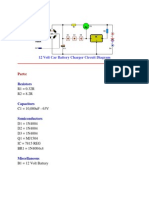

Communication Engineering, Lakshmi Narain College of Technology & Fig. 1: Full Adder Cell

Science, Bhopal, M.P., India.

Impact Factor: 4.012 33

Published under

Asian Research & Training Publication

ISO 9001:2015 Certified

INTERNATIONAL JOURNAL OF RESEARCH IN TECHNOLOGY (IJRT) ISSN No. 2394-9007

Vol. V, No. III, June 2018 www.ijrtonline.org

Many full adder cells designed with the help of static logic

style in 180 nm CMOS technology. One is the Pseudo-nMOS

Full Adder and other is the Conventional CMOS Full Adder.

The Pseudo-nMOS Full Adder cell is worked by Pseudo-

nMOS logic or radioed logic. The CMOS pull up network is

substituted by a single pMOS transistor with its gate

grounded. The pMOS is always ‘on’ because it is not driven

by signals. Vdd is the effective gate voltage seen by the pMOS

transistor. When the nMOS is turned ‘on’, static power will be

drawn in the transistor because direct path between supply and

ground exists. It uses 18 transistors to make a single full adder

circuit. The operation is executed by negative addition. The

advantages of using Pseudo-nMOS logic is that it gives less

number of transistors than CCMOS with high speed

performance and disadvantage is that it is more susceptible to

noise, has increased power consumption of pull up transistor

and reduced output swing. The Conventional CMOS Full

Adder is based on regular CMOS structures known as pull-up

and pull-down networks but it uses 28 transistor.

Complementary transistor pairs construct the circuit layout to

be very straight forward. It generates carry through a static

gate. The advantage of using CCMOS is that it has stability at

low voltage due to complementary transistor pair, layout

regularity, high noise margins and smaller number of

interconnecting wires. The disadvantage is that it produces an

unwanted additional delay, has weak output driving capability

due to series transistors in output stage, requires large silicon

area and consumes more power.

Fig. 4: Schematic design for 4 bit parallel adder

Fig. 2: Block diagram of Carry Look ahead adder

III. DESIGN RESULT

Fig. 3: 10 FFT plots for sum signals in 4 bit ADDER Fig. 5: Schematic design for 16 bit parallel adder

Impact Factor: 4.012 34

Published under

Asian Research & Training Publication

ISO 9001:2015 Certified

INTERNATIONAL JOURNAL OF RESEARCH IN TECHNOLOGY (IJRT) ISSN No. 2394-9007

Vol. V, No. III, June 2018 www.ijrtonline.org

Fig. 6: Transient analysis plot for Carryout Fig. 9: FFT plots or Noise index plot for Sum Signals in 16 bit Adder

design

IV. FFT PLOTS COMPARISON BETWEEN 4 BIT & 16 BIT

ADDERS

The performance analysis of adders 4 bits and 16 bits in erms

of their FFT profile is shown in above section and tabulation

and comparison of FFT and transient parameters is illustrated

here and drawn in table- 1, shows different,. thus, there exist

tradeoff between these parameters. the results are helpful in

selection of an adder according to desired result and

application.

TABLE I: FFT INDEX RESULTS FOR 4 BIT ADDER (SUM SIGNALS)

Fig. 7: Transient analysis plot for propagate and generate signals in 16 bit

ADDER

Fig. 8: Transient plot for Sum signals in 4 bit Adder

Impact Factor: 4.012 35

Published under

Asian Research & Training Publication

ISO 9001:2015 Certified

INTERNATIONAL JOURNAL OF RESEARCH IN TECHNOLOGY (IJRT) ISSN No. 2394-9007

Vol. V, No. III, June 2018 www.ijrtonline.org

TABLE II: FFT INDEX RESULTS FOR 16 BIT ADDER (SUM

SIGNALS) 100MHz 110.07 dB 58.34 ps

1THz 204.57 dB 186.18 ps

FFT plot parameters for signal S12

Frequency Magnitude Delay

13. 100MHz 117.51 dB 5.081 ns

1THz 176.16 dB 3.17 ns

FFT plot parameters for signal S13

FFT plot parameters for signal S2 14. Frequency Magnitude Delay

3. Frequency Magnitude Delay 100MHz 167.68 dB 56.266 ps

100MHz 6.89 dB 4.59 ns

1THz 132.36 dB 2.47 ns 1THz 216.44 dB 3.08 ns

FFT plot parameters for signal S3

4. Frequency Magnitude Delay FFT plot parameters for signal S14

100MHz 7.025 dB 555.40ps

1THz 135.157 dB 1.55 ns 15. Frequency Magnitude Delay

FFT plot parameters for signal S4

100MHz 189.96 dB 5.09 ns

Frequency Magnitude Delay

5. 100MHz 150.10 148.89 ps

1THz 186.049 dB 1.89 ns 1THz 213.35 dB 2.73 ns

FFT plot parameters for signal S5

6. Frequency Magnitude Delay FFT plot parameters for signal S15

100MHz 184.98 dB 101.89 ps 16. Frequency Magnitude Delay

1THz 149.19 dB 346.01 ps

FFT plot parameters for signal S6 100MHz 122.05 dB 76.21 ps

7. Frequency Magnitude Delay

100MHz 149.27 dB 6.05 ns 1THz 218.46 dB 1.01 ns

1THz 203.24 dB 3.26 ns

FFT plot parameters for signal S7

V. CONCLUSION

8. Frequency Magnitude Delay

100MHz 138.17 dB 5.04 ns Keeping in view different applications the multibit parallel

1THz 218.60 dB 153.78 ps adder design has been done. For this first a selection is made

FFT plot parameters for signal S8 for the active device used. The development of a design

Frequency Magnitude Delay procedure provides a quick, well integrated and effective

9. 100MHz 162.83 dB 76.49 ps mechanism for estimation and calculation of various

1THz 185.61 dB 3.88 ns parameters. The steps highlighted make it easy to redesign the

FFT plot parameters for signal S9 circuit for various set of specifications. The responses are

simulated using LTSpice and Electric VLSI CAD design tool.

10. Frequency Magnitude Delay

100MHz 188.09 dB 15.09 ns The simulated results of the multibit adders will be in

1THz 197.16 dB 12.77 ns compliance with the theoretical values. The responses are

simulated using LTSpice and Electric VLSI CAD design tool.

FFT plot parameters for signal S10

11. Frequency Magnitude Delay REFERENCES

100MHz 124.05 dB 4.63 ns

1 Bhattacharyya, Partha, Bijoy Kundu, Sovan Ghosh, Vinay Kumar, and

1THz 159.97 dB 3.99 ns Anup Dandapat. "Performance analysis of a low-power high-speed

hybrid 1-bit full adder circuit." IEEE Transactions on very large scale

integration (VLSI) systems 23, no. 10 (2015): 2001-2008.

FFT plot parameters for signal S11

2. Han, Liu, Hao Zhang, and Seok-Bum Ko. "Area and power efficient

12. Frequency Magnitude Delay decimal carry-free adder." Electronics Letters 51.23 (2015): 1852-1854.

Impact Factor: 4.012 36

Published under

Asian Research & Training Publication

ISO 9001:2015 Certified

INTERNATIONAL JOURNAL OF RESEARCH IN TECHNOLOGY (IJRT) ISSN No. 2394-9007

Vol. V, No. III, June 2018 www.ijrtonline.org

3. Mohanty, Basant Kumar, and Sujit Kumar Patel. "Area-Delay–Power a carry-free signed-digit decimal adder." 2007 IEEE International

efficient carry-select adder." IEEE Transactions on Circuits and Systems Symposium on Circuits and Systems. IEEE, 2007.

II: Express Briefs 61.6 (2014): 418-422.

21. Alioto, Massimo, Giuseppe Di Cataldo, and Gaetano Palumbo. "Mixed

4. Pan, Yu, and Pramod Kumar Meher. "Bit-level optimization of adder- Full Adder topologies for high-performance low-power arithmetic

trees for multiple constant multiplications for efficient FIR filter circuits." Microelectronics Journal 38.1 (2007): 130-139.

implementation." IEEE Transactions on Circuits and Systems I: Regular

Papers 61.2 (2014): 455-462. 22. Goel, Sumeer, Ashok Kumar, and Magdy A. Bayoumi. "Design of

robust, energy-efficient full adders for deep-submicrometer design using

5. Manju, S., and V. Sornagopal. "An efficient SQRT architecture of carry hybrid-CMOS logic style." IEEE Transactions on Very Large Scale

select adder design by common Boolean logic." Emerging Trends in Integration (VLSI) Systems 14.12 (2006): 1309-1321.

VLSI, Embedded System, Nano Electronics and Telecommunication

System (ICEVENT), 2013 International Conference on. IEEE, 2013. 23. HE, Weste Neil. Cmos Vlsi Design: A Circuits And Systems

Perspective, 3/E. Pearson Education India, 2006.

6. Ramkumar, B., and Harish M. Kittur. "Low-power and area-efficient

carry select adder." IEEE transactions on very large scale integration 24. Chang, Chip-Hong, Jiangmin Gu, and Mingyan Zhang. "A review of

(VLSI) systems 20.2 (2012): 371-375. 0.18-/spl mu/m full adder performances for tree structured arithmetic

circuits." IEEE Transactions on very large scale integration (VLSI)

7. Wey, I-Chyn, et al. "An area-efficient carry select adder design by systems 13.6 (2005): 686- 695.

sharing the common Boolean logic term." Proceedings on the

25. Nikmehr, Hooman, Braden Phillips, and Cheng-Chew Lim. "A decimal

International Multiconference of Engineering and computer scientist,

carry-free adder." Smart Materials, Nano-, and Micro-Smart Systems.

IMECS. 2012.

International Society for Optics and Photonics, 2005.

8. Prashanth, P., and Prabhu Swamy. "Architecture of adders based on

26. Zhang, Mingyan, Jiangmin Gu, and Chip-Hong Chang. "A novel hybrid

speed, area and power dissipation." Information and Communication

pass logic with static CMOS output drive full-adder cell." Circuits and

Technologies (WICT), 2011 World Congress on. IEEE, 2011.

Systems, 2003. ISCAS'03. Proceedings of the 2003 International

9. Zavarei, Mohammad Javad, et al. "Design of new full adder cell using Symposium on. Vol. 5, IEEE, 2003.

hybrid-CMOS logic style." Electronics, Circuits and Systems (ICECS),

2011 18th IEEE International Conference on. IEEE, 2011. 26. Goel, Sumeer, Mohamed A. Elgamel, and Magdy A. Bayoumi. "Novel

design methodology for high-performance XOR-XNOR circuit design."

10. Aguirre-Hernandez, Mariano, and Monico Linares-Aranda. "CMOS full- Integrated Circuits and Systems Design, 2003. SBCCI 2003.

adders for energy-efficient arithmetic applications." IEEE transactions Proceedings. 16th Symposium on. IEEE, 2003.

on very large scale integration (VLSI) systems 19.4 (2011): 718-721.

27. Rabaey, J. M., A. Chandrakasan, and B. Nikolic. "Digital Integrated

11. Han, Liu, et al. "Nonspeculative decimal signed digit adder." 2011 IEEE Circuits, A Design Perspective, 2nd Prentice Hall." Englewood Cliffs,

International Symposium of Circuits and Systems (ISCAS). IEEE, 2011. NJ (2002).

12. Wairya, Subodh, et al. "Design analysis of XOR (4T) based low voltage 28. Shams, Ahmed M., Tarek K. Darwish, and Magdy A. Bayoumi.

CMOS full adder circuit." 2011 Nirma University International "Performance analysis of low-power 1-bit CMOS full adder cells." IEEE

Conference on Engineering. IEEE, 2011. Transactions on Very Large Scale Integration (VLSI) Systems 10.1

13. Aranda, Monico Linares, Ramon Báez, and Oscar Gonzalez Diaz. (2002): 20-29.

"Hybrid adders for high-speed arithmetic circuits: A comparison." 29. Bui, Hung Tien, Yuke Wang, and Yingtao Jiang. "Design and analysis

Electrical Engineering Computing Science and Automatic Control of low-power 10-transistor full adders using novel XOR-XNOR gates."

(CCE), 2010 7th International Conference on. IEEE, 2010. IEEE Transactions on Circuits and Systems II: Analog and Digital

Signal Processing 49.1 (2002): 25-30.

15. Hassoune, Ilham, et al. "ULPFA: a new efficient design of a power-

aware full adder." IEEE Transactions on Circuits and Systems I: 30. Kim, Youngjoon, and Lee-Sup Kim. "64-bit carry-select adder with

Regular Papers 57.8 (2010): 2066-2074. reduced area." Electronics Letters 37.10 (2001): 1.+ Radhakrishnan, D.

"Low-voltage low-power CMOS full adder." IEE Proceedings-Circuits,

16. Navi, Keivan, et al. "A novel low-power full-adder cell with new

technique in designing logical gates based on static CMOS inverter." Devices and Systems 148.1 (2001): 19-24.

Microelectronics Journal 40.10 (2009): 1441-1448. 31. Vesterbacka, Mark. "A 14-transistor CMOS full adder with full voltage-

17. Jaberipur, Ghassem, and Saeid Gorgin. "A nonspeculative maximally swing nodes." Signal Processing Systems, 1999. SiPS 99. 1999 IEEE

Workshop on. IEEE, 1999.

redundant signed digit adder." Advances in Computer Science and

Engineering. Springer Berlin Heidelberg, 2008. 235-242. 32. Wang, Jyh-Ming, Sung-Chuan Fang, and Wu-Shiung Feng. "New

efficient designs for XOR and XNOR functions on the transistor level."

18. Chandrakasan, Anantha P., Naveen Verma, and Denis C. Daly. IEEE Journal of solid-state Circuits 29.7 (1994): 780-786.

"Ultralow-power electronics for biomedical applications." Biomedical

Engineering 10 (2008).

19. Tung, Chiou-Kou, et al. "A low-power high-speed hybrid CMOS full

adder for embedded system." 2007 IEEE Design and Diagnostics of

Electronic Circuits and Systems. IEEE, 2007.

20. Moskal, John, Erdal Oruklu, and Jafar Saniie. "Design and synthesis of

Impact Factor: 4.012 37

Published under

Asian Research & Training Publication

ISO 9001:2015 Certified

S-ar putea să vă placă și

- Q-Deformation in Logistic MapDocument4 paginiQ-Deformation in Logistic MapIJRT OnlineÎncă nu există evaluări

- An Experimental Study On Strength of Concrete Using Tyre Rubber & Replacing Aggregates of Different Percentage With Tyre RubberDocument3 paginiAn Experimental Study On Strength of Concrete Using Tyre Rubber & Replacing Aggregates of Different Percentage With Tyre RubberIJRT OnlineÎncă nu există evaluări

- IOT Based Parking SystemDocument3 paginiIOT Based Parking SystemIJRT OnlineÎncă nu există evaluări

- Study of Utilization of Neutralized Red Mud For Improvement of Concrete StrengthDocument5 paginiStudy of Utilization of Neutralized Red Mud For Improvement of Concrete StrengthIJRT OnlineÎncă nu există evaluări

- AOMDV-RC Routing Protocol With Secure & Trust Based For Mobile Ad-Hoc NetworkDocument2 paginiAOMDV-RC Routing Protocol With Secure & Trust Based For Mobile Ad-Hoc NetworkIJRT OnlineÎncă nu există evaluări

- Review Paper On Call Admission Control With Bandwidth Reservation Schemes in Wireless Communication SystemDocument4 paginiReview Paper On Call Admission Control With Bandwidth Reservation Schemes in Wireless Communication SystemIJRT OnlineÎncă nu există evaluări

- Review On Hybrid LUT/Multiplexer Combinational Logic Block ArchitectureDocument3 paginiReview On Hybrid LUT/Multiplexer Combinational Logic Block ArchitectureIJRT OnlineÎncă nu există evaluări

- Extraction, Isolation and Characterization of Natural Dye From Kathanda (Tabernaemontanum Divericata) and Vaola (Mangifera Macrophylla)Document4 paginiExtraction, Isolation and Characterization of Natural Dye From Kathanda (Tabernaemontanum Divericata) and Vaola (Mangifera Macrophylla)IJRT OnlineÎncă nu există evaluări

- Adaptive Channel Estimation Technique in MIMO-OFDM System For Wireless Communication SystemDocument4 paginiAdaptive Channel Estimation Technique in MIMO-OFDM System For Wireless Communication SystemIJRT OnlineÎncă nu există evaluări

- Design and Simulation of Digital Phase Locked Loop Using MOSFET SPICE Models of 300nmDocument4 paginiDesign and Simulation of Digital Phase Locked Loop Using MOSFET SPICE Models of 300nmIJRT OnlineÎncă nu există evaluări

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (895)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (588)

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (400)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (345)

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (74)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2259)

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (121)

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)

- How To Interface I2C-EEPROM With LPC2148 - ARM7 SlickerDocument8 paginiHow To Interface I2C-EEPROM With LPC2148 - ARM7 SlickerabidparwezÎncă nu există evaluări

- LD Lab 2Document6 paginiLD Lab 2Nicoll Méndez ChicaÎncă nu există evaluări

- Allen and Holberg Homework SolutionDocument121 paginiAllen and Holberg Homework SolutionNihit Varshney100% (1)

- Lab9 - Counters, Timers, and Real-Time ClockDocument6 paginiLab9 - Counters, Timers, and Real-Time Clockwert1a2Încă nu există evaluări

- 12 Volt Charger Circuit DiagramDocument1 pagină12 Volt Charger Circuit DiagramSarah RossÎncă nu există evaluări

- Chap 06 HMWK SolDocument72 paginiChap 06 HMWK Solapi-3841575Încă nu există evaluări

- S Feature D Escriptio: LTC1163/LTC1165 Triple 1.8V To 6V High-Side MOSFET DriversDocument8 paginiS Feature D Escriptio: LTC1163/LTC1165 Triple 1.8V To 6V High-Side MOSFET DriversPablo LloveraÎncă nu există evaluări

- Lecture 12 Binary Adder-SubtractorDocument8 paginiLecture 12 Binary Adder-SubtractorSasi Kiran SÎncă nu există evaluări

- Counters Using D FlipflopsDocument13 paginiCounters Using D FlipflopsMostafa ElngarÎncă nu există evaluări

- Fault Tolerant Feedback Shift RegisterDocument7 paginiFault Tolerant Feedback Shift RegisterVasanth BhaskarÎncă nu există evaluări

- Diode ModelsDocument10 paginiDiode ModelsTeferi LemmaÎncă nu există evaluări

- Frank Vahid - Tony Givargis - Embedded System DesignDocument174 paginiFrank Vahid - Tony Givargis - Embedded System DesignSambasiva100% (2)

- Chain of InverterDocument23 paginiChain of InverterRavi RajanÎncă nu există evaluări

- Bistable Mono StableDocument30 paginiBistable Mono StableTurkish GatxyÎncă nu există evaluări

- Ed2 Assignment - 7segmentDocument7 paginiEd2 Assignment - 7segmentdinÎncă nu există evaluări

- Combinational Circuits: ALU: AND OR ADD SUB SLT Zero (A B)Document16 paginiCombinational Circuits: ALU: AND OR ADD SUB SLT Zero (A B)anbaneÎncă nu există evaluări

- Introduction To The Design of Analogs by Allen and HollbergDocument14 paginiIntroduction To The Design of Analogs by Allen and HollbergKiran KirruÎncă nu există evaluări

- 2-1-Registers and Register Files - Interconnection of components-04-Aug-2021Material - I - 04-Aug-2021 - RegistersandDocument12 pagini2-1-Registers and Register Files - Interconnection of components-04-Aug-2021Material - I - 04-Aug-2021 - RegistersandGoutam GoyalÎncă nu există evaluări

- Pucknell Vlsi Design PDF - CompressDocument2 paginiPucknell Vlsi Design PDF - CompressKotresh HothurÎncă nu există evaluări

- 24AA128/24LC128/24FC128: 128K I C Serial EEPROMDocument44 pagini24AA128/24LC128/24FC128: 128K I C Serial EEPROMJosemar M. FerreiraÎncă nu există evaluări

- Scope and Objective of The CourseDocument3 paginiScope and Objective of The CourseK.KARTHIKEYAN IYERÎncă nu există evaluări

- Millman Halkias - Integrated ElectronicsDocument28 paginiMillman Halkias - Integrated ElectronicsPranav SinhaÎncă nu există evaluări

- Trescientos Uno Flanger: Resistors Trim Pots Parts ListDocument1 paginăTrescientos Uno Flanger: Resistors Trim Pots Parts ListJefersonMatosdeColaresÎncă nu există evaluări

- 2020 12 Concept of Timing AnalysisDocument28 pagini2020 12 Concept of Timing AnalysisJecsÎncă nu există evaluări

- DD Module-2 Part-2 (Comparator, Encoder, Decoder, Mux)Document43 paginiDD Module-2 Part-2 (Comparator, Encoder, Decoder, Mux)Aneal SinghÎncă nu există evaluări

- GAL22V10Document21 paginiGAL22V10jackkairiÎncă nu există evaluări

- CSD Open Ended Last PID Exp Proteus KeilDocument4 paginiCSD Open Ended Last PID Exp Proteus Keilpnaik048711Încă nu există evaluări

- UC5895Document8 paginiUC5895aniÎncă nu există evaluări

- RF PIC12 F675 K, 675 F, 675 HDocument137 paginiRF PIC12 F675 K, 675 F, 675 HcartobonÎncă nu există evaluări

- Performance Analysis of A Low-Power High-Speed Hybrid 1-Bit Full Adder CircuitDocument8 paginiPerformance Analysis of A Low-Power High-Speed Hybrid 1-Bit Full Adder CircuitSandeep MishraÎncă nu există evaluări