Documente Academic

Documente Profesional

Documente Cultură

Analog Manual

Încărcat de

Rushabh PatelDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Analog Manual

Încărcat de

Rushabh PatelDrepturi de autor:

Formate disponibile

Analog Electronics

EXPERIMENT: 1 DATE: __/__/__

AIM: To configure op-amp as an inverting and non-inverting amplifier in open

Loop Configuration. Observe their output and draw waveform.

APPARTUS:

IC 741, Bread board, CRO, Function Generator, Resistors, Connecting wires, CRO,

CRO Probes, Multimeter, etc.

CIRCUIT DIAGRAM:

INVERTING AMPLIFIER

NON-INVERTING AMPLIFIER

SSASIT, SURAT EC DEPARTMENT Page 1

Analog Electronics

PROCEDURE:

INVERTING AMPLIFIER

1. Connect output of the Function generator at the input terminal of the inverting

amplifier

2. Connect CRO at output terminal.

3. Set offset preset so that output voltage becomes merely zero.

4. Set input voltage 0.5Vp-p or you can take any value that output cannot reach at

saturation.

5. Vary frequency starting from 50 Hz to 1 MHz and measure output voltage.

NON-INVERTING AMPLIFIER

1. Connect output of the Function Generator at the input terminal of the non-inverting

amplifier.

2. Connect CRO at output terminal.

3. Set offset preset so that output voltage becomes merely zero.

4. Set input voltage 0.5Vp-p or you can take any value that output cannot reach at

saturation.

5. Vary frequency starting from 50 Hz to 1 MHz and measure output voltage.

CONCLUSION:

_______________________

Remark with Sign & Date

SSASIT, SURAT EC DEPARTMENT Page 2

Analog Electronics

EXPERIMENT: 2 DATE: __/__/__

AIM: To configure op-amp as an inverting and non-inverting amplifier mode and

measure their gain and bandwidth.

APPARTUS:

IC 741, Bread board, CRO, Function Generator, Resistors, Connecting wires, CRO,

CRO Probes, Multimeter, etc.

CIRCUIT DIAGRAM:

INVERTING AMPLIFIER

NON-INVERTING AMPLIFIER

SSASIT, SURAT EC DEPARTMENT Page 3

Analog Electronics

PROCEDURE:

INVERTING AMPLIFIER

6. Connect output of the Function generator at the input terminal of the inverting

amplifier

7. Connect CRO at output terminal.

8. Set offset preset so that output voltage becomes merely zero.

9. Keep feedback resistor switch to 10K position.

10. Set input voltage 0.5Vp-p or you can take any value that output cannot reach at

saturation.

11. Vary frequency starting from 50 Hz to 1 MHz and measure output voltage.

NON-INVERTING AMPLIFIER

6. Connect output of the Function Generator at the input terminal of the non-inverting

amplifier.

7. Connect CRO at output terminal.

8. Set offset preset so that output voltage becomes merely zero.

9. Keep feedback resistor switch to 10K position.

10. Set input voltage 0.5Vp-p or you can take any value that output cannot reach at

saturation.

11. Vary frequency starting from 50 Hz to 1 MHz and measure output voltage.

CONCLUSION:

_______________________

Remark with Sign & Date

SSASIT, SURAT EC DEPARTMENT Page 4

Analog Electronics

EXPERIMENT: 3 DATE: __/__/__

AIM: To design and implement summing, scaling and subtractor amplifier using

IC 741.

APPARTUS:

IC-741, bread board, power supply, function generator, resister, connecting wires,

CRO, CRO Probe, etc.

THEORY:

Summing amplifier

The summing amplifier is an application of the inverting op-amp configuration. The

summing amplifier has two or more inputs, and its output voltage is proportional to the

algebraic sum of its input voltages.

Subtractor or Differential amplifier

A differential amplifier is the combination of inverting and non inverting amplifier. A

differential amplifier is a type of electronic amplifier that amplifies the difference

between two input voltages but suppresses any voltage common to the two inputs.

SSASIT, SURAT EC DEPARTMENT Page 5

Analog Electronics

CIRCUIT DIAGRAM:

SSASIT, SURAT EC DEPARTMENT Page 6

Analog Electronics

PROCEDURE:

1. Connect the circuit as shown in circuit diagram.

2. Apply No. of inputs as per the requirement & obtain the output for Summing

Amplifier or for Differential Amplifier or for Subtractor.

3. Connect CRO at output terminal.

4. Measure the output voltage for particular amplifier.

CONCLUSION:

_______________________

Remark with Sign & Date

SSASIT, SURAT EC DEPARTMENT Page 7

Analog Electronics

EXPERIMENT: 4 DATE: __/__/__

AIM: To built transistor based RC phase shift oscillator circuit, and measure

and verify its frequency of operation.

APPARATUS: Bread Board, Electronics Component, Function Generator, C.R.O.,

Connecting wires.

CIRCUIT DIAGRAM:

THEORY:

Oscillator is defined as a circuit that generates an A.C output signal without requiring

any externally applied input signal. This is a sine wave oscillator in which feedback

network is R and C. They are used not only to provide feedback but also set the

frequency of oscillations. The circuit diagram of RC oscillator is as shown in fig. In this

circuit the basic amplifier provides 180 degree of phase shift, other phase shift that is

needed for positive feedback is provided by phase shift network consisting of three

identical RC sections. Thus each section provides a phase shift of 60 degree.

SSASIT, SURAT EC DEPARTMENT Page 8

Analog Electronics

PROCEDURE:

1) Connect 12 V DC regulated power supply to the terminals provided.

2) Connect one channel of C.R.O at the output terminals.

3) Switch on the supply.

4) Observe the output waveform on the C.R.O. Record the output frequency.

5) Observe the waveform at other terminals see the phase shift of 60, 120 and 180

degree.

OBSERVATIONS:

Output frequency (theoretical) = ______________

Output frequency (practically) = ______________

GRAPH:

Draw the graph of V- T phase shift

CONCLUSION:

_______________________

Remark with Sign & Date

SSASIT, SURAT EC DEPARTMENT Page 9

Analog Electronics

EXPERIMENT: 5 DATE: __/__/__

AIM: Measure the effect on Bandwidth and Gain of the amplifier with & without

Negative feedback network.

APPARATUS: Bread Board, Electronics Component, Function Generator, C.R.O.,

Connecting wires.

CIRCUIT DIAGRAM:

THEORY:

One of the most important advantages of negative feedback is that it increases the

bandwidth of the amplifier. For any amplifier the product of voltage gain and

bandwidth always remains constant.

Gain x Bandwidth = Constant

As with the negative feedback, gain reduces therefore to keep the value of the

product constant, bandwidth of the amplifier increases proportionally. So with

increases the bandwidth measure the gain

SSASIT, SURAT EC DEPARTMENT Page 10

Analog Electronics

PROCEDURE:

Without Feedback:

1) Negative feedback kit is available in Analog Electronics.

2) Do not connect the output to the input.

3) Connect the output and check the waveform on CRO for different values of

input frequency with fixed input.

4) Check the output voltage.

With Feedback:

1) Negative feedback kit is available in Analog Electronics

2) Connect the output to the input.

3) Connect the output and check the waveform on CRO for different values of

input frequency with fixed input

4) Check the output voltage.

OBSERVATIONS:

Applied Input Voltage Vi = _______________.

WITHOUT FEEDBACK WITH FEEDBACK

SR. APPLIED OUTPUT VOLTAGE GAIN OUTPUT VOLTAGE GAIN

NO. FREQUENCY fin VOLTAGE (20 log10 (V0/Vi)) VOLTAGE (20 log10 (V0/Vi))

(V0) dB (V0) dB

1

SSASIT, SURAT EC DEPARTMENT Page 11

Analog Electronics

10

11

12

13

14

15

16

17

18

19

CALCULATIONS:

CONCLUSION:

____________________

Remark with sign & date

SSASIT, SURAT EC DEPARTMENT Page 12

Analog Electronics

EXPERIMENT: 6 DATE: __/__/__

AIM: To design Precision Half Wave Rectifier using Op-amp and verify its

operation.

APPARTUS:

IC-741, bread board, power supply, function generator, resister, connecting wires,

CRO, CRO Probe, Diode etc.

THEORY:

Rectifier circuits are used in the design of power supply circuits. In such applications,

the voltage being rectified is usually much greater than the diode voltage drop,

rendering the exact value of the diode drop unimportant to the proper operation of the

rectifier.

Show in fig.1, the resultant circuit can rectify signals with peak values down to a few

mill volts, unlike conventional diodes. This is possible because the high open-loop gain

of the op-amp automatically adjust the voltage drive to the diode D1 so that the rectified

output peak is the same as the input.

In fact, the diode acts as an ideal diode, since the voltage drop across the on diode is

divided by the open loop gain of the op amp. As Vin starts increasing in the positive

direction, the V’0 also starts increasing positively until diode D1 is forward biased.

When D1 is biased, it closes a feedback loop and the op-amp works as a voltage

follower. Therefore the output voltage V’0 follows the input voltage Vin during the

positive half-cycle, as in fig.1. However, when Vin starts increasing in the negative

direction, V’0 also increases negatively until it is equal to the negative saturation voltage

(-VEE). This reverse biases diode D1 and opens the feedback loop. Therefore, during the

negative half-cycle of the input signal, V’0 is 0V

SSASIT, SURAT EC DEPARTMENT Page 13

Analog Electronics

Fig. 1 Positive small signal half wave rectifier and its input & output waveforms.

Fig.2 Negative small signal half wave rectifier and its input & output waveforms.

Yet another negative half wave rectifier is shown in fig.3. In this circuit two diodes are

used so that the output V’0 of the op-amp does not saturate.

The minimizes the response time and increase the operating frequency range of the op-

amp. However, notice that the op-amp is used in the inverting configuration and the

output is measured at the anode of diode D1 with respect to ground. Also, the output

resistance is non uniform since it depends on the sate of diode D1. In other words, the

output impedance is low when D1 is on and high when D1 is off. This problem, however,

can be cured by connecting a voltage follower stage at the output. During the positive

half-cycle of Vin, output V’0 is negative, which forward biases diode D1and close the

feedback loop through Rf.

SSASIT, SURAT EC DEPARTMENT Page 14

Analog Electronics

Fig. 3 Negative half wave rectifier and its input & output waveforms.

Since R1= Rf , V0=Vin. However, on the negative alternation of Vin, output V’0 is

positive; hence diodeD2 is forward biased. In fact, it is this diode that prevents the op-

amp from going positive saturation. Since diode D1 is off, output V0=0 V. To obtain

positive half-wave rectified outputs, diodes D1 and D2 must be reserved. to low

frequencies.

CIRCUIT DIAGRAM:

GRAPH:

Draw V vs Time graph

SSASIT, SURAT EC DEPARTMENT Page 15

Analog Electronics

PROCEDURE:

1. Connect the circuit as shown in circuit diagram.

2. Apply sine wave as input (2Vpp,100Hz) to the circuit from function generator and

obtain the output on output pin V0

3. Connect CRO at output terminal.

4. Draw the o/p waveform for circuit shown on figure.

CONCLUSION:

_______________

Remark with Sign & Date

SSASIT, SURAT EC DEPARTMENT Page 16

Analog Electronics

EXPERIMENT: 7 DATE: __/__/__

AIM: To design Schmitt trigger circuit using op-amp and take measurements.

APPARTUS:

IC-741, bread board, power supply, function generator, resister, connecting wires,

CRO, CRO Probe etc.

THEORY:

The circuit which converts an irregular-shaped waveform to a square wave or pulse is

called as Schmitt Trigger or Squaring Circuit. The input voltage Vin triggers the output

Vo every time it exceeds certain voltage levels called as the upper threshold voltage Vut

and lower threshold voltage Vl t.

These threshold voltages are obtained by using the voltage divider R1-R2, where the

voltage across R1 is fed back to the (+) input. The voltage across R1 is a variable

reference threshold voltage that depends on the value and polarity of the output voltage

Vo. When Vo= +Vsat, the voltage across R1 is called the upper threshold voltage, Vut.

The input voltage Vin must be slightly more positive than Vut in order to cause the

output Vo to switch from +Vsat to –Vsat. As long as Vin<Vut, Vo is at +Vsat. Using

the voltage-divider rule,

𝑉𝑢𝑡=(𝑅1/(𝑅1+𝑅2))(+𝑉𝑠𝑎𝑡) ----------(a)

On the other hand, when Vo= -Vsat , the voltage across R1 is referred to as the lower

threshold voltage, Vlt. Vin must be slightly more negative than Vlt in order to cause Vo

to switch from –Vsat to +Vsat. In other words, for Vin values greater than Vlt, Vo is at

–Vsat. Vlt is given by the following equation:

𝑉𝑙𝑡=(𝑅1/(𝑅1+𝑅2))(−𝑉𝑠𝑎𝑡) -----------(b)

Thus, if the threshold voltages Vut and Vlt are made larger than the input noise voltages,

the positive feedback will eliminate the false output transition. Also, the positive

feedback, because of its regenerative action, will make Vo switch faster between +Vsat

and –Vsat. The resistance ROM=R1||R2 is used to minimize the offset problems. The

comparator with positive feedback is said to exhibit hysteresis, a deadband condition.

That is, when the input of the comparator exceeds Vut, its output swiches from +Vsat

to –Vsat and reverts back to its original state, +Vsat, when the input goes

SSASIT, SURAT EC DEPARTMENT Page 17

Analog Electronics

below Vlt. The hysteresis voltage is, of course, equal to the difference between Vut and

Vlt. Therefore,

𝑉ℎ𝑦=𝑉𝑢𝑡−𝑉𝑙𝑡 =𝑅1𝑅1+𝑅2[+𝑉𝑠𝑎𝑡—𝑉𝑠𝑎𝑡] -----------(c)

DESIGN:

CIRCUIT DIAGRAM:

SCHMITT TRIGGER CIRCUIT IN INVERTING MODE

SSASIT, SURAT EC DEPARTMENT Page 18

Analog Electronics

PROCEDURE:

1. Connect the circuit as shown in circuit diagram.

2. Apply sine wave as input (2Vpp,100Hz) to the circuit from function generator and

obtain the output on output pin V0

3. Connect CRO at output terminal.

4. Draw the o/p waveform for ckt shown on figure.

GRAPH: Plot the Graph of input and output waveform & hysteresis loop with proper

scale on Graph paper.

CONCLUSION:

_______________________

Remark with Sign & Date

SSASIT, SURAT EC DEPARTMENT Page 19

Analog Electronics

EXPERIMENT: 8 DATE: __/__/__

AIM: To design, build and obtain the frequency responses of First order Low-

Pass and Band-Pass Active Filters.

APPARTUS:

IC-741, breadboard, power supply, function generator, resisters, capacitors of desire

value, connecting wires, CRO, CRO probes, etc.

THEORY:

First order low pass filter

The most common and easily understood active filter is the Active Low Pass Filter. Its

principle of operation and frequency response is exactly the same as those for the

previously seen passive filter, the only difference this time is that it uses an op-amp for

amplification and gain control. The simplest form of a low pass active filter is to connect

an inverting or non-inverting amplifier, the same as those discussed in the Op-amp

tutorial, to the basic RC low pass filter circuit as shown. This first-order low pass active

filter, consists simply of a passive RC filter stage providing a low frequency path to the

input of a non-inverting operational amplifier. The amplifier is configured as a voltage-

follower (Buffer) giving it a DC gain of one, Av = +1 or unity gain as opposed to the

previous passive RC filter which has a DC gain of less than unity.

The advantage of this configuration is that the op-amps high input impedance prevents

excessive loading on the filters output while its low output impedance prevents the

filters cut-off frequency point from being affected by changes in the impedance of the

load.

While this configuration provides good stability to the filter, its main disadvantage is

that it has no voltage gain above one. However, although the voltage gain is unity the

power gain is very high as its output impedance is much lower than its input impedance.

If a voltage gain greater than one is required we can use the following filter circuit.

The frequency response of the circuit will be the same as that for the passive RC filter,

except that the amplitude of the output is increased by the pass band gain, AF of the

SSASIT, SURAT EC DEPARTMENT Page 20

Analog Electronics

amplifier. For a non-inverting amplifier circuit, the magnitude of the voltage gain for

the filter is given as a function of the feedback resistor ( R2 ) divided by its

corresponding input resistor ( R1 ) value and is given as:

Therefore, the gain of an active low pass filter as a function of frequency will be:

Gain of a first-order low pass filter

Where:

AF = the pass band gain of the filter, (1 + R2/R1)

ƒ = the frequency of the input signal in Hertz, (Hz)

ƒc = the cut-off frequency in Hertz, (Hz)

Thus, the operation of a low pass active filter can be verified from the frequency gain

equation above as:

1. At very low frequencies, ƒ < ƒc

2. At the cut-off frequency, ƒ = ƒc

SSASIT, SURAT EC DEPARTMENT Page 21

Analog Electronics

3. At very high frequencies, ƒ > ƒc

Thus, the Active Low Pass Filter has a constant gain AF from 0Hz to the high frequency

cut-off point, ƒC. At ƒC the gain is 0.707AF, and after ƒC it decreases at a constant rate

as the frequency increases. That is, when the frequency is increased tenfold (one

decade), the voltage gain is divided by 10.

In other words, the gain decreases 20dB (= 20log 10) each time the frequency is

increased by 10. When dealing with filter circuits the magnitude of the pass band gain

of the circuit is generally expressed in decibels or dB as a function of the voltage gain,

and this is defined as:

Magnitude of Voltage Gain in (dB)

First order Band pass filter

This cascading together of the individual low and high pass passive filters produces a

low “Q-factor” type filter circuit which has a wide pass band. The first stage of the filter

will be the high pass stage that uses the capacitor to block any DC biasing from the

source. This design has the advantage of producing a relatively flat asymmetrical pass

SSASIT, SURAT EC DEPARTMENT Page 22

Analog Electronics

band frequency response with one half representing the low pass response and the other

half representing high pass response as shown.

The higher corner point ( ƒH ) as well as the lower corner frequency cut-off point ( ƒL )

are calculated the same as before in the standard first-order low and high pass filter

circuits. Obviously, a reasonable separation is required between the two cut-off points

to prevent any interaction between the low pass and high pass stages. The amplifier also

provides isolation between the two stages and defines the overall voltage gain of the

circuit.

The bandwidth of the filter is therefore the difference between these upper and lower -

3dB points. For example, suppose we have a band pass filter whose -3dB cut-off points

are set at 200Hz and 600Hz. Then the bandwidth of the filter would be given as:

Bandwidth (BW) = 600 – 200 = 400Hz.

The normalised frequency response and phase shift for an active band pass filter will be

as follows.

SSASIT, SURAT EC DEPARTMENT Page 23

Analog Electronics

CIRCUIT DIAGRAM:

FIRST ORDER BUTTERWORTH LOW-PASS FILTER

FIRST ORDER BAND-PASS BUTTERWORTH FILTER

SSASIT, SURAT EC DEPARTMENT Page 24

Analog Electronics

PROCEDURE:

FIRST ORDER BUTTERWORTH LOW-PASS FILTER

1. Calculate the value of resistors and capacitors from given data by using formula of

theory.

2. Connect circuit diagram on breadboard.

3. Apply Vpp Sine wave signal from function generator at the input terminals of 1st

order Low pass filter. Connect CRO channel 1 at input of Low pass filter. Connect

CRO channel 2 at the output terminals of 1st order Low pass filter.

4. Start varying frequency of input sine wave signal from 0Hz onwards

5. Observe input and output signals on CRO.

6. Calculate the cut off frequency by formula from theory.

FIRST ORDER BAND-PASS BUTTERWORTH FILTER

1. Calculate the value of resistors and capacitors from given data by using formula of

theory.

2. Connect circuit diagram on breadboard.

3. Apply Vpp Sine wave signal from function generator at the input terminals of 1st

order Band pass filter. Connect CRO channel 1 at input of Band pass filter. Connect

CRO channel 2 at the output terminals of 1st order Band pass filter.

4. Start varying frequency of input sine wave signal from 0Hz onwards

5. Observe input and output signals on CRO.

6. Calculate the cut off frequency by formula from theory.

GRAPH: Draw the gain versus frequency graph on semi log and find out the cut off

frequency for Low Pass and Band Pass filter.

CONCLUSION:

______________________

_

Remark with Sign & Date

SSASIT, SURAT EC DEPARTMENT Page 25

Analog Electronics

EXPERIMENT: 9 DATE: __/__/__

AIM: To design monostable and astable multi-vibrators using 555 timer IC and

verify their operation using measurements.

APPARTUS:

IC-555, breadboard, power supply, function generator, resisters, capacitors, connecting

wires, CRO, CRO probes, etc.

THEORY:

The 555 IC is a monolithic timing ckt that can produce accurate and highly stable time

delays or oscillations. The timer basically operates in one of the two modes: either as

an Astable (free - running) Multivibrator or Monostable (one - shot) Multivibrator.

MONOSTABLE OPERATION:

Initially when the o/p is low that is the ckt is in the stable state, transistor Q 1 is on and

capacitor C is shorted out to gnd. However, upon application of a negative trigger pulse

to pin 2, Q1 is turned off, which releases the short circuit across the capacitor C and

drives the o/p high. Capacitor C now is charging up towards Vcc through RA. However,

when the voltage across the capacitor equals the 2/3 Vcc, comparator 1’s o/p switches

from low to high, which in turn drive the o/p to its low state via the o/p of the flip-flop.

At the same time, the o/p of the flip-flop turns Q1 on, and hence C rapidly discharges

through the transistor. The o/p of the Monostable remains low until a pulse is again

applied. Then the cycle repeats. The pulse width of the trigger i/p must be smaller than

the expected pulse width of the o/p waveform. Also the trigger pulse must be a negative-

going i/p signal with an amplitude larger than 1/3 Vcc.

The time during which the o/p remains high is given by,

tp = 1.1 RAC

ASTABLE OPERATION:

Initially when the o/p is high, C starts charging toward Vcc through RA and RB. However

as soon as voltage across the C equals to the 2/3 Vcc comparator 1 triggers the flip-flop

SSASIT, SURAT EC DEPARTMENT Page 26

Analog Electronics

and the o/p switches low. Now C starts discharging through RB and Q1. When the

voltage across C equals 1/3 Vcc, comparator 2’s o/p triggers the flip-flop, and the o/p

goes high. Then the cycle repeats.

Here the C is periodically charged and discharged between 2/3 Vcc and 1/3 Vcc,

respectively. The timing during which C charges from 1/3 Vcc to 2/3 Vcc is equal to

the time the o/p is high and is given by,

tc = 0.69(RA+ RB) C.

Similarly, the time during which C discharges from 2/3 Vcc to 1/2 Vcc is equal to time

the o/p is low and is given by

td = 0.69 RBC

Thus the total period of time of the o/p wave form is

T = tc + td

= 0.69 (RA+2RB)C

So, the frequency of oscillation

1

Fo =

T

1.45

=

(RA+2RB)C

and the duty cycle is given by the ratio of the time tc for which the o/p is high to the

total time period T.

tc (RA+RB)

% duty cycle = 100 = [ ] 100

T (RA+2RB)

SSASIT, SURAT EC DEPARTMENT Page 27

Analog Electronics

DESIGN:

CIRCUIT DIAGRAM:

MONOSTABLE MULTIVIBRATOR

SSASIT, SURAT EC DEPARTMENT Page 28

Analog Electronics

ASTABLE MULTIVIBRATOR

PROCEDURE:

1. Connect the circuit as per the circuit dia. For each of Monostable Multivibrator and

Astable Multivibrator ckts.

2. Give trigger i/p in Monostable Multivibrator configuration and observe o/p on CRO

in each case.

3. See that both the circuit act as precision Multivibrator.

4. Draw the waveform on graph paper with proper scale that has been observed on

CRO.

OBSERVATION:

SSASIT, SURAT EC DEPARTMENT Page 29

Analog Electronics

GRAPH: Draw the waveform on graph paper with proper scale that has been observed

on CRO.

CONCLUSION:

_______________________

Remark with Sign & Date

SSASIT, SURAT EC DEPARTMENT Page 30

Analog Electronics

EXPERIMENT: 10 DATE: __/__/__

AIM: To design Triangular Wave Generator using op-amp and verify it operations with

Measurements.

APPARTUS:

IC-741, breadboard, power supply, function generator, resisters, capacitors of desire

value, connecting wires, CRO, CRO probes, etc.

THEORY:

The output waveform of the integrator is triangular if its input is a square wave. This

means that a triangular wave generator can be formed by simply connecting an

integrator to the square wave generator. The resultant circuit requires a dual op-amp,

two capacitors, and at least five resistors.

The generator consists of a comparator A1 and an integrator A2. To illustrate the circuit

operation, let us set the output of A1 at positive saturation +Vsat (≅+Vcc). This +Vsat is

an input of the integrator A2. The output of A2, therefore, will be a negative-going ramp.

Thus one end of the voltage divider R2-R3 is the positive saturation voltage +Vsat of A1

and the other is the negative-going ramp attains a certain value –VRamp, point P is

slightly below 0V;hence the output of A1 will switch from positive saturation to negative

saturation –Vsat(≅-VEE). This means that the output of A2 will now stop going

negatively and will begin to go positively. The output of A2 will continue to increase

until it reaches +VRamp. At this time the point P is slightly above 0V; therefore, the

output of A1 is switched back to the positive saturation level +Vsat.. The sequence then

repeats.

The amplitude and the frequency of the triangular wave can be determined as follows:

When the output of the comparator A1 is +Vsat, the output of the integrator A2 steadily

decreases until it reaches –VRamp. At this time the output of A1 switches from +Vsat to -

Vsat. Just before this switching occurs, the voltage at point P(+input) is 0V.This means

that the -VRamp must be developed across R2, and +Vsat must be developed across R3.

That is,

SSASIT, SURAT EC DEPARTMENT Page 31

Analog Electronics

𝑉𝑅𝑎𝑚𝑝 +𝑉𝑠𝑎𝑡

− = −

𝑅2 𝑅3

OR

𝑅2

−𝑉𝑅𝑎𝑚𝑝= − (+𝑉𝑠𝑎𝑡 ) -------------

𝑅3

(1a)

Similarly, +VRamp , the output voltage of A2 at which the output of A1 switches from –

Vsat to +Vsat, is given by

𝑅2

+𝑉𝑅𝑎𝑚𝑝= − (−𝑉𝑠𝑎𝑡 ) ------------ (1b)

𝑅3

Thus, from equations (1a) and (1b), the peak-to-peak (pp) output amplitude of the

triangular wave is

𝑉𝑜 (𝑝𝑝) = +𝑉𝑅𝑎𝑚𝑝 − (−𝑉𝑅𝑎𝑚𝑝 ) -------------- (2)

𝑅2

𝑉𝑜 (𝑝𝑝) = (2) (𝑉𝑠𝑎𝑡 )

𝑅3

Where Vsat=|+Vsat|=|-Vsat|. Equation (2) indicates that the amplitude of the triangular

wave decreases with an increase in R3.

The time it takes for the output waveform to swing from –VRamp to +VRamp is equal to

half the time period T/2.This time can be calculated from the integrator output equation.

Therefore, the time period of the triangular wave is,

4𝑅1 𝐶1 𝑅2

𝑇= --------------- (3a)

𝑅3

𝑅3

𝑓𝑜 = -------------- (3b)

4𝑅1 𝐶1 𝑅2

Equation (3b) shows that the frequency of oscillation f o increases with an increase in

R3.

Triangular wave generator is designed for a desired amplitude and frequency fo by using

equations (2) and (3b).

SSASIT, SURAT EC DEPARTMENT Page 32

Analog Electronics

CIRCUIT DIAGRAM:

OP-AMP AS TRIANGULAR WAVE GENERATOR

PROCEDURE:

1. Calculate the value of resistors and capacitors from given data by using formula of

theory.

2. Connect the circuit on bread board as per the circuit diagram.

3. Connect CRO at Triangular wave outputs and observes it. Also observes frequency.

4. Draw the waveform on graph paper with proper scale that has been observed on

CRO.

GRAPH: Draw the waveform on graph paper with proper scale that has been

observed on CRO.

CONCLUSION:

SSASIT, SURAT EC DEPARTMENT Page 33

Analog Electronics

______________________

Remark with Sign & Date

SSASIT, SURAT EC DEPARTMENT Page 34

S-ar putea să vă placă și

- GuidelinesOfDiamondFactory PDFDocument5 paginiGuidelinesOfDiamondFactory PDFRushabh PatelÎncă nu există evaluări

- Guidelines of Textile MarketDocument4 paginiGuidelines of Textile MarketRushabh PatelÎncă nu există evaluări

- ) ZT Dcfguz5Fl, SF: Smjl0V!) V/Tu"T LCZF Ahfzg (RF,) ZFBJF V/U (GL Dfu"Nlx"Sf Q LgidmDocument5 pagini) ZT Dcfguz5Fl, SF: Smjl0V!) V/Tu"T LCZF Ahfzg (RF,) ZFBJF V/U (GL Dfu"Nlx"Sf Q LgidmRushabh PatelÎncă nu există evaluări

- GuidelinesOfDiamondFactory PDFDocument5 paginiGuidelinesOfDiamondFactory PDFRushabh PatelÎncă nu există evaluări

- Ebaco Indoor Rubber FlooringDocument3 paginiEbaco Indoor Rubber FlooringRushabh PatelÎncă nu există evaluări

- Shoulder Stretching and Strengthening: IMG Physical TherapyDocument8 paginiShoulder Stretching and Strengthening: IMG Physical TherapyRushabh PatelÎncă nu există evaluări

- Guidelines of Textile MarketDocument4 paginiGuidelines of Textile MarketRushabh PatelÎncă nu există evaluări

- Gluten-Free Diets and Exercise Performance: A Nutritionist 'S ViewDocument2 paginiGluten-Free Diets and Exercise Performance: A Nutritionist 'S ViewRushabh PatelÎncă nu există evaluări

- Current Concepts in Sport NutritionDocument56 paginiCurrent Concepts in Sport NutritionJulioÎncă nu există evaluări

- Guidelines of Textile MarketDocument4 paginiGuidelines of Textile MarketRushabh PatelÎncă nu există evaluări

- Ebaco Indoor Rubber FlooringDocument3 paginiEbaco Indoor Rubber FlooringRushabh PatelÎncă nu există evaluări

- GuidelinesOfDiamondFactory PDFDocument5 paginiGuidelinesOfDiamondFactory PDFRushabh PatelÎncă nu există evaluări

- Gluten-Free Diets and Exercise Performance: A Nutritionist 'S ViewDocument2 paginiGluten-Free Diets and Exercise Performance: A Nutritionist 'S ViewRushabh PatelÎncă nu există evaluări

- Guidelines of Textile MarketDocument4 paginiGuidelines of Textile MarketRushabh PatelÎncă nu există evaluări

- Shoulder Stretching and Strengthening: IMG Physical TherapyDocument8 paginiShoulder Stretching and Strengthening: IMG Physical TherapyRushabh PatelÎncă nu există evaluări

- Academic Calender 16-17 EvenDocument2 paginiAcademic Calender 16-17 EvenRushabh PatelÎncă nu există evaluări

- GuidelinesOfDiamondFactory PDFDocument5 paginiGuidelinesOfDiamondFactory PDFRushabh PatelÎncă nu există evaluări

- High Intensity Circuit Training Using Body WeightDocument6 paginiHigh Intensity Circuit Training Using Body Weightenrico.talpoÎncă nu există evaluări

- Mauro Di Pasquale - Anabolic - SynergismDocument5 paginiMauro Di Pasquale - Anabolic - SynergismBobÎncă nu există evaluări

- Ebaco Indoor Rubber FlooringDocument3 paginiEbaco Indoor Rubber FlooringRushabh PatelÎncă nu există evaluări

- New Doc 170119 - 1 - Full Time Project AssociateDocument1 paginăNew Doc 170119 - 1 - Full Time Project AssociateRushabh PatelÎncă nu există evaluări

- Btech First Year Syllabus FinalDocument39 paginiBtech First Year Syllabus FinalvenkithebossÎncă nu există evaluări

- Application Form Advt DT 29-03-2018 Teaching StaffDocument5 paginiApplication Form Advt DT 29-03-2018 Teaching Staffbhushan tavdeÎncă nu există evaluări

- Experiment - 2: Heat Loss by Natural Convection From Ice PlateDocument7 paginiExperiment - 2: Heat Loss by Natural Convection From Ice PlateRushabh PatelÎncă nu există evaluări

- Composite WallDocument6 paginiComposite WallRushabh PatelÎncă nu există evaluări

- MSM Manual 02072016 035354AMDocument177 paginiMSM Manual 02072016 035354AMPraveen SinghÎncă nu există evaluări

- Post-Graduate Research Centre For Industrial Design: B.E. Semester IV: Design Engineering - 1BDocument12 paginiPost-Graduate Research Centre For Industrial Design: B.E. Semester IV: Design Engineering - 1BRushabh PatelÎncă nu există evaluări

- Experiment - 5: AIM: Study and Calculate The Efficiency of Fin in Natural and Forced ConvectionDocument17 paginiExperiment - 5: AIM: Study and Calculate The Efficiency of Fin in Natural and Forced ConvectionRushabh PatelÎncă nu există evaluări

- Experiment - 4: AIM: To Measure The Emissivity of Test PlateDocument8 paginiExperiment - 4: AIM: To Measure The Emissivity of Test PlateRushabh PatelÎncă nu există evaluări

- Heat Transfer: Lab ManualDocument3 paginiHeat Transfer: Lab ManualRushabh PatelÎncă nu există evaluări

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5794)

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (895)

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (400)

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (588)

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (74)

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (344)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (121)

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)

- Probador CCFL-CreatronicaDocument6 paginiProbador CCFL-CreatronicasanlugoÎncă nu există evaluări

- 1SS355Document3 pagini1SS355Barton EletronicsÎncă nu există evaluări

- Clarion Pn2165mDocument12 paginiClarion Pn2165mJorge NovoaÎncă nu există evaluări

- Listening Scripts: Unit 1Document7 paginiListening Scripts: Unit 1giusy scottoÎncă nu există evaluări

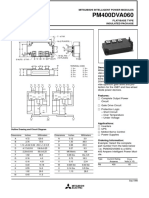

- PM400DVA060: Mitsubishi Intelligent Power ModulesDocument6 paginiPM400DVA060: Mitsubishi Intelligent Power ModulesDiego GrisalesÎncă nu există evaluări

- Basic Electronics Lab Manual: TechnologyDocument89 paginiBasic Electronics Lab Manual: TechnologykhanrahÎncă nu există evaluări

- Fds6982S: Dual Notebook Power Supply N-Channel Powertrench SyncfetDocument12 paginiFds6982S: Dual Notebook Power Supply N-Channel Powertrench SyncfetAlejandro DelgadoÎncă nu există evaluări

- A Look at The Yaqin MC100BDocument24 paginiA Look at The Yaqin MC100BRoi Rey100% (1)

- Module 1 Microwave Fundamentals and Electromagnetic Field TheoryDocument41 paginiModule 1 Microwave Fundamentals and Electromagnetic Field TheorySachin RuikarÎncă nu există evaluări

- Theory Class 1dggfgDocument250 paginiTheory Class 1dggfgKumar GorlaÎncă nu există evaluări

- Osg 65 R 125 HFDocument10 paginiOsg 65 R 125 HFmrromocom7Încă nu există evaluări

- Appnote Operating SPL PLXX 03112004Document5 paginiAppnote Operating SPL PLXX 03112004interconnectfast4Încă nu există evaluări

- Slot-Based Pattern Reconfigurable ESPAR Antenna For IoT ApplicationsDocument10 paginiSlot-Based Pattern Reconfigurable ESPAR Antenna For IoT ApplicationsloganathanÎncă nu există evaluări

- Sylla PDFDocument50 paginiSylla PDFGiju PaulÎncă nu există evaluări

- Suniva Suniva Opt330 72 4 100 Silver Mono Solar Panel Specs PDFDocument2 paginiSuniva Suniva Opt330 72 4 100 Silver Mono Solar Panel Specs PDFJean Miguel BacaniÎncă nu există evaluări

- Littelfuse TVS Diode 20KPA Datasheet - pdf-369791Document7 paginiLittelfuse TVS Diode 20KPA Datasheet - pdf-369791K.S. BalasubramaniamÎncă nu există evaluări

- Ece Mini Project On Embedded Password Based Security Door Lock SystemDocument45 paginiEce Mini Project On Embedded Password Based Security Door Lock Systemvalgin100% (2)

- Class 12 Physics Project On Full Wave Bridge RectifierDocument14 paginiClass 12 Physics Project On Full Wave Bridge RectifierVaibhavPal75% (96)

- PN JunctionDocument4 paginiPN JunctionJohn Raymart CostalesÎncă nu există evaluări

- Lab 3 Report WDocument19 paginiLab 3 Report WRick JordanÎncă nu există evaluări

- Analogue Electronic Lab (MCE3013) : Experiment 1: Diode CharacteristicsDocument7 paginiAnalogue Electronic Lab (MCE3013) : Experiment 1: Diode CharacteristicsAmirul InÎncă nu există evaluări

- Thomson Chassis Icc17 Instruction SCH PDFDocument180 paginiThomson Chassis Icc17 Instruction SCH PDFFrancisco Rodriguez MartinezÎncă nu există evaluări

- E5 Data AcquisitionDocument25 paginiE5 Data Acquisitionmuhammad afaq IEEEÎncă nu există evaluări

- Be 201 Engineering Physics Unit 4Document28 paginiBe 201 Engineering Physics Unit 4Pravar AnuÎncă nu există evaluări

- Lavadora Frigidaire Gb7nc60hdDocument15 paginiLavadora Frigidaire Gb7nc60hdHernan Vallenilla Rumildo MixÎncă nu există evaluări

- Qfet Qfet Qfet Qfet: FQA9P25Document9 paginiQfet Qfet Qfet Qfet: FQA9P25Tahar BenacherineÎncă nu există evaluări

- Byv32 MosfetDocument5 paginiByv32 MosfetHungaro KikoÎncă nu există evaluări

- Questions & Answers On Application of DiodesDocument46 paginiQuestions & Answers On Application of Diodeskibrom atsbha100% (1)

- MP6908 同步整流Document14 paginiMP6908 同步整流857462946Încă nu există evaluări