Documente Academic

Documente Profesional

Documente Cultură

Grounding Microstrip Lines With Via Holes: Ref Plane

Încărcat de

Sandeep Kumar PalaniswamyTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Grounding Microstrip Lines With Via Holes: Ref Plane

Încărcat de

Sandeep Kumar PalaniswamyDrepturi de autor:

Formate disponibile

IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES, VOL. 40, NO.

8, AUGUST 1992 1719

[2] J. D. Montgomery, “Hybrid MIC North American markets,” Micro-

wave J . , vol. 32, no. 4, pp. 32-39, Apr. 1989.

131 Y. L. Chow, X. Y. She, G. E. Howard, M. G. Stubbs and M. Gau-

dreault, “A modified moment method for the computation of complex

MMIC circuits,” in Proc. 16th European Microwave Conf., Dublin,

Sept., 1986, pp. 625-630.

141 M. G. Stubbs, Y. L. Chow, and G. E. Howard, “Use of a spatial field

t-4 1

technique for the analysis of the active MMIC’s,” in Proc. 17rh Eu-

ropean Microwave Conf., Rome, Sept. 1987, pp. 273-278.

151 Y . L. Chow, G. E. Howard, and M. G. Stubbs, “The field theoretic

MMIC computation enhanced by the variational principle,” in Proc.

5th Annual Review of Progress in Applied Computational Electromag-

netics,” Monterey, CA, Mar. 1989.

[6] G. E. Howard, J . Dai, Y . L. Chow, and M. G. Stubbs, “The power REF PLANE 13

transfer mechanism of MMIC spiral transformers and adjacent spiral

inductors,” in IEEE MTT-S Int. Microwave Symp. D i g . , Long Beach,

CA June 1989, pp. 1251-1254.

171 R. Faraji-Dana and Y. L. Chow, “The ac resistance of a microstripline

and its ground plane,” in IEEE M7T-S Int. Microwave Symp. D i g . , Fig. 1. Microstrip single via hole and microstrip line of width w . All di-

Long Beach, CA, June 1989. mensions are mils.

IS] Y. L. Chow and K. D. Srivastava, “Non-uniform electric field induced

voltage calculations,” Revised, Report (1 17T317) for the Canadian

Electrical Association, Montreal, Quebec, Canada, pp. 23-26, Feb.

1988.

191 Y. L. Chow and M. M . Yovanovich, “The shape factor of the capac-

itance of a conductor,” J . Appl. Phys., vol. 52, pp. 8470-8475, 1982.

Grounding Microstrip Lines With Via Holes

Daniel G. Swanson, Jr.

Abstract-Grounding microstrip circuits with via holes is an estah-

lished technology and modeling isolated via holes with analytical models

is well known. However, the availability of electromagnetic field

solvers provides an opportunity to model via holes and the metalization 0 5 10 15 20 25

surrounding them in a more realistic fashion. Calculated equivalent

inductances for single and double via hole configurations are pre- FREQUENCY (GHz)

sented. A microstrip interdigital filter with grounded resonators pro- Fig. 2, Equivalent inductance of microstrip single via, alumina substrate,

vides experimental verification. h = 15 mil, t, = 9.8, w = line width in mils.

I. INTRODUCTION mil thick and 25 mil thick alumina. The surrounding metalization

is 24 mils square. A microstrip line of width w could then be con-

Most thin film fabrication facilities have a via hole process avail-

nected to one side of square. Because the component designer is

able to microwave component designers. In most cases the designer

most likely to use the minimum via hole diameter and metalization

will choose the minimum via hole diameter and spacing allowed

area allowed, the equivalent inductance of this structure can be

by the process. Earlier work [ l ] has focused on analytical models

computed as a function of only line width and frequency. The

for a single via hole as a function of hole diameter and substrate

equivalent inductance is computed at a reference plane defined by

thickness. But the actual via hole configuration used by the de-

the junction of the microstrip line and the square pad around the

signer is often a more complex combination of several via holes

via hole. For lines other than 24 mils wide it is clear that the model

and other microstrip discontinuities. And the significant interac-

includes a step junction, the inductance of the via hole and the

tions between several discontinuities in close proximity cannot be

capacitance of the pad surrounding the via.

accurately described by combining analytical models for isolated

The analysis of this structure was carried out on a full wave field

elements. In this work, an electromagnetic field solver has been

solver [2] for several line widths over the 2 to 20 GHz frequency

used to compute the equivalent inductance of two different via hole

range. The round via hole was approximated by an octagonal hole

topologies as a function of frequency, substrate thickness and a

in the analysis. The results of this analysis for 15 mil thick alu-

microstrip discontinuity variable.

mina, E , = 9.8 are shown in Fig. 2. A similar analysis for 25 mil

thick alumina, E,. = 9.8 was also performed with the results shown

11. SINGLE

VIA HOLES in Fig. 3. These graphs provide a convenient look-up table for the

Fig. 1 is the preferred geometry for a single via hole in alumina designer using single via holes.

at Watkins-Johnson. The 13 mil diameter hole is used in both 15

111. DOUBLEVIA HOLES

Manuscript received August 5, 1991; revised February 4, 1992.

The author is with Watkins-Johnson Company, 3333 Hillview Ave., Double via holes are often used to decrease the parasitic induc-

Stanford Research Park, Palo Alto, CA 94304.1204. tance of the ground connection or to ground a wider microstrip line.

IEEE Log Number 9200862. Fig. 4 is the preferred geometry for double via holes at Watkins-

0018-9480/92$03,00 0 1992 IEEE

1720 IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES, VOL. 40, NO. 8, AUGUST 1992

.I9 w=4

-

W

.27 1 w=4 : F

E. . I 8

w W=8

g .26 r g .I7

a w=8 : w=12

63 .25

20

.16

w=16

n w=12 : .15 w = 20

z .24 f z ~ = 2 4:

w=l6 : .I4 w=28 :

.

.23 : w=20

.13 ~ = 4 0

.22

0 5 10 15 20 25 0 5 10 15 20 25

FREQUENCY (GHz) FREQUENCY (GHz)

Fig. 3 . Equivalent inductance of microstrip single via, alumina substrate, Fig. 6 . Equivalent inductance of microstrip double via, alumina substrate,

h = 25 mil, 6 , = 9.8, w = line width in mils h = 25 mil, t , = 9.8, w = line width in mils.

REF PLANE 1

Fig. 4. Microstrip double via holes and microstrip line of width w. All

dimensions are mils.

-: : 1

z . 1 1 o - - - - = = = t o

Fig. 7. Current density on microstrip double via, alumina substrate, h

15 mil, E, = 9.8, w = 20 mil, freq = 18 GHz.

=

analysis for 25 mil thick alumina, t, = 9 . 8 was also performed

with the results shown in Fig. 6.

Note that for both substrate thicknesses the equivalent induc-

tance is lower for the double via holes compared to the single via

hole although the ratio is less than two due to the mutual coupling

between the double via holes. Also, the dispersion in the equivalent

inductance is much higher for the thicker substrates at high fre-

quencies. The sharp increase in equivalent inductance for w = 2

at 2 GHz in all four inductance versus frequency plots is thought

FREQUENCY (GHz) to be a numerical precision problem in the analysis.

Fig. 5. Equivalent inductance of microstrip double via, alumina substrate, It is also interesting to observe the conduction current density on

h = 15 mil, E, = 9.8, w = line width in mils. the metalization for the double via configuration (Fig. 7). Lightly

shaded areas indicate high currents while dark regions indicate low

currents. The high current density at the edges of the microstrip

Johnson. The two 13 mil diameter via holes are separated by 24 line can clearly be seen. The current down the vias follows the

mils center to center. The surrounding metalization is 24 mils by shortest path and flows mostly on the sides of the vias nearest the

48 mils. This structure was also analyzed for various line widths step discontinuity. It may be surprising to some workers that the

over the 2 to 20 GHz frequency range. The results of this analysis sides of the via holes away from the step junction and the trailing

for 15 mil thick alumina, E , = 9.8 are shown in Fig. 5 . A similar edge of the surrounding metallization conduct very little current.

IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES, VOL 40, NO. 8. AUGUST 1992 1721

I 6

-10

rr

3 -20

rn

v)

5 -30

z

E 4 0

171.7

i

K

W

v) -50

z

-60

-70

4.0 4.5 5.0 5.5 6.0

1 FREQUENCY (GHz)

Fig. 10. Measured and computed insertion loss for the microstrip inter-

digital filter. The computer analysis includes equivalent double via hole

Fig. 8. Microstrip interdigital filter, alumina substrate, h = 15 mil, E, = inductances from Fig. 5.

9.8. All dimensions are mils.

The measured versus computed results (assuming zero induc-

tance for the vias) for the filter are shown in Fig. 9. The error in

center frequency is approximately 200 MHz or about 4 % of the

m^ desired center frequency. A second computer prediction was made

3 using the equivalent double via hole inductances from Fig. 5 . The

In

rn measured versus computed results (with via hole inductance) are

sz shown in Fig. 10.

P Note the close agreement between the measured and computed

I- center frequencies in Fig. 10. Figs. 9 and 10 together demonstrate

K

W

U) the sensitivity of the interdigital filter to the via hole inductance.

z Fig. 10 demonstrates, at least indirectly, the accuracy of the equiv-

alent inductance values taken from Fig. 5 . Similar results for in-

terdigital filters have been achieved at 8 GHz and 14 GHz.

4.0 4.5 5.0 5.5 6.0

V . CONCLUSION

FREQUENCY (GHz)

Fig. 9. Measured and computed insertion loss for the microstrip inter- Grounding microwave circuits with via holes is an accepted

digital filter. The parasitic inductance of the via holes was ignored in the practice. Analytical models for isolated via holes are available but

design procedure. may not fully describe the actual topology. The equivalent induc-

tance of a single via hole or several via holes and their surrounding

metalization can be accurately modeled using a full wave electro-

There is a high current density on the leading edge of the step and magnetic field solver. A simple equivalent inductance can be com-

part way down the sides of the via hole pad. But at the outer corners puted directly from the Z-parameters provided by the field solver.

of the step there are very definite current nulls. This distribution of A lumped element model with several inductors and capacitors

current around the step discontinuity is consistent with computa- would eliminate the frequency variable and is a more convenient

tions made by others [3]. representation for general purpose CAD programs. We are cur-

Clearly the electromagnetic field solver can account for the non- rently working on fitting the computed data to a lumped element

uniform current distribution on the via holes and their surrounding model.

metalization. In fact, this current distribution will change depend- A microstrip interdigital filter was designed and built to experi-

ing on the exact circuit topology, an effect that would be very dif- mentally verify the computed equivalent inductances. When the

ficult to include in a general purpose analytical model. parasitic grounding inductances were included in the analysis, the

agreement between the computed and measured center frequencies

IV. EXPERIMENTAL

VERIFICATION was excellent.

To verify the accuracy of the computations a microstrip inter-

digital filter was designed and fabricated. The interdigital filter (Fig. REFERENCES

8) is an excellent test case because the center frequency of the fab- [l] M. Goldfarb and R. Pucel, “Modeling via hole grounds in micro-

ricated filter is very sensitive to the parasitic inductance of the via strip,” IEEE Microwave Guided Wave Lett., vol. I , no. 6 , pp. 135-

hole grounding, and frequency is an easy parameter to measure. 137, June 1991.

The filter was designed assuming the equivalent inductance at the [2] Em, Sonnet Software, Liverpool, NY.

edge of the via pad was zero. The adjacent and non-adjacent cou- [3] S . Marchetti and T. Rozzi, “H-field and J-current singularities at sharp

edges in printed circuits,” IEEE Trans. Antennas Propagat., vol. 39,

plings between interdigital resonators were modeled using a spec- no. 9, pp. 1321-1331, Sept. 1991.

tral domain based multi-strip model [4]. [4] SUPER-COMPACT, Compact Software, Paterson, NJ.

S-ar putea să vă placă și

- The Design of Small Slot ArraysDocument6 paginiThe Design of Small Slot ArraysRoberto B. Di RennaÎncă nu există evaluări

- SIW Mixer 2006Document3 paginiSIW Mixer 2006Longbui4845Încă nu există evaluări

- Parameters of Microstrip Transmission LinesDocument7 paginiParameters of Microstrip Transmission LinesSergio Castro RodriguezÎncă nu există evaluări

- Theory and Experiment On Microstrip AntennasDocument9 paginiTheory and Experiment On Microstrip AntennasFabian VazquezÎncă nu există evaluări

- Novel Microstrip Bandpass Filter Based On Defected Ground Structure and Slotline Coupling TechniquesDocument4 paginiNovel Microstrip Bandpass Filter Based On Defected Ground Structure and Slotline Coupling TechniqueshosseinÎncă nu există evaluări

- Ring Type Patch AntennaDocument9 paginiRing Type Patch Antennashuvro911Încă nu există evaluări

- The Propagation of Electromagnetic Waves in Multiconductor Transmission Lines: International Series of Monographs on Electromagnetic WavesDe la EverandThe Propagation of Electromagnetic Waves in Multiconductor Transmission Lines: International Series of Monographs on Electromagnetic WavesÎncă nu există evaluări

- Millimeter-Wave Dual-Band Microstrip Patch Antennas Using Multilayer Gaas TechnologyDocument4 paginiMillimeter-Wave Dual-Band Microstrip Patch Antennas Using Multilayer Gaas TechnologyShivanandKalmaniÎncă nu există evaluări

- A New Compact Wideband BalunDocument3 paginiA New Compact Wideband BalunYaz AbueitaÎncă nu există evaluări

- World Academy of Science, Engineering and Technology 49 2009Document3 paginiWorld Academy of Science, Engineering and Technology 49 2009BarirAs-Syifa'Încă nu există evaluări

- A Design Approach Analysis For Inset-Fed RectangulDocument4 paginiA Design Approach Analysis For Inset-Fed RectangulNam TàoÎncă nu există evaluări

- A Wideband Circular Patch Antenna: D and AirDocument2 paginiA Wideband Circular Patch Antenna: D and Airحماد حسينÎncă nu există evaluări

- Elrashidi2012 PDFDocument10 paginiElrashidi2012 PDFGurulakshmi A BÎncă nu există evaluări

- R 6915641Document87 paginiR 6915641BulentÎncă nu există evaluări

- Mstrip-Slot Transtion MOTL98Document4 paginiMstrip-Slot Transtion MOTL98Sreedhar GundlapalliÎncă nu există evaluări

- FerreiraDocument5 paginiFerreiraSaikat MondalÎncă nu există evaluări

- IEEEMagn 44 2745 2008 Ni-Cu WiresDocument5 paginiIEEEMagn 44 2745 2008 Ni-Cu Wireskevin gonzalezÎncă nu există evaluări

- 1136 or For: Trans. Antennas Propagat.Document5 pagini1136 or For: Trans. Antennas Propagat.Shesha PrasadÎncă nu există evaluări

- Engg Approach To Design of Tapered Dielectric Rod Horn AntDocument9 paginiEngg Approach To Design of Tapered Dielectric Rod Horn Antవేలుసామి లింగాసామిÎncă nu există evaluări

- Mesh Antennas With Reduced Size: July 2004Document5 paginiMesh Antennas With Reduced Size: July 2004sheng-huang WuÎncă nu există evaluări

- 2001 - Horenstein - A Micro-Aperture Electrostatic Field Mill Based On MEMS TechnologyDocument7 pagini2001 - Horenstein - A Micro-Aperture Electrostatic Field Mill Based On MEMS TechnologyFelipeapalexandÎncă nu există evaluări

- Literature ReviewDocument9 paginiLiterature Reviewshuvro911Încă nu există evaluări

- Electromagnetic Coupling To Thin-Wire Structures in Complex CavitiesDocument4 paginiElectromagnetic Coupling To Thin-Wire Structures in Complex CavitiesZied HouanebÎncă nu există evaluări

- Fundamentals of Microwave Electronics: International Series of Monographs on Electronics and InstrumentationDe la EverandFundamentals of Microwave Electronics: International Series of Monographs on Electronics and InstrumentationÎncă nu există evaluări

- A New Circular Spinneret System For Electrospinning Numerical Approach and Electric Field OptimizationDocument8 paginiA New Circular Spinneret System For Electrospinning Numerical Approach and Electric Field OptimizationNounaÎncă nu există evaluări

- Simulation Study On Insertion and Return Loss of Planar Transmission Lines For Different Dielectric SubstratesDocument8 paginiSimulation Study On Insertion and Return Loss of Planar Transmission Lines For Different Dielectric SubstratesBeeresha R SÎncă nu există evaluări

- A Single-Layer Ultrawideband Microstrip AntennaDocument4 paginiA Single-Layer Ultrawideband Microstrip Antennanguyễn đắc huyÎncă nu există evaluări

- Practical Wide Frequency Approach For CalculatingDocument6 paginiPractical Wide Frequency Approach For Calculatingmichael gorgeÎncă nu există evaluări

- Project ReportDocument6 paginiProject ReportLeo7 ProdÎncă nu există evaluări

- Liao - Microstrip Lines - ANSWERDocument23 paginiLiao - Microstrip Lines - ANSWERcdg prqÎncă nu există evaluări

- Equivalent-Circuit Models For The Design of Metamaterials Based On Artificial Magnetic InclusionsDocument9 paginiEquivalent-Circuit Models For The Design of Metamaterials Based On Artificial Magnetic InclusionskillerjackassÎncă nu există evaluări

- Theory of Microwave Valves: International Series of Monographs on Electronics and InstrumentationDe la EverandTheory of Microwave Valves: International Series of Monographs on Electronics and InstrumentationÎncă nu există evaluări

- Caulton1968Document8 paginiCaulton1968عبد المجيد فرةÎncă nu există evaluări

- Frequency Reconfigurable Triple Band-Notched Ultra-Wideband Antenna With Compact SizeDocument11 paginiFrequency Reconfigurable Triple Band-Notched Ultra-Wideband Antenna With Compact SizenikitaÎncă nu există evaluări

- Probing The Magnetic Field ProbeDocument6 paginiProbing The Magnetic Field Probe4hgtrb0xÎncă nu există evaluări

- Analytical Scalable PDFDocument9 paginiAnalytical Scalable PDFsourabhbasuÎncă nu există evaluări

- Analytical Scalable PDFDocument9 paginiAnalytical Scalable PDFsourabhbasuÎncă nu există evaluări

- Design & Development of Helmholtz Coil For Hyperpolarized MRIDocument6 paginiDesign & Development of Helmholtz Coil For Hyperpolarized MRIJosué Daniel Meneses DíazÎncă nu există evaluări

- Modelling of Substation Grounding Grids: A. El-Morshedy, PH.D., A.G Zeitoun, PH.D., and M.M. GhourabDocument6 paginiModelling of Substation Grounding Grids: A. El-Morshedy, PH.D., A.G Zeitoun, PH.D., and M.M. GhouraboscarÎncă nu există evaluări

- Project-Antenna ArrayDocument17 paginiProject-Antenna ArraysushantÎncă nu există evaluări

- CPW Fed Slot Antenna For UWBDocument4 paginiCPW Fed Slot Antenna For UWBBarirAs-Syifa'Încă nu există evaluări

- Ieee Transactions On Antennas and Propagation, Vol. 60, No. 1, January 2012 389Document4 paginiIeee Transactions On Antennas and Propagation, Vol. 60, No. 1, January 2012 389正气歌Încă nu există evaluări

- MOS Integrated Circuit DesignDe la EverandMOS Integrated Circuit DesignE. WolfendaleÎncă nu există evaluări

- Overview of Quasi-Planar Transmission Lines: FinlinesDocument6 paginiOverview of Quasi-Planar Transmission Lines: FinlinesVimalÎncă nu există evaluări

- Cavity Couplers Traveling Tubes : EllipticDocument5 paginiCavity Couplers Traveling Tubes : EllipticRaktim GuhaÎncă nu există evaluări

- An Introduction to the Theory of Microwave CircuitsDe la EverandAn Introduction to the Theory of Microwave CircuitsK. KurokawaÎncă nu există evaluări

- Small-Size Wide-Bandwidth Microstrip Patch Antennas: February 2001Document10 paginiSmall-Size Wide-Bandwidth Microstrip Patch Antennas: February 2001Amador Garcia IIIÎncă nu există evaluări

- Printed Circular Disc Monopole Antenna For Ultra-Wideband ApplicationsDocument2 paginiPrinted Circular Disc Monopole Antenna For Ultra-Wideband ApplicationsmoonyraÎncă nu există evaluări

- Geophysical Field Theory and Method, Part B: Electromagnetic Fields IDe la EverandGeophysical Field Theory and Method, Part B: Electromagnetic Fields IÎncă nu există evaluări

- Static Electromagnetic Frequency Changers: International Series of Monographs on Electronics and InstrumentationDe la EverandStatic Electromagnetic Frequency Changers: International Series of Monographs on Electronics and InstrumentationÎncă nu există evaluări

- Sample Paper - 2012 Class - XII Subject - PHYSICS (Theory)Document7 paginiSample Paper - 2012 Class - XII Subject - PHYSICS (Theory)Abhimanyu MalhotraÎncă nu există evaluări

- Simon C. Bott Et Al - Quantitative Measurements of Wire Ablation in Tungsten X-Pinches at 80 KaDocument6 paginiSimon C. Bott Et Al - Quantitative Measurements of Wire Ablation in Tungsten X-Pinches at 80 KaCola7890Încă nu există evaluări

- Bandwidth Limitations of Log Periodic Microstrip Patch Antenna ArraysDocument2 paginiBandwidth Limitations of Log Periodic Microstrip Patch Antenna ArraysJorge MitrioneÎncă nu există evaluări

- Progress in Electromagnetics Research C, Vol. 6, 93-102, 2009Document10 paginiProgress in Electromagnetics Research C, Vol. 6, 93-102, 2009amit ranjanÎncă nu există evaluări

- 2021IEEE57n2a5300305 - Development of A Broad Bandwidth Helmholtz Coil For Biomagnetic ApplicationDocument5 pagini2021IEEE57n2a5300305 - Development of A Broad Bandwidth Helmholtz Coil For Biomagnetic Applicationf111142151Încă nu există evaluări

- CAD Cavity Model Analysis of High TC Superconducting Rectangular Patch Printed On Anisotropic SubstratesDocument4 paginiCAD Cavity Model Analysis of High TC Superconducting Rectangular Patch Printed On Anisotropic SubstratesHoucine HoucineÎncă nu există evaluări

- Subthreshold Conduction in Mosfet'S: Acknowledgment A. KDocument14 paginiSubthreshold Conduction in Mosfet'S: Acknowledgment A. KshanujgargÎncă nu există evaluări

- A New Aperture Coupled Microstrip Slot AntennaDocument19 paginiA New Aperture Coupled Microstrip Slot AntennaSiddharthSharmaÎncă nu există evaluări

- Substrate Integrated Waveguide PaperDocument3 paginiSubstrate Integrated Waveguide PaperSabirSayedÎncă nu există evaluări

- Geophysical Field Theory and Method, Part C: Electromagnetic Fields IIDe la EverandGeophysical Field Theory and Method, Part C: Electromagnetic Fields IIÎncă nu există evaluări

- Week 11Document11 paginiWeek 11Sandeep Kumar PalaniswamyÎncă nu există evaluări

- Committee On AllowancesDocument116 paginiCommittee On AllowancesSandeep Kumar PalaniswamyÎncă nu există evaluări

- Frequency Response and Bode Plots: 1.1 PreliminariesDocument20 paginiFrequency Response and Bode Plots: 1.1 PreliminariesAmresh VarshneyÎncă nu există evaluări

- TutorialDocument2 paginiTutorialSandeep Kumar PalaniswamyÎncă nu există evaluări

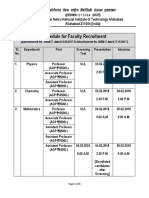

- Schedule Faculty RecruitmentDocument6 paginiSchedule Faculty RecruitmentSandeep Kumar PalaniswamyÎncă nu există evaluări

- Frequency Response and Bode Plots: 1.1 PreliminariesDocument20 paginiFrequency Response and Bode Plots: 1.1 PreliminariesAmresh VarshneyÎncă nu există evaluări

- Coupled Lines 123Document11 paginiCoupled Lines 123Sandeep Kumar PalaniswamyÎncă nu există evaluări

- ECED 6000 EligibleDocument7 paginiECED 6000 EligibleSandeep Kumar PalaniswamyÎncă nu există evaluări

- Course Notes 7824 Part6Document15 paginiCourse Notes 7824 Part6Tareq SalahÎncă nu există evaluări

- Operational Amplifiers and LinearI Cs - 3EDocument591 paginiOperational Amplifiers and LinearI Cs - 3Emaxwell_eulerÎncă nu există evaluări

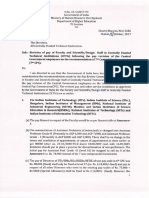

- 7th CPC Order CFTIs PDFDocument7 pagini7th CPC Order CFTIs PDFknighthood4allÎncă nu există evaluări

- Rolling Advt - No.6 2017Document4 paginiRolling Advt - No.6 2017Sandeep Kumar PalaniswamyÎncă nu există evaluări

- Lec 10Document18 paginiLec 10Sandeep Kumar PalaniswamyÎncă nu există evaluări

- Microstrip AntennaDocument84 paginiMicrostrip Antennanishanth17492% (12)

- RF MemsDocument31 paginiRF MemsSandeep Kumar PalaniswamyÎncă nu există evaluări

- Lecture-4: 3.4 Relation Between Wire and Aperture AntennasDocument4 paginiLecture-4: 3.4 Relation Between Wire and Aperture AntennasSandeep Kumar PalaniswamyÎncă nu există evaluări

- Lecture7 Loop Antenna PDFDocument3 paginiLecture7 Loop Antenna PDFSandeep Kumar PalaniswamyÎncă nu există evaluări

- Lecture-4: 3.4 Relation Between Wire and Aperture AntennasDocument4 paginiLecture-4: 3.4 Relation Between Wire and Aperture AntennasSandeep Kumar PalaniswamyÎncă nu există evaluări

- Ngữ Âm Âm Vị Trắc NghiệmDocument14 paginiNgữ Âm Âm Vị Trắc Nghiệmd.duongnguyen1901Încă nu există evaluări

- Chordu Piano Chords Ay Hairathe Official Audio Song Guru Hariharan A R Rahman Gulzar Chordsheet Id 038jmlSH3iMDocument3 paginiChordu Piano Chords Ay Hairathe Official Audio Song Guru Hariharan A R Rahman Gulzar Chordsheet Id 038jmlSH3iMAditya KanjarlaÎncă nu există evaluări

- Emcee ScriptDocument4 paginiEmcee ScriptMss JunabelleÎncă nu există evaluări

- SS-Standartenführer Hans Wilhelm KempinDocument2 paginiSS-Standartenführer Hans Wilhelm KempinNilia PustakaÎncă nu există evaluări

- I Favor The Villainess - 02 - (v2)Document263 paginiI Favor The Villainess - 02 - (v2)Abel SotoÎncă nu există evaluări

- Gabriel's Oboe Banda 1 Oboe PDFDocument1 paginăGabriel's Oboe Banda 1 Oboe PDFRod Carb JoaquínÎncă nu există evaluări

- 73 Magazine - May 1963Document100 pagini73 Magazine - May 1963Benjamin Dover100% (1)

- New York Bus MapDocument1 paginăNew York Bus MapSzabÎncă nu există evaluări

- Radio Production Manual - Edited and FormattedDocument152 paginiRadio Production Manual - Edited and FormattedMushtaq Muhammad100% (1)

- Sfbadr Tab PDFDocument11 paginiSfbadr Tab PDFRichard SmithÎncă nu există evaluări

- Lighting Guides LG 5 Lecture, Teaching and Conference Rooms (Includes Addendum 1, 2003)Document63 paginiLighting Guides LG 5 Lecture, Teaching and Conference Rooms (Includes Addendum 1, 2003)Vinay PallivalppilÎncă nu există evaluări

- ALC887Document82 paginiALC887EmmanuelchatoÎncă nu există evaluări

- Engines of Creation - Joe SatrianiDocument8 paginiEngines of Creation - Joe SatrianiJP Pretorius100% (1)

- 05 May 1968 Orr Vertical Corta DobladaDocument100 pagini05 May 1968 Orr Vertical Corta DobladaNestor Alberto EscalaÎncă nu există evaluări

- KoomanDocument8 paginiKoomanJamie KoronkiewiczÎncă nu există evaluări

- How Does DGPS (Differential GPS) Work - RACELOGIC Support CentreDocument10 paginiHow Does DGPS (Differential GPS) Work - RACELOGIC Support CentreMAHESH CHANDÎncă nu există evaluări

- Fender Custo Collection 2012Document12 paginiFender Custo Collection 2012eternal_harpyÎncă nu există evaluări

- Vienna in Your PocketDocument68 paginiVienna in Your PocketccoccinellaÎncă nu există evaluări

- Iphone 7 Iphone 7 PlusDocument12 paginiIphone 7 Iphone 7 PlusJessa BidangÎncă nu există evaluări

- Colin Fraser and Restrepo Estrada - Community Radio HandbookDocument105 paginiColin Fraser and Restrepo Estrada - Community Radio HandbookBurmaClubÎncă nu există evaluări

- Coarse Wavelength Division Multiplexing (CWDM)Document15 paginiCoarse Wavelength Division Multiplexing (CWDM)shridonÎncă nu există evaluări

- Kalisay Tango ArgentinoDocument3 paginiKalisay Tango ArgentinoArmando TantinoÎncă nu există evaluări

- UNITDocument4 paginiUNITHarshJindalÎncă nu există evaluări

- FOX - The X-Files 3x12 - War of The CoprophagesDocument64 paginiFOX - The X-Files 3x12 - War of The CoprophagesAlbertBravoÎncă nu există evaluări

- Web Results: Tinapay NG Buhay (Mga Bagong Awiting Pangmisa) - SpotifyDocument5 paginiWeb Results: Tinapay NG Buhay (Mga Bagong Awiting Pangmisa) - SpotifyKitÎncă nu există evaluări

- PE Lesson 1 - TYPES OF DANCEDocument3 paginiPE Lesson 1 - TYPES OF DANCEBSEdMathGerance, Mary Jane D.Încă nu există evaluări

- Noise Generation in Dynamic Wireless Power TransferDocument4 paginiNoise Generation in Dynamic Wireless Power TransferChristian DavidÎncă nu există evaluări

- Whenever Wherever - ShakiraDocument4 paginiWhenever Wherever - ShakiraDaniel RuedaÎncă nu există evaluări

- Architecture Design 201402Document158 paginiArchitecture Design 201402mihaiarsene100% (2)

- Strong Woman Do Bong Soon: TH THDocument2 paginiStrong Woman Do Bong Soon: TH THajeng rizky agitaÎncă nu există evaluări