Documente Academic

Documente Profesional

Documente Cultură

College of Engineering, Nashik - 4

Încărcat de

Klein Morallos BianesTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

College of Engineering, Nashik - 4

Încărcat de

Klein Morallos BianesDrepturi de autor:

Formate disponibile

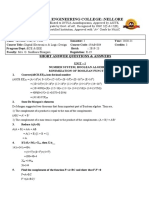

Pune Vidyarthi Griha’s

COLLEGE OF ENGINEERING, NASHIK – 4

COMPUTER ENGINEERING DEPARTMENT

Subject : DELD ASSIGNMENT NO – 03 Unit : III

1. What is ASM? State & explain basic component of ASM Chart. Features of ASM.

2. Draw an ASM Chart & state table of a 2-bit up-down counter having a mode control i/p.

3. Draw the ASM Chart & state diagram for Synchronous circuit having the following

description : The circuit has control input C, Clock & Output x, y, z.

i. If C = 1 Then changes from 000010100110000 & Repeats

ii. If C = 0 Then circuit holds the present state.

4. Explain the Mux Controller Method with an example?

5. A sequential circuit has to count DOWN from ‘111’ to ‘000’. The circuit also has input

‘X’. If X = 0 then the circuit will count DOWN and if X = 1 then they will remain in

current state. Draw an ASM Chart and state table for this circuit and design the circuit to

generate the output using MUX Controller method.

6. Draw ASM Chart for the following state machine : A two bit UP Counter with output

‘Q1Q0’ and enable signal ‘X’ is to be designed. If ‘X’ = 0 counter changes the state as

’00 – 01 – 10 – 11 – 00’. If ‘X’ = 1 , counter should remain in present state. Design your

circuit using JK-FF and suitable MUXs.

7. Design ASM Chart for 4-bit gray code sequence with up-down conditions.

8. Design ASM Chart for 3-bit octal number sequence with up-down condition.

9. Design a sequence generator circuit to generate the sequence 1 – 3 – 5 – 7 using MUX

Controller based ASM approach. Consideration :

i. If C = 0 Then the sequence generator circuit in the same state

ii. If C = 1 Then the sequence generator circuit goes into next state.

10. Design a sequence generator circuit to generate the sequence 1 – 2 - 3 – 7 - 1 using MUX

Controller based ASM approach. Consideration :

iii. If C = 0 Then the sequence generator circuit in the same state

iv. If C = 1 Then the sequence generator circuit goes into next state.

11. What is VHDL? Features of VHDL and its advantages.

12. State the VHDL Program format & entity format. Explain the entity declaration for basic

logic gate and Universal gates.

13. Explain the entity architecture declaration for 2-bit AND, OR, NOR gate.

14. Describe the different Modeling Styles of VHDL with suitable examples.

15. Comparison between dataflow, behavioral and structural modeling.

16. Compare concurrent Vs sequential statements.

17. Write VHDL code for 4:1 MUX. AND Full Adder.

****************** Best of Luck *******************

S-ar putea să vă placă și

- Simulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetDe la EverandSimulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetEvaluare: 2 din 5 stele2/5 (1)

- Simulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetDe la EverandSimulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetÎncă nu există evaluări

- Question Bank DSDDocument6 paginiQuestion Bank DSDJithinmvijayan VijayanÎncă nu există evaluări

- Digital 16 Marks.Document4 paginiDigital 16 Marks.Saranya PrabhuÎncă nu există evaluări

- DCEPFDocument11 paginiDCEPFkanishkhatanaÎncă nu există evaluări

- Deld QB EndsemDocument4 paginiDeld QB EndsemUV New MoviesÎncă nu există evaluări

- EESB423 Sem1 1314 Assignment2Document3 paginiEESB423 Sem1 1314 Assignment2Shamraj KunnasagarÎncă nu există evaluări

- PLC Question BankDocument3 paginiPLC Question BankAjay kumarÎncă nu există evaluări

- TP 1 Computer Systems II - Yonder ArellanoDocument9 paginiTP 1 Computer Systems II - Yonder ArellanoScribdTranslationsÎncă nu există evaluări

- Design A Pulse Mode Circuit Having Two InputDocument4 paginiDesign A Pulse Mode Circuit Having Two InputSiva GuruÎncă nu există evaluări

- Advanced Digital Systems DesignDocument12 paginiAdvanced Digital Systems DesignlawrencerajasekaranÎncă nu există evaluări

- Question Bank Unit 4-1Document3 paginiQuestion Bank Unit 4-1birajkushwaha1996Încă nu există evaluări

- Tut6 PDFDocument1 paginăTut6 PDFArchana TripathiÎncă nu există evaluări

- Capstone ResearchProject Moore Mealy MachineDocument9 paginiCapstone ResearchProject Moore Mealy MachineAnish ChatterjeeÎncă nu există evaluări

- A0601-Digital System Design - 2Document6 paginiA0601-Digital System Design - 2LaxmiPrasad KonchaÎncă nu există evaluări

- Ass1 PDFDocument2 paginiAss1 PDFOsho GeraÎncă nu există evaluări

- Kongunadu College of Engineering and Technology M.E-Applied Electronics Advanced Digital System Design-Assignment-IDocument1 paginăKongunadu College of Engineering and Technology M.E-Applied Electronics Advanced Digital System Design-Assignment-IshankarÎncă nu există evaluări

- ASSIGNMENT 2.docx - VerilogDocument2 paginiASSIGNMENT 2.docx - VerilogfiitnessbynehaÎncă nu există evaluări

- Digital Logic CircuitsDocument7 paginiDigital Logic CircuitsMATHANKUMAR.SÎncă nu există evaluări

- Ap9212 AdsdDocument12 paginiAp9212 AdsdKartheeswaran Arumugam33% (3)

- Power System Control QuestionDocument8 paginiPower System Control QuestionMATHANKUMAR.SÎncă nu există evaluări

- Motor Control TI C2000Document16 paginiMotor Control TI C2000Mohammed BelkheiriÎncă nu există evaluări

- DLC Lab QP Oct2019Document5 paginiDLC Lab QP Oct2019bnatarajÎncă nu există evaluări

- Digital Logic Circuits PDFDocument8 paginiDigital Logic Circuits PDFnaina10691Încă nu există evaluări

- Cw1 (Part1) BriefDocument3 paginiCw1 (Part1) Briefoussama sadkiÎncă nu există evaluări

- WWW - Universityquestions.in: Unit 1 Number Systems and Digital Logic Families Part ADocument7 paginiWWW - Universityquestions.in: Unit 1 Number Systems and Digital Logic Families Part Abunny_589318117Încă nu există evaluări

- Mecha ExamDocument2 paginiMecha Examdereje destaÎncă nu există evaluări

- Assignment EDES232CDocument3 paginiAssignment EDES232CPrakash DasÎncă nu există evaluări

- VHDL ProjectDocument10 paginiVHDL ProjectSalma MohamedÎncă nu există evaluări

- Digital Electronics Question BankDocument6 paginiDigital Electronics Question BankReshna ShowkathÎncă nu există evaluări

- Design A Combinatorial Circuit 863832727868Document5 paginiDesign A Combinatorial Circuit 863832727868Siva Guru0% (1)

- Me010 605 Mechatronics and Control SystemsDocument3 paginiMe010 605 Mechatronics and Control SystemsSreehari VpÎncă nu există evaluări

- Unit 4 PDFDocument59 paginiUnit 4 PDFgkk001Încă nu există evaluări

- ADE Imp QuestionsDocument2 paginiADE Imp QuestionsKishore RÎncă nu există evaluări

- PDFDocument24 paginiPDFOlga Joy Labajo GerastaÎncă nu există evaluări

- FSM ProbDocument3 paginiFSM ProbSouhardya MondalÎncă nu există evaluări

- PS7202-Flexible AC Transmission Systems PDFDocument5 paginiPS7202-Flexible AC Transmission Systems PDF1balamanianÎncă nu există evaluări

- EE-Conventional Paper-IIDocument7 paginiEE-Conventional Paper-IISoumyabrataPatraÎncă nu există evaluări

- DDDC87ECAA084E5DA4D2D77F7DC80391Document5 paginiDDDC87ECAA084E5DA4D2D77F7DC80391Sameer NandagaveÎncă nu există evaluări

- R09-Cmos Analog and Mixed Signal DesignDocument1 paginăR09-Cmos Analog and Mixed Signal DesignbalashyamuÎncă nu există evaluări

- PSOC Model II - Set2Document2 paginiPSOC Model II - Set2Vidhya Priya SenthilÎncă nu există evaluări

- State Graphs For Control NetworksDocument37 paginiState Graphs For Control Networksashudiya100% (1)

- Haramaya University Institute of Technology School of Electrical and Computer EngineeringDocument5 paginiHaramaya University Institute of Technology School of Electrical and Computer Engineeringewnetu kassaÎncă nu există evaluări

- Kings: Subject Code: Subject Name: Unit - IDocument6 paginiKings: Subject Code: Subject Name: Unit - IBalasubramaniam SaravananÎncă nu există evaluări

- Prime-Implicants of The Boolean FunctionDocument3 paginiPrime-Implicants of The Boolean FunctionSiva GuruÎncă nu există evaluări

- Modelling and Simulation of A DC Motor DriveDocument12 paginiModelling and Simulation of A DC Motor DriveMi HoangÎncă nu există evaluări

- Exp 9Document14 paginiExp 9yeisongarcesÎncă nu există evaluări

- Experiment 9 Single Phase InvertersDocument14 paginiExperiment 9 Single Phase InvertersnandhakumarmeÎncă nu există evaluări

- Experiment No.:2: Elec 20001 - Ac Electrical Circuit AnalysisDocument8 paginiExperiment No.:2: Elec 20001 - Ac Electrical Circuit AnalysisramÎncă nu există evaluări

- EE6301-Digital Logic Circuits QBDocument7 paginiEE6301-Digital Logic Circuits QBariv2009Încă nu există evaluări

- Assignment Sequential CircuitsDocument2 paginiAssignment Sequential CircuitsPavan SaiÎncă nu există evaluări

- TWRKV46F150 PMSM SensorlessDocument22 paginiTWRKV46F150 PMSM Sensorlessb_dupÎncă nu există evaluări

- ECNG3016 Practical 2Document13 paginiECNG3016 Practical 2Marlon BoucaudÎncă nu există evaluări

- Power System Control-1Document6 paginiPower System Control-1Venkatesh KumarÎncă nu există evaluări

- VHDL FSM UNIT 5 ET&T 7th SemDocument22 paginiVHDL FSM UNIT 5 ET&T 7th SemDEEPA KUNWARÎncă nu există evaluări

- Ocb 283Document34 paginiOcb 283Karthik VarmaÎncă nu există evaluări

- DGD 9 SolDocument9 paginiDGD 9 SolDolores Makaruina100% (1)

- VSC-FACTS-HVDC: Analysis, Modelling and Simulation in Power GridsDe la EverandVSC-FACTS-HVDC: Analysis, Modelling and Simulation in Power GridsÎncă nu există evaluări

- Some Power Electronics Case Studies Using Matlab Simpowersystem BlocksetDe la EverandSome Power Electronics Case Studies Using Matlab Simpowersystem BlocksetÎncă nu există evaluări

- Simulation of Some Power System, Control System and Power Electronics Case Studies Using Matlab and PowerWorld SimulatorDe la EverandSimulation of Some Power System, Control System and Power Electronics Case Studies Using Matlab and PowerWorld SimulatorÎncă nu există evaluări

- One Last Thing (2011 Documentary)Document30 paginiOne Last Thing (2011 Documentary)Klein Morallos BianesÎncă nu există evaluări

- TRANS WP29 129 Inf06eDocument2 paginiTRANS WP29 129 Inf06eKlein Morallos BianesÎncă nu există evaluări

- Understanding Ip Addressing 3Document21 paginiUnderstanding Ip Addressing 3wrenchguyÎncă nu există evaluări

- IP Addressing3Document19 paginiIP Addressing3Klein Morallos BianesÎncă nu există evaluări

- Chapter12 PDFDocument40 paginiChapter12 PDFKlein Morallos BianesÎncă nu există evaluări

- Process Synchronization: Practice ExercisesDocument4 paginiProcess Synchronization: Practice ExercisesSyed Mohammad RizwanÎncă nu există evaluări

- Understanding Ip Addressing 3Document21 paginiUnderstanding Ip Addressing 3wrenchguyÎncă nu există evaluări

- ConvolutionDocument1 paginăConvolutionKlein Morallos BianesÎncă nu există evaluări

- CodeDocument3 paginiCodeKlein Morallos BianesÎncă nu există evaluări

- Chapter 4 Algorithmic State Machines and Finite State MachinesDocument28 paginiChapter 4 Algorithmic State Machines and Finite State MachinesHeena DhasmanaÎncă nu există evaluări

- Prisoner Face Detecting System A Java Project.Document138 paginiPrisoner Face Detecting System A Java Project.Amit Acharya100% (2)

- Aps Writing GuideDocument7 paginiAps Writing GuideKlein Morallos BianesÎncă nu există evaluări

- Data Communication - CS601 Fall 2004 Assignment 03 SolutionDocument3 paginiData Communication - CS601 Fall 2004 Assignment 03 SolutionKlein Morallos BianesÎncă nu există evaluări

- MicrosequencerDocument38 paginiMicrosequencerJonathan MejiaÎncă nu există evaluări

- Electronic and Circuit DevicesDocument8 paginiElectronic and Circuit DevicesKlein Morallos BianesÎncă nu există evaluări

- Factors: How Time and Interest Affect Money: FoundationsDocument64 paginiFactors: How Time and Interest Affect Money: FoundationsangelicastefanieÎncă nu există evaluări

- Parts PDFDocument10 paginiParts PDFashok PradhanÎncă nu există evaluări

- Section 5 - 4 BJT Circuits at DC PackageDocument34 paginiSection 5 - 4 BJT Circuits at DC PackagedraggonboyÎncă nu există evaluări

- Abb CL-LMRDocument296 paginiAbb CL-LMRInajá FerreiraÎncă nu există evaluări

- Logic Design Concepts: Zainalabedin NavabiDocument110 paginiLogic Design Concepts: Zainalabedin NavabiNiXiaohanÎncă nu există evaluări

- 74 Series Logic ICsDocument6 pagini74 Series Logic ICsanon-466841Încă nu există evaluări

- Datasheet ICE2QS03 V22 20110704Document19 paginiDatasheet ICE2QS03 V22 20110704Alvaro Jose ArgumedoÎncă nu există evaluări

- Time Operated Electrical Appliance Control SystemDocument82 paginiTime Operated Electrical Appliance Control Systempoozu100% (1)

- DELD - Short Answer Questions and AnswersDocument23 paginiDELD - Short Answer Questions and AnswersPasupuleti Venkata RamanaÎncă nu există evaluări

- LC72131-AM FM-PLL Frequency Synthesizer-Denon's TunersDocument23 paginiLC72131-AM FM-PLL Frequency Synthesizer-Denon's TunersRayner MihailovÎncă nu există evaluări

- PLC Solution BookDocument49 paginiPLC Solution BookJagadeesh Rajamanickam71% (14)

- Lec12 Basic Computer OrganizationDocument75 paginiLec12 Basic Computer OrganizationAya AbdAllah AmmarÎncă nu există evaluări

- Simulation and Synthesis Techniques For Asynchronous FIFO DesignDocument24 paginiSimulation and Synthesis Techniques For Asynchronous FIFO DesignKavyashreeMÎncă nu există evaluări

- Final Syllabus ICE 3rd Semester4,5,6,7,8Document106 paginiFinal Syllabus ICE 3rd Semester4,5,6,7,8Arup ChowdhuryÎncă nu există evaluări

- Vidyarthi Plus Digital ElectronicsDocument58 paginiVidyarthi Plus Digital Electronicsnaveenbabu19Încă nu există evaluări

- Experiment No: 1 HDL Code To Realize All The Logic Gates: Name: A.Vineela Reddy Date: HT N0.: 16H61A04C6 Page No.Document49 paginiExperiment No: 1 HDL Code To Realize All The Logic Gates: Name: A.Vineela Reddy Date: HT N0.: 16H61A04C6 Page No.Suraj AnanthulaÎncă nu există evaluări

- HEF4020B: 1. General DescriptionDocument11 paginiHEF4020B: 1. General DescriptionIury GuedesÎncă nu există evaluări

- LCD Interfacing With Microcontroller 8051Document50 paginiLCD Interfacing With Microcontroller 8051Darshan Vala100% (2)

- DE LAB Question BankDocument2 paginiDE LAB Question BankMalayalam TechÎncă nu există evaluări

- Data Sheet 5460 ADocument54 paginiData Sheet 5460 AredtronicÎncă nu există evaluări

- Cobol ESDocument40 paginiCobol ESfransuescleyÎncă nu există evaluări

- PLC Project ReportDocument18 paginiPLC Project ReportMayowaÎncă nu există evaluări

- Siemens PLC Counters and Comparators LogicDocument10 paginiSiemens PLC Counters and Comparators LogicleosenthilÎncă nu există evaluări

- Quiz QuestionsDocument40 paginiQuiz QuestionsHarold Wilson0% (1)

- Kepware Mitsubishi FXDocument20 paginiKepware Mitsubishi FXlue-ookÎncă nu există evaluări

- UNIT4Document32 paginiUNIT4Azliana Mohd Taib100% (1)

- 8035Document103 pagini8035Dan EsentherÎncă nu există evaluări

- Digital Electronics ExamDocument4 paginiDigital Electronics ExamAlbin peterÎncă nu există evaluări

- Data Blocks in Simatic Step 7 SiemensDocument12 paginiData Blocks in Simatic Step 7 SiemensAhmed AlnagarÎncă nu există evaluări

- ENCODER Troubleshooting-Guide PDFDocument2 paginiENCODER Troubleshooting-Guide PDFdorin serbanÎncă nu există evaluări

- Digital System Design Syllabus For EC 3 Sem 2018 Scheme - VTU CBCS 18EC34 SyllabusDocument2 paginiDigital System Design Syllabus For EC 3 Sem 2018 Scheme - VTU CBCS 18EC34 SyllabusSYAMALA100% (1)

- Nike Triax300 - 250 - 120Document15 paginiNike Triax300 - 250 - 120durrutino pardoÎncă nu există evaluări

- Number System and CodesDocument5 paginiNumber System and CodesPavan KumarÎncă nu există evaluări