Documente Academic

Documente Profesional

Documente Cultură

Debugger stm8 PDF

Încărcat de

betodias30Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Debugger stm8 PDF

Încărcat de

betodias30Drepturi de autor:

Formate disponibile

STM8 Debugger

TRACE32 Online Help

TRACE32 Directory

TRACE32 Index

TRACE32 Documents ......................................................................................................................

ICD In-Circuit Debugger ................................................................................................................

Processor Architecture Manuals ..............................................................................................

STM8 .........................................................................................................................................

STM8 Debugger .................................................................................................................... 1

History ................................................................................................................................ 3

Introduction ....................................................................................................................... 4

Brief Overview of Documents for New Users 4

Demo and Start-up Script 4

Configuration ..................................................................................................................... 5

System Overview 5

Warning .............................................................................................................................. 6

Quick Start ......................................................................................................................... 7

Troubleshooting ................................................................................................................ 9

FAQ ..................................................................................................................................... 10

Debugger 10

STM8 specific SYStem Settings ....................................................................................... 12

SYStem.CPU Select the used CPU 12

SYStem.CpuAccess Run-time memory access (intrusive) 12

SYStem.MemAccess Real-time memory access (non-intrusive) 13

SYStem.Mode Establish the communication with the target 13

SYStem.LOCK Lock and tristate the debug port 13

SYStem.Option IMASKASM Disable interrupts while single stepping 14

SYStem.Option IMASKHLL Disable interrupts while HLL single stepping 14

STM8 specific TrOnchip Command ................................................................................. 15

TrOnchip.VarCONVert Adjust complex breakpoint in on-chip resource 15

Breakpoints ........................................................................................................................ 16

Software breakpoints 16

On-chip breakpoints for instructions 16

On-chip breakpoints for data 16

Memory Classes ................................................................................................................ 17

©1989-2018 Lauterbach GmbH

STM8 Debugger 1

Target Adaption ................................................................................................................. 18

Connector Type and Pinout 18

Support ............................................................................................................................... 18

Available Tools 19

Compilers 22

Products ............................................................................................................................. 23

Product Information 23

Order Information 23

©1989-2018 Lauterbach GmbH

STM8 Debugger 2

STM8 Debugger

Version 16-Nov-2018

History

14-Feb-18 New manual.

©1989-2018 Lauterbach GmbH

STM8 Debugger 3

Introduction

This document serves as a guideline for debugging STM8 MCUs and describes all MCU-specific

TRACE32 settings and features.

Please keep in mind that only the Processor Architecture Manual (the document you are reading at the

moment) is CPU specific, while all other parts of the online help are generic for all CPUs supported by

Lauterbach. So if there are questions related to the CPU, the Processor Architecture Manual should be your

first choice.

Brief Overview of Documents for New Users

Architecture-independent information:

• “Debugger Basics - Training” (training_debugger.pdf): Get familiar with the basic features of a

TRACE32 debugger.

• “T32Start” (app_t32start.pdf): T32Start assists you in starting TRACE32 PowerView instances

for different configurations of the debugger. T32Start is only available for Windows.

• “General Commands” (general_ref_<x>.pdf): Alphabetic list of debug commands.

Architecture-specific information:

• “Processor Architecture Manuals”: These manuals describe commands that are specific for the

processor architecture supported by your debug cable. To access the manual for your processor

architecture, proceed as follows:

- Choose Help menu > Processor Architecture Manual.

• “OS Awareness Manuals” (rtos_<os>.pdf): TRACE32 PowerView can be extended for operating

system-aware debugging. The appropriate OS Awareness manual informs you how to enable the

OS-aware debugging.

Demo and Start-up Script

The on-chip FLASH and the EEProm memory can be programmed via the stm8.cmm script:

CD.DO ~~/demo/stm8/flash/stm8.cmm

Please be aware that you should check the Flash and EEProm size specified for your MCU in the stm8.cmm

before executing this script.

©1989-2018 Lauterbach GmbH

STM8 Debugger 4

Configuration

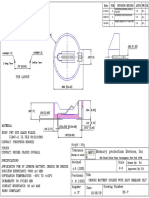

System Overview

Example configuration for an STM8 debugger.

PC

Windows / Linux / Mac OS

Target

Debug Cable

PODBUS IN

POWER DEBUG USB INTERFACE / USB 3

USB LAUTERBACH

Connector

POWER

SELECT

Cable

Debug

TRIG

EMULATE

DEBUG CABLE

DEBUG CABLE

USB

LAUTERBACH

POWER

7-9V

PODBUS OUT

POWER DEBUG INTERFACE / USB 3

AC/DC Adapter

©1989-2018 Lauterbach GmbH

STM8 Debugger 5

Warning

NOTE: To prevent debugger and target from damage it is recommended to connect or

disconnect the debug cable only while the target power is OFF.

Recommendation for the software start:

1. Disconnect the debug cable from the target while the target power is

off.

2. Connect the host system, the TRACE32 hardware and the debug

cable.

3. Power ON the TRACE32 hardware.

4. Start the TRACE32 software to load the debugger firmware.

5. Connect the debug cable to the target.

6. Switch the target power ON.

7. Configure your debugger e.g. via a start-up script.

Power down:

1. Switch off the target power.

2. Disconnect the debug cable from the target.

3. Close the TRACE32 software.

4. Power OFF the TRACE32 hardware.

©1989-2018 Lauterbach GmbH

STM8 Debugger 6

Quick Start

Starting up the debugger is done as follows:

1. Select the device prompt B (BDM debugger) and reset TRACE32.

B::

RESet

The device prompt B:: is normally already selected in the command line. If this is not the case enter

B:: to set the correct device prompt. The RESet command is only necessary if you do not start

directly after booting the TRACE32 development tool.

2. Specify the CPU specific settings.

SYStem.CPU STM8S005K6

This command selects the CPU type.

3. Inform the debugger about cashable address range (FLASH/EEPROM)..

MAP.UpdateOnce p:0x8000--0xffff

This is important to speed up the T32 GUI responsiveness. The specified address range will be

accesses only once after a break, thus avoiding unnecessary memory accesses.

4. Reset the target and enter debug mode.

SYStem.Mode Up

This command resets the CPU on the target, enables On-Chip-Debug Mode and issues a breakpoint

right after the reset interrupt routine.The CPU stops executing any instruction, and the user is able to

download the code and test. After this command is executed, it is possible to access memory and

registers.

©1989-2018 Lauterbach GmbH

STM8 Debugger 7

5. Load the program into the flash.

DO ~~/demo/stm8/flash/stm8.cmm

A typical start sequence of the STM8 is shown below. This sequence can be written to an ASCII file (script

file) and executed with the command DO <filename>.

B:: ; Select the ICD device prompt

RESet ; Reset the TRACE32 software

MAP.UpdateOnce p:0x8000-- ; Specify the address range for caching

0xffff

WinCLEAR ; Clear all windows

SYStem.Up ; Reset the target and enter debug mode

DO ; Load the target application into the

~~/demo/stm8/flash/stm8.cmm Flash

PER.view ; Show clearly arranged peripherals

; in window *)

Data.List ; Open source code window *)

Register.view /SpotLight ; Open register window *)

Frame.view /Locals /Caller ; Open the stack frame with

; local variables *)

Var.Watch %SpotLight flags ast ; Open watch window for variables *)

Break.Set 0x1000 /Program ; Set software breakpoint to address

; 1000 (address 1000 is within RAM

; address range)

Break.Set 0x101000 /Program ; Set on-chip breakpoint

; to address 101000 (address 101000 is

; within Flash address range)

*) These commands open windows on the screen. The window position can be specified with the WinPOS

command.

©1989-2018 Lauterbach GmbH

STM8 Debugger 8

Troubleshooting

Error Message Event Reason

target power fail SYStem.Mode.Up See below.

target processor in reset SYStem.Down See below.

Target is not connected SYStem.Mode.Up The debugger expects to receive a

or the SWD Interface is SYStem.Mode.Go confirmation for each command sent to

returning an error. the target. An error occurs in case the

confirmation is not received.

The number of No special event Internal error, please consult your

<number> accessed Lauterbach representative.

bytes in memory is not a

multiple of the access

<size> bytes.

Memory <address> is No special event Internal error, please consult your

not aligned to access Lauterbach representative.

<size>.

Invalid memory access No special event Internal error, please consult your

size: <size> bytes (@ Lauterbach representative.

<address>)

Memory access timeout: No special event Corrupted JTAG connection. Check

Reading from JTAG hardware and settings.

<address>

Typically the SYStem.Up command is the first command of a debug session where communication with the

target is required. If you receive error messages like “debug port fail” or “debug port time out” while executing

this command, this may have the reasons below. “target processor in reset” is just a follow-up error

message.

• Open the AREA.view window to display all error messages.

• If the target has no power or the debug cable is not connected to the target, this results in the

error message “target power fail”.

• Did you select the correct core type SYStem.CPU <type>?

• There is an issue with the SWD interface. Maybe there is the need to set jumpers on the target to

connect the correct signals to the SWD connector.

• The target is in an unrecoverable state. Re-power your target and try again.

• The core is kept in reset.

• There is a watchdog which needs to be deactivated.

©1989-2018 Lauterbach GmbH

STM8 Debugger 9

FAQ

Debugger

Debugging via

The debugger is accessed via Internet/VPN and the performance is very

VPN

slow. What can be done to improve debug performance?

Ref: 0307

The main cause for bad debug performance via Internet or VPN are low data

throughput and high latency. The ways to improve performance by the debugger

are limited:

In PRACTICE scripts, use "SCREEN.OFF" at the beginning of the script

and "SCREEN.ON" at the end. "SCREEN.OFF" will turn off screen

updates. Please note that if your program stops (e.g. on error) without exe-

cuting "SCREEN.OFF", some windows will not be updated.

"SYStem.POLLING SLOW" will set a lower frequency for target state

checks (e.g. power, reset, jtag state). It will take longer for the debugger to

recognize that the core stopped on a breakpoint.

"SETUP.URATE 1.s" will set the default update frequency of

Data.List/Data.dump/Variable windows to 1 second (the slowest possible

setting).

prevent unneeded memory accesses using "MAP.UPDATEONCE

[address-range]" for RAM and "MAP.CONST [address--range]" for

ROM/FLASH. Address ranged with "MAP.UPDATEONCE" will read the

specified address range only once after the core stopped at a breakpoint or

manual break. "MAP.CONST" will read the specified address range only

once per SYStem.Mode command (e.g. SYStem.Up).

©1989-2018 Lauterbach GmbH

STM8 Debugger 10

Setting a

What can be the reasons why setting a software breakpoint fails?

Software

Breakpoint fails Setting a software breakpoint can fail when the target HW is not able to

Ref: 0276

implement the wanted breakpoint.

Possible reasons:

The wanted breakpoint needs special features that are only possible to

realize by the trigger unit inside the controller.

Example: Read, write and access (Read/Write) breakpoints ("type" in Break.Set

window). Breakpoints with checking in real-time for data-values ("Data").

Breakpoints with special features ("action") like TriggerTrace, TraceEnable,

TraceOn/TraceOFF.

TRACE32 can not change the memory.

Example: ROM and Flash when no preparation with FLASH.Create,

FLASH.TARGET and FLASH.AUTO was made. All type of memory if the

memory device is missing the necessary control signals like WriteEnable or

settings of registers and SpecialFunctionRegisters (SFR).

Contrary settings in TRACE32.

Like: MAP.BOnchip for this memory range. Break.SELect.<breakpoint-type>

Onchip (HARD is only available for ICE and FIRE).

RTOS and MMU:

If the memory can be changed by Data.Set but the breakpoint doesn't work it

might be a problem of using an MMU on target when setting the breakpoint to a

symbolic address that is different than the writable and intended memory

location.

©1989-2018 Lauterbach GmbH

STM8 Debugger 11

STM8 specific SYStem Settings

SYStem.CPU Select the used CPU

Format: SYStem.CPU <cpu>

<cpu>: STM8S005K6 | STM8S003K3 | STM8S001J3 | …

Default: STM8xxx.

Selects the processor type. All of the STM8 MCU cores with SWD Interface are supported.

SYStem.CpuAccess Run-time memory access (intrusive)

Format: SYStem.CpuAccess Enable | Denied | Nonstop

Default: Denied.

Enable Allow intrusive run-time memory access.

In order to perform a memory read or write while the CPU is executing a

program, the debugger stops the program execution shortly. Each short

stop takes 1 … 100 ms depending on the speed of the debug interface

and on the number of the read/write accesses required.

A red S in the state line of the TRACE32 screen indicates this intrusive

behavior of the debugger.

Denied Do not allow intrusive run-time memory access.

Nonstop Lock all features of the debugger that affect the run-time behavior.

Nonstop reduces the functionality of the debugger to:

• Run-time access to memory and variables

• Trace display

The debugger inhibits the following:

• To stop the program execution

• All features of the debugger that are intrusive (e.g. action Spot for

breakpoints, performance analysis via StopAndGo mode, condi-

tional breakpoints etc.)

©1989-2018 Lauterbach GmbH

STM8 Debugger 12

SYStem.MemAccess Real-time memory access (non-intrusive)

Format: SYStem.MemAccess CPU | Denied

Default: Denied.

CPU This option is not available at the moment.

Denied Real-time memory access during program execution to target is disabled.

SYStem.Mode Establish the communication with the target

Format: SYStem.Mode <mode>

<mode>: Down

Go

Up

Default: Down.

Down Disables the debugger. The state of the CPU remains unchanged.

Go Resets the target and starts execution.

Up Resets the target and stops the CPU at the reset vector.

SYStem.LOCK Lock and tristate the debug port

Format: SYStem.LOCK [ON | OFF]

Default: OFF

If the system is locked, no access to the debug port will be performed by the debugger. While locked, the

debug connector of the debugger is tristated. The main intention of the SYStem.Lock command is to give

debug access to another tool.

©1989-2018 Lauterbach GmbH

STM8 Debugger 13

SYStem.Option IMASKASM Disable interrupts while single stepping

Format: SYStem.Option IMASKASM [ON | OFF]

Default: OFF.

If enabled, the interrupt enable flag of the EFLAGS register will be cleared during assembler single-step

operations. After the single step, the interrupt enable flag is restored to the value it had before the step. It is

turned on to make sure that no interrupt routine is serviced between break and go states.

SYStem.Option IMASKHLL Disable interrupts while HLL single stepping

Format: SYStem.Option IMASKHLL [ON | OFF]

Default: OFF.

If enabled, the interrupt enable flag of the EFLAGS register will be cleared during HLL single-step

operations. After the single step, the interrupt enable flag is restored to the value it had before the step.

©1989-2018 Lauterbach GmbH

STM8 Debugger 14

STM8 specific TrOnchip Command

TrOnchip.VarCONVert Adjust complex breakpoint in on-chip resource

Format: TrOnchip.VarCONVert [ON | OFF]

The on-chip breakpoints can only cover specific ranges. If you want to set a marker or breakpoint to a

complex variable, the on-chip break resources of the CPU may be not powerful enough to cover the whole

structure. If the option TrOnchip.VarCONVert is set to ON, the breakpoint will automatically be converted

into a single address breakpoint. This is the default setting. Otherwise an error message is generated.

©1989-2018 Lauterbach GmbH

STM8 Debugger 15

Breakpoints

Software breakpoints

The Microchip STM8 architecture does not support software breakpoints.

On-chip breakpoints for instructions

The STM8 MCUs support a total of two on-chip breakpoint registers which can be used as program

breakpoints to stop and debug the program which executes always in the Flash.

On-chip breakpoints for data

Data breakpoints are used to analyze the read and write accesses to global variables. The data breakpoints

can be triggered with respect to the data address or access type, i.e. read, write or both, or the data value.

The two instruction breakpoints of STM8 MCUs can be used as data breakpoints

In case of an on-chip data breakpoint, every load and store instruction is checked with respect to the

breakpoint address, access type and the value. The data breakpoints are especially useful to find out when

a global variable is written with a certain value. It is not possible to implement a similar breakpoint in software

without affecting the real-time behavior of the system. Since the load and store instructions work on RAM,

data breakpoints always point to addresses on RAM.

©1989-2018 Lauterbach GmbH

STM8 Debugger 16

Memory Classes

The following memory access classes are available:

Access Class Description

D Data

P Program

To access a memory class, write the class in front of the address. For example, use D to access the data

memory

Data.dump D:0x00

The memory class P is used to denote the Flash memory.

Data.dump P:0x00

Since the STM8 architecture uses a Unified Memory Architecture, the following two examples return the

same results.

Data.dump D:0x100

Data.dump P:0x100

©1989-2018 Lauterbach GmbH

STM8 Debugger 17

Target Adaption

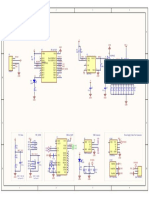

Connector Type and Pinout

Debug Cable

Pin Signal

1 VDD

2 PD1

3 GND

4 RESET[PA0]

Support

Lauterbach technical support is available via www.lauterbach.com/tsupport.html.

©1989-2018 Lauterbach GmbH

STM8 Debugger 18

Available Tools

INSTRUCTION

INTEGRATOR

SIMULATOR

MONITOR

POWER

DEBUG

TRACE

FIRE

CPU

ICD

ICD

ICD

ICE

STM8AF5268 YES

STM8AF5269 YES

STM8AF5286 YES

STM8AF5288 YES

STM8AF5289 YES

STM8AF528A YES

STM8AF52A6 YES

STM8AF52A8 YES

STM8AF52A9 YES

STM8AF52AA YES

STM8AF6213 YES

STM8AF6213A YES

STM8AF6223 YES

STM8AF6223A YES

STM8AF6226 YES

STM8AF6246 YES

STM8AF6248 YES

STM8AF6266 YES

STM8AF6268 YES

STM8AF6269 YES

STM8AF6286 YES

STM8AF6288 YES

STM8AF6289 YES

STM8AF628A YES

STM8AF62A6 YES

STM8AF62A8 YES

STM8AF62A9 YES

STM8AF62AA YES

STM8AF6366 YES

STM8AF6388 YES

STM8AL3136 YES

STM8AL3138 YES

STM8AL3146 YES

STM8AL3148 YES

STM8AL3166 YES

STM8AL3168 YES

STM8AL3188 YES

STM8AL3189 YES

©1989-2018 Lauterbach GmbH

STM8 Debugger 19

INSTRUCTION

INTEGRATOR

SIMULATOR

MONITOR

POWER

DEBUG

TRACE

FIRE

CPU

ICD

ICD

ICD

ICE

STM8AL318A YES

STM8AL31E88 YES

STM8AL31E89 YES

STM8AL31E8A YES

STM8AL3L46 YES

STM8AL3L48 YES

STM8AL3L66 YES

STM8AL3L68 YES

STM8AL3L88 YES

STM8AL3L89 YES

STM8AL3L8A YES

STM8AL3LE88 YES

STM8AL3LE89 YES

STM8AL3LE8A YES

STM8L001J3 YES

STM8L051F3 YES

STM8L052C6 YES

STM8L052R8 YES

STM8L101F1 YES

STM8L101F2 YES

STM8L101F3 YES

STM8L101G2 YES

STM8L101G3 YES

STM8L101K3 YES

STM8L151C2 YES

STM8L151C3 YES

STM8L151C4 YES

STM8L151C6 YES

STM8L151C8 YES

STM8L151F2 YES

STM8L151F3 YES

STM8L151G2 YES

STM8L151G3 YES

STM8L151G4 YES

STM8L151G6 YES

STM8L151K2 YES

STM8L151K3 YES

STM8L151K4 YES

STM8L151K6 YES

STM8L151M8 YES

STM8L151R6 YES

©1989-2018 Lauterbach GmbH

STM8 Debugger 20

INSTRUCTION

INTEGRATOR

SIMULATOR

MONITOR

POWER

DEBUG

TRACE

FIRE

CPU

ICD

ICD

ICD

ICE

STM8L151R8 YES

STM8L152C4 YES

STM8L152C6 YES

STM8L152C8 YES

STM8L152K4 YES

STM8L152K6 YES

STM8L152K8 YES

STM8L152M8 YES

STM8L152R6 YES

STM8L152R8 YES

STM8L162M8 YES

STM8L162R8 YES

STM8S001J3 YES

STM8S003F3 YES

STM8S003K3 YES

STM8S005C6 YES

STM8S005K6 YES

STM8S007C8 YES

STM8S103F2 YES

STM8S103F3 YES

STM8S103K3 YES

STM8S105C4 YES

STM8S105C6 YES

STM8S105K4 YES

STM8S105K6 YES

STM8S105S4 YES

STM8S105S6 YES

STM8S207C6 YES

STM8S207C8 YES

STM8S207CB YES

STM8S207K6 YES

STM8S207K8 YES

STM8S207M8 YES

STM8S207MB YES

STM8S207R6 YES

STM8S207R8 YES

STM8S207RB YES

STM8S207S6 YES

STM8S207S8 YES

STM8S207SB YES

STM8S208C6 YES

©1989-2018 Lauterbach GmbH

STM8 Debugger 21

INSTRUCTION

INTEGRATOR

SIMULATOR

MONITOR

POWER

DEBUG

TRACE

FIRE

CPU

ICD

ICD

ICD

ICE

STM8S208C8 YES

STM8S208CB YES

STM8S208MB YES

STM8S208R6 YES

STM8S208R8 YES

STM8S208RB YES

STM8S208S6 YES

STM8S208S8 YES

STM8S208SB YES

STM8S903F3 YES

STM8S903K3 YES

STM8SPLNB1 YES

STM8TL52F4 YES

STM8TL52G4 YES

STM8TL53C4 YES

STM8TL53F4 YES

STM8TL53G4 YES

Compilers

Language Compiler Company Option Comment

C STM8 Cosmic Software ELF/DWARF

C STM8 IAR Systems AB ELF/DWARF

C STM8 Raisonance ELF/DWARF

C STM8 Small Device C ELF/DWARF

Compiler

©1989-2018 Lauterbach GmbH

STM8 Debugger 22

Products

Product Information

OrderNo Code Text

LA-2719 Debugger for STM8 (ICD)

DEBUG-STM8 supports STM8

includes software for Windows, Linux and MacOSX

requires Power Debug Module

LA-2731 Converter ARM20 to STM8 4 Pin Connector

CONV-ARM20-STM8-4 supports STM8 4 pin connector

Order Information

Order No. Code Text

LA-2719 DEBUG-STM8 Debugger for STM8 (ICD)

LA-2731 CONV-ARM20-STM8-4 Converter ARM20 to STM8 4 Pin Connector

©1989-2018 Lauterbach GmbH

STM8 Debugger 23

S-ar putea să vă placă și

- Programming the Intel Galileo: Getting Started with the Arduino -Compatible Development BoardDe la EverandProgramming the Intel Galileo: Getting Started with the Arduino -Compatible Development BoardEvaluare: 5 din 5 stele5/5 (1)

- Hands-On ZigBee: Implementing 802.15.4 with MicrocontrollersDe la EverandHands-On ZigBee: Implementing 802.15.4 with MicrocontrollersÎncă nu există evaluări

- 40-Pin IDE Flash Module Installation GuideDocument1 pagină40-Pin IDE Flash Module Installation GuideSergioMesquita01Încă nu există evaluări

- Starting STM8 MicrocontrollersDocument126 paginiStarting STM8 MicrocontrollersTushar Shenoy100% (1)

- I2c 1602 LCDDocument8 paginiI2c 1602 LCDnarwres barhoumiÎncă nu există evaluări

- ST Visual Develop (STVD)Document363 paginiST Visual Develop (STVD)api-3697475Încă nu există evaluări

- Guitar Rig 2 Manual EnglishDocument143 paginiGuitar Rig 2 Manual EnglishDavid SantinhoÎncă nu există evaluări

- Arduino Software Internals: A Complete Guide to How Your Arduino Language and Hardware Work TogetherDe la EverandArduino Software Internals: A Complete Guide to How Your Arduino Language and Hardware Work TogetherÎncă nu există evaluări

- Arduino Esp8266Document89 paginiArduino Esp8266Carlos NiñoÎncă nu există evaluări

- Beginning Arduino Nano 33 IoT: Step-By-Step Internet of Things ProjectsDe la EverandBeginning Arduino Nano 33 IoT: Step-By-Step Internet of Things ProjectsÎncă nu există evaluări

- Bitcoin and Lightning Network on Raspberry Pi: Running Nodes on Pi3, Pi4 and Pi ZeroDe la EverandBitcoin and Lightning Network on Raspberry Pi: Running Nodes on Pi3, Pi4 and Pi ZeroÎncă nu există evaluări

- Embedded Systems: ARM Programming and OptimizationDe la EverandEmbedded Systems: ARM Programming and OptimizationÎncă nu există evaluări

- 1701ad Gold ManualDocument32 pagini1701ad Gold ManualSingensaiÎncă nu există evaluări

- Raspberry Pi for Arduino Users: Building IoT and Network Applications and DevicesDe la EverandRaspberry Pi for Arduino Users: Building IoT and Network Applications and DevicesÎncă nu există evaluări

- The Definitive Guide to How Computers Do Math: Featuring the Virtual DIY CalculatorDe la EverandThe Definitive Guide to How Computers Do Math: Featuring the Virtual DIY CalculatorÎncă nu există evaluări

- GetStarted STM8 ST7Document44 paginiGetStarted STM8 ST7Jesus Almanzar Santos100% (1)

- Rust for the IoT: Building Internet of Things Apps with Rust and Raspberry PiDe la EverandRust for the IoT: Building Internet of Things Apps with Rust and Raspberry PiÎncă nu există evaluări

- Olly ScriptDocument5 paginiOlly Scriptj_humbsÎncă nu există evaluări

- Themida - Winlicense Ultra Unpacker 1.4Document270 paginiThemida - Winlicense Ultra Unpacker 1.4VirlanRoberttÎncă nu există evaluări

- Hands-on TinyML: Harness the power of Machine Learning on the edge devices (English Edition)De la EverandHands-on TinyML: Harness the power of Machine Learning on the edge devices (English Edition)Evaluare: 5 din 5 stele5/5 (1)

- Advanced Home Automation Using Raspberry Pi: Building Custom Hardware, Voice Assistants, and Wireless NodesDe la EverandAdvanced Home Automation Using Raspberry Pi: Building Custom Hardware, Voice Assistants, and Wireless NodesÎncă nu există evaluări

- BeagleBone BlackDocument117 paginiBeagleBone Blackjupiter8053Încă nu există evaluări

- Body Area Networks using IEEE 802.15.6: Implementing the ultra wide band physical layerDe la EverandBody Area Networks using IEEE 802.15.6: Implementing the ultra wide band physical layerÎncă nu există evaluări

- Arduino UNO WorkingDocument6 paginiArduino UNO WorkingSssÎncă nu există evaluări

- Beginning STM32: Developing with FreeRTOS, libopencm3 and GCCDe la EverandBeginning STM32: Developing with FreeRTOS, libopencm3 and GCCÎncă nu există evaluări

- Surveillance With Face Recognition Door LockDocument26 paginiSurveillance With Face Recognition Door LockAkashÎncă nu există evaluări

- ST7 Software ToolsetDocument4 paginiST7 Software Toolsetapi-3697475100% (2)

- (Ebook - PDF - Hack) Advanced Hardware HackingDocument20 pagini(Ebook - PDF - Hack) Advanced Hardware HackingogmpsqjuÎncă nu există evaluări

- An Event-Driven Arduino QP-nanoDocument33 paginiAn Event-Driven Arduino QP-nanoEldglay Da Silva DomingosÎncă nu există evaluări

- 2 Minute Read Published: 2015-08-16: Arduino-MenusystemDocument3 pagini2 Minute Read Published: 2015-08-16: Arduino-MenusystemMatt VennÎncă nu există evaluări

- HP Dv5 Caps Lock - BlinkDocument3 paginiHP Dv5 Caps Lock - Blinkbratu_ovidiuÎncă nu există evaluări

- Foundation Course for Advanced Computer StudiesDe la EverandFoundation Course for Advanced Computer StudiesÎncă nu există evaluări

- DEFCON 21 Grand JTAGulator PDFDocument62 paginiDEFCON 21 Grand JTAGulator PDFhisohisoÎncă nu există evaluări

- Software Defined Radio: The Software Communications ArchitectureDe la EverandSoftware Defined Radio: The Software Communications ArchitectureÎncă nu există evaluări

- A Short and Simple Guide To Bootloading The Attiny-85 or 45Document4 paginiA Short and Simple Guide To Bootloading The Attiny-85 or 45StephanieAnnRosales100% (1)

- Arduino The Object WayDocument23 paginiArduino The Object Wayopenjavier5208Încă nu există evaluări

- Linux Driver Development For Embedded Processors: ST STM32MP1 Practical Labs SetupDocument22 paginiLinux Driver Development For Embedded Processors: ST STM32MP1 Practical Labs SetupRonaldMartinezÎncă nu există evaluări

- Arduino - SPIDocument4 paginiArduino - SPIMuhammad Fikri100% (1)

- S8254A E.en - PTDocument24 paginiS8254A E.en - PTleandroÎncă nu există evaluări

- Data Recovery Hardware A Complete Guide - 2021 EditionDe la EverandData Recovery Hardware A Complete Guide - 2021 EditionÎncă nu există evaluări

- Developing Practical Wireless ApplicationsDe la EverandDeveloping Practical Wireless ApplicationsEvaluare: 5 din 5 stele5/5 (2)

- Boot Reference ListDocument6 paginiBoot Reference ListAdal Broke TruthsÎncă nu există evaluări

- ATtiny Examples For ProgramingDocument10 paginiATtiny Examples For ProgramingLeo MilosevÎncă nu există evaluări

- MAC OS X UNIX Toolbox: 1000+ Commands for the Mac OS XDe la EverandMAC OS X UNIX Toolbox: 1000+ Commands for the Mac OS XÎncă nu există evaluări

- 25 Useful Arduino Shields That You Might Need To Get - Random Nerd TutorialsDocument30 pagini25 Useful Arduino Shields That You Might Need To Get - Random Nerd TutorialsRadismel Salazar FudichelisÎncă nu există evaluări

- About Software ToolsDocument40 paginiAbout Software ToolsFurqon Madaz XskaMaticÎncă nu există evaluări

- BS-7-Suporte CR2032Document1 paginăBS-7-Suporte CR2032betodias30Încă nu există evaluări

- DataSheet SKN 20 02234940Document3 paginiDataSheet SKN 20 02234940Engenheiro TeslandoÎncă nu există evaluări

- Ah49e 1317872Document11 paginiAh49e 1317872betodias30Încă nu există evaluări

- A1324 5 6 DatasheetDocument12 paginiA1324 5 6 DatasheetJuan Pablo Merck SifontesÎncă nu există evaluări

- Active Load PAL Tester Schematic v0.6Document1 paginăActive Load PAL Tester Schematic v0.6betodias30Încă nu există evaluări

- DECODING HT6P20 WITH Attachinterrupt Arduino Forum PDFDocument6 paginiDECODING HT6P20 WITH Attachinterrupt Arduino Forum PDFbetodias30Încă nu există evaluări

- An826 - Sold Pads Vishay RecommendationDocument40 paginiAn826 - Sold Pads Vishay Recommendationbetodias30Încă nu există evaluări

- Status ReportDocument1 paginăStatus Reportbetodias30Încă nu există evaluări

- VSE-DB0069-1009 NTC Thermistors - INTERACTIVE PDFDocument141 paginiVSE-DB0069-1009 NTC Thermistors - INTERACTIVE PDFbetodias30Încă nu există evaluări

- NTC ncp18Document10 paginiNTC ncp18betodias30Încă nu există evaluări

- 3000 Problemas de CircuitosDocument768 pagini3000 Problemas de Circuitosbetodias30Încă nu există evaluări

- NOUVEAucPIC PDFDocument684 paginiNOUVEAucPIC PDFbabiloneÎncă nu există evaluări

- Infineon AN2016 10 CIPOS Mini Technical Description An v02 41 enDocument45 paginiInfineon AN2016 10 CIPOS Mini Technical Description An v02 41 enbetodias30Încă nu există evaluări

- Measuring Speed and Position With A Quadrature EncoderDocument3 paginiMeasuring Speed and Position With A Quadrature Encoderbetodias30Încă nu există evaluări

- En - cd00296680 PWM Stm8sDocument7 paginiEn - cd00296680 PWM Stm8sbetodias30Încă nu există evaluări

- Display 20x4 TC2004A-01Document2 paginiDisplay 20x4 TC2004A-01betodias30Încă nu există evaluări

- MAX038Document17 paginiMAX038Brane PetkoskiÎncă nu există evaluări

- Infineon Ikcm20l60ga Ds v02 03 enDocument17 paginiInfineon Ikcm20l60ga Ds v02 03 enbetodias30Încă nu există evaluări

- AN650 - Max038 PDFDocument15 paginiAN650 - Max038 PDFbetodias30Încă nu există evaluări

- An185 - Thermal Management Using Heat SinksDocument9 paginiAn185 - Thermal Management Using Heat Sinksbetodias30Încă nu există evaluări

- An-1215 - Iram256-1067aDocument28 paginiAn-1215 - Iram256-1067abetodias30Încă nu există evaluări

- HD44780Document60 paginiHD44780nzltfÎncă nu există evaluări

- Display 20x4 TC2004A-01 PDFDocument18 paginiDisplay 20x4 TC2004A-01 PDFbetodias30Încă nu există evaluări

- MDP Cnvecad enDocument76 paginiMDP Cnvecad enbetodias30Încă nu există evaluări

- Manual Altium 2014 PDFDocument630 paginiManual Altium 2014 PDFbetodias30Încă nu există evaluări

- 1724-Motion Detection - Dual AnalogueDocument2 pagini1724-Motion Detection - Dual Analoguebetodias30Încă nu există evaluări

- Altium - Creating Library ComponentsDocument32 paginiAltium - Creating Library Componentseaa603100% (1)

- Primer Curso AlltiumDocument82 paginiPrimer Curso AlltiumMiguel JardinezÎncă nu există evaluări

- Gu0104 Shortcut KeysDocument16 paginiGu0104 Shortcut Keysbetodias30Încă nu există evaluări

- Loading Material Masters With LSMW Direct Input MethodDocument20 paginiLoading Material Masters With LSMW Direct Input MethodBob GrochowskiÎncă nu există evaluări

- Fix Certificate Error On ChromeDocument10 paginiFix Certificate Error On Chromepardhasaradhi photosÎncă nu există evaluări

- Introduction To CarsimDocument20 paginiIntroduction To Carsimshiva nÎncă nu există evaluări

- Department of Education: Republic of The PhilippinesDocument3 paginiDepartment of Education: Republic of The PhilippinesLeonicus WilliamsÎncă nu există evaluări

- Recovery - Magisk 25.2 (25200) .Apk - 2022 10 31 20 49 07Document21 paginiRecovery - Magisk 25.2 (25200) .Apk - 2022 10 31 20 49 07RaydenflyÎncă nu există evaluări

- Samar National SchoolDocument20 paginiSamar National SchoolJonathan CayatÎncă nu există evaluări

- PersonalisationDocument113 paginiPersonalisationFarooq MohammedÎncă nu există evaluări

- Leaf Disease Detection: Software Requirements SpecificationDocument8 paginiLeaf Disease Detection: Software Requirements Specificationiot forum75% (4)

- Western Digital EIDE Hard Drive: Installation GuideDocument36 paginiWestern Digital EIDE Hard Drive: Installation GuideJohn HamillÎncă nu există evaluări

- Functional Programming IDocument34 paginiFunctional Programming IMoti King MotiÎncă nu există evaluări

- Critical Occupations List 2020/2021: Occupation ReportDocument135 paginiCritical Occupations List 2020/2021: Occupation ReportHamizan HassanÎncă nu există evaluări

- Opensolaris DatasheetDocument2 paginiOpensolaris Datasheetvirtualraidz.com100% (1)

- Pandoc Mode ManualDocument11 paginiPandoc Mode ManualnorbulinuksÎncă nu există evaluări

- Lab 7 PL/SQL: IS221: Database Management SystemsDocument36 paginiLab 7 PL/SQL: IS221: Database Management SystemsmsskjcÎncă nu există evaluări

- Hangman GameDocument15 paginiHangman Gamerohan_twrÎncă nu există evaluări

- Wizard Creation in SAPDocument10 paginiWizard Creation in SAPRicky DasÎncă nu există evaluări

- Tafc Tafj Tafj Format: URL Syntax: : /TAFJEEDocument11 paginiTafc Tafj Tafj Format: URL Syntax: : /TAFJEECHARLES TUMWESIGYEÎncă nu există evaluări

- A Quick Guide To SSI: by Andrew J. WilliamsDocument12 paginiA Quick Guide To SSI: by Andrew J. WilliamsJohn StuartÎncă nu există evaluări

- ViewPower Pro User ManualDocument60 paginiViewPower Pro User ManualredoriciÎncă nu există evaluări

- Correspondence Archiving & Tracking SystemDocument45 paginiCorrespondence Archiving & Tracking SystemahmednaximÎncă nu există evaluări

- PDF Solution of Treybal DLDocument2 paginiPDF Solution of Treybal DLaliÎncă nu există evaluări

- Lab AssignmentsEngg12Document2 paginiLab AssignmentsEngg12Sandeep SukhaniÎncă nu există evaluări

- Bashforsysadmins-Scriptlistingbyfile 1470005386Document16 paginiBashforsysadmins-Scriptlistingbyfile 1470005386Prasanth UnnikrishnanÎncă nu există evaluări

- Verification and ValidationDocument4 paginiVerification and ValidationZamm ZammÎncă nu există evaluări

- Mercusuar Uzone IdDocument26 paginiMercusuar Uzone Idenni fitriaÎncă nu există evaluări

- Integrated Lights Out Manager (ILOM) Administration GuideDocument208 paginiIntegrated Lights Out Manager (ILOM) Administration Guidemgaur2Încă nu există evaluări

- How To Configure A Failover Guest Domain As A Single-Node Oracle Solaris ClusterDocument12 paginiHow To Configure A Failover Guest Domain As A Single-Node Oracle Solaris Clusterimranpathan22Încă nu există evaluări

- Active Home ProDocument25 paginiActive Home ProEnrique RochaÎncă nu există evaluări

- CP600 Webinar Trends, Alarms and Recipes Rev0Document28 paginiCP600 Webinar Trends, Alarms and Recipes Rev0Fabio Passos GuimaraesÎncă nu există evaluări

- CS91000 AdminGuideDocument30 paginiCS91000 AdminGuideChocoGuysÎncă nu există evaluări