Documente Academic

Documente Profesional

Documente Cultură

New Microsoft Word Document

Încărcat de

செல்வம் முத்துராமன்Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

New Microsoft Word Document

Încărcat de

செல்வம் முத்துராமன்Drepturi de autor:

Formate disponibile

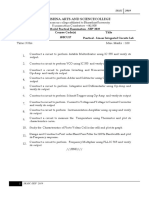

Assignment 1

Due date for this assignment: 2019-03-13, 23:59 IST.

1. In order to remove the body effect, the substrate of an n-channel enhancement mode

MOSFET should be

a) Connected to the most positive bias

b) Connected to the most negative bias

c) Grounded

d) Floating

2. Assuming that the bulk NMOS device has equal source and drain doping then the

effective channel length (Leff) is related to drawn length (Ldrawn) and diffusion length

(LD) as

a) Leff = Ldrawn – 2 LD

b) Leff = Ldrawn – LD

c) Leff = 2Ldrawn – LD

d) Leff = LD – Ldrawn

3. A bulk n-channel enhancement mode MOSFET is biased in the saturation region of

operation, such that VDS> VGS – Vth. Vth is the threshold voltage. Taking into

consideration Channel Length Modulation, the MOSFET in saturation state behaves as

a

a) Constant Voltage Source

b) Variable Voltage Source

c) Current Source with infinite output impedance

d) Current Source with finite output impedance

4. Drain Induced Barrier Lowering (DIBL) for a bulk MOSFET

a) Reduces the device operating frequency

b) Increases the device operating frequency

c) Has no influence on the device operating frequency

d) Increases the carrier transit time

5. Under Gradual Channel Approximation (GCA), the depletion region in the bulk of the

long channel MOSFET on application of a drain bias

a) Reduces as we move towards the drain end

b) Increases as we move towards the drain end

c) Remains constant

d) Has no relationship

6. The unit of mobility is

a) m^2/V-s

b) m/V^2-s

c) m/V-s^2

d) m/V-s

7. Assuming λ as the Channel Length Parameter for a short channel MOSFET, the

formulation used for drain current in SPICE Level-2 for the MOSFET is given as

a) ID= IDsat[1 /(1-λ VDS)]

b) ID = IDsat[1 / (1-VDS) ]

c) ID= IDsat[λ /(1-λ VDS)]

d) ID= IDsat[λ/(λ -λ VDS)]

8. For a bulk MOSFET with aspect ratio of W/L and a depletion width of XD the analytical

expression for gate-to-drain overlap capacitance (Cgd) is

a) Cgd = 2CoxWXD

b) Cgd = CoxXDW/2

c) Cgd = 2CoxXDWL

d) Cgd = CoxXDWL

9. A static CMOS Inverter is powered by a supply voltage of VDD. Assuming the pull-up

and pull-down networks are equal and symmetric, which of the following statement are

true

a) The switching threshold is VDD/2

b) The switching threshold is 2VDD

c) The switching threshold is VDD

d) The switching threshold is VDD/4

10. For a static CMOS, the output is high, then the state of the NMOS and PMOS are as

follows

a) NMOS on and PMOS non-linear

b) NMOS off and PMOS linear

c) NMOS off and PMOS non-linear

d) NMOS on and PMOS linear

S-ar putea să vă placă și

- All India Anna Oravida Munnetra KAZHAGI:..r"! R.Egulations: (Inc Amendments Passed by THF On 5.2-2.007)Document38 paginiAll India Anna Oravida Munnetra KAZHAGI:..r"! R.Egulations: (Inc Amendments Passed by THF On 5.2-2.007)செல்வம் முத்துராமன்Încă nu există evaluări

- IndexDocument1 paginăIndexசெல்வம் முத்துராமன்Încă nu există evaluări

- Expt4 Chopper AmplifierDocument2 paginiExpt4 Chopper AmplifierESAUÎncă nu există evaluări

- 18ecu01 BenDocument7 pagini18ecu01 Benசெல்வம் முத்துராமன்Încă nu există evaluări

- BamaDocument1 paginăBamaசெல்வம் முத்துராமன்Încă nu există evaluări

- BENDocument7 paginiBENசெல்வம் முத்துராமன்Încă nu există evaluări

- Analog Communications: Lab ManualDocument99 paginiAnalog Communications: Lab Manualuday kiranÎncă nu există evaluări

- Cs PDFDocument224 paginiCs PDFசெல்வம் முத்துராமன்Încă nu există evaluări

- TV, ECS - CoursesDocument1 paginăTV, ECS - Coursesசெல்வம் முத்துராமன்Încă nu există evaluări

- How To ApplyDocument6 paginiHow To ApplyKpsmurugesan KpsmÎncă nu există evaluări

- ICI SchemeDocument8 paginiICI Schemeசெல்வம் முத்துராமன்Încă nu există evaluări

- Experiment.3.SingleTunedAmp 22112016Document12 paginiExperiment.3.SingleTunedAmp 22112016Saurav kumarÎncă nu există evaluări

- 18ECU04-Integrated Circuits and InstrumentationDocument3 pagini18ECU04-Integrated Circuits and Instrumentationசெல்வம் முத்துராமன்Încă nu există evaluări

- Draft NEP 2019 en RevisedDocument484 paginiDraft NEP 2019 en RevisedArjun PrabhakaranÎncă nu există evaluări

- Executive Development PDFDocument2 paginiExecutive Development PDFசெல்வம் முத்துராமன்Încă nu există evaluări

- How To ApplyDocument6 paginiHow To ApplyKpsmurugesan KpsmÎncă nu există evaluări

- Executive DevelopmentDocument2 paginiExecutive Developmentசெல்வம் முத்துராமன்Încă nu există evaluări

- 18ECU17-Linear Integrated Circuits LabDocument1 pagină18ECU17-Linear Integrated Circuits Labசெல்வம் முத்துராமன்Încă nu există evaluări

- 4901Document4 pagini4901செல்வம் முத்துராமன்Încă nu există evaluări

- Final Course July-Dec 2019Document20 paginiFinal Course July-Dec 2019செல்வம் முத்துராமன்Încă nu există evaluări

- Cover PagesDocument13 paginiCover Pagesசெல்வம் முத்துராமன்Încă nu există evaluări

- Goms 65 24042019Document12 paginiGoms 65 24042019செல்வம் முத்துராமன்Încă nu există evaluări

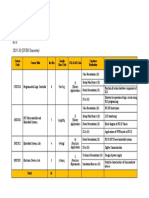

- AC 02 (01) AC 02 (01) : Department: Electronics and Communication Systems Semester: EvenDocument6 paginiAC 02 (01) AC 02 (01) : Department: Electronics and Communication Systems Semester: Evenசெல்வம் முத்துராமன்Încă nu există evaluări

- Design of Low Power Multiplier Using CNTFET: 2017 IEEE 7th International Advance Computing Conference (IACC)Document4 paginiDesign of Low Power Multiplier Using CNTFET: 2017 IEEE 7th International Advance Computing Conference (IACC)செல்வம் முத்துராமன்Încă nu există evaluări

- Microprocessor and Microcontroller Course MaterialDocument165 paginiMicroprocessor and Microcontroller Course Materialசெல்வம் முத்துராமன்Încă nu există evaluări

- Robotics and Machine Vision SystemDocument55 paginiRobotics and Machine Vision Systemசெல்வம் முத்துராமன்Încă nu există evaluări

- Financial Analysis of Shanthi Gears Limited, Coimbatore"Document19 paginiFinancial Analysis of Shanthi Gears Limited, Coimbatore"செல்வம் முத்துராமன்Încă nu există evaluări

- 2 Days: DAY 1 SessionDocument2 pagini2 Days: DAY 1 Sessionசெல்வம் முத்துராமன்Încă nu există evaluări

- 2 Days: DAY 1 SessionDocument2 pagini2 Days: DAY 1 Sessionசெல்வம் முத்துராமன்Încă nu există evaluări

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (894)

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (265)

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (73)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (119)

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)

- Industry LayoutDocument31 paginiIndustry LayoutGiriraj T KulkarniÎncă nu există evaluări

- Adobe Photoshop WorkshopDocument67 paginiAdobe Photoshop WorkshopInigo JosephÎncă nu există evaluări

- Shopping CartDocument40 paginiShopping CartveerusadarÎncă nu există evaluări

- TranslatorsDocument3 paginiTranslatorsijas100% (1)

- Chaderton Barbara AS400Document3 paginiChaderton Barbara AS400Sivakumar RajuÎncă nu există evaluări

- Solucionario Econometría Jeffrey M. WooldridgeDocument4 paginiSolucionario Econometría Jeffrey M. WooldridgeHéctor F Bonilla3% (30)

- MikroTik Wireless Wire nRAYDocument3 paginiMikroTik Wireless Wire nRAYddddÎncă nu există evaluări

- Unlock Networking Possibilities With CloudDocument16 paginiUnlock Networking Possibilities With CloudthedreafÎncă nu există evaluări

- Lesson 7Document42 paginiLesson 7Nithya NairÎncă nu există evaluări

- Page 2Document43 paginiPage 2mariaÎncă nu există evaluări

- Relay Circuit PDFDocument8 paginiRelay Circuit PDFGuru Mishra100% (1)

- Eiki LC-XT2 SMDocument100 paginiEiki LC-XT2 SMgreggles777Încă nu există evaluări

- Accounting 12 Course OutlineDocument3 paginiAccounting 12 Course OutlineKenrose LaguyoÎncă nu există evaluări

- Billing Invoice Payment PlanDocument7 paginiBilling Invoice Payment PlanyogeshÎncă nu există evaluări

- HLAB1Document27 paginiHLAB1SenseiÎncă nu există evaluări

- BOP Replacement Parts CatalogDocument60 paginiBOP Replacement Parts Catalogdesavinicius100% (1)

- Langdo Led Lighting Co.,LimitedDocument24 paginiLangdo Led Lighting Co.,LimitedRudi CressaÎncă nu există evaluări

- 8DIO Songwriting Guitar Read MeDocument10 pagini8DIO Songwriting Guitar Read MeAcidbassÎncă nu există evaluări

- 3 Months Look Ahead PlanDocument6 pagini3 Months Look Ahead PlananjnaÎncă nu există evaluări

- EE1071-Turnitin Guide For StudentsDocument6 paginiEE1071-Turnitin Guide For StudentsRogsÎncă nu există evaluări

- BA-M-PL 830 G3: Product DatasheetDocument5 paginiBA-M-PL 830 G3: Product DatasheetDavid YazoÎncă nu există evaluări

- Quizlet-Quiz 1 Web Apps in OutsystemsDocument2 paginiQuizlet-Quiz 1 Web Apps in OutsystemsedymaradonaÎncă nu există evaluări

- Translated Camera Test Equipment ManualDocument43 paginiTranslated Camera Test Equipment ManualAltaf HussainÎncă nu există evaluări

- IT 111 Chapter1Document72 paginiIT 111 Chapter1Maria Jonalene Dela MercedÎncă nu există evaluări

- Math 10 Learning PlanDocument11 paginiMath 10 Learning PlanmichaelÎncă nu există evaluări

- Advanced SAS Interview Questions You'll Most Likely Be AskedDocument27 paginiAdvanced SAS Interview Questions You'll Most Likely Be AskedVibrant PublishersÎncă nu există evaluări

- AI QuestionsDocument2 paginiAI QuestionsNarender SinghÎncă nu există evaluări

- Ibm Websphere Application Server Advanced Edition, v3.5 - Websphere Jms - Jta Support For Mqseries (370K) WasDocument49 paginiIbm Websphere Application Server Advanced Edition, v3.5 - Websphere Jms - Jta Support For Mqseries (370K) Wasimene IBÎncă nu există evaluări

- Heliodent Plus Manual de Servicio PDFDocument64 paginiHeliodent Plus Manual de Servicio PDFsolcarwx100% (2)

- BNB List 3742Document443 paginiBNB List 3742Walter MatsudaÎncă nu există evaluări